Page 1

A

B

C

D

E

HGF

P75D V10

GP107 128b GDDR5, 75W

1

1

DVI-D + HDMI + DP

TABLE OF CONTENTS

Page

2

3

4

Description

Table of Contents

1

2

Block Diagram

3

PCI Express

4

MEMORY: GPU Partition A/B

5

MEMORY: FBA[31:0]

6

MEMORY: FBA[63:32]

7

MEMORY: FBB[31:0]

8

MEMORY: FBB[63:32]

9

GPU FBVDDQ & 1V8 Decoupling

10

GPU NVVDD & NVVDDS DECOUPLING

11

IFPAB DVI-DL

12

IFPD DP

13

IFPC HDMI

14

IFPEF UNUSED

15

MISC1: Fan, Thermal, JTAG, GPIO

16

MISC2: ROM, XTAL, Straps

17

Power Inputs and Filtering

18

Power Sequence

19

PS: NV3V3 & NV12V

20

PSI: 1V8

21

PSII: 5V & 12V_FAN

22

PS III: PEXVDD

23

PS IV: FBVDDQ

24

PS V: NVVDD OVR2+1

25

PS V: NVVDD Phase 1,2

Page

Description

26

PS V: NVVDD Phase 3

SN Eprom&MECH_ Bracket/Thermal

27

2

3

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAW INGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPEC IFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE W ITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, W ITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRA DE PRACTICE, OR INDUSTRY STANDARDS.

A

B

C

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

ASSEMBLY

PAGE DETAIL

D F H

<ASSEMBLY_DESCRIPTION>

Table of Contents

E

G

Size Project Name: Rev

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

Date : Sheet of

PROPERTY NOTE: This doc ument contains information confidential and

PROPERTY NOTE: This doc ument contains information confidential and

PROPERTY NOTE: This doc ument contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Table of Contents

Table of Contents

Table of Contents

Design By:

Design By:

P75L

P75L

P75L

Design By:

James V10

James V10

James V10

1 27Wednesday, December 21, 2016

1 27Wednesday, December 21, 2016

1 27Wednesday, December 21, 2016

5

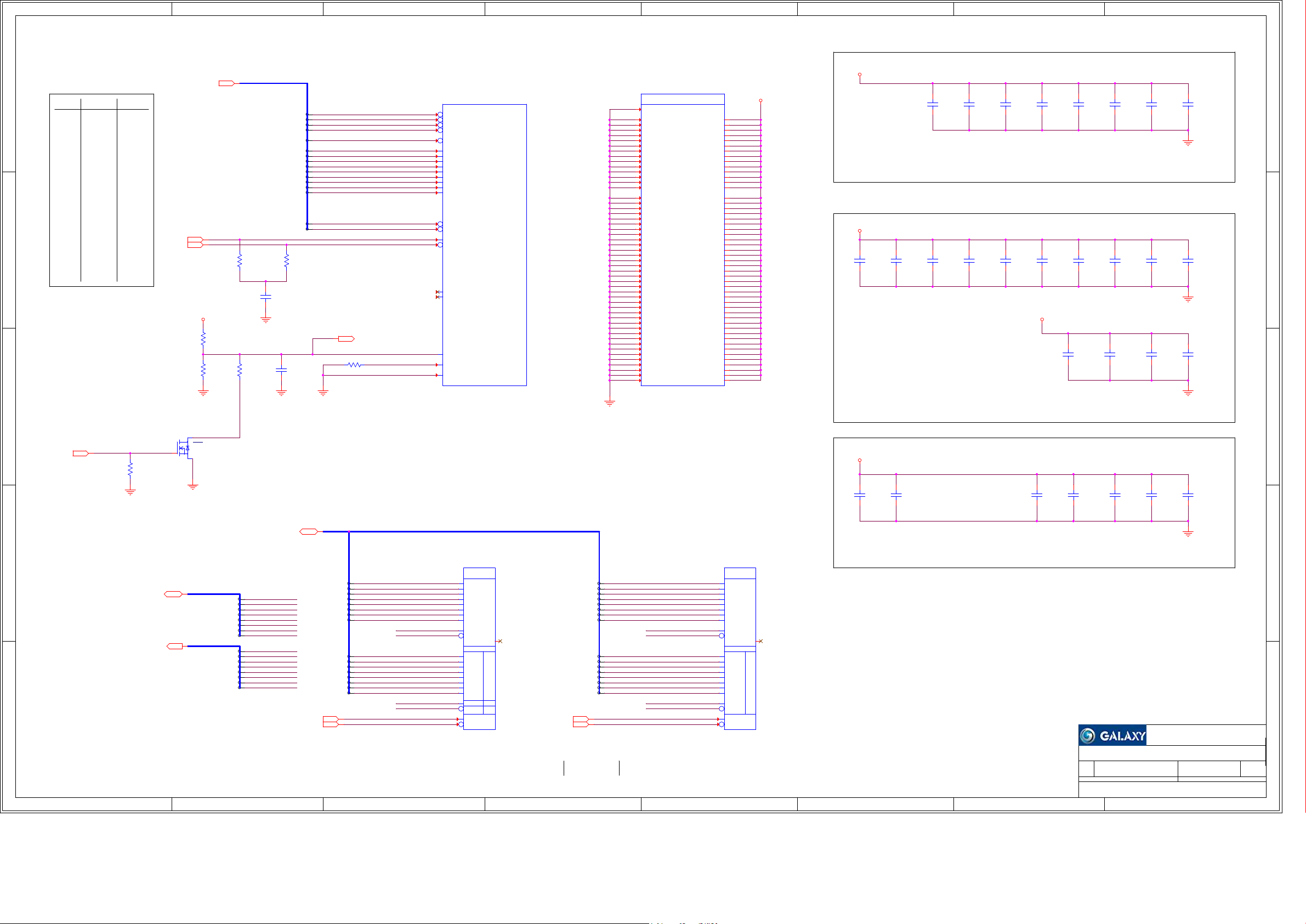

Page 2

A

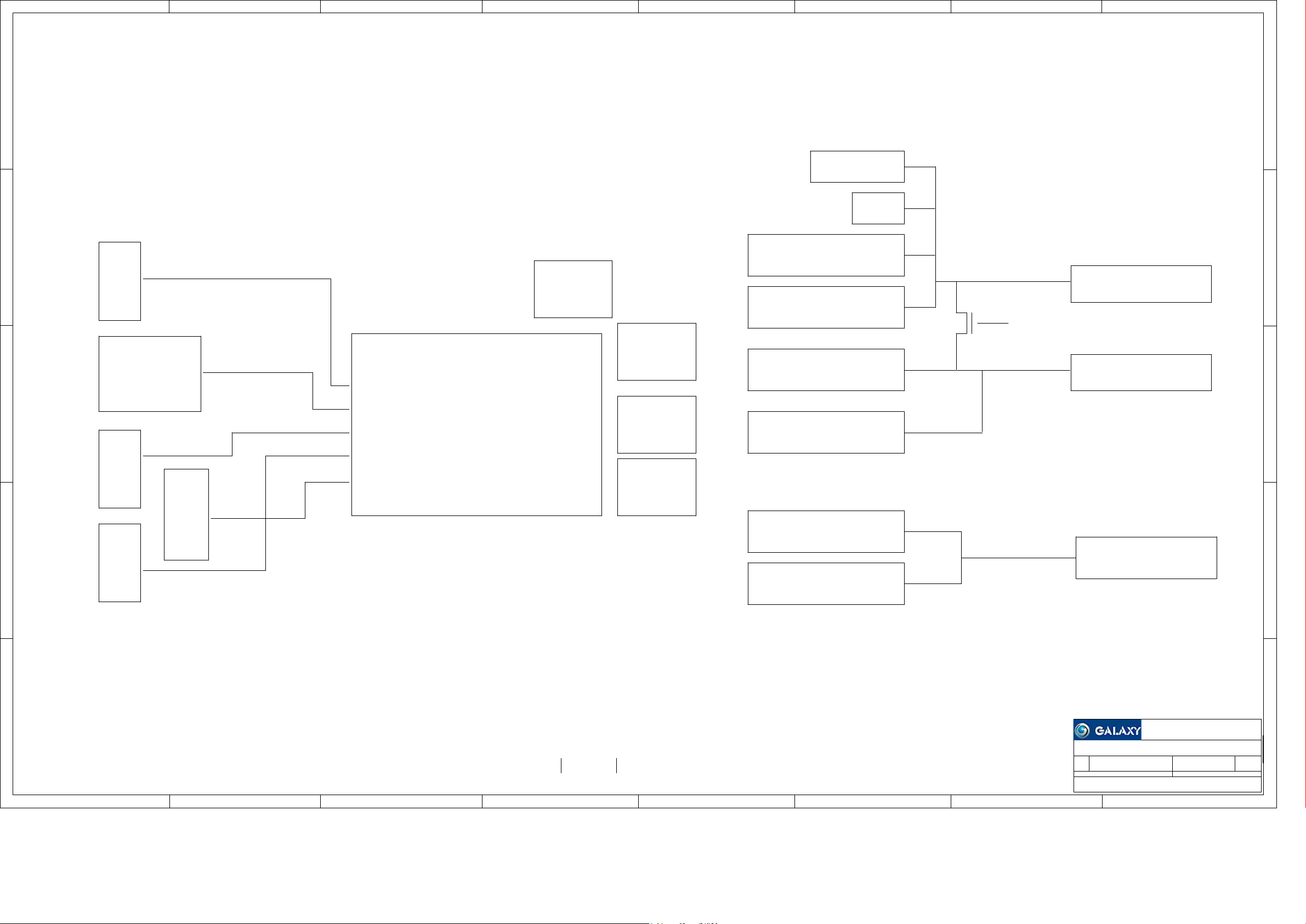

Block Diagram

B

C D

E

F G H

1

1

5V LDO

Fan

2

Power Supply

FBVDD/FBVDDQ

DP

DP/

3

HDMI

LINK C

LINK D

LINK A

LINK B

GP107

MEM

LO

B

EXT6_12V

Power Supply

MEM

HI

MEM

NVVDD-PH3

B

Power Supply

NVVDD-PH1

A

DET

PEX_12V Finger

Power Supply

LO

NVVDD-PH2

2

3

LINK AB

DVI-I

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAW INGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPEC IFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE W ITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, W ITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRA DE PRACTICE, OR INDUSTRY STANDARDS.

DP DP

A

B

C

ASSEMBLY

PAGE DETAIL

MEM

HI

<ASSEMBLY_DESCRIPTION>

Block Diagram

A

PEX_VDD

PEX_3V3 Finger

4

IO_VDD

5

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

Size Project Name: Rev

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

Date : Sheet of

PROPERTY NOTE: This doc ument contains information confidential and

PROPERTY NOTE: This doc ument contains information confidential and

PROPERTY NOTE: This doc ument contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

E

FD

G

Galaxy Microsystems (HK) Ltd.

Block Diagram

Block Diagram

Block Diagram

Design By:

Design By:

P75L

P75L

P75L

Design By:

James V10

James V10

James V10

2 27Wednesday, December 21, 2016

2 27Wednesday, December 21, 2016

2 27Wednesday, December 21, 2016

H

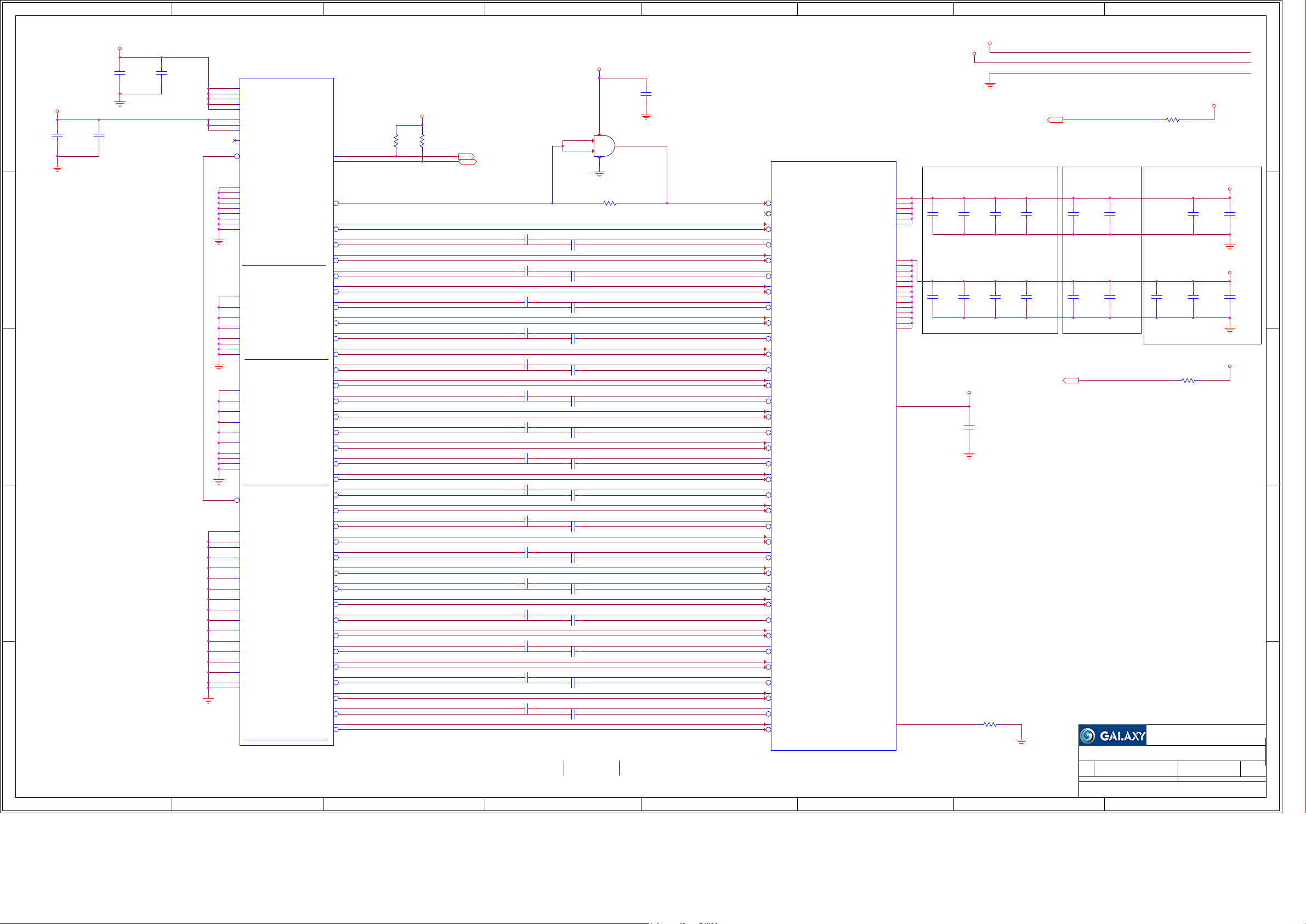

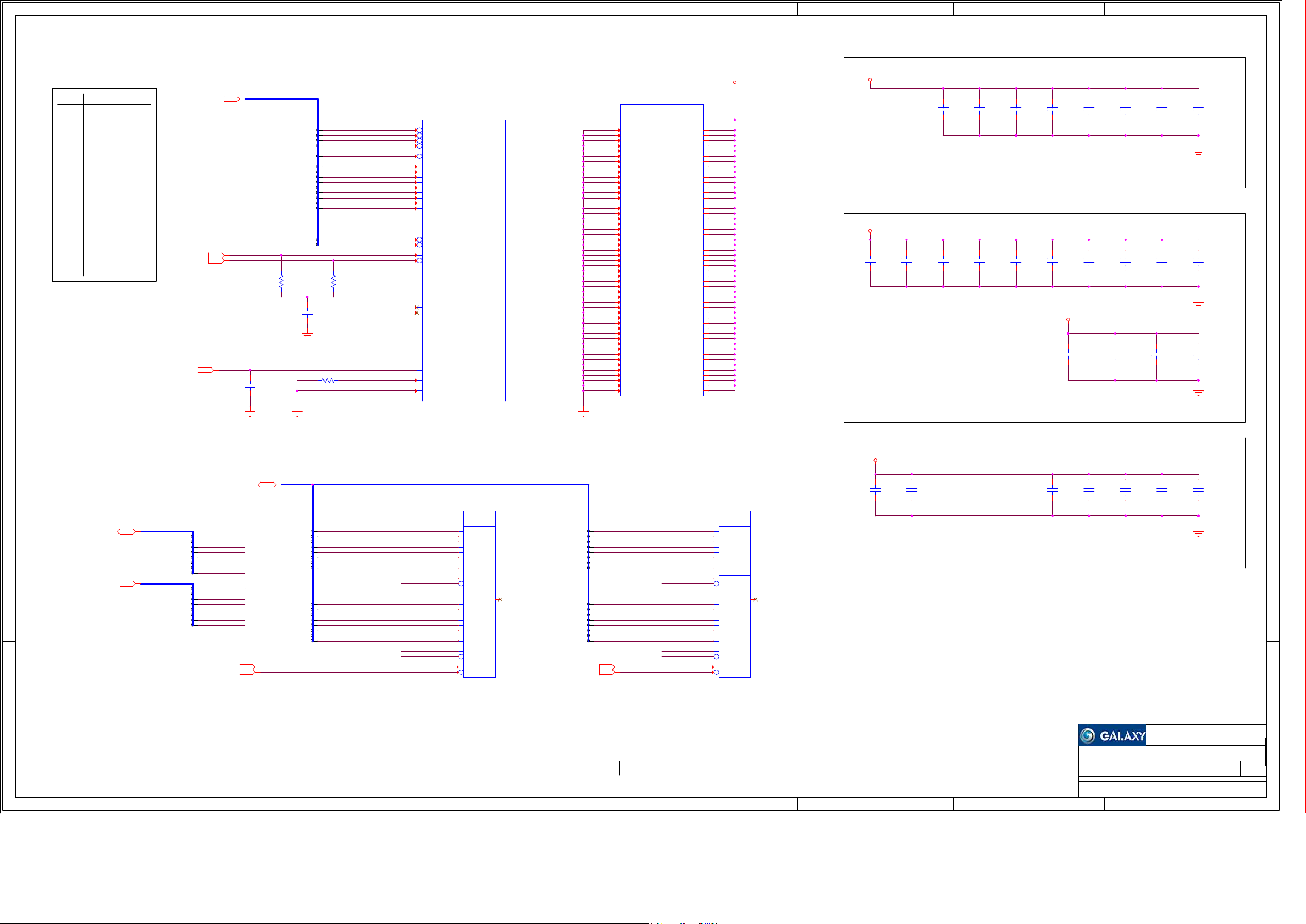

Page 3

A

B

C D

E

F G H

PCI Express

12V

C794

10uF

16V

10%

X5R

0805

C106

0.1uF

16V

10%

X7R

0402

COMMON

COMMON

GND

1

3V3

C107

4.7uF

6.3V

20%

X6S

0603

COMMON

C792

0.1uF

16V

10%

X7R

0402

COMMON

GND

PEX_PRSNT*

2

3

4

GND

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAW INGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPEC IFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE W ITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, W ITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRA DE PRACTICE, OR INDUSTRY STANDARDS.

A

GND

GND

GND

B1

B2

A2

A3

B3

B8

A9

A10

B10

A1

B4

A4

B7

A12

B13

A15

B16

B18

A18

A20

B22

A24

B26

A28

B29

A31

B32

A34

B36

A38

B40

A42

B44

A46

B47

B49

A49

B81

A51

B53

A54

B56

A58

B60

A62

B64

A66

B68

A70

B72

A74

B76

A78

B80

A82

CN1

NONPHY-X16-124PIN

CON_X16

NO STUFF

+12V

+12V

+12V

+12V

+12V/RSVD

+3V3

+3V3

+3V3

+3V3AUX

PRSNT1

GND

GND

GND

GND

GND

GND

GND

GND

GND

END OF X1

GND

GND

GND

GND

GND

GND

GND

GND

END OF X4

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

END OF X8

PRSNT2

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

END OF X16

B

SMCLK

SMDAT

PERST

REFCLK

REFCLK

PERP0

PERN0

PETP0

PETN0

PERP1

PERN1

PETP1

PETN1

PERP2

PERN2

PETP2

PETN2

PERP3

PERN3

PETP3

PETN3

PERP4

PERN4

PETP4

PETN4

PERP5

PERN5

PETP5

PETN5

PERP6

PERN6

PETP6

PETN6

PERP7

PERN7

PETP7

PETN7

PERP8

PERN8

PETP8

PETN8

PERP9

PERN9

PETP9

PETN9

PERP10

PERN10

PETP10

PETN10

PERP11

PERN11

PETP11

PETN11

PERP12

PERN12

PETP12

PETN12

PERP13

PERN13

PETP13

PETN13

PERP14

PERN14

PETP14

PETN14

PERP15

PERN15

PETP15

PETN15

3V3_F

115-14 48-00 0

115-00 14-00 0

R55

R56

100k

100k

5 %

5 %

0402

0402

NO STUFF

PEX_RX0

PEX_RX0

PEX_RX1

PEX_RX1

PEX_RX2

PEX_RX2

PEX_RX3

PEX_RX3

PEX_RX4

PEX_RX4

PEX_RX5

PEX_RX5

PEX_RX6

PEX_RX6

PEX_RX7

PEX_RX7

PEX_RX8

PEX_RX8

PEX_RX9

PEX_RX9

PEX_RX10

PEX_RX10

PEX_RX11

PEX_RX11

PEX_RX12

PEX_RX12

PEX_RX13

PEX_RX13

PEX_RX14

PEX_RX14

PEX_RX15

PEX_RX15

C

NO STUFF

OUT

BI

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEX_REFCLK

PEX_REFCLK

0.22uFC754

0402

COMMON

0.22uFC744

0402

COMMON

0.22uFC732

0402

COMMON

0.22uFC717

0402

COMMON

0.22uFC698

0402

COMMON

0.22uFC684

0402

COMMON

0.22uFC671

0402

COMMON

0.22uFC658

0402

COMMON

0.22uFC640

0402

COMMON

0.22uFC618

0402

COMMON

0.22uFC614

0402

COMMON

0.22uFC608

0402

COMMON

0.22uFC597

0402

COMMON

0.22uFC593

0402

COMMON

0.22uFC587

0402

COMMON

0.22uFC579

0402

COMMON

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

PEX_SMCLK

B5

B6

A11

A13

A14

A16

A17

B14

B15

A21

A22

B19

B20

A25

A26

B23

B24

A29

A30

B27

B28

A35

A36

B33

B34

A39

A40

B37

B38

A43

A44

B41

B42

A47

A48

B45

B46

A52

A53

B50

B51

A56

A57

B54

B55

A60

A61

B58

B59

A64

A65

B62

B63

A68

A69

B66

B67

A72

A73

B70

B71

A76

A77

B74

B75

A80

A81

B78

B79

15

PEX_SMDAT

15

PEX_RST* PEX_RST_BUF*

PEX_REFCLK

PEX_REFCLK*

PEX_TXX0

PEX_TXX0*

PEX_RX0

PEX_RX0*

PEX_TXX1

PEX_TXX1*

PEX_RX1

PEX_RX1*

PEX_TXX2

PEX_TXX2*

PEX_RX2

PEX_RX2*

PEX_TXX3

PEX_TXX3*

PEX_RX3

PEX_RX3*

PEX_TXX4

PEX_TXX4*

PEX_RX4

PEX_RX4*

PEX_TXX5

PEX_TXX5*

PEX_RX5

PEX_RX5*

PEX_TXX6

PEX_TXX6*

PEX_RX6

PEX_RX6*

PEX_TXX7

PEX_TXX7*

PEX_RX7

PEX_RX7*

PEX_TXX8

PEX_TXX8*

PEX_RX8

PEX_RX8*

PEX_TXX9

PEX_TXX9*

PEX_RX9

PEX_RX9*

PEX_TXX10

PEX_TXX10*

PEX_RX10

PEX_RX10*

PEX_TXX11

PEX_TXX11*

PEX_RX11

PEX_RX11*

PEX_TXX12

PEX_TXX12*

PEX_RX12

PEX_RX12*

PEX_TXX13

PEX_TXX13*

PEX_RX13

PEX_RX13*

PEX_TXX14

PEX_TXX14*

PEX_RX14

PEX_RX14*

PEX_TXX15

PEX_TXX15*

PEX_RX15

PEX_RX15*

0.22uFC750

0402

COMMON

0.22uFC740

0402

COMMON

0.22uFC727

0402

COMMON

0.22uFC713

0402

COMMON

0.22uFC693

0402

COMMON

0.22uFC678

0402

COMMON

0.22uFC665

0402

COMMON

0.22uFC650

0402

COMMON

0.22uFC637

0402

COMMON

0.22uFC616

0402

COMMON

0.22uFC613

0402

COMMON

0.22uFC603

0402

COMMON

0.22uFC595

0402

COMMON

0.22uFC592

0402

COMMON

0.22uFC582

0402

COMMON

0.22uFC578

0402

COMMON

ASSEMBLY

PAGE DETAIL

1

2

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

16V

10%

X7R

1V8

5

3

GND

0

R672

0402 NO STUFF

0.05 ohm

PEX_TX0

PEX_TX0*

PEX_TX1

PEX_TX1*

PEX_TX2

PEX_TX2*

PEX_TX3

PEX_TX3*

PEX_TX4

PEX_TX4*

PEX_TX5

PEX_TX5*

PEX_TX6

PEX_TX6*

PEX_TX7

PEX_TX7*

PEX_TX8

PEX_TX8*

PEX_TX9

PEX_TX9*

PEX_TX10

PEX_TX10*

PEX_TX11

PEX_TX11*

PEX_TX12

PEX_TX12*

PEX_TX13

PEX_TX13*

PEX_TX14

PEX_TX14*

PEX_TX15

PEX_TX15*

C765

0.1uF

16V

10%

X7R

0402

COMMON

GND

U504

M74VHC1GT08DFT2G

4

SC70-5

COMMON

PEX_TX0

PEX_TX0

PEX_TX1

PEX_TX1

PEX_TX2

PEX_TX2

PEX_TX3

PEX_TX3

PEX_TX4

PEX_TX4

PEX_TX5

PEX_TX5

PEX_TX6

PEX_TX6

PEX_TX7

PEX_TX7

PEX_TX8

PEX_TX8

PEX_TX9

PEX_TX9

PEX_TX10

PEX_TX10

PEX_TX11

PEX_TX11

PEX_TX12

PEX_TX12

PEX_TX13

PEX_TX13

PEX_TX14

PEX_TX14

PEX_TX15

PEX_TX15

<ASSEMBLY_DESCRIPTION>

PCI Express

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

12V

3V3

12V

3V3

GND

VOLTAGENET

12V

3.3V

0V

8.5A

GND

PS_PEXVDD_FB

OUT

22

R531

0402 COMMON

0.05 ohm

0ohm

MIN_WIDTHMAX_CURRENT

0.4005.5A

0.4003.0A

0.400

PEX_VDD

1

Place under GPU to close PEX_DVDD balls

G1A

@digital.u_gpu_gb4c_128(sym_1):page3_i1175

BGA908

COMMON

1/17 PCI_EXPRESS

Place under GPU

Near to balls

AG19

AJ12

AK12

AL13

AK13

AK14

AJ14

AN12

AM12

AH14

AG14

AN14

AM14

AK15

AJ15

AP14

AP15

AL16

AK16

AN15

AM15

AK17

AJ17

AN17

AM17

AH17

AG17

AP17

AP18

AK18

AJ18

AN18

AM18

AL19

AK19

AN20

AM20

AK20

AJ20

AP20

AP21

AH20

AG20

AN21

AM21

AK21

AJ21

AN23

AM23

AL22

AK22

AP23

AP24

AK23

AJ23

AN24

AM24

AH23

AG23

AN26

AM26

AK24

AJ24

AP26

AP27

AL25

AK25

AN27

AM27

PEX_RST

PEX_CLKREQ

PEX_REFCLK

PEX_REFCLK

PEX_TX0

PEX_TX0

PEX_RX0

PEX_RX0

PEX_TX1

PEX_TX1

PEX_RX1

PEX_RX1

PEX_TX2

PEX_TX2

PEX_RX2

PEX_RX2

PEX_TX3

PEX_TX3

PEX_RX3

PEX_RX3

PEX_TX4

PEX_TX4

PEX_RX4

PEX_RX4

PEX_TX5

PEX_TX5

PEX_RX5

PEX_RX5

PEX_TX6

PEX_TX6

PEX_RX6

PEX_RX6

PEX_TX7

PEX_TX7

PEX_RX7

PEX_RX7

PEX_TX8

PEX_TX8

PEX_RX8

PEX_RX8

PEX_TX9

PEX_TX9

PEX_RX9

PEX_RX9

PEX_TX10

PEX_TX10

PEX_RX10

PEX_RX10

PEX_TX11

PEX_TX11

PEX_RX11

PEX_RX11

PEX_TX12

PEX_TX12

PEX_RX12

PEX_RX12

PEX_TX13

PEX_TX13

PEX_RX13

PEX_RX13

PEX_TX14

PEX_TX14

PEX_RX14

PEX_RX14

PEX_TX15

PEX_TX15

PEX_RX15

PEX_RX15

PEX_DVDD

PEX_DVDD

PEX_DVDD

PEX_DVDD

PEX_DVDD

PEX_DVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_PLL_HVDD

PEX_TERMP

AG21

AG22

AG24

AH21

AH25

AG13

AG15

AG16

AG18

AG25

AH15

AH18

AH26

AH27

AJ27

AK27

AL27

AM28

AN28

AH12

PEX_TERMP

AP29

50OHM_NETCLASS1

C664

1uF

6.3V

10%

X6S

0402

COMMON

C623

1uF

6.3V

10%

X6S

0402

COMMON

GND

1V8

C649

1uF

6.3V

10%

X6S

0402

COMMON

C689

1uF

6.3V

10%

X6S

0402

COMMON

R529

C690

0.1uF

16V

10%

X7R

0402

COMMON

2.49k

0402 COMMON

1 %

C641

1uF

6.3V

10%

X6S

0402

COMMON

C676

1uF

6.3V

10%

X6S

0402

COMMON

C638

1uF

6.3V

10%

X6S

0402

COMMON

C675

1uF

6.3V

10%

X6S

0402

COMMON

GND

E

FD

G

Place near GPU

Place midway GPU <-> VR

PEX_VDD

C150

4.7uF

6.3V

20%

X6S

0603

COMMON

C145

4.7uF

6.3V

20%

X6S

0603

COMMON

OUT

PS_1V8_FB

C151

4.7uF

6.3V

20%

X6S

0603

COMMON

C146

4.7uF

6.3V

20%

X6S

0603

COMMON

C598

22uF

6.3V

20%

X6S

0805

COMMON

C610

22uF

6.3V

20%

X6S

0805

COMMON

20

R536

0402 COMMON

0.05 ohm

0ohm

C611

22uF

6.3V

20%

X6S

0805

COMMON

Place under GPU to close 1V8 balls

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

Size Project Name: Rev

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

Date : Sheet of

PROPERTY NOTE: This doc ument contains information confidential and

PROPERTY NOTE: This doc ument contains information confidential and

PROPERTY NOTE: This doc ument contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

PCI Express

PCI Express

PCI Express

Design By:

Design By:

P75L

P75L

P75L

Design By:

James V10

James V10

James V10

H

3 27Wednesday, December 21, 2016

3 27Wednesday, December 21, 2016

3 27Wednesday, December 21, 2016

GND

GND

C599

22uF

6.3V

20%

X6S

0805

COMMON

2

1V8

C612

22uF

6.3V

20%

X6S

0805

COMMON

1V8

3

4

5

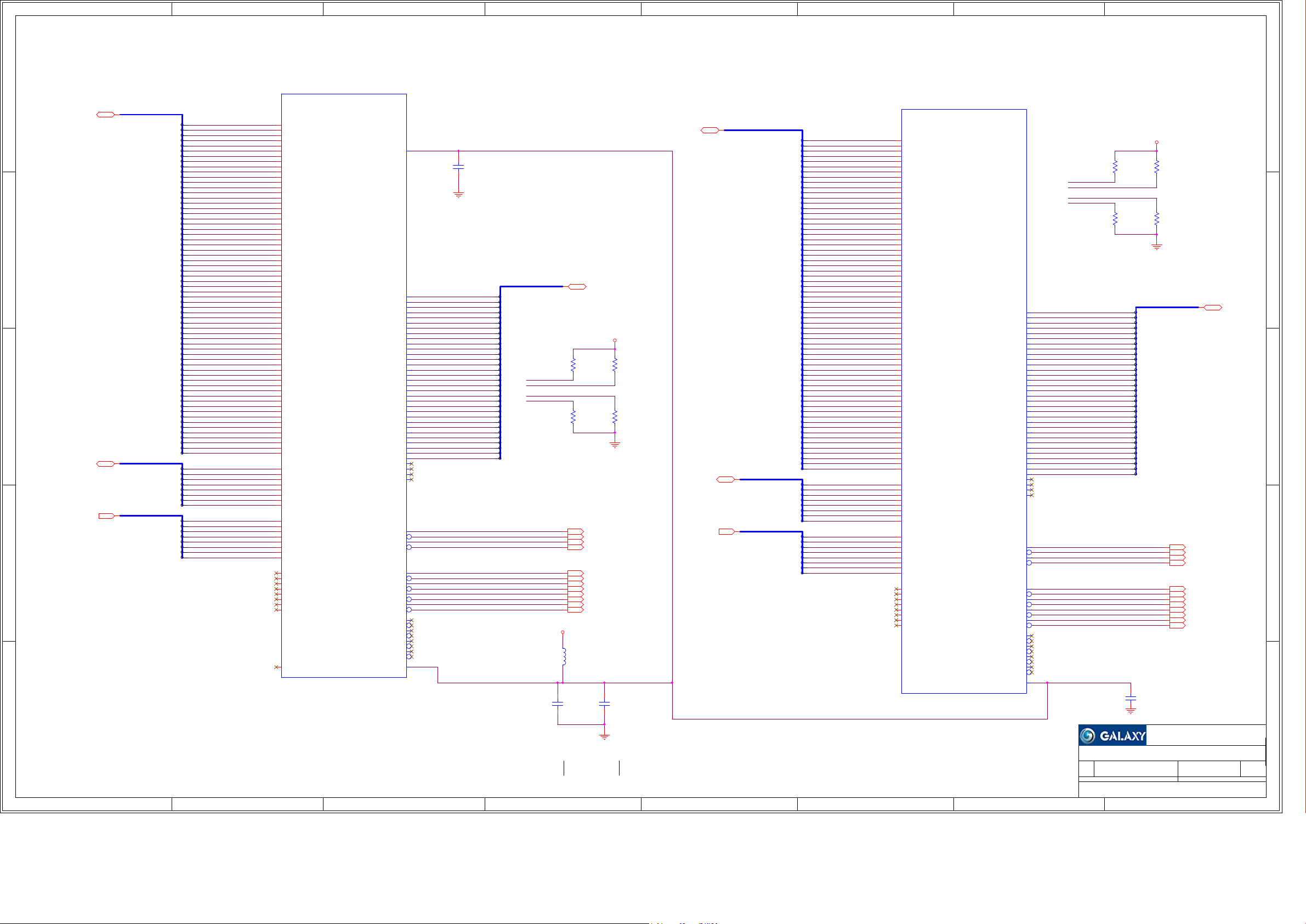

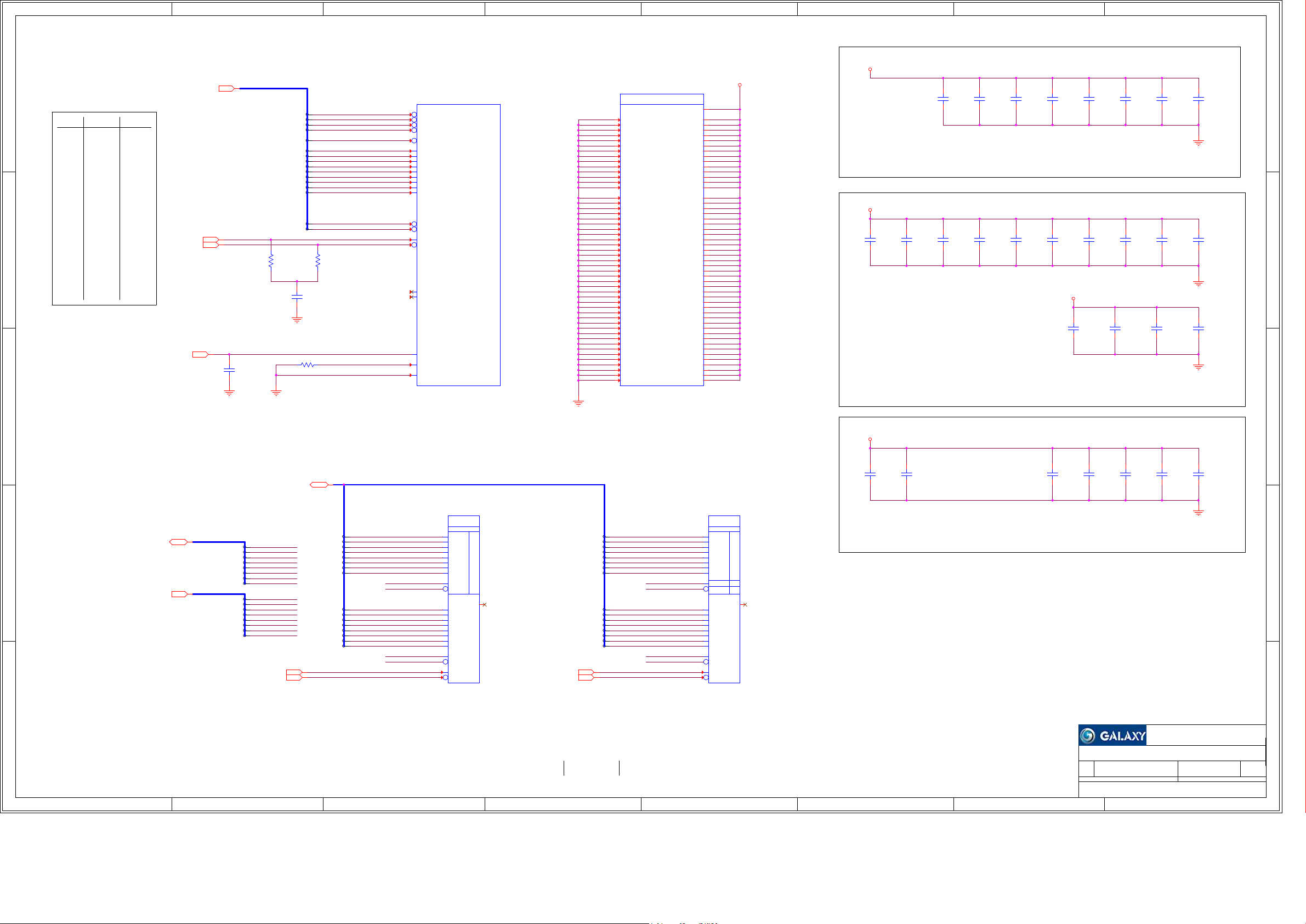

Page 4

A

B

C D

MEMORY: GPU Partition A/B

G1B

@digital.u_gpu_gb4c_128(sym_2):page4_i2168

BGA908

1

FB_DATA

FBA_D[63..0]

BI

2

3

FB_DBI

FBA_DBI[7..0]

BI

FB_EDC

FBA_EDC[7..0]

IN

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAW INGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPEC IFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE W ITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, W ITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRA DE PRACTICE, OR INDUSTRY STANDARDS.

5,6

5,6

5,6

FBA_D0

0

FBA_D1

1

FBA_D2

2

FBA_D3

3

FBA_D4

4

FBA_D5

5

FBA_D6

6

FBA_D7

7

FBA_D8

8

FBA_D9

9

FBA_D10

10

FBA_D11

11

FBA_D12

12

FBA_D13

13

FBA_D14

14

FBA_D15

15

FBA_D16

16

FBA_D17

17

FBA_D18

18

FBA_D19

19

FBA_D20

20

FBA_D21

21

FBA_D22

22

FBA_D23

23

FBA_D24

24

FBA_D25

25

FBA_D26

26

FBA_D27

27

FBA_D28

28

FBA_D29

29

FBA_D30

30

FBA_D31

31

FBA_D32

32

FBA_D33

33

FBA_D34

34

FBA_D35

35

FBA_D36

36

FBA_D37

37

FBA_D38

38

FBA_D39

39

FBA_D40

40

FBA_D41

41

FBA_D42

42

FBA_D43

43

FBA_D44

44

FBA_D45

45

FBA_D46

46

FBA_D47

47

FBA_D48

48

FBA_D49

49

FBA_D50

50

FBA_D51

51

FBA_D52

52

FBA_D53

53

FBA_D54

54

FBA_D55

55

FBA_D56

56

FBA_D57

57

FBA_D58

58

FBA_D59

59

FBA_D60

60

FBA_D61

61

FBA_D62

62

FBA_D63

63

FBA_DBI0

0

FBA_DBI1

1

FBA_DBI2

2

FBA_DBI3

3

FBA_DBI4

4

FBA_DBI5

5

FBA_DBI6

6

FBA_DBI7

7

FBA_EDC0

0

FBA_EDC1

1

FBA_EDC2

2

FBA_EDC3

3

FBA_EDC4

4

FBA_EDC5

5

FBA_EDC6

6

FBA_EDC7

7

A

COMMON

2/17 FBA

L28

FBA_D0

M29

FBA_D1

L29

FBA_D2

M28

FBA_D3

N31

FBA_D4

P29

FBA_D5

R29

FBA_D6

P28

FBA_D7

J28

FBA_D8

H29

FBA_D9

J29

FBA_D10

H28

FBA_D11

G29

FBA_D12

E31

FBA_D13

E32

FBA_D14

F30

FBA_D15

C34

FBA_D16

D32

FBA_D17

B33

FBA_D18

C33

FBA_D19

F33

FBA_D20

F32

FBA_D21

H33

FBA_D22

H32

FBA_D23

P34

FBA_D24

P32

FBA_D25

P31

FBA_D26

P33

FBA_D27

L31

FBA_D28

L34

FBA_D29

L32

FBA_D30

L33

FBA_D31

AG28

FBA_D32

AF29

FBA_D33

AG29

FBA_D34

AF28

FBA_D35

AD30

FBA_D36

AD29

FBA_D37

AC29

FBA_D38

AD28

FBA_D39

AJ29

FBA_D40

AK29

FBA_D41

AJ30

FBA_D42

AK28

FBA_D43

AM29

FBA_D44

AM31

FBA_D45

AN29

FBA_D46

AM30

FBA_D47

AN31

FBA_D48

AN32

FBA_D49

AP30

FBA_D50

AP32

FBA_D51

AM33

FBA_D52

AL31

FBA_D53

AK33

FBA_D54

AK32

FBA_D55

AD34

FBA_D56

AD32

FBA_D57

AC30

FBA_D58

AD33

FBA_D59

AF31

FBA_D60

AG34

FBA_D61

AG32

FBA_D62

AG33

FBA_D63

P30

FBA_DQM0

F31

FBA_DQM1

F34

FBA_DQM2

M32

FBA_DQM3

AD31

FBA_DQM4

AL29

FBA_DQM5

AM32

FBA_DQM6

AF34

FBA_DQM7

M31

FBA_DQS_WP0

G31

FBA_DQS_WP1

E33

FBA_DQS_WP2

M33

FBA_DQS_WP3

AE31

FBA_DQS_WP4

AK30

FBA_DQS_WP5

AN33

FBA_DQS_WP6

AF33

FBA_DQS_WP7

M30

FBA_DQS_RN0

H30

FBA_DQS_RN1

E34

FBA_DQS_RN2

M34

FBA_DQS_RN3

AF30

FBA_DQS_RN4

AK31

FBA_DQS_RN5

AM34

FBA_DQS_RN6

AF32

FBA_DQS_RN7

H31

FB_VREF

B

FB_REFPLL_AVDD

FBA_CMD0

FBA_CMD1

FBA_CMD2

FBA_CMD3

FBA_CMD4

FBA_CMD5

FBA_CMD6

FBA_CMD7

FBA_CMD8

FBA_CMD9

FBA_CMD10

FBA_CMD11

FBA_CMD12

FBA_CMD13

FBA_CMD14

FBA_CMD15

FBA_CMD16

FBA_CMD17

FBA_CMD18

FBA_CMD19

FBA_CMD20

FBA_CMD21

FBA_CMD22

FBA_CMD23

FBA_CMD24

FBA_CMD25

FBA_CMD26

FBA_CMD27

FBA_CMD28

FBA_CMD29

FBA_CMD30

FBA_CMD31

FBA_CMD32

FBA_CMD33

FBA_CMD34

FBA_CMD35

FBA_CLK0

FBA_CLK0

FBA_CLK1

FBA_CLK1

FBA_WCK01

FBA_WCK01

FBA_WCK23

FBA_WCK23

FBA_WCK45

FBA_WCK45

FBA_WCK67

FBA_WCK67

FBA_WCKB01

FBA_WCKB01

FBA_WCKB23

FBA_WCKB23

FBA_WCKB45

FBA_WCKB45

FBA_WCKB67

FBA_WCKB67

FBA_PLL_AVDD

FB_PLLVDD

K27

C615

0.1uF

16V

10%

X7R

0402

COMMON

GND

FB_CMD

FBA_CMD[31..0]

U30

T31

U29

R34

R33

U32

U33

U28

V28

V29

V30

U34

U31

V34

V33

Y32

AA31

AA29

AA28

AC34

AC33

AA32

AA33

Y28

Y29

W31

Y30

AA34

Y31

Y34

Y33

V31

R28

AC28

R32

AC32

R30

R31

AB31

AC31

K31

L30

H34

J34

AG30

AG31

AJ34

AK34

J30

J31

J32

J33

AH31

AJ31

AJ32

AJ33

FBA_CMD0

FBA_CMD1

FBA_CMD2

FBA_CMD3

FBA_CMD4

FBA_CMD5

FBA_CMD6

FBA_CMD7

FBA_CMD8

FBA_CMD9

FBA_CMD10

FBA_CMD11

FBA_CMD12

FBA_CMD13

FBA_CMD14

FBA_CMD15

FBA_CMD16

FBA_CMD17

FBA_CMD18

FBA_CMD19

FBA_CMD20

FBA_CMD21

FBA_CMD22

FBA_CMD23

FBA_CMD24

FBA_CMD25

FBA_CMD26

FBA_CMD27

FBA_CMD28

FBA_CMD29

FBA_CMD30

FBA_CMD31

FBA_CLK0

FBA_CLK0*

FBA_CLK1

FBA_CLK1*

FBA_WCK01

FBA_WCK01*

FBA_WCK23

FBA_WCK23*

FBA_WCK45

FBA_WCK45*

FBA_WCK67

FBA_WCK67*

5,6

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

FBA_CLK0

FBA_CLK0

FBA_CLK1

FBA_CLK1

FBA_WCK01

FBA_WCK01

FBA_WCK23

FBA_WCK23

FBA_WCK45

FBA_WCK45

FBA_WCK67

FBA_WCK67

CKE*

FBA_CMD30

FBA_CMD14

FBA_CMD29

FBA_CMD13

RST *

FB_CLK

5

FB_CLK

5

FB_CLK

6

FB_CLK

6

FB_WCK

5

FB_WCK

5

FB_WCK

5

FB_WCK

5

FB_WCK

6

FB_WCK

6

FB_WCK

6

FB_WCK

6

U27

C

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

1V8

LB501

30ohm

COMMON

BEAD_0603

C617

0.1uF

16V

10%

X7R

0402

COMMON

ASSEMBLY

PAGE DETAIL

BI

R134

10k

5 %

0402

COMMON

R131

10k

5 %

0402

COMMON

GND

FBVDDQ

GND

C609

22uF

6.3V

20%

X6S

0805

COMMON

R133

10k

5 %

0402

COMMON

R130

10k

5 %

0402

COMMON

<ASSEMBLY_DESCRIPTION>

MEMORY: GPU Partition A/B

E

FB_DATA

FBB_D[63..0]

FB_DBI

FBB_DBI[7..0]

FB_EDC

FBB_EDC[7..0]

7,8

7,8

7,8

FBB_D0

0

FBB_D1

1

FBB_D2

2

FBB_D3

3

FBB_D4

4

FBB_D5

5

FBB_D6

6

FBB_D7

7

FBB_D8

8

FBB_D9

9

FBB_D10

10

FBB_D11

11

FBB_D12

12

FBB_D13

13

FBB_D14

14

FBB_D15

15

FBB_D16

16

FBB_D17

17

FBB_D18

18

FBB_D19

19

FBB_D20

20

FBB_D21

21

FBB_D22

22

FBB_D23

23

FBB_D24

24

FBB_D25

25

FBB_D26

26

FBB_D27

27

FBB_D28

28

FBB_D29

29

FBB_D30

30

FBB_D31

31

FBB_D32

32

FBB_D33

33

FBB_D34

34

FBB_D35

35

FBB_D36

36

FBB_D37

37

FBB_D38

38

FBB_D39

39

FBB_D40

40

FBB_D41

41

FBB_D42

42

FBB_D43

43

FBB_D44

44

FBB_D45

45

FBB_D46

46

FBB_D47

47

FBB_D48

48

FBB_D49

49

FBB_D50

50

FBB_D51

51

FBB_D52

52

FBB_D53

53

FBB_D54

54

FBB_D55

55

FBB_D56

56

FBB_D57

57

FBB_D58

58

FBB_D59

59

FBB_D60

60

FBB_D61

61

FBB_D62

62

FBB_D63

63

FBB_DBI0

0

FBB_DBI1

1

FBB_DBI2

2

FBB_DBI3

3

FBB_DBI4

4

FBB_DBI5

5

FBB_DBI6

6

FBB_DBI7

7

FBB_EDC0

0

FBB_EDC1

1

FBB_EDC2

2

FBB_EDC3

3

FBB_EDC4

4

FBB_EDC5

5

FBB_EDC6

6

FBB_EDC7

7

BI

BI

IN

E

F G H

G1C

@digital.u_gpu_gb4c_128(sym_3):page4_i2169

BGA908

COMMON

3/17 FBB

G9

FBB_D0

E9

FBB_D1

G8

FBB_D2

F9

FBB_D3

F11

FBB_D4

G11

FBB_D5

F12

FBB_D6

G12

FBB_D7

G6

FBB_D8

F5

FBB_D9

E6

FBB_D10

F6

FBB_D11

F4

FBB_D12

G4

FBB_D13

E2

FBB_D14

F3

FBB_D15

C2

FBB_D16

D4

FBB_D17

D3

FBB_D18

C1

FBB_D19

B3

FBB_D20

C4

FBB_D21

B5

FBB_D22

C5

FBB_D23

A11

FBB_D24

C11

FBB_D25

D11

FBB_D26

B11

FBB_D27

D8

FBB_D28

A8

FBB_D29

C8

FBB_D30

B8

FBB_D31

F24

FBB_D32

G23

E24

G24

D21

E21

G21

F21

G27

D27

G26

E27

E29

F29

E30

D30

A32

C31

C32

B32

D29

A29

C29

B29

B21

C23

A21

C21

B24

C24

B26

C26

E11

F23

F27

C30

A24

D10

E23

E28

B30

A23

D22

D28

A30

B23

E3

A3

C9

D5

C3

B9

D9

E4

B2

A9

FBB_D33

FBB_D34

FBB_D35

FBB_D36

FBB_D37

FBB_D38

FBB_D39

FBB_D40

FBB_D41

FBB_D42

FBB_D43

FBB_D44

FBB_D45

FBB_D46

FBB_D47

FBB_D48

FBB_D49

FBB_D50

FBB_D51

FBB_D52

FBB_D53

FBB_D54

FBB_D55

FBB_D56

FBB_D57

FBB_D58

FBB_D59

FBB_D60

FBB_D61

FBB_D62

FBB_D63

FBB_DQM0

FBB_DQM1

FBB_DQM2

FBB_DQM3

FBB_DQM4

FBB_DQM5

FBB_DQM6

FBB_DQM7

FBB_DQS_WP0

FBB_DQS_WP1

FBB_DQS_WP2

FBB_DQS_WP3

FBB_DQS_WP4

FBB_DQS_WP5

FBB_DQS_WP6

FBB_DQS_WP7

FBB_DQS_RN0

FBB_DQS_RN1

FBB_DQS_RN2

FBB_DQS_RN3

FBB_DQS_RN4

FBB_DQS_RN5

FBB_DQS_RN6

FBB_DQS_RN7

FBB_CMD0

FBB_CMD1

FBB_CMD2

FBB_CMD3

FBB_CMD4

FBB_CMD5

FBB_CMD6

FBB_CMD7

FBB_CMD8

FBB_CMD9

FBB_CMD10

FBB_CMD11

FBB_CMD12

FBB_CMD13

FBB_CMD14

FBB_CMD15

FBB_CMD16

FBB_CMD17

FBB_CMD18

FBB_CMD19

FBB_CMD20

FBB_CMD21

FBB_CMD22

FBB_CMD23

FBB_CMD24

FBB_CMD25

FBB_CMD26

FBB_CMD27

FBB_CMD28

FBB_CMD29

FBB_CMD30

FBB_CMD31

FBB_CMD32

FBB_CMD33

FBB_CMD34

FBB_CMD35

FBB_CLK0

FBB_CLK0

FBB_CLK1

FBB_CLK1

FBB_WCK01

FBB_WCK01

FBB_WCK23

FBB_WCK23

FBB_WCK45

FBB_WCK45

FBB_WCK67

FBB_WCK67

FBB_WCKB01

FBB_WCKB01

FBB_WCKB23

FBB_WCKB23

FBB_WCKB45

FBB_WCKB45

FBB_WCKB67

FBB_WCKB67

FBB_PLL_AVDD

FD

G

D13

E14

F14

A12

B12

C14

B14

G15

F15

E15

D15

A14

D14

A15

B15

C17

D18

E18

F18

A20

B20

C18

B18

G18

G17

F17

D16

A18

D17

A17

B17

E17

G14

G20

C12

C20

D12

E12

E20

F20

F8

E8

A5

A6

D24

D25

B27

C27

D6

D7

C6

B6

F26

E26

A26

A27

H17

CKE*

FBB_CMD30

FBB_CMD14

FBB_CMD29

FBB_CMD13

RST *

FBB_CMD0

FBB_CMD1

FBB_CMD2

FBB_CMD3

FBB_CMD4

FBB_CMD5

FBB_CMD6

FBB_CMD7

FBB_CMD8

FBB_CMD9

FBB_CMD10

FBB_CMD11

FBB_CMD12

FBB_CMD13

FBB_CMD14

FBB_CMD15

FBB_CMD16

FBB_CMD17

FBB_CMD18

FBB_CMD19

FBB_CMD20

FBB_CMD21

FBB_CMD22

FBB_CMD23

FBB_CMD24

FBB_CMD25

FBB_CMD26

FBB_CMD27

FBB_CMD28

FBB_CMD29

FBB_CMD30

FBB_CMD31

FBB_CLK0

FBB_CLK0*

FBB_CLK1

FBB_CLK1*

FBB_WCK01

FBB_WCK01*

FBB_WCK23

FBB_WCK23*

FBB_WCK45

FBB_WCK45*

FBB_WCK67

FBB_WCK67*

FBB_CLK0

7

FBB_CLK0

7

FBB_CLK1

8

FBB_CLK1

8

FBB_WCK01

7

FBB_WCK01

7

FBB_WCK23

7

FBB_WCK23

7

FBB_WCK45

8

FBB_WCK45

8

FBB_WCK67

8

FBB_WCK67

8

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

Size Project Name: Rev

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

Date : Sheet of

PROPERTY NOTE: This doc ument contains information confidential and

PROPERTY NOTE: This doc ument contains information confidential and

PROPERTY NOTE: This doc ument contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

FBVDDQ

R115

10k

5 %

0402

COMMON

R112

10k

5 %

0402

COMMON

R113

10k

5 %

0402

COMMON

R116

10k

5 %

0402

COMMON

GND

FB_CMD

FBB_CMD[31..0]

7,8

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

FB_CLK

FB_CLK

FB_CLK

FB_CLK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

C668

0.1uF

16V

10%

X7R

0402

GND

COMMON

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

MEMORY: GPU Partition A/B

MEMORY: GPU Partition A/B

MEMORY: GPU Partition A/B

P75L

P75L

P75L

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

Design By:

Design By:

Design By:

H

BI

James V10

James V10

James V10

4 27Wednesday, December 21, 2016

4 27Wednesday, December 21, 2016

4 27Wednesday, December 21, 2016

1

2

3

4

5

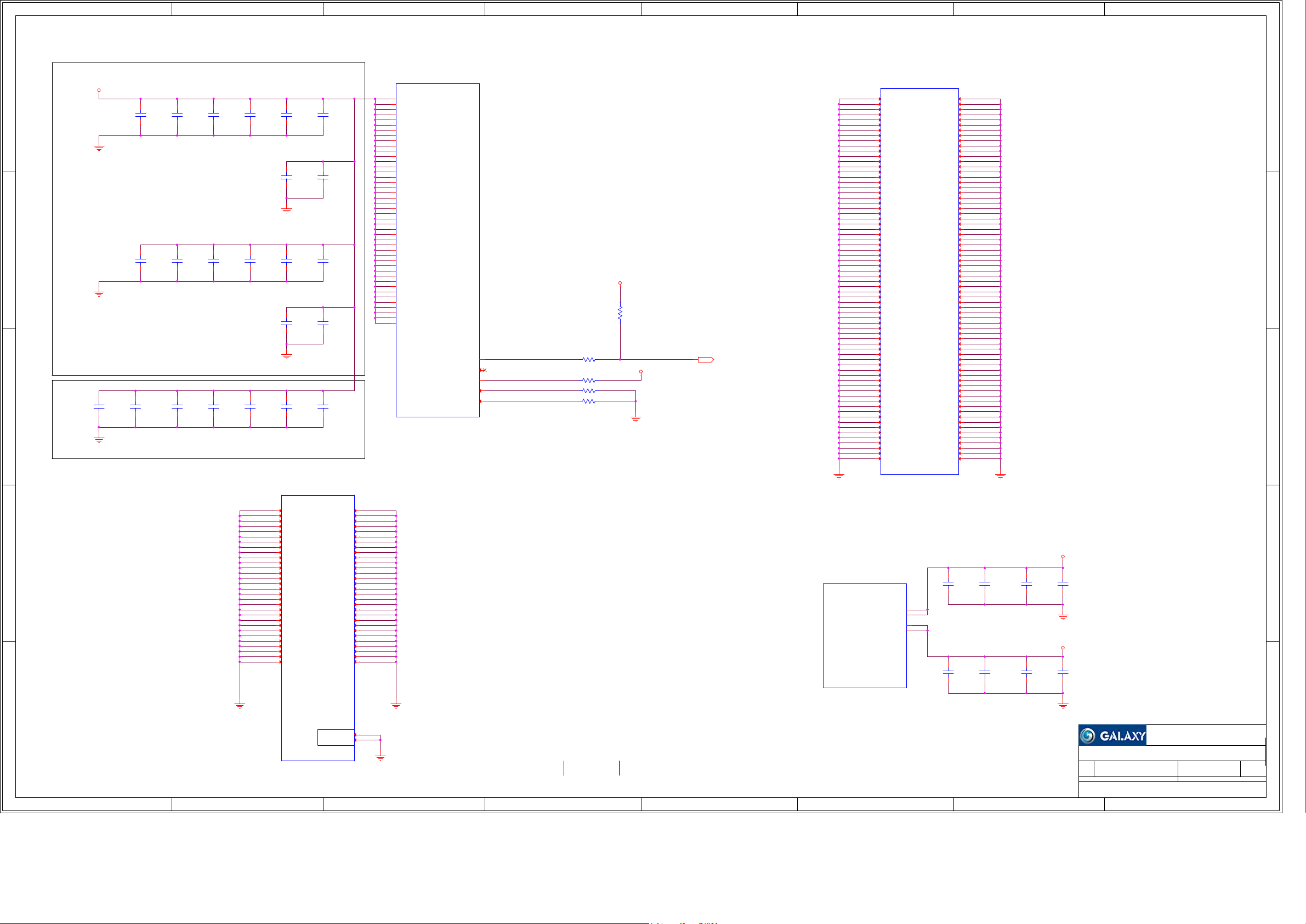

Page 5

A

MEMORY: FBA Partition 31..0

B

C D

E

F G H

FBA_CMD[31..0]

IN

1

2

CMD 0..3 1

CMD0

CS*

A3_BA3

CMD1

A2_BA0

CMD2

A4_BA2

CMD3

A5_BA1

CMD4

WE*

CMD5

A7_A8

CMD6

A6_A11

CMD7

CMD8

ABI*

CMD9

A12_RFU

A0_A10

CMD10

A1_A9

CMD11

CMD12

RAS*

CMD13

RST*

CMD14

CKE*

CMD15

CAS*

CMD16

CMD17

CMD18

CMD19

CMD20

CMD21

CMD22

CMD23

CMD24

CMD25

CMD26

CMD27

CMD28

CMD29

CMD30

CMD31

32.. 63

CS*

A3_BA3

A2_BA0

A4_BA2

A5_BA1

WE*

A7_A8

A6_A11

ABI*

A12_RFU

A0_A10

A1_A9

RAS*

RST*

CKE*

CAS*

IN

IN

R126

40.2

1 %

0402

COMMON

FBA_CLK0_CM

FBVDDQ

R509

549

1 %

0402

COMMON

R132

1.33k

1 %

0402

COMMON

3

GND

R501

931

1 %

0402

COMMON

FBA_CLK0

4

FBA_CLK0*

4

GND

4,6

R128

40.2

1 %

0402

COMMON

C157

103pF

25V

10%

X7R

0402

COMMON

6

C504

103pF

25V

10%

X7R

0402

COMMON

GND GND

12

15

5

0

8

10

11

2

1

3

4

7

6

9

13

14

0.300

FBA_CMD12

FBA_CMD15

FBA_CMD5

FBA_CMD0

FBA_CMD8

FBA_CMD10

FBA_CMD11

FBA_CMD2

FBA_CMD1

FBA_CMD3

FBA_CMD4

FBA_CMD7

FBA_CMD6

FBA_CMD9

FBA_CMD13

FBA_CMD14

OUT

0.140A

R522

121

0402 COMMON

1 %

FBA_VREFC

FBA_ZQ_1

M3A

@memory.u_mem_sd_ddr5_x32(sym_5):page5_i650

BGA170

COMMON

G3

RAS

L3

CAS

L12

WE

G12

CS

J4

ABI

H4

A0_A10

H5

A1_A9

H11

A2_BA0

H10

A3_BA3

K11

A4_BA2

K10

A5_BA1

K5

A6_A11

K4

A7_A8

J5

RFU_A12

J2

RESET

J3

CKE

J12

CLK

J11

CLK

A5

NC_RFU_A5

V5

NC_RFU_V5

J14

VREFC

J13

ZQ

J10

SEN

GND

M3B

@memory.u_mem_sd_ddr5_x32(sym_6):page5_i651

BGA170

COMMON

Normal

J1

MF_VSS/SOE*

add 1k to VSS

B10

VSS

B5

VSS

D10

VSS

G10

VSS

G5

VSS

H1

VSS

H14

VSS

K1

VSS

K14

VSS

L10

VSS

L5

VSS

P10

VSS

T10

VSS

T5

VSS

A1

VSSQ

A12

VSSQ

A14

VSSQ

A3

VSSQ

C1

VSSQ

C11

VSSQ

C12

VSSQ

C14

VSSQ

C3

VSSQ

C4

VSSQ

E1

VSSQ

E12

VSSQ

E14

VSSQ

E3

VSSQ

F10

VSSQ

F5

VSSQ

H13

VSSQ

H2

VSSQ

K13

VSSQ

K2

VSSQ

M10

VSSQ

M5

VSSQ

N1

VSSQ

N12

VSSQ

N14

VSSQ

N3

VSSQ

R1

VSSQ

R11

VSSQ

R12

VSSQ

R14

VSSQ

R3

VSSQ

R4

VSSQ

V1

VSSQ

V12

VSSQ

V14

VSSQ

V3

VSSQ

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

C10

C5

D11

G1

G11

G14

G4

L1

L11

L14

L4

P11

R10

R5

B1

B12

B14

B3

D1

D12

D14

D3

E10

E5

F1

F12

F14

F3

G13

G2

H12

H3

K12

K3

L13

L2

M1

M12

M14

M3

N10

N5

P1

P12

P14

P3

T1

T12

T14

T3

FBVDDQ

FBVDDQ

C166

1uF

6.3V

10%

X6S

0402

COMMON

C163

1uF

6.3V

10%

X6S

0402

COMMON

C170

1uF

6.3V

10%

X6S

0402

COMMON

C555

1uF

6.3V

10%

X6S

0402

COMMON

PLACE Directly Under DRAM

FBVDDQ

C544

1uF

6.3V

10%

X6S

0402

COMMON

C531

1uF

6.3V

10%

X6S

0402

COMMON

C534

1uF

6.3V

10%

X6S

0402

COMMON

C169

1uF

6.3V

10%

X6S

0402

COMMON

C525

1uF

6.3V

10%

X6S

0402

COMMON

C168

1uF

6.3V

10%

X6S

0402

COMMON

FBVDDQ

PLACE AT THE PACKAGE KEEPOUT/PERIMETER OF THE DRAM

C165

10uF

4V

20%

X6S

0603

COMMON

C553

1uF

6.3V

10%

X6S

0402

COMMON

C520

1uF

6.3V

10%

X6S

0402

COMMON

C541

1uF

6.3V

10%

X6S

0402

COMMON

C536

1uF

6.3V

10%

X6S

0402

COMMON

C543

10uF

4V

20%

X6S

0603

COMMON

C549

1uF

6.3V

10%

X6S

0402

COMMON

C548

1uF

6.3V

10%

X6S

0402

COMMON

C174

10uF

4V

20%

X6S

0603

COMMON

GND

GND

GND

C509

1uF

6.3V

10%

X6S

0402

COMMON

C516

1uF

6.3V

10%

X6S

0402

COMMON

C160

10uF

4V

20%

X6S

0603

COMMON

1

2

3

FBA_VREF_Q

G

1

BI

OUT

3

D

Q501

LBSS138LT1

SOT23

S

2

50V

0.2A

22mohm@10V / 22mohm@4.5V / 22mohm@2.5V

6.5A

0.225W

8V

GND

FB_DBI

FBA_DBI[7..0]

FB_EDC

FBA_EDC[7..0]

0.300

FBA_D[63..0]

BI

4,6

FBA_DBI0

0

FBA_DBI1

1

FBA_DBI2

2

FBA_DBI3

3

FBA_DBI4

4

FBA_DBI5

5

FBA_DBI6

6

FBA_DBI7

7

4,6

FBA_EDC0

0

FBA_EDC1

1

FBA_EDC2

2

FBA_EDC3

3

FBA_EDC4

4

FBA_EDC5

5

FBA_EDC6

6

FBA_EDC7

7

IN

IN

B

4,6

M3D

@memory.u_mem_sd_ddr5_x32(sym_1):page5_i648

BGA170

COMMON

FBA_D0

0

FBA_D1

1

FBA_D2

2

FBA_D3

3

FBA_D4

4

FBA_D5

5

FBA_D6

6

FBA_D7

7

8

9

10

11

12

13

14

15

FBA_D8

FBA_D9

FBA_D10

FBA_D11

FBA_D12

FBA_D13

FBA_D14

FBA_D15

FBA_EDC0

FBA_DBI0

FBA_EDC1

FBA_DBI1

FBA_WCK01

4

FBA_WCK01*

4

NORMA L

A4

DQ0

A2

DQ1

B4

DQ2

B2

DQ3

E4

DQ4

E2

DQ5

F4

DQ6

F2

DQ7

C2

EDC0

D2

DBI0

A10

VREFD

x16

x32

A11

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

EDC1

DBI1

WCK01

WCK01

NC

NC

NC

NC

NC

NC

NC

NC

GND

NC

A13

B11

B13

E11

E13

F11

F13

C13

D13

D4

D5

C

1G1D1S

IN

GPIO10_FBVREF_SEL

7,15

R505

10k

5 %

0402

COMMON

GND

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAW INGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPEC IFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE W ITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, W ITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRA DE PRACTICE, OR INDUSTRY STANDARDS.

A

IN

IN

ASSEMBLY

PAGE DETAIL

FBA_D16

16

FBA_D17

17

FBA_D18

18

FBA_D19

19

FBA_D20

20

FBA_D21

21

FBA_D22

22

FBA_D23

23

FBA_D24

24

FBA_D25

25

FBA_D26

26

FBA_D27

27

FBA_D28

28

FBA_D29

29

FBA_D30

30

FBA_D31

31

<ASSEMBLY_DESCRIPTION>

MEMORY: FBA[31:0]

FBA_WCK23

4

FBA_WCK23*

4

FBA_EDC2

FBA_DBI2

FBA_EDC3

FBA_DBI3

M3C

@memory.u_mem_sd_ddr5_x32(sym_3):page5_i649

BGA170

COMMON

NORMA L

V11

DQ16

V13

DQ17

T11

DQ18

T13

DQ19

N11

DQ20

N13

DQ21

M11

DQ22

M13

DQ23

R13

EDC2

P13

DBI2

VREFD

x16

x32

V4

DQ24

V2

T4

T2

N4

N2

M4

M2

R2

P2

P4

P5

NC

DQ25

NC

DQ26

NC

DQ27

NC

DQ28

NC

DQ29

NC

DQ30

NC

DQ31

NC

EDC3

NC

DBI3

NC

WCK23

WCK23

E

FBVDDQ

C519

10uF

4V

20%

X6S

0603

COMMON

C556

10uF

4V

20%

X6S

0603

COMMON

C513

22uF

6.3V

20%

X6S

0805

COMMON

C564

22uF

6.3V

20%

X6S

0805

COMMON

C508

22uF

6.3V

20%

X6S

0805

COMMON

C523

22uF

6.3V

20%

X6S

0805

COMMON

C559

22uF

6.3V

20%

X6S

0805

COMMON

GND

PLACE Around DRAM

4

V10

5

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

Size Project Name: Rev

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

Date : Sheet of

PROPERTY NOTE: This doc ument contains information confidential and

PROPERTY NOTE: This doc ument contains information confidential and

PROPERTY NOTE: This doc ument contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

FD

G

property to Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

MEMORY: FBA Partition 31..0

MEMORY: FBA Partition 31..0

MEMORY: FBA Partition 31..0

Design By:

Design By:

P75L

P75L

P75L

Design By:

H

James V10

James V10

James V10

5 27Wednesday, December 21, 2016

5 27Wednesday, December 21, 2016

5 27Wednesday, December 21, 2016

Page 6

A

MEMORY: FBA Partition 63..32

B

C D

E

F G H

M4B

FBVDDQ

1

2

CMD

CS*

CMD0

A3_BA3

CMD1

A2_BA0

CMD2

A4_BA2

CMD3

A5_BA1

CMD4

WE*

CMD5

A7_A8

CMD6

A6_A11

CMD7

CMD8

ABI*

A12_RFU

CMD9

A0_A10

CMD10

A1_A9

CMD11

RAS*

CMD12

CMD13

RST*

CKE*

CMD14

CAS*CMD15

CMD16

CMD17

CMD18

CMD19

CMD20

CMD21

CMD22

CMD23

CMD24

CMD25 A12_RFU

CMD26

CMD27

CMD28

CMD29

CMD30

CMD31

32.. 630.. 31

CS*

A3_BA3

A2_BA0

A4_BA2

A5_BA1

WE*

A7_A8

A6_A11

ABI*

A0_A10

A1_A9

RAS*

RST*

CKE*

CAS*

IN

IN

IN

FBA_CLK1

FBA_CLK1*

FBA_CMD[31..0]

4

4

4,5

R124

40.2

1 %

0402

COMMON

FBA_CLK1_CM

C156

103pF

25V

10%

X7R

0402

COMMON

M4D

@memory.u_mem_sd_ddr5_x32(sym_5):page6_i734

BGA170_MIRR

G12

H11

H10

COMMON

L3

RAS

G3

CAS

WE

L12

CS

J4

ABI

K4

A0_A10

K5

A1_A9

K11

A2_BA0

K10

A3_BA3

A4_BA2

A5_BA1

H5

A6_A11

H4

A7_A8

J5

RFU_A12

J2

RESET

J3

CKE

J12

CLK

J11

CLK

A5

NC_RFU_A5

V5

NC_RFU_V5

FBA_CMD28

28

FBA_CMD31

31

FBA_CMD21

21

FBA_CMD16

16

FBA_CMD24

24

FBA_CMD26

26

FBA_CMD27

27

FBA_CMD18

18

FBA_CMD17

17

FBA_CMD19

19

FBA_CMD20

20

FBA_CMD23

23

FBA_CMD22

22

FBA_CMD25

25

FBA_CMD29

29

FBA_CMD30

30

R125

40.2

1 %

0402

COMMON

GND

IN

3

5

C540

103pF

25V

10%

X7R

0402

COMMON

R520

0402 COMMON

1 %

121

FBA_VREFC

FBA_ZQ_2_B

GND GND

J14

VREFC

J13

ZQ

J10

SEN

GND

@memory.u_mem_sd_ddr5_x32(sym_7):page6_i735

BGA170_MIRR

COMMON

Mirrored

B10

VSS

B5

VSS

D10

VSS

G10

VSS

G5

VSS

H1

VSS

H14

VSS

K1

VSS

K14

VSS

L10

VSS

L5

VSS

P10

VSS

T10

VSS

T5

VSS

A1

VSSQ

A12

VSSQ

A14

VSSQ

A3

VSSQ

C1

VSSQ

C11

VSSQ

C12

VSSQ

C14

VSSQ

C3

VSSQ

C4

VSSQ

E1

VSSQ

E12

VSSQ

E14

VSSQ

E3

VSSQ

F10

VSSQ

F5

VSSQ

H13

VSSQ

H2

VSSQ

K13

VSSQ

K2

VSSQ

M10

VSSQ

M5

VSSQ

N1

VSSQ

N12

VSSQ

N14

VSSQ

N3

VSSQ

R1

VSSQ

R11

VSSQ

R12

VSSQ

R14

VSSQ

R3

VSSQ

R4

VSSQ

V1

VSSQ

V12

VSSQ

V14

VSSQ

V3

VSSQ

SOE*/MF_VDD

add 1k to VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

J1

C10

C5

D11

G1

G11

G14

G4

L1

L11

L14

L4

P11

R10

R5

B1

B12

B14

B3

D1

D12

D14

D3

E10

E5

F1

F12

F14

F3

G13

G2

H12

H3

K12

K3

L13

L2

M1

M12

M14

M3

N10

N5

P1

P12

P14

P3

T1

T12

T14

T3

FBVDDQ

C539

1uF

6.3V

10%

X6S

0402

COMMON

C521

1uF

6.3V

10%

X6S

0402

COMMON

C546

1uF

6.3V

10%

X6S

0402

COMMON

C550

1uF

6.3V

10%

X6S

0402

COMMON

PLACE Directly Under DRAM

FBVDDQ

C171

1uF

6.3V

10%

X6S

0402

COMMON

C161

1uF

6.3V

10%

X6S

0402

COMMON

C164

1uF

6.3V

10%

X6S

0402

COMMON

C172

1uF

6.3V

10%

X6S

0402

COMMON

C175

1uF

6.3V

10%

X6S

0402

COMMON

C517

1uF

6.3V

10%

X6S

0402

COMMON

FBVDDQ

PLACE AT THE PACKAGE KEEPOUT/PERIMETER OF THE DRAM

C533

10uF

4V

20%

X6S

0603

COMMON

C511

1uF

6.3V

10%

X6S

0402

COMMON

C532

1uF

6.3V

10%

X6S

0402

COMMON

C167

10uF

4V

20%

X6S

0603

COMMON

C547

1uF

6.3V

10%

X6S

0402

COMMON

C515

1uF

6.3V

10%

X6S

0402

COMMON

C561

1uF

6.3V

10%

X6S

0402

COMMON

C518

1uF

6.3V

10%

X6S

0402

COMMON

C528

10uF

4V

20%

X6S

0603

COMMON

GND

GND

GND

C545

1uF

6.3V

10%

X6S

0402

COMMON

C529

1uF

6.3V

10%

X6S

0402

COMMON

C162

10uF

4V

20%

X6S

0603

COMMON

1

2

3

FBA_D[63..0]

BI

FB_DBI

FBA_DBI[7..0]

BI

4

FB_EDC

FBA_EDC[7..0]

IN

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAW INGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPEC IFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE W ITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, W ITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRA DE PRACTICE, OR INDUSTRY STANDARDS.

A

4,5

FBA_DBI0

0

FBA_DBI1

1

FBA_DBI2

2

FBA_DBI3

3

FBA_DBI4

4

FBA_DBI5

5

FBA_DBI6

6

FBA_DBI7

7

4,5

FBA_EDC0

0

FBA_EDC1

1

FBA_EDC2

2

FBA_EDC3

3

FBA_EDC4

4

FBA_EDC5

5

FBA_EDC6

6

FBA_EDC7

7

FBA_WCK45

IN

FBA_WCK45*

IN

B

4,5

M4A

@memory.u_mem_sd_ddr5_x32(sym_2):page6_i732

BGA170_MIRR

COMMON

MIRRORED

FBA_D32

32

FBA_D33

33

FBA_D34

34

FBA_D35

35

FBA_D36

36

FBA_D37

37

FBA_D38

38

FBA_D39

39

FBA_D40

40

FBA_D41

41

FBA_D42

42

FBA_D43

43

FBA_D44

44

FBA_D45

45

FBA_D46

46

FBA_D47

47

4

4

FBA_EDC4

FBA_DBI4

FBA_EDC5

FBA_DBI5

V11

V13

T11

T13

N11

N13

M11

M13

R13

P13

V4

V2

T4

T2

N4

N2

M4

M2

R2

P2

P4

P5

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

EDC0

DBI0

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

EDC1

DBI1

WCK01

WCK01

x16x32

VREFD

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

V10

C

ASSEMBLY

PAGE DETAIL

FBA_D48

48

FBA_D49

49

FBA_D50

50

FBA_D51

51

FBA_D52

52

FBA_D53

53

FBA_D54

54

FBA_D55

55

FBA_D56

56

FBA_D57

57

FBA_D58

58

FBA_D59

59

FBA_D60

60

FBA_D61

61

FBA_D62

62

FBA_D63

63

IN

IN

FBA_EDC6

FBA_DBI6

FBA_EDC7

FBA_WCK67

FBA_WCK67*

<ASSEMBLY_DESCRIPTION>

MEMORY: FBA[63:32]

4

4

FBA_DBI7

M4C

@memory.u_mem_sd_ddr5_x32(sym_4):page6_i733

BGA170_MIRR

COMMON

MIRRORED

x32 x16

A11

DQ16

E

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

EDC2

DBI2

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

EDC3

DBI3

WCK23

WCK23

VREFD

NC

NC

NC

NC

NC

NC

NC

NC

GND

NC

A13

B11

B13

E11

E13

F11

F13

C13

D13

A4

A2

B4

B2

E4

E2

F4

F2

C2

D2

D4

D5

FBVDDQ

C173

10uF

4V

20%

X6S

0603

COMMON

C512

10uF

4V

20%

X6S

0603

COMMON

C524

22uF

6.3V

20%

X6S

0805

COMMON

C554

22uF

6.3V

20%

X6S

0805

COMMON

C176

22uF

6.3V

20%

X6S

0805

COMMON

C570

22uF

6.3V

20%

X6S

0805

COMMON

C560

22uF

6.3V

20%

X6S

0805

COMMON

GND

PLACE Around DRAM

4

A10

5

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

Size Project Name: Rev

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

Date : Sheet of

PROPERTY NOTE: This doc ument contains information confidential and

PROPERTY NOTE: This doc ument contains information confidential and

PROPERTY NOTE: This doc ument contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

FD

G

property to Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

MEMORY: FBA Partition 63..32

MEMORY: FBA Partition 63..32

MEMORY: FBA Partition 63..32

Design By:

Design By:

P75L

P75L

P75L

Design By:

H

James V10

James V10

James V10

6 27Wednesday, December 21, 2016

6 27Wednesday, December 21, 2016

6 27Wednesday, December 21, 2016

Page 7

A

MEMORY: FBB Partition 31..0

B

C D

E

F G H

FBVDDQ

FBB_CMD[31..0]

1

CMD

0.. 31

CMD0

CS*

A3_BA3

CMD1

A2_BA0

CMD2

A4_BA2

CMD3

A5_BA1

CMD4

WE*

CMD5

A7_A8

CMD6

A6_A11

CMD7

CMD8

ABI*

CMD9

A12_RFU

A0_A10

CMD10

A1_A9

CMD11

CMD12

RAS*

CMD13

RST*

CMD14

CKE*

CMD15

CAS*

CMD16

CMD17

CMD18

2

CMD19

CMD20

CMD21

CMD22

CMD23

CMD24

CMD25

CMD26

CMD27

CMD28

CMD29

CMD30

CMD31

32.. 63

CS*

A3_BA3

A2_BA0

A4_BA2

A5_BA1

WE*

A7_A8

A6_A11

ABI*

A12_RFU

A0_A10

A1_A9

RAS*

RST*

CKE*

CAS*

IN

FBB_CLK0

IN

FBB_CLK0*

IN

FBVDDQ

R535

549

1 %

0402

COMMON

FBB_VREF_Q

0.300

R534

931

1 %

0402

COMMON

R558

1.33k

1 %

0402

COMMON

G

1

GND

3

D

Q503

LBSS138LT1

SOT23

S

2

50V

0.2A

22mohm@10V / 22mohm@4.5V / 22mohm@2.5V

6.5A

0.225W

8V

3

1G1D1S

IN

GPIO10_FBVREF_SEL

5,15

4

4

GND

R96

40.2

1 %

0402

COMMON

FBB_CLK0_CM

4,8

FBB_CMD12

12

FBB_CMD15

15

FBB_CMD5

5

FBB_CMD0

0

FBB_CMD8

8

FBB_CMD10

10

FBB_CMD11

11

FBB_CMD2

2

FBB_CMD1

1

FBB_CMD3

3

FBB_CMD4

4

FBB_CMD7

7

FBB_CMD6

6

FBB_CMD9

9

FBB_CMD13

13

FBB_CMD14

14

R95

40.2

1 %

0402

COMMON

C131

103pF

25V

10%

X7R

0402

COMMON

M1A

@memory.u_mem_sd_ddr5_x32(sym_5):page7_i662

BGA170

COMMON

G3

RAS

L3

CAS

L12

WE

G12

CS

J4

ABI

H4

A0_A10

H5

A1_A9

H11

A2_BA0

H10

A3_BA3

K11

A4_BA2

K10

A5_BA1

K5

A6_A11

K4

A7_A8

J5

RFU_A12

J2

RESET

J3

CKE

J12

CLK

J11

CLK

A5

NC_RFU_A5

V5

NC_RFU_V5

GND

C659

103pF

25V

10%

X7R

0402

COMMON

8

0.300

121

R88

0402 COMMON

1 %

0.140A

OUT

FBB_VREFC

J14

FBB_ZQ_1

VREFC

J13

ZQ

J10

SEN

GND GND

GND

FBB_D[63..0]

BI

4

BI

IN

FB_DBI

FBB_DBI[7..0]

FB_EDC

FBB_EDC[7..0]

4,8

FBB_DBI0

0

FBB_DBI1

1

FBB_DBI2

2

FBB_DBI3

3

FBB_DBI4

4

FBB_DBI5

5

FBB_DBI6

6

FBB_DBI7

7

4,8

FBB_EDC0

0

FBB_EDC1

1

FBB_EDC2

2

FBB_EDC3

3

FBB_EDC4

4

FBB_EDC5

5

FBB_EDC6

6

FBB_EDC7

7

IN

IN

4,8

M1D

@memory.u_mem_sd_ddr5_x32(sym_1):page7_i663

BGA170

COMMON

FBB_D0

0

FBB_D1

1

FBB_D2

2

FBB_D3

3

FBB_D4

4

FBB_D5

5

FBB_D6

6

FBB_D7

7

8

9

10

11

12

13

14

15

FBB_D8

FBB_D9

FBB_D10

FBB_D11

FBB_D12

FBB_D13

FBB_D14

FBB_D15

FBB_WCK01

4

FBB_WCK01*

4

FBB_EDC0

FBB_DBI0

FBB_EDC1

FBB_DBI1

NORMA L

A4

DQ0

A2

DQ1

B4

DQ2

B2

DQ3

E4

DQ4

E2

DQ5

F4

DQ6

F2

DQ7

C2

EDC0

D2

DBI0

A10

VREFD

x16

x32

A11

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

EDC1

DBI1

WCK01

WCK01

NC

NC

NC

NC

NC

NC

NC

NC

GND

NC

IN

IN

A13

B11

B13

E11

E13

F11

F13

C13

D13

D4

D5

M1B

@memory.u_mem_sd_ddr5_x32(sym_6):page7_i639

BGA170

COMMON

Normal

J1

MF_VSS/SOE*

add 1k to VSS

B10

VSS

B5

VSS

D10

VSS

G10

VSS

G5

VSS

H1

VSS

H14

VSS

K1

VSS

K14

VSS

L10

VSS

L5

VSS

P10

VSS

T10

VSS

T5

VSS

A1

VSSQ

A12

VSSQ

A14

VSSQ

A3

VSSQ

C1

VSSQ

C11

VSSQ

C12

VSSQ

C14

VSSQ

C3

VSSQ

C4

VSSQ

E1

VSSQ

E12

VSSQ

E14

VSSQ

E3

VSSQ

F10

VSSQ

F5

VSSQ

H13

VSSQ

H2

VSSQ

K13

VSSQ

K2

VSSQ

M10

VSSQ

M5

VSSQ

N1

VSSQ

N12

VSSQ

N14

VSSQ

N3

VSSQ

R1

VSSQ

R11

VSSQ

R12

VSSQ

R14

VSSQ

R3

VSSQ

R4

VSSQ

V1

VSSQ

V12

VSSQ

V14

VSSQ

V3

VSSQ

FBB_D16

16

FBB_D17

17

FBB_D18

18

FBB_D19

19

FBB_D20

20

FBB_D21

21

FBB_D22

22

FBB_D23

23

FBB_D24

24

FBB_D25

25

FBB_D26

26

FBB_D27

27

FBB_D28

28

FBB_D29

29

FBB_D30

30

FBB_D31

31

FBB_WCK23

4

FBB_WCK23*

4

FBB_EDC2

FBB_DBI2

FBB_EDC3

FBB_DBI3

C10

VDD

C5

VDD

D11

VDD

G1

VDD

G11

VDD

G14

VDD

G4

VDD

L1

VDD

L11

VDD

L14

VDD

L4

VDD

P11

VDD

R10

VDD

R5

VDD

B1

VDDQ

B12

VDDQ

B14

VDDQ

B3

VDDQ

D1

VDDQ

D12

VDDQ

D14

VDDQ

D3

VDDQ

E10

VDDQ

E5

VDDQ

F1

VDDQ

F12

VDDQ

F14

VDDQ

F3

VDDQ

G13

VDDQ

G2

VDDQ

H12

VDDQ

H3

VDDQ

K12

VDDQ

K3

VDDQ

L13

VDDQ

L2

VDDQ

M1

VDDQ

M12

VDDQ

M14

VDDQ

M3

VDDQ

N10

VDDQ

N5

VDDQ

P1

VDDQ

P12

VDDQ

P14

VDDQ

P3

VDDQ

T1

VDDQ

T12

VDDQ

T14

VDDQ

T3

VDDQ

M1C

@memory.u_mem_sd_ddr5_x32(sym_3):page7_i664

BGA170

COMMON

NORMA L

V11

DQ16

V13

DQ17

T11

DQ18

T13

DQ19

N11

DQ20

N13

DQ21

M11

DQ22

M13

DQ23

R13

EDC2

P13

DBI2

VREFD

x16

x32

V4

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

EDC3

DBI3

WCK23

WCK23

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

V2

T4

T2

N4

N2

M4

M2

R2

P2

P4

P5

FBVDDQ

V10

C124

1uF

6.3V

10%

X6S

0402

COMMON

C125

1uF

6.3V

10%

X6S

0402

COMMON

C751

1uF

6.3V

10%

X6S

0402

COMMON

C757

1uF

6.3V

10%

X6S

0402

COMMON

PLACE Directly Under DRAM

FBVDDQ

C126

1uF

6.3V

10%

X6S

0402

COMMON

C136

1uF

6.3V

10%

X6S

0402

COMMON

C749

1uF

6.3V

10%

X6S

0402

COMMON

C137

1uF

6.3V

10%

X6S

0402

COMMON

C742

1uF

6.3V

10%

X6S

0402

COMMON

C708

1uF

6.3V

10%

X6S

0402

COMMON

FBVDDQ

PLACE AT THE PACKAGE KEEPOUT/PERIMETER OF THE DRAM

FBVDDQ

C123

10uF

4V

20%

X6S

0603

COMMON

C139

10uF

4V

20%

X6S

0603

COMMON

C775

22uF

6.3V

20%

X6S

0805

COMMON

PLACE Around DRAM

C771

10uF

4V

20%

X6S

0603

COMMON

C764

1uF

6.3V

10%

X6S

0402

COMMON

C709

1uF

6.3V

10%

X6S

0402

COMMON

C705

22uF

6.3V

20%

X6S

0805

COMMON

C772

10uF

4V

20%

X6S

0603

COMMON

C769

1uF

6.3V

10%

X6S

0402

COMMON

C724

1uF

6.3V

10%

X6S

0402

COMMON

C706

22uF

6.3V

20%

X6S

0805

COMMON

C138

10uF

4V

20%

X6S

0603

COMMON

C770

1uF

6.3V

10%

X6S

0402

COMMON

C737

1uF

6.3V

10%

X6S

0402

COMMON

C774

22uF

6.3V

20%

X6S

0805

COMMON

GND

GND

GND

C766

1uF

6.3V

10%

X6S

0402

COMMON

C741

1uF

6.3V

10%

X6S

0402

COMMON

C707

10uF

4V

20%

X6S

0603

COMMON

GND

C688

22uF

6.3V

20%

X6S

0805

COMMON

1

2

3

4

5