NTE NTE857M, NTE857SM Datasheet

NTE857M

NTE857SM

Integrated Circuit

Low–Noise JFET–Input Operational Amplifier

Description:

The NTE857M and NTE857SM are low–noise JFET input operational amplifiers combining two

state–of–the–art linear technologies on a single monolithic integrated circuit. Each internally compensated operational amplifier has well matched high voltage JFET input devices for low input offset

voltage. The BIFET technology provides wide bandwidths and fast slew rates with low input bias currents, input offset currents, and supply currents. Moreover, these devices exhibit low–noise and low

harmonic distortion making them ideal for use in high–fidelity audio amplifier applications.

Features:

D Available in Two Different Package Types:

8–Lead Mini DIP (NTE857M)

SOIC–8 Surface Mount (NTE857SM)

D Low Input Noise Voltage: 18nV√Hz

D Low Harmonic Distortion: 0.01% Typ

D Low Input Bias and Offset Currents

12

D High Input Impedance: 10

Ω Ty p

D High Slew Rate: 13V/µs Typ

D Wide Gain Bandwidth: 4MHz Typ

D Low Supply Current: 1.4mA per Amp

Ty p

Absolute Maximum Ratings:

Supply Voltage

V

CC

V

EE

Differential Input Voltage, V

Input Voltage Range (Note 1), V

Output Short–Circuit Duration (Note 2), t

Power Dissipation, P

D

Derate Above T

ID

IDR

S

= +47°C 10mW/°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A

Operating Ambient Temperature Range, T

Storage Temperature Range, T

stg

Continuous. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A

–65° to +150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

+18V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

–18V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

±30V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

±15V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

680mW. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

0 to +70°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Note 1. The magnitude of the input voltage must not exceed the magnitude of the supply voltage or

15V, whichever is less.

Note 2. The output may be shorted to GND or either supply. Temperature and/or supply voltages

must be limited to ensure that power dissipation ratungs are not exceeded.

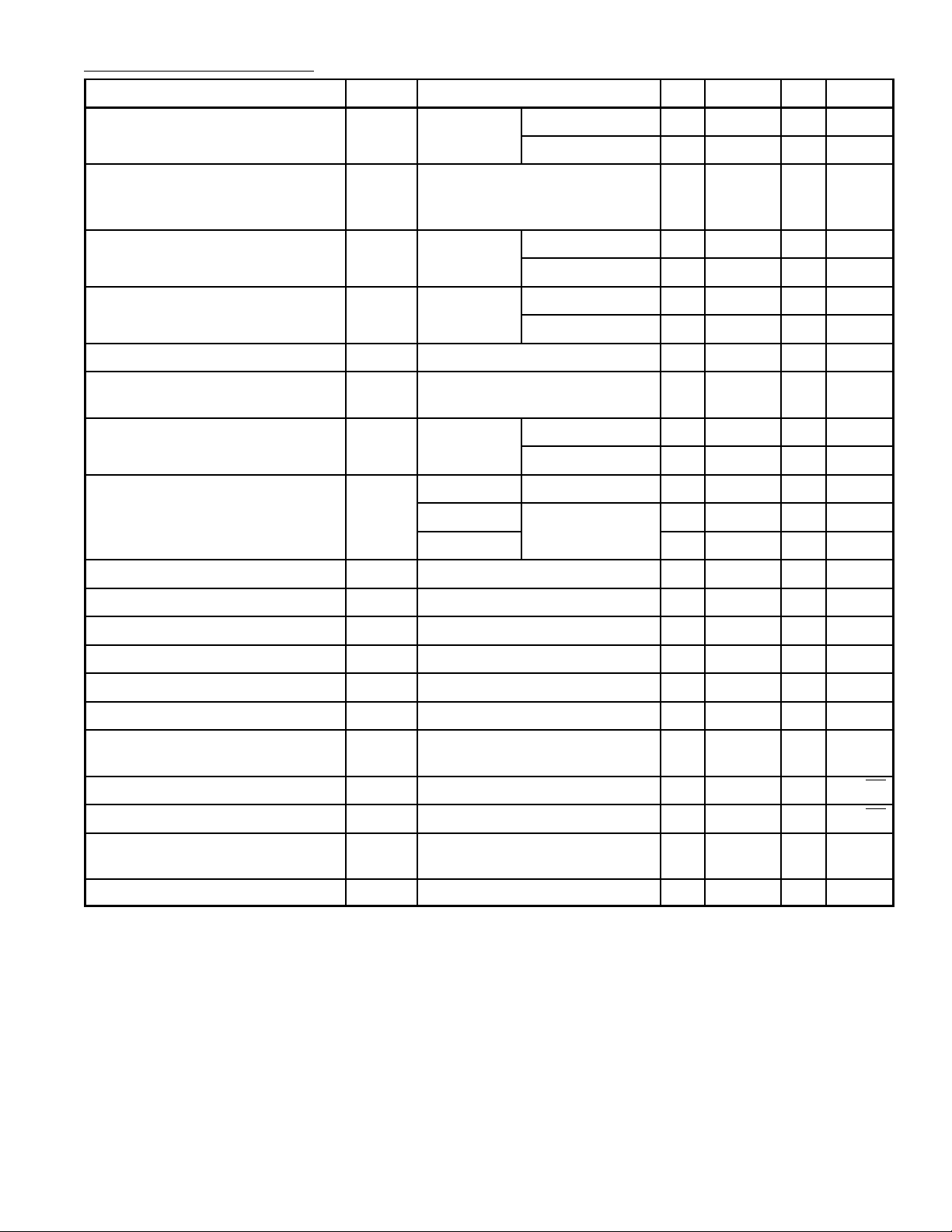

Electrical Characteristics: (VCC = +15V, VEE = –15V, TA = +25°C unless otherwise specified)

Parameter Symbol Test Conditions Min Typ Max Unit

Input Offset Voltage V

Average Temperature

∆VIO/∆T TA = 0 to +70°C – 10 – µV/°C

Coefficient of Input Offset

Voltage

Input Offset Current I

Input Bias Current I

Input Resistance r

Common Mode Input Voltage

V

Range

Large–Signal Voltage Gain A

Output Voltage Swing V

(Peak–to–Peak)

IO

IO

IB

i

ICR

VOL

O

RS ≤ 10k,

VCM = 0

VCM = 0,

Note 3

VCM = 0,

Note 3

TA = 0 to +70°C – – 13 mV

TA = 0 to +70°C – – 2 nA

TA = 0 to +70°C – – 7 nA

– 3 10 mV

– 5 50 pA

– 30 200 pA

– 10

12

– Ω

±10 +15, –12 – V

VO = ±10V,

RL ≤ 2k

TA = 0 to +70°C 15 – – V/mV

25 150 – V/mV

RL = 10k 24 28 – V

RL ≥ 10k

TA = 0 to +70°C

24 – – V

RL ≥ 2k 20 – – V

Common Mode Rejection Ratio CMRR RS ≤ 10k 70 100 – dB

Supply Voltage Rejection Ratio PSRR RS ≤ 10k 70 100 – dB

Supply Current (Each Amplifier) I

D

– 1.4 2.5 mA

Unity Gain Bandwidth BW – 4 – MHz

Slew Rate SR VIN = 10V, RL = 2k, CL = 100pF – 13 – V/µs

Rise Time t

r

Overshoot Factor VIN = 20mV, RL = 2k,

= 100pF

C

L

Equivalent Input Noise Voltage e

Equivalent Input Noise Current i

Total Harmonic Distortion THD V

RS = 100Ω, f = 1000Hz – 18 – nV/√Hz

n

RS = 100Ω, f = 1000Hz – 0.01 – pA/√Hz

n

O(RMS)

R

L

= 10V, RS ≤ 1k,

≥ 2k, f = 1000Hz

– 0.1 – µs

– 10 – %

– 0.01 – %

Channel Separation AV = 100 – 120 – dB

Note 3. Input Bias currents of JFET input operational amplifiers approximately double for every 10°C

rise in Junction Temperature. To maintain Junction Temperature as close to Ambient Temperature as possible, pulse techniques must be used during test.

Loading...

Loading...