NTE NTE7156 Datasheet

NTE7156

Integrated Circuit

DC–Coupled Vertical Deflection Circuit

Description:

The NTE7156 is a power circuit in a 9–Lead SIP type package designed for use in 90° and 110° color

deflection systems for field frequencies of 50Hz to 120Hz. This device provides a DC driven vertical

deflection output circuit, operating as a highly efficient class G system.

Features:

D Few External Components

D Highly Efficient Fully DC–Coupled Vertical Output Bridge Circuit

D Vertical Flyback Switch

D Guard Circuit

D Protection Aaginst:

– Short–Circuit of the Output Pins (7 and 4)

– Short–Circuit of the Output Pins to V

D Temperature Protection

D High EMC Immunity Because of Common Mode Inputs

D A Guard Signal in Zoom Mode

Absolute Maximum Ratings:

DC Supply

Supply Voltage, V

P

Non–Operating 40V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating 25V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Flyback Supply Voltage, V

FB

Note 1 60V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Vertical Circuit

Output Current (Peak–to–Peak Value, Note 2), I

Output Voltage (Pin7), V

O(A)

Note 1 62V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Flyback Switch

Peak Output Current, I

M

Thermal Data

Virtual Junction Temperature, T

VJ

Operating Ambient Temperature Range, T

Storage Temperature Range, T

stg

Thermal Resistance, Virtual Junction–to–Ambient, R

Thermal Resistance, Virtual Junction–to–Case, R

Short–Circuit Time (Note 3), t

sc

Note 1. A flyback supply voltage of > 50V up to 60V is allowed in application. A 22–nF capacititor

in series with a 22Ω resistor (depending on I

nected between Pin7 and GND. The decoupling capacitor of V

tween Pin6 and Pin3. This supply voltage line must have a resistance of 33Ω.

Note 2. I

Note 3. Up to V

maximum determined by current protection.

O

= 18V.

P

P

50V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

O(P–P)

3A. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

52V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

±15A. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

+150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A

–20° to +75°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

–55° to +150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

thVJ–C

thVJ–A

40K/W. . . . . . . . . . . . . . . . . . . . . . . . . . .

4K/W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1 Hour. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

and the inductance of the coil) has to be con-

O

has to be connected be-

FB

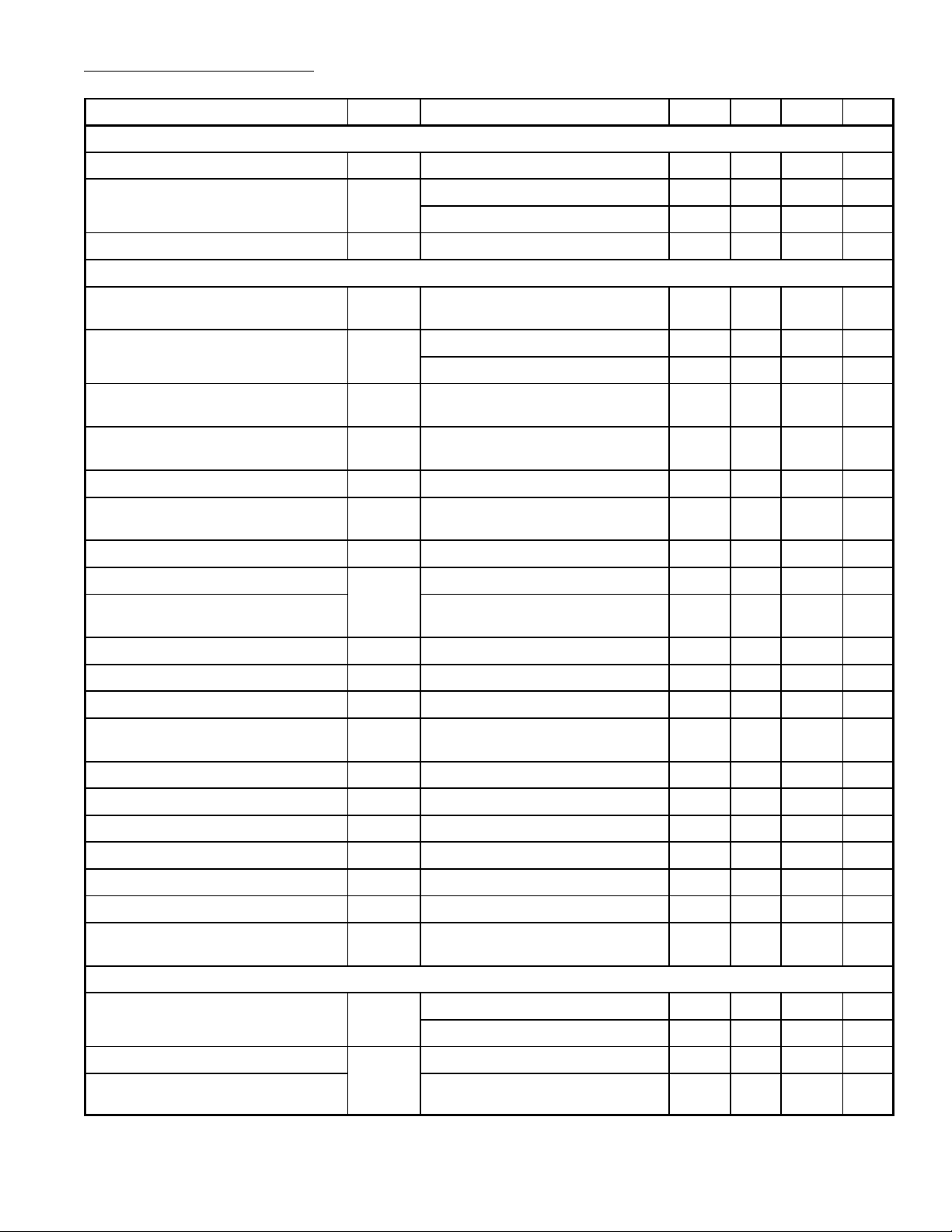

Electrical Characteristics: (VP = 17.5V, TA = +25°C, VFB = 45V, fi = 50Hz, I

unless otherwise specified)

Parameter Symbol Test Conditions Min Typ Max Unit

DC Supply

= 400µA

I(sb)

Operating Supply Voltage V

Flyback Supply Voltage V

P

FB

Note 1 V

Supply Current I

No Load, No Signal – 30 55 mA

P

Vertical Circuit

Output Voltage Swing (Scan) V

I

O

= 0.6mA

diff

= 3A

I

O

Linearity Error LE IO = 3A

IO = 50mA

Output Voltage Swing (Flyback)

– V

V

O(A)

O(B)

Forward Voltage of the Internal

Efficiency Diode (V

O(A)

– VFB)

Output Offset Current |IOS| I

Offset Voltage at the Input of the

Feedback Amplifier (V

I(fb)

– V

O(B)

DC Output Voltage V

Open Loop Voltage Gain (V

7–4/V1–2

Open Loop Voltage Gain

, V

(V

7–4/V9–4

Voltage Ratio V

= 0)

1–2

1–2/V9–4

Frequency Response (–3dB) f

Current Gain (IO/I

) G

diff

Current Gain Drift as a Function

V

V

∆VOS T I

O

DF

I

= 0.3mA, IO = 1.5A – 39 – V

diff

IO = –1.5A, I

= 0, I

diff

= 0 – – 72 µV/K

diff

)

= 0, Note 5 – 8 – V

Note 6, Note 7 – 80 – dB

) G

O(A)Idiff

VO

Note 6 – 80 – dB

V

R

res

Open Loop, Note 8 – 40 – Hz

I

∆GC T – – 10

of Temperature

9 – 25 V

V

P

P

, V

(P–P)

(P–P)

, Note 4 – 1 3 %

(P–P)

(P–P)

diff

= 50µA to 500µA – – 30 mA

I(sb)

= 1.8V

diff

, Note 4 – 1 3 %

= 0.3mA – – 1.5 V

(P–P)

,

19.8 – – V

– 50 V

– 60 V

– 0 – dB

– 5000 –

–4

K

Signal Bias Current I

Flyback Supply Current I

I(sb)

FB

During Scan – – 100 µA

50 400 500 µA

Power Supply Ripple Rejection PSRR Note 9 – 80 – dB

DC Input Voltage V

Common Mode Input Voltage V

Input Bias Current I

Common Mode Output Current I

I(DC)

I(CM)II(sb)

bias

O(CM)

I

I(sb)

∆I

I

diff

= 0 0 – 1.6 V

= 0 – 0.1 0.5 µA

I(sub)

= 300µA

(P–P)

, fi = 50Hz,

= 0

– 2.7 – V

– 0.2 – mA

Guard Circuit

Output Current I

Output Voltage on Pin8 V

O(guard)IO

Allowable Voltage on Pin8 Maximum Leakage Current =

O

Not Active, V

Active, V

O(guard)

O(guard)

= 0V – – 50 µA

= 3.6V 1.0 – 2.5 mA

= 100µA 4.6 – 5.5 V

– – 40 V

10µA

Loading...

Loading...