NTE NTE7049 Datasheet

NTE7049

Integrated Circuit

CMOS–Sync Generator for TV & Video

Processing Systems

Description:

The NTE7049 is a CMOS LSI sync generator in a 24–Lead DIP type package that produces all the timing signals required to drive a fully 2–to–1 interlaced 525–line 30–frame/second, or 625–line 25–frame/second TV

camera or video processing system. A complete sync waveform is produced which begins each field with six

serrated vertical sync pulses, preceded and followed by six half–width double frequency equalizing pulses.

The sync output is gated by the master clock to preserve horizontal phase continuity during the vertical interval.

The NTE7049 can be operated either in “genlock” mode, in which it is synchronized with a reference sync pulse

train from another TV camera, or in “stand–alone” mode, in which it is synchronized with a local on–chip crystal

oscillator (the crystal and two passive components are off chip). Also, the circuit can sense the presence or

absence of a reference sync pulse train and automatically select the “genlock” or “stand–alone” mode.

A frame sync pulse is produced at the beginning of every odd field. The vertical counter can be reset to either

the first equalizing pulse or the first vertical sync pulse of the vertical interval.

Features:

D Interlaced Composite Sync Output

D Automatic Genlock Capability

D Crystal Oscillator Operation

D 525 or 625 Line Operation

D Vertical Reset Option

D Wide Power Supply Operating Voltage: 4V to 15V

Applications:

D Cameras

D Monitors and Displays

D CATV

D Teletext

D Video Games

D Sync Restorer

D Video Service Instruments

Absolute Maximum Ratings:

DC Supply Voltage (Voltage referenced to VSS terminal), V

Input Voltage Range (All Inputs), V

DC Input Current (Any One Input), I

Power Dissipation (T

= –40° to +60°C), P

A

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

I

I

D

DD

Derate Linearly Above +60°C to 200mW 12mW/°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Device Dissipation Per Output Transistor (T

Operating Temperature Range, T

Storage Temperature Range, T

A

stg

= –40° to +85°C) 100mW. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A

Lead Temperature (During Soldering, 1/16 ±1/32 from case for 10sec), T

15V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

VSS ≤ VI ≤ V

DD

±10mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

500mW. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

–40° to +85°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

–65° to +150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

L

+265°C. . . . . . . . . . . . . . . . . . . . . .

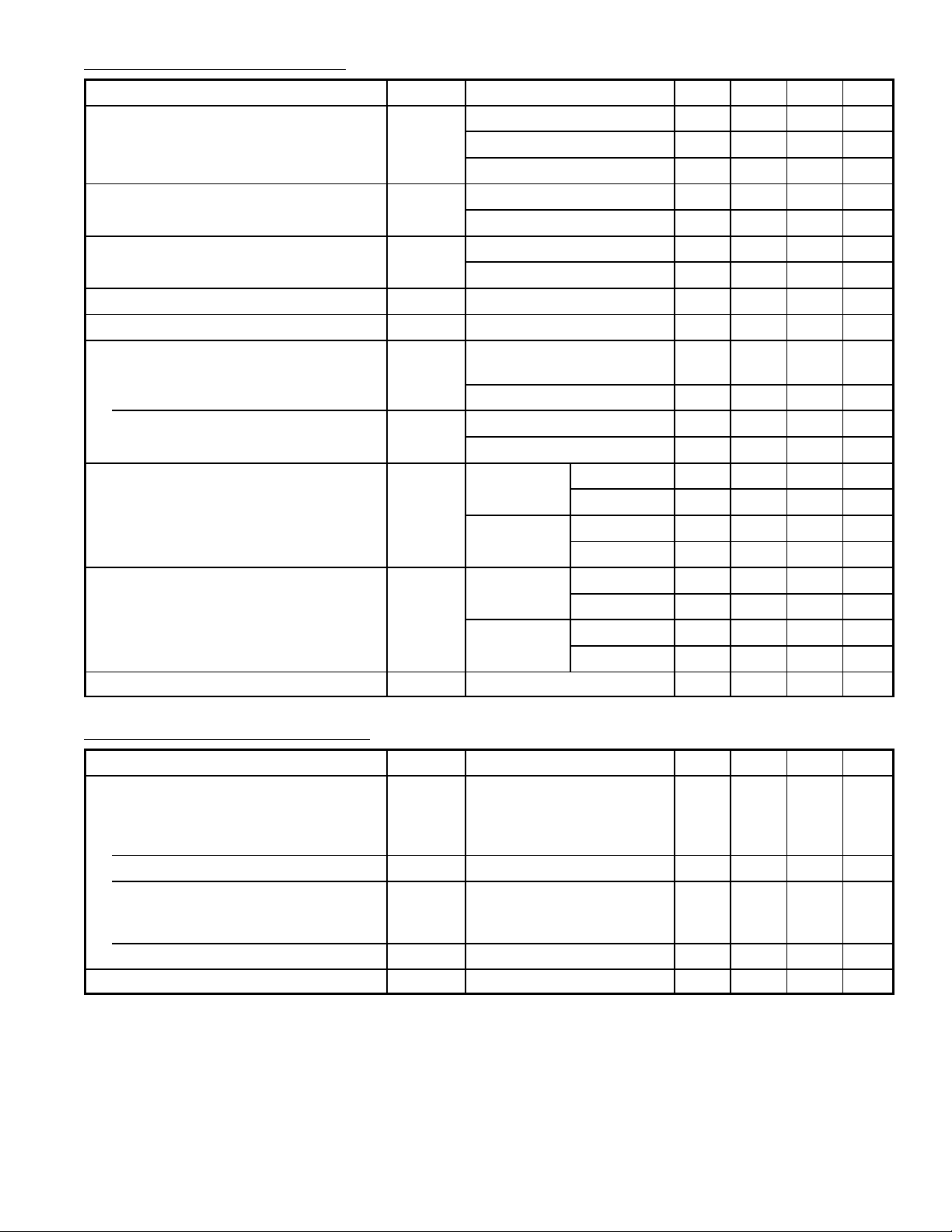

Static Electrical Characteristics: (TA = +25°C unless otherwise specified)

Parameter Symbol Test Conditions Min Typ Max Unit

Quiescent Device Current I

DD

VDD = 5V 0.5 0.75 1.0 mA

VDD = 10V 1.5 2.0 2.5 mA

VDD = 15V 3.0 4.0 5.0 mA

Output Voltage, Low Level V

OL

VDD = 5V – – 0.01 V

VDD = 10V – – 0.01 V

Output Voltage, High Level V

OH

VDD = 5V 4.99 – – V

VDD = 10V 9.99 – – V

Threshold Voltage, N–Channel VTHN ID = 10µA 1.0 1.5 2.6 V

Threshold Voltage, P–Channel VTHP ID = 10µA –1.0 –1.5 –2.6 V

Noise Immunity (Any Input)

Low Level

V

NL

VDD = 5V 1.5 2.25 – V

VDD = 10V 3.0 4.5 – V

High Level V

NH

VDD = 5V 1.5 2.25 – V

VDD = 10V 3.0 4.5 – V

Output SINK Current, N–Channel IDN VDD = 5V VO = 0.5V 80 160 – µA

VO = 5V 960 1920 – µA

VDD = 10V VO = 0.5V 200 400 – µA

VO = 10V 2400 4800 – µA

Output SOURCE Current, P–Channel IDP VDD = 5V VO = 4.5V 80 160 – µA

VO = 0V 960 1920 – µA

VDD = 10V VO = 9.5V 200 400 – µA

VO = 0V 2400 4800 – µA

Input Current (Each Input) I

I

– 10 – pA

Dynamic Electrical Characteristics: (TA = +25°C, CL = 15pF, Note 1 unless otherwise specified)

Parameter

Symbol Test Conditions Min Typ Max Unit

Output State

Propagation Delay Time

(50% to 50%)

Low–to–High Level

High–to–Low Level t

t

PLH

PHL

VDD = 5V – 40 80 ns

VDD = 10V – 20 40 ns

Transition Time

(10% to 90%)

Low–to–High

High–to–Low t

Input Capacity (Per Input) C

t

TLH

THL

VDD = 5V – 45 90 ns

VDD = 10V – 30 60 ns

I

– 5 – pF

Note 1. Typical temperature coefficient for all values of VDD = 0.3%/°C.

Loading...

Loading...