NTE1690

Integrated Circuit

Telephone DTMF Dialer

Description:

The NTE1690 is a low threshold voltage, field–implanted, metal gate CMOS integrated circuit in a

16–Lead DIP type package. This device interfaces directly to a standard telephone keypad and generates all dual tone multi–frequency pairs required in tone dialing systems. The tone synthesizers

are locked to an on–chip reference oscillator using an inexpensive 3.579545MHz crystal for high tone

accuracy. The crystal and an output load resistor are the only external components required for tone

generation. A MUTE

vided.

Features:

D 3V to 10V Operation When Generating Tones

D 2V Operation of Keyscan and MUTE

D Static Sensing of Key Closures or Logic Inputs

D On–Chip 3.579545MHz Crystal–Controlled Oscillator

D Output Amplitudes Proportional to Supply Voltage

D High Group Pre–Emphasis

D Low Harmonic Distortion

D Open Emitter–Follower Low–Impedance Output

D SINGLE TONE INHIBIT

OUT logic signal, which changes state when any key is depressed is also pro-

Logic

Pin

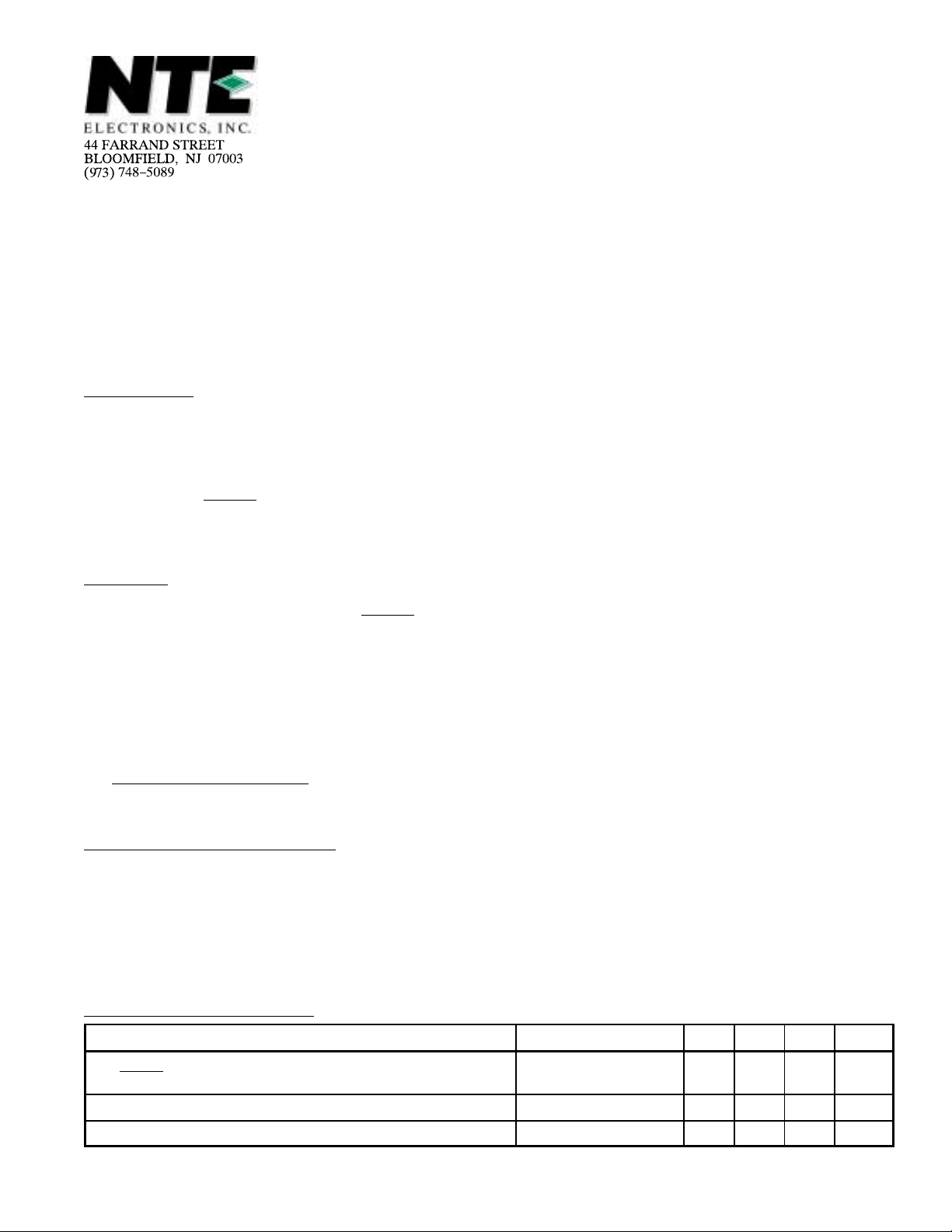

Absolute Maximum Ratings:

Supply Voltage (VDD – V

Maximum Voltage at Any Pin V

Power Dissipation, P

D

Operating Temperature Range, T

Storage Temperature Range, T

Electrical Characteristics:

Minimum Supply Voltage for Keysense and

MUTE

Logic Functions

Operating Current, Idle RL = 10kΩ – 20 – µA

Operating Current, Generating Tones VO = 5V – 2 – mA

)

SS

+0.3V to VSS–0.3V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DD

500mW. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

opr

stg

–30° to +60°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

–55° to +150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

(–30°C < TA < +60°C, 3V < VDD < 10V unless otherwise specified)

Parameter Test Conditions Min Typ Max Unit

– – 2 V

15V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

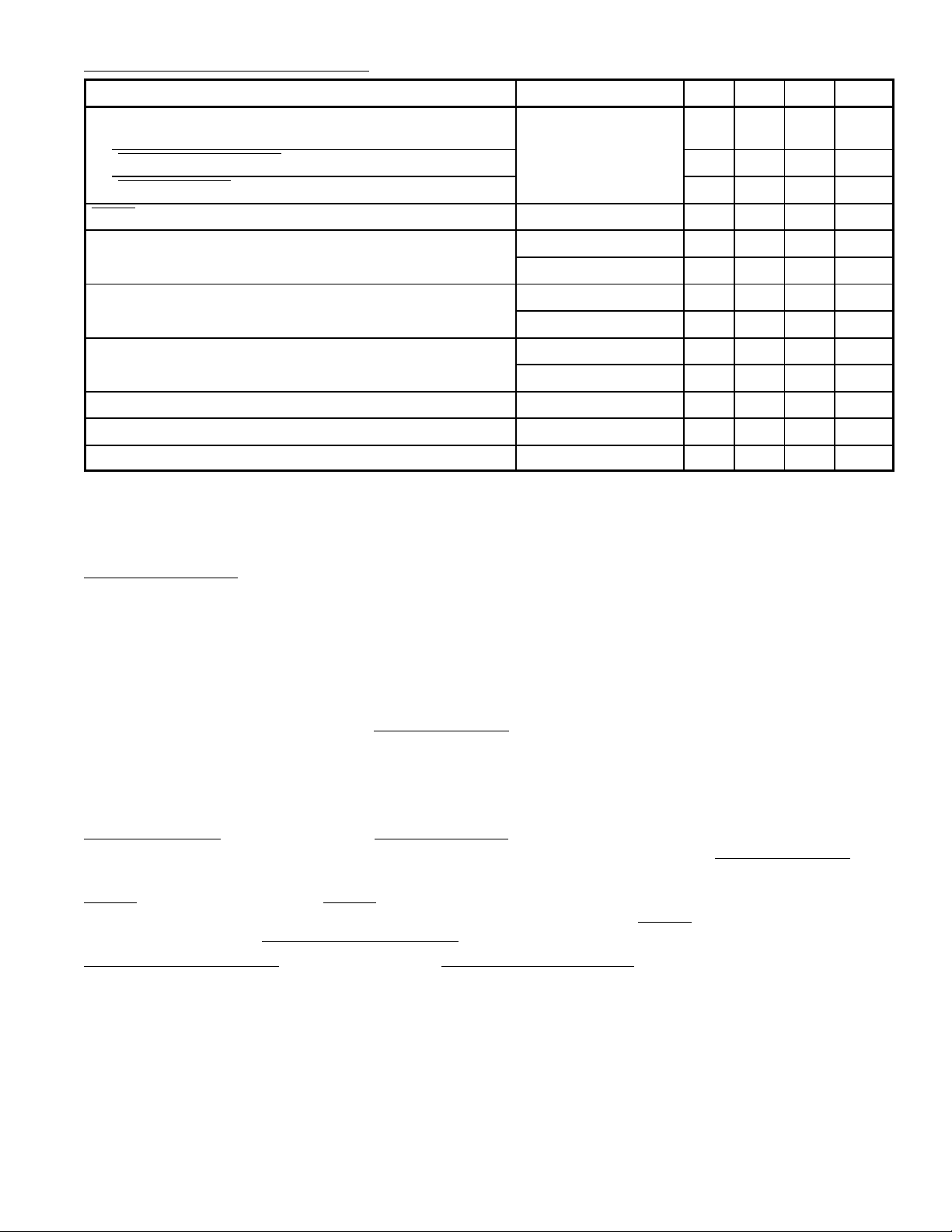

Electrical Characteristics (Cont’d): (–30°C < TA < +60°C, 3V < VDD < 10V unless othewise specified)

Parameter Test Conditions Min Typ Max Unit

Input Resistors

COLUMN and ROW (Pull–Up)

SINGLE TONE INHIBIT (Pull–Down) – 50 – kΩ

TONE DISABLE (Pull–Up) – 50 – kΩ

MUTE OUT Sink Current (COLUMN and ROW Active) VDD = 3V, VO = 0.5V 0.5 – – mA

– 40 – kΩ

Output Amplitudes, Low Group RL = 240Ω, VDD = 3V – 250 – mV

RL = 240Ω, VDD = 10V – 850 – mV

Output Amplitudes, High Group RL = 240Ω, VDD = 3V – 315 – mV

RL = 240Ω, VDD = 10V – 1000 – mV

Mean Output DC Offset VDD = 3V – 1.2 – V

VDD = 10V – 4.2 – V

High Group Pre–Emphasis 2.4 2.7 3.0 dB

Dual Tone/Harmonic Distortion Ratio 1MHz Bandwidth 22 – – dB

Start–Up Time (90% Amplitude) – 3 5 ms

rms

rms

rms

rms

Note 1. Crystal Specification: Parallel Resonant 3.579545MHz, RS ≤ 150Ω, L = 100mH, C0 = 5pF,

C

= 0.02pf.

1

Pin Descriptions:

VDD (Pin1): This is the positive voltage supply to the device, referenced to VSS. The collector of the

TONE OUT transistor is connected to this pin.

(Pin6): This is the negative voltage supply.

V

SS

OSCILLA T OR (Pin7 and Pin8): All tone generation timing is derived from the on–chip oscillator cir-

cuit. A low–cost 3.579545MHz A–cut crystal (NTSC TV color–burst) is needed between Pin7 and

Pin8. Load capacitors and feedback resistor are included on–chip for good start–up and stability.

The oscillator stops when column inputs are sensed with no valid input having been detected. The

oscillator is also stopped when the TONE DISABLE

input is pulled to logic low.

Row and Column Inputs (Pins 3, 4, 5, 9, 11, 12, 13, 14): When no key is pushed, pull–up resistors

are active on row and column inputs. A key closure is recognized when a single row and a single

column are connected to V

, which starts the oscillator and initiates tone generation. Negative–true

SS

logic signals simulating key closures can also be used.

TONE DISABLE

input is open or at logic high, the normal tone output mode will occur. When TONE DISABLE

Input (Pin2): The TONE DISABLE input has an internal pull–up resistor . When this

input

is at logic low , the device will be in the inactive mode, TONE OUTPUT will be at an open circuit state.

MUTE

V

Output (Pin10): The MUTE output is an open–drain N–channel device that sinks current to

with any key input and is open when no key input is sensed. The MUTE output will switch regard-

SS

less o the state of he SINGLE TONE INHIBIT input.

SINGLE TONE INHIBIT

Input (Pin15): The SINGLE TONE INHIBIT input is used to inhibit the gener-

ation of other than valid tone pairs due to multiple row–column closures. It has a pull–down resistor

to V

will now result in no tone, with all other functions operating normally. When tied to V

, and when left open or tied to VSS any input condition that would normally result in a single tone

SS

, single or dual

DD

tones may be generated (See Table II).

TONE OUT (Pin16): This output is the open emitter of an NPN transistor, the collector of which is

connected to V

. When an external load resistor is connected from TONE OUT to VSS, the output

DD

voltage on this pin is the sum of the high and low group sine–waves superimposed on a DC offset.

When not generating tones, this output transistor is turned OFF to minimize the device idle current.

Loading...

Loading...