NTE1167

Integrated Circuit

Phase Lock Loop (PLL) Frequency Synthesizer

Description:

The NTE1167 consists of a crystal oscillator, 10 bit divider, phase comparator, and a programmable

divide–by–N 9–bit counter in a single CMOS 16–Lead DIP type integrated circuit.

This device is designed for use in frequency synthesizers and phase locked loop applications for CB

transceivers since it includes a reference frequency selector pin.

Absolute Maximum Ratings:

Supply Voltage, V

Input Voltage, V

Power Dissipation, P

– V

DD

IN

SS

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

D

Operating Temperature Range, T

Storage Temperature Range, T

Lead Temperature (During Soldering, 5sec Max), T

Electrical Characteristics:

(TA = +25°C unless otherwise specified)

–0.3V to +7V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

VSS ≤ VIN ≤ V

opr

stg

L

–30° to +70°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

–55° to +125°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

(VDD – VSS = 6V, –30° ≤ TA ≤ +70°C, fin Qin = 1 0.24MHz unless otherwise

specified)

Parameter Symbol Test Conditions Min Typ Max Unit

Input Voltage (All Inputs)

Low Level

High Level V

Pull–Up Resistance RUP F

Pull–Down Resistance RDN P0 – P

Supply Current I

Output Voltage

High Level

Low Level VOL LD IOL = 0.1mA 0 – 0.5 V

Output Current

High Level

Low Level I

Output Voltage VIF F

Max Input Frequency fIN Max Q

Max Free Running Frequency fFR Max F

Operating Voltage V

V

IL

IH

DD

Note 1 – – 0.5 V

5.5 – – V

S

8

VDD = 5.5V, Vin Fin = 1V

P–P

,

– 2.0 0 MΩ

15 75 – kΩ

– 5.0 9.0 mA

Exclude sink current of preset pin

VOH LD IOH = 0.1mA 5.5 – – V

I

H D

SAT

L D

SAT

in

VIF F

S

VIF P0 – P

fIN Max F

DD

VO = 0V 400 – – µA

O

VO = 0V 400 – – µA

O

VDD = 5V 1.7 2.2 2.8 V

5.5 – – V

8

in

in

IN

– – 0.5 V

11 – – MHz

3.3 – – MHz

3.5 – – MHz

5.0 – 6.5 V

DD

250mW. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

+260°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Note 1. All inputs refers to pins P0 to P8, FS, Fin, and Qin. This parameter defins their input levels

at DC coupling.

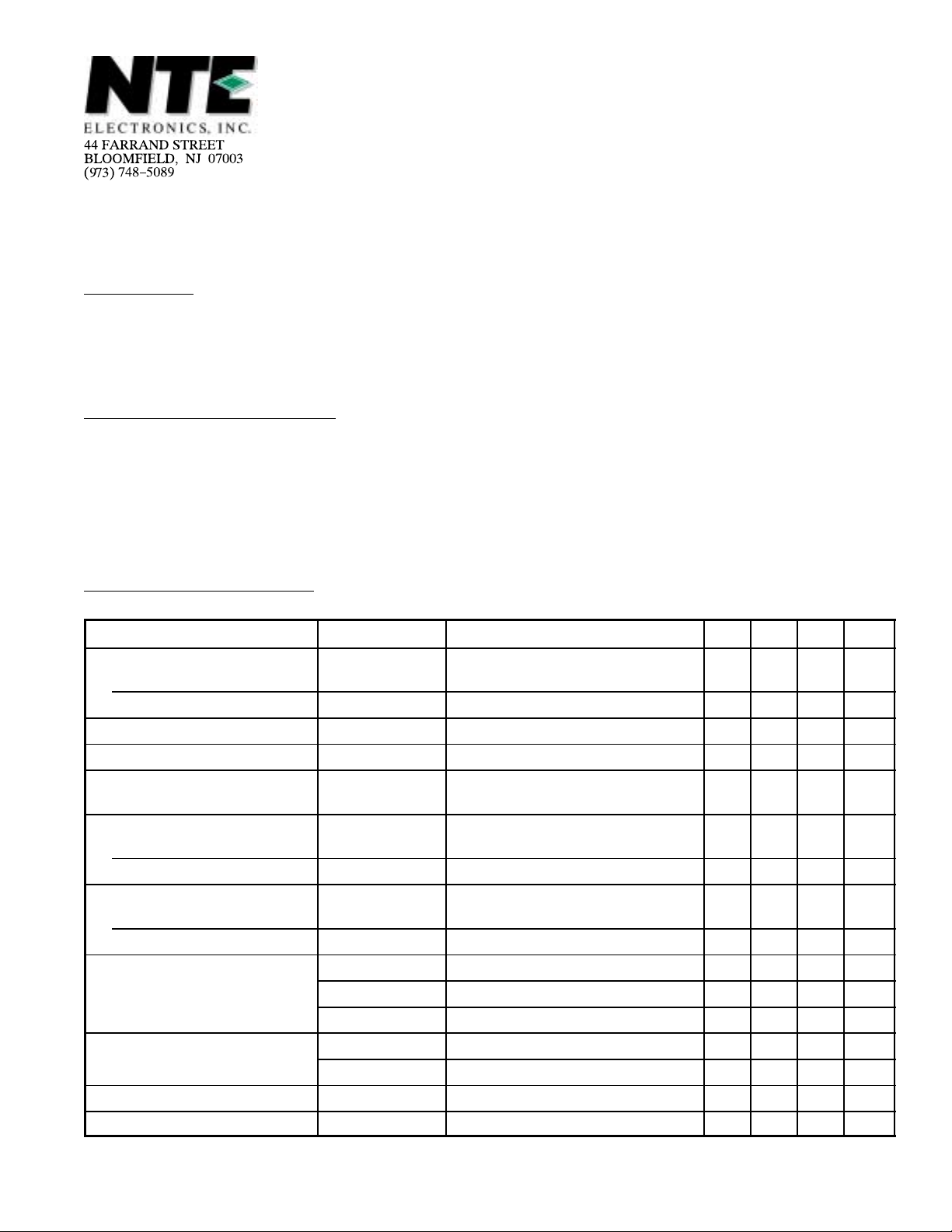

Pin Connection Diagram

V

DD

P

IN

R

IN

N.C.

D

L

P

P

1

2

3

4

5

O

6

D

7

8

8 9

7

16

15

14

13

12

11

10

V

P

P

P

P

P

P

P

SS

0

1

2

3

4

5

6

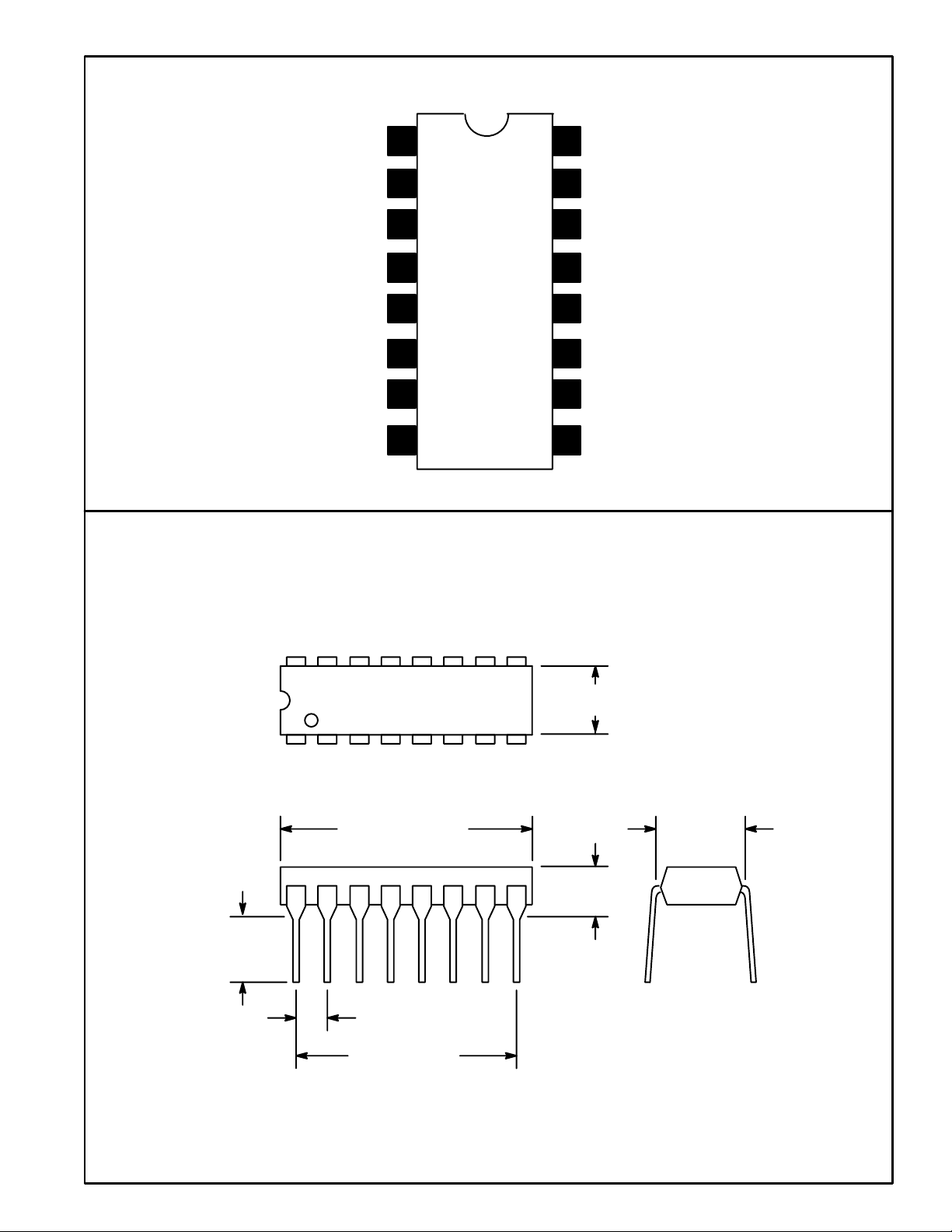

.245

(6.22)

Min

16 9

.260 (6.6) Max

18

.785 (19.9) Max

.200 (5.08)

Max

.100 (2.54)

.700 (17.7)

.300 (7.62)

Loading...

Loading...