NSC LP3927ILQX-AJ, LP3927ILQX-AH, LP3927ILQ-AH Datasheet

LP3927

Cellular/PCS System Power Management IC

LP3927 Cellular/PCS System Power Management IC

August 2002

General Description

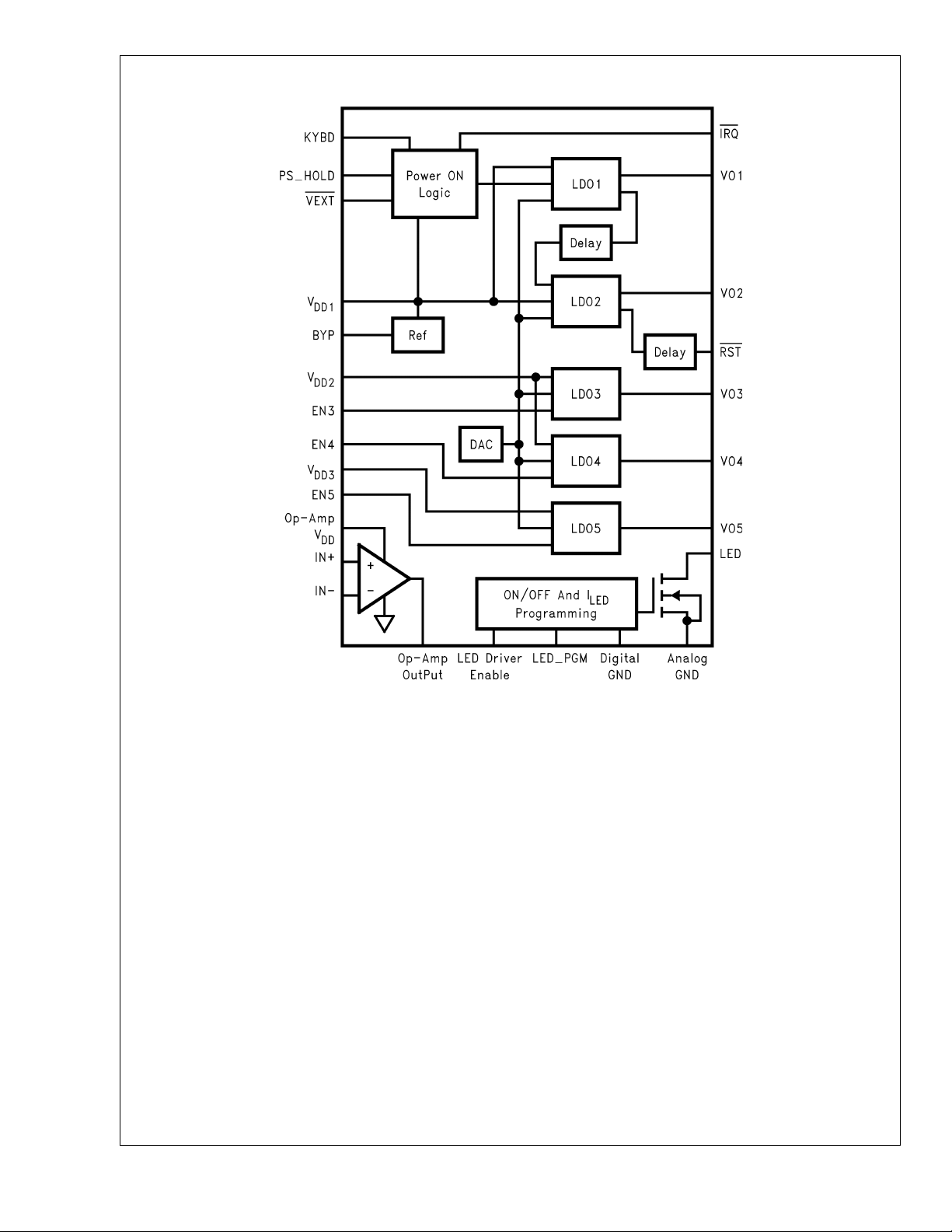

The LP3927 system power management IC is designed for

cellular/PCS handsets as well as other portable systems that

require intelligent power management. Each device contains

five low-dropout linear regulators (LDO’s), a reset timer, a

power-up control logic, a general-purpose open drain output

that can be used to light LEDs, and a CMOS rail-to-rail

input/output operational amplifier.

Each linear regulator features an extremely low dropout

voltage of 100 mV (typ) at maximum output current. LDO1

and LDO2 are powered on and off by either the KYBD or the

VEXT pin. LDO3, LDO4 and LDO5 each have its independent enable pin. LDO1 and LDO4 are rated at 150 mA each,

LDO2 and LDO5 are rated at 200 mA each and LDO3 is

rated at 100 mA. All LDO’s are optimized for low noise and

high isolation.

The open drain output current sink can be programmed up to

150 mA by using an external low cost resistor.

A single supply, low voltage operational amplifier has rail to

rail input and output with 600 kHz of gain-bandwidth product.

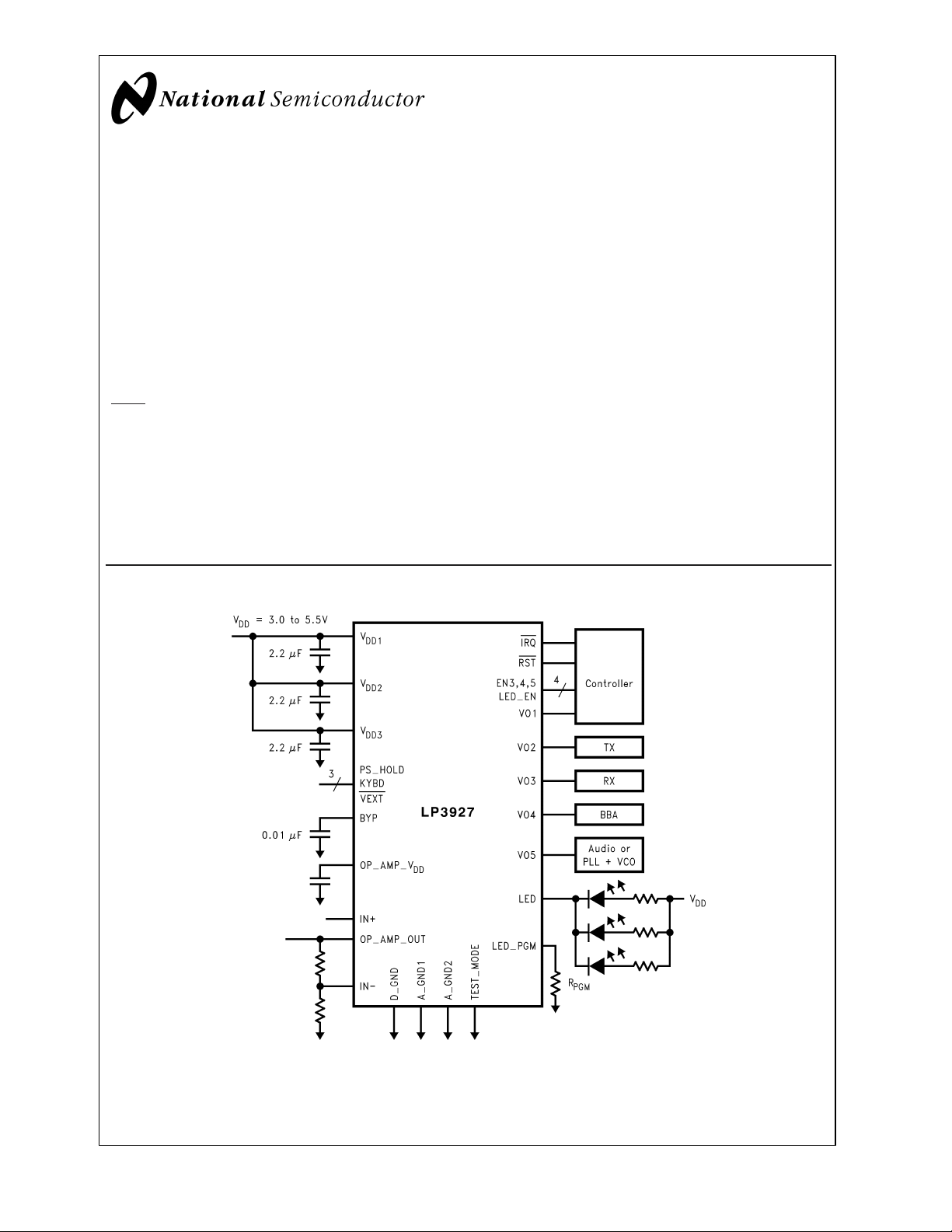

Typical Application Circuit

Key Specifications

n 3.0V to 5.5V Input Voltage Range

n Two 200 mA, Two 150 mA and One 100 mA LDO’s

n 100 mV typ Dropout Voltage

n 150 mA General-Purpose Open-drain programmable

current sink for back light LED

n Low Voltage Rail to Rail Input/Output Operational

Amplifier

n 28 pin LLP package

@

I

MAX

Applications

n Cellular/PCS handsets

n PDA’s, Palmtops, and portable terminals

n Single–Cell Li+ Systems

n 2- or 3- Cell NiMH, NiCd or Alkaline System

20037901

V

DD1,VDD2

© 2002 National Semiconductor Corporation DS200379 www.national.com

and V

must be tied together externally. Collectively called VDD.

DD3

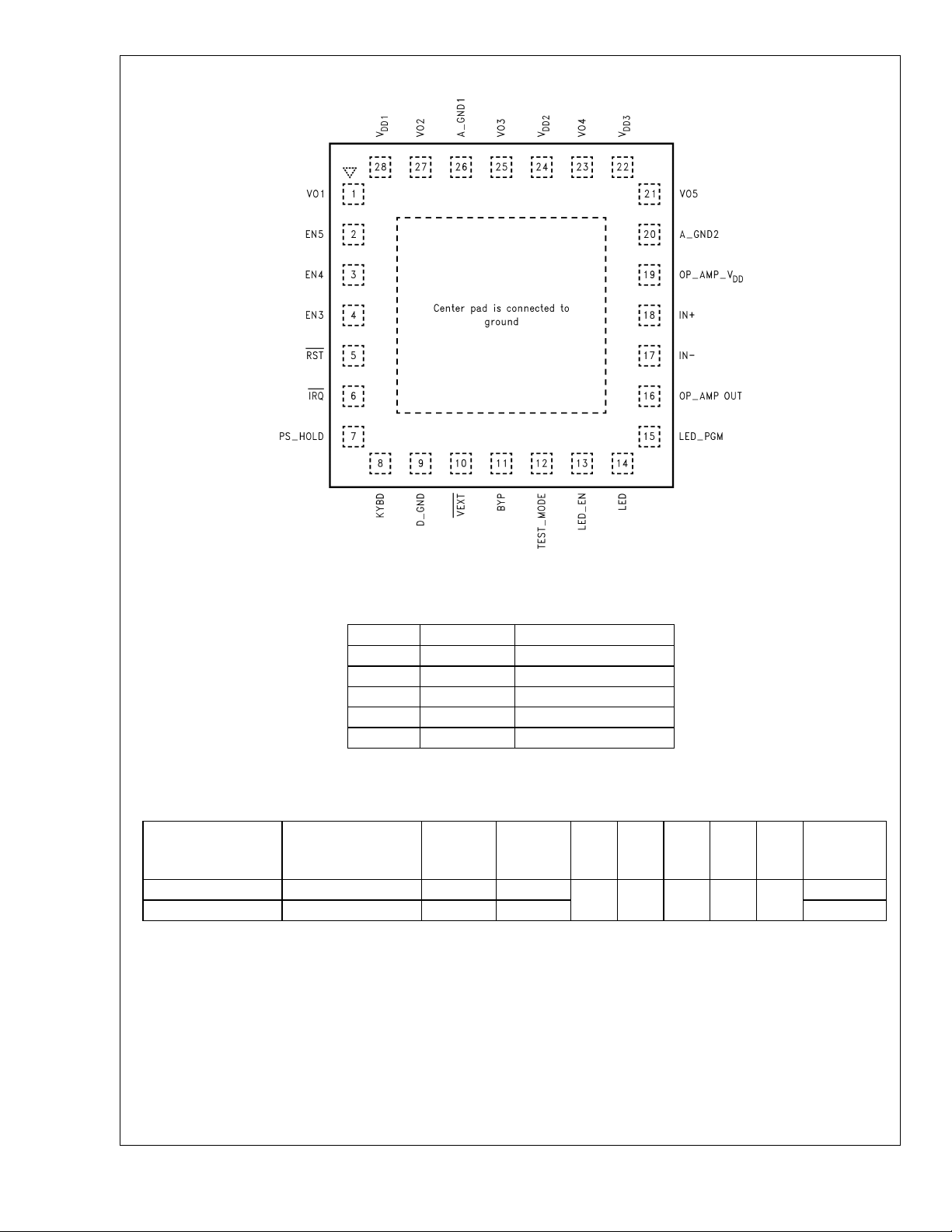

LP3927 Pin Out Diagram (Top View)

LP3927

20037902

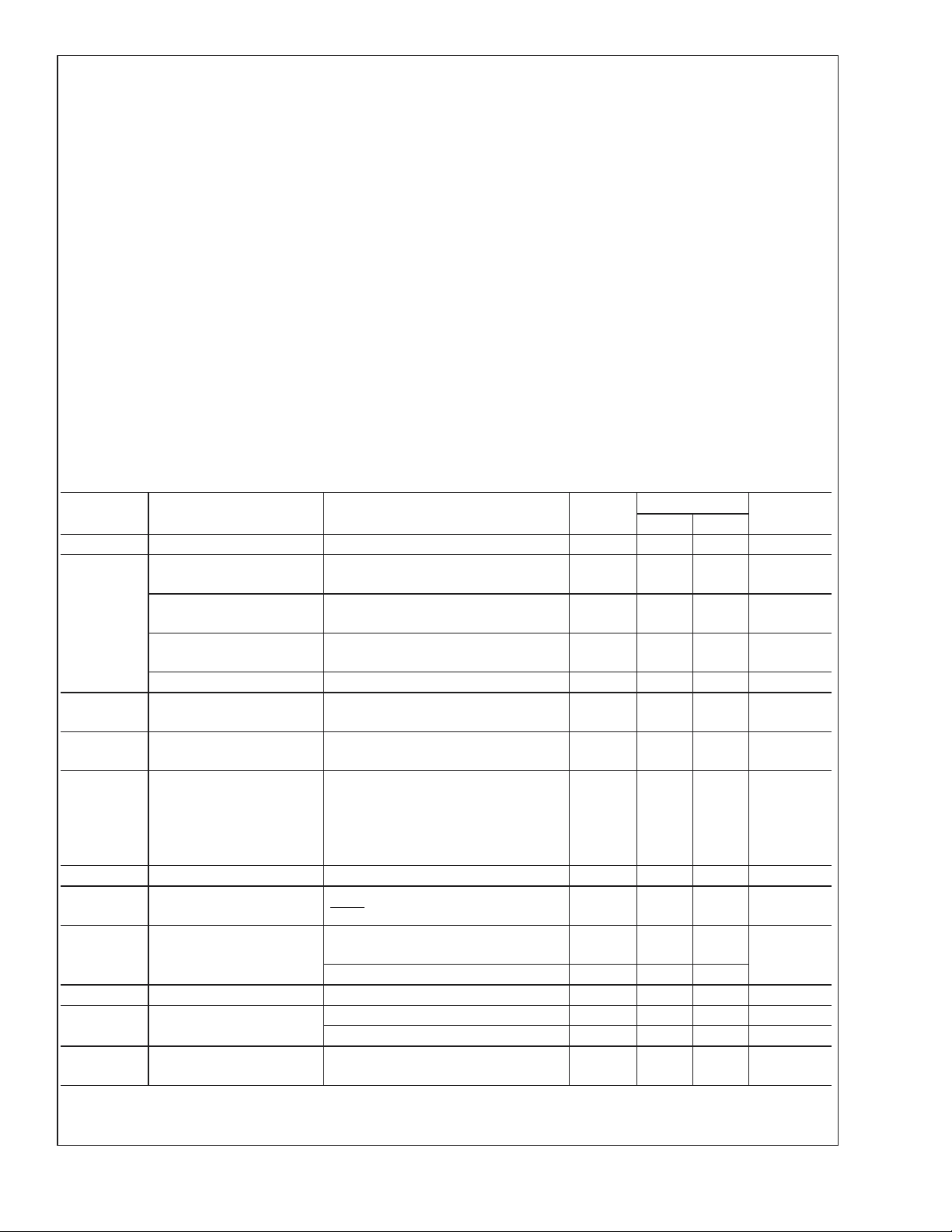

Output Current Rating and Voltage Options

I

(mA) Voltage Options (V)

MAX

LDO1 150 1.8, 1.9, 2.5, 2.6*, 2.7

LDO2 200 1.8, 2.85*, 2.9, 3.0

LDO3 100 2.7, 2.8, 2.9

LDO4 150 2.7, 2.8, 2.9

LDO5 200 2.7, 2.8, 2.9, 3.0

*

denotes the voltage options that are available currently. For other options, please contact the

National Semiconductor factory sales office/distributors for availability and specifications.

*

, 3.0

*

, 3.0

*

Ordering Information

LP3927 Supplied as

1000 Units, tape and

reel

LP3927ILQ-AH LP3927ILQX-AH X

LP3927ILQ-AJ LP3927ILQX-AJ X 3927AJ

For LDO delay options, please refer to Electrical Characteristics Table.

LP3927 Supplied as

4500 Units, tape and

reel

Standard

LDO delay

Optional

LDO delay

VO1

VO2

VO3

VO4

VO5

(V)

(V)

(V)

2.6 2.85 2.9 2.9 3.0

(V)

(V)

TOP

MARKING

3927AH

www.national.com 2

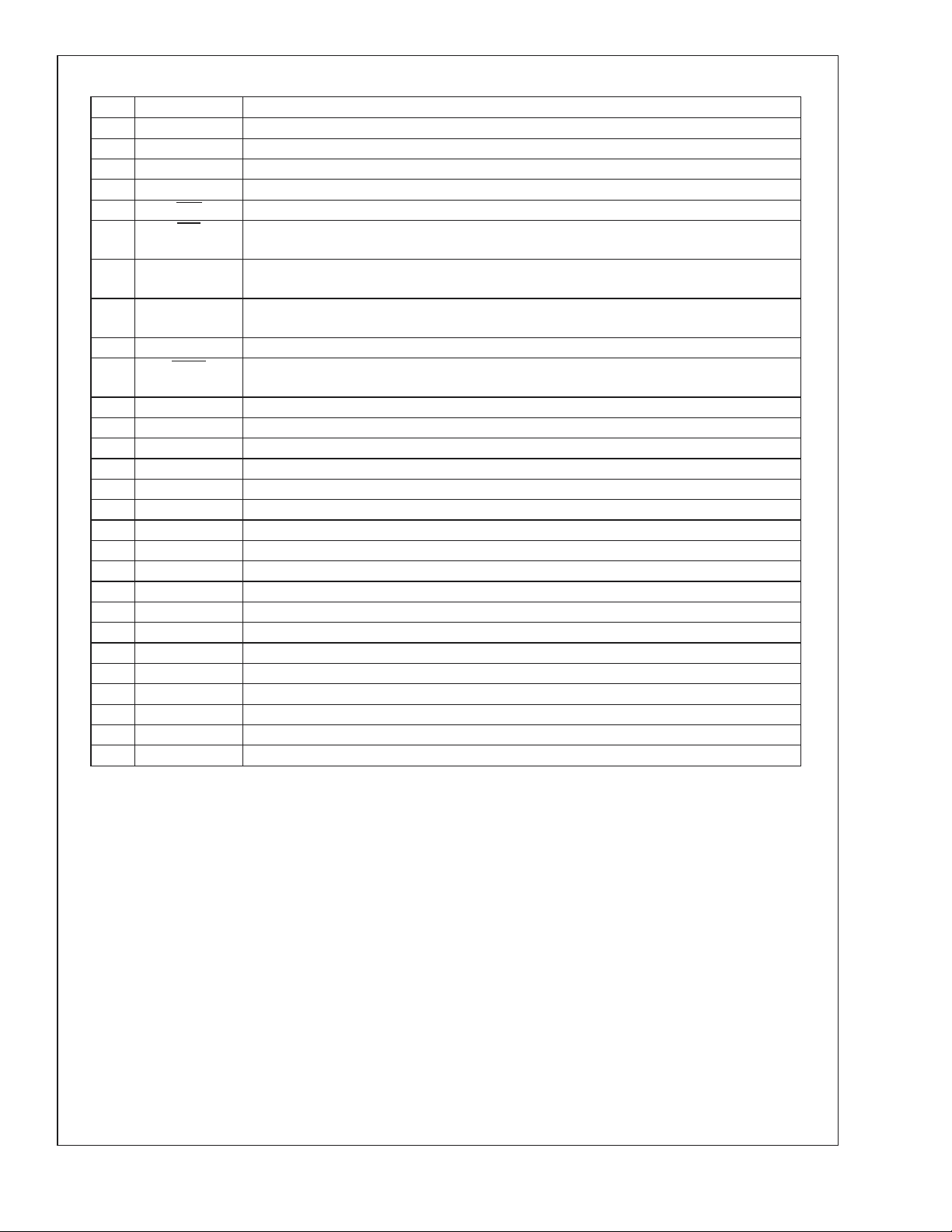

Pin Description

Pin Name Functional Description

1 VO1 150 mA, LDO1 output pin.

2 EN5 LDO5 enable input.

3 EN4 LDO4 enable input.

4 EN3 LDO3 enable input.

5 RST

6 IRQ

7 PS_HOLD Input from the processor to the LP3927. A HIGH indicates a steady supply of power is

8 KYBD An active high input signal indicating the keyboard “On/Off” button has been asserted. Refer

9 D_GND Digital ground, used primarily for the digital and DAC circuits.

10 VEXT

11 BYP Reference bypass pin.

12 TEST_MODE Pin used for production testing, factory use only. This pin should be grounded in applications.

13 LED_EN LED driver enable input.

14 LED LED driver, drain connection of the LED drive MOSFET.

15 LED_PGM LED drive current programming pin.

16 OP_AMP_OUT Operational amplifier output pin.

17 IN− − input of the Op-Amp.

18 IN+ + input of the Op-Amp.

19 OP_AMP_V

20 A_GND2 Ground for analog.

21 VO5 200 mA, LDO5 output pin.

22 V

DD3

23 VO4 150 mA, LDO4 output pin.

24 V

DD2

25 VO3 100 mA, LDO3 output pin.

26 A_GND1 Ground for analog.

27 VO2 200 mA, LDO2 output pin.

28 V

DD1

Externally pulled high, open drain output to processor/memory reset.

Externally pulled high, open drain output to processor interrupt indicating KYBD has gone

high.

granted. Refer to ’Application Hints’ section for more detail.

to ’Application Hints’ section for more detail.

Active low input indicating a battery charger insertion Refer to ’Application Hints’ section for

more detail.

Power supply pin for Op-Amp.

DD

Input power pin for LDO5. V

DD1,VDD2

Input power pin for LDO3 and LDO4. V

Input power pin for LDO1 and LDO2. V

and V

DD3

DD1,VDD2

DD1,VDD2

must be tied together externally.

and V

and V

must be tied together externally.

DD3

must be tied together externally.

DD3

LP3927

www.national.com3

Functional Block Diagram

LP3927

20037903

www.national.com 4

LP3927

Absolute Maximum Ratings (Notes 1,

All other pins 2 kV

2)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

All pins except LED_PGM,

BYP, op amp’s inputs & output −0.3V to 6.0V

OP_AMP_OUT, IN-, IN+ -0.3V to 5.5V

GND to GND SLUG

±

0.3V

Junction Temperature 150˚C

Storage Information −65˚C to 150˚C

Soldering Temperature

Pad Temperature 235˚C

Maximum Power Dissipation (Note 3) 2.6W

Operating Ratings (Notes 1, 2)

V

DD1,VDD2,VDD3

EN3, EN4, EN5 −0.3V to (V

C

:

OUT

Capacitance 1.0 µF to 20.0 µF

ESR 0.005Ω to 0.5Ω

Junction Temperature −40˚C to 125˚C

Operating Temperature −40˚C to 85˚C

Thermal Resistance (Note 5)

θ

(LLP28) 30.8˚C/W

JA

Maximum Power Dissipation (Note 6) 1.78W

, KYBD, OP_AMP_V

ESD (Note 4):

KYBD 4 kV

Electrical Characteristics, LDO’s

Unless otherwise noted, VDD=V

OUT(target)

0.1 µF. Typical values and limits appearing in normal type apply for T

the entire junction temperature range for operation, −40˚C to +85˚C. (Notes 7, 8)

Symbol Parameter Conditions Typical

V

∆V

DD

OUT

Input Voltage Range V

Output Voltage Tolerance I

Load Regulation I

Line Regulation V

Total Accuracy Error −3.5 +3.5 %

V

IN-VOUT

e

N

Dropout Voltage I

Output Noise Voltage I

PSRR Power Supply Ripple

Rejection Ratio

Cross Talk (Note 10) 30 dB

I

I

I

C

R

Q

GND

SC

OUT

SHUNT

Quiescent Current I

Ground Current I

Short Circuit Current Limit V

Output Capacitor Capacitance 120 µF

VO2-VO5Output Shunt

Resistor

+ 0.7V, CIN(V

DD1,VDD2,VDD3

OUT=IMAX

V

DD

OUT

V

DD

DD=VOUT(target)

I

OUT=IMAX

OUT=IMAX

OUT

/2,

= 3.7V

= 100 µA to I

= 3.7V

/2

= 100 µA,

DD1,VDD2,VDD3

,KYBD 3.7 3 5.5 V

,

MAX

+0.7V to 5.5V

(Note 9) 100 170

) = 4.7 µF, C

= 25˚C. Limits appearing in boldface type apply over

J

OUT

10 Hz ≤ f ≤ 100 kHz 27 µV

CIN= 2.2µF, I

OUT=IMAX

,

f = 100 Hz

f=1kHz

f=10kHz

f = 100 kHz

= 0, PS_HOLD = KYBD = 0

OUT

VEXT = V

OUT1=IOUT2

DD

= 1 mA,

LDO3, LDO4, LDO5 OFF

I

OUT1,IOUT2,IOUT3,IOUT4,IOUT5=IMAX

=0V 400 %ofI

OUT

ESR 5 500 mΩ

3.0V to 5.5V

DD

+ 0.3V)

DD

(VO1 to VO5) = 2.2 µF, C

Limit

Min Max

byp

Units

−2 +2 %

−2 +2 %

−40 +40 mV

mV

200

45

45

dB

30

10

5

µA

8

100 200 µA

400 950

70 200 Ω

=

rms

MAX

www.national.com5

Loading...

Loading...