NSC LP2995MX, LP2995MRX, LP2995LQX, LP2995LQ, LP2995MR Datasheet

LP2995

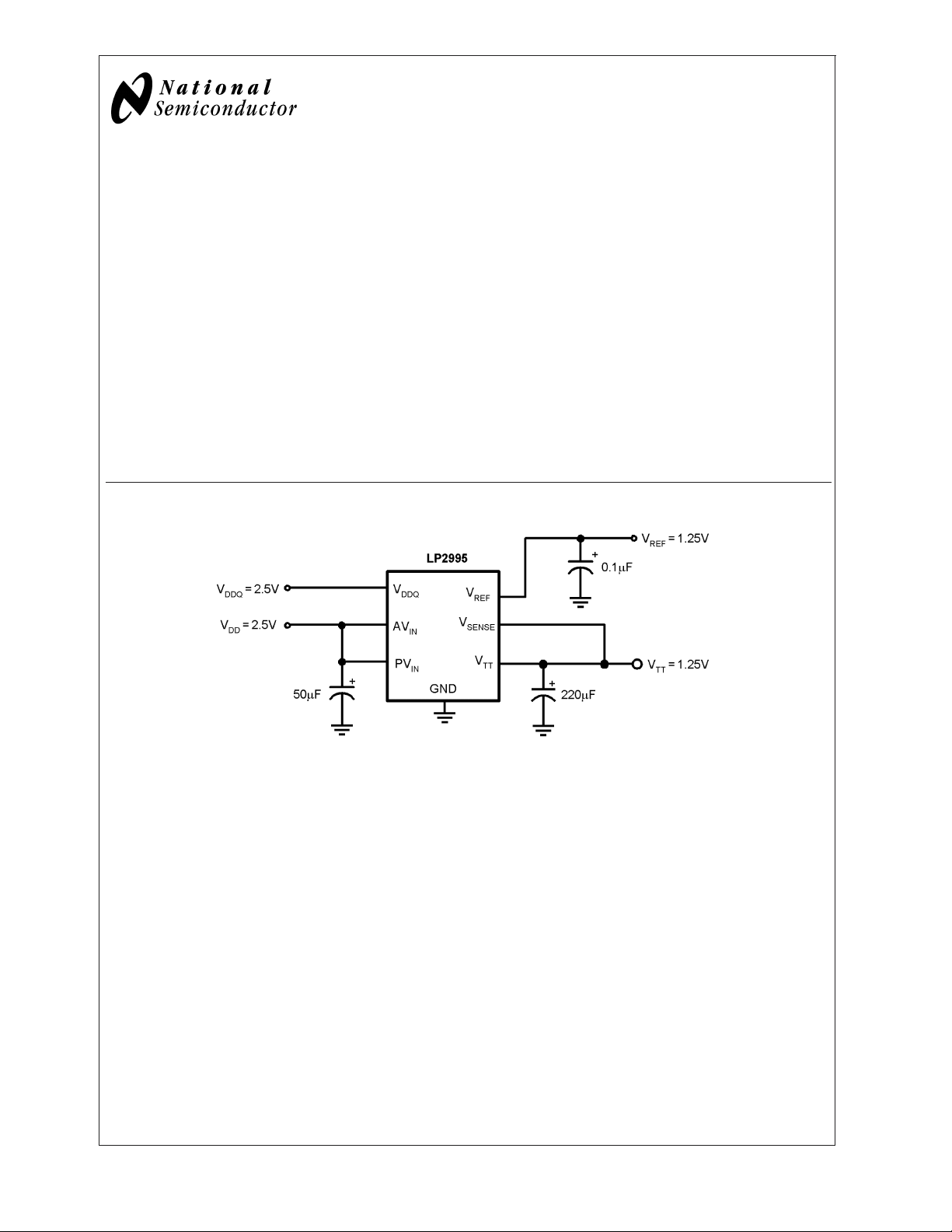

DDR Termination Regulator

LP2995 DDR Termination Regulator

July 2003

General Description

The LP2995 linear regulator is designed to meet the JEDEC

SSTL-2 and SSTL-3 specifications for termination of DDRSDRAM. The device contains a high-speed operational amplifier to provide excellent response to load transients. The

output stage prevents shoot through while delivering 1.5A

continuous current and transient peaks up to 3A in the

application as required for DDR-SDRAM termination. The

LP2995 also incorporates a V

load regulation and a V

chipset and DDR DIMMS.

Patents Pending

REF

pin to provide superior

SENSE

output as a reference for the

Typical Application Circuit

Features

n Low output voltage offset

n Works with +5v, +3.3v and 2.5v rails

n Source and sink current

n Low external component count

n No external resistors required

n Linear topology

n Available in SO-8, PSOP-8 or LLP-16 packages

n Low cost and easy to use

Applications

n DDR Termination Voltage

n SSTL-2

n SSTL-3

20039302

© 2003 National Semiconductor Corporation DS200393 www.national.com

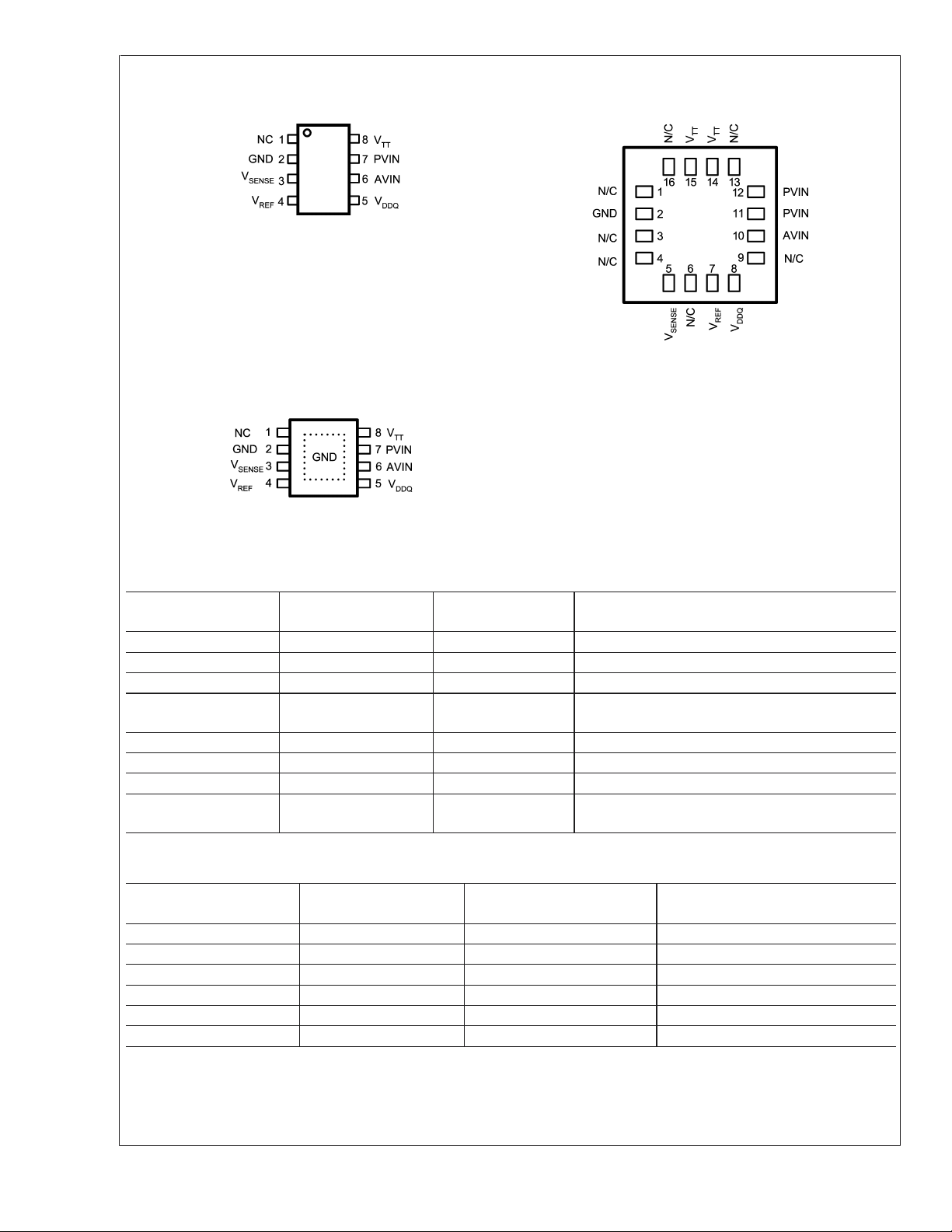

Connection Diagrams

LP2995

SO-8 (M08A) Package LQA- 16 Package

PSOP-8 (MRA08A) Package

Pin Description

SO-8 Pin or

PSOP-8 Pin

1 1,3,4,6,9, 13,16 NC No internal connection. Can be used for vias.

2 2 GND Ground.

3 5 VSENSE Feedback pin for regulating VTT.

4 7 VREF Buffered internal reference voltage of

5 8 VDDQ Input for internal reference equal to VDDQ/2.

6 10 AVIN Analog input pin.

7 11, 12 PVIN Power input pin.

8 14, 15 VTT Output voltage for connection to termination

Top View

20039320

20039304

Top View

20039350

Top View

LLP Pin Name Function

VDDQ/2.

resistors.

Ordering Information

Order Number Package Type

LP2995M SO-8 M08A 95 Units per Rail

LP2995MX SO-8 M08A 2500 Units Tape and Reel

LP2995MR PSOP-8 MRA08A 95 Units per Rail

LP2995MRX PSOP-8 MRA08A 2500 Units Tape and Reel

LP2995LQ LLP-16 LQA16A 1000 Units Tape and Reel

LP2995LQX LLP-16 LQA16A 4500 Units Tape and Reel

www.national.com 2

NSC Package

Drawing

Supplied As

LP2995

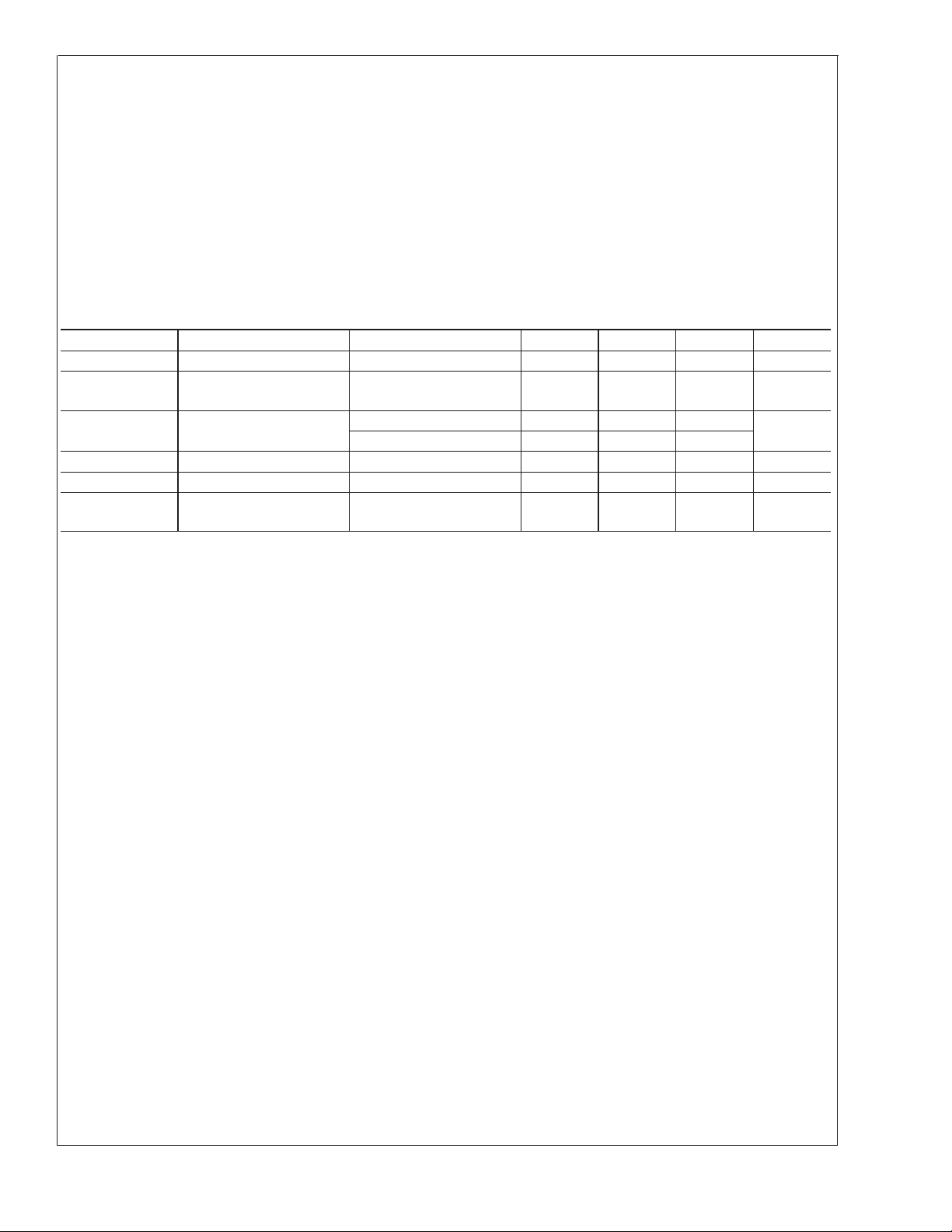

Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required,

Lead Temperature (Soldering, 10 sec) 260˚C

ESD Rating (Note 7) 1kV

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Operating Range

PVIN, AVIN, VDDQ to GND −0.3V to +6V

Storage Temp. Range −65˚C to +150˚C

Junction Temperature 150˚C

SO-8 Thermal Resistance (θ

LLP-16 Thermal Resistance (θ

) 151˚C/W

JA

) 51˚C/W

JA

Electrical Characteristics Specifications with standard typeface are for T

type apply over the full Operating Temperature Range (T

AVIN = PVIN = 2.5V, VDDQ = 2.5V (Note 6).

Symbol Parameter Conditions Min Typ Max Units

V

REF

VOS

VTT

V

Voltage I

REF

VTTOutput Voltage Offset I

REF_OUT

OUT

(Note 2)

∆V

Z

Z

I

q

TT/VTT

VREF

VDDQ

Load Regulation

(Note 3)

V

Output Impedance I

REF

VDDQ Input Impedance 100 kΩ

Quiescent Current I

I

I

OUT

OUT

REF

OUT

(Note 4)

Note 1: Absolute maximum ratings indicate limits beyond which damage to the device may occur. Operating range indicates conditions for which the device is

intended to be functional, but does not guarantee specific performance limits. For guaranteed specifications and test conditions see Electrical Characteristics. The

guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed

test conditions.

Note 2: V

Note 3: Load regulation is tested by using a 10ms current pulse and measuring V

Note 4: Quiescent current defined as the current flow into AVIN.

Note 5: At elevated temperatures, devices must be derated based on thermal resistance. The device in the SO-8 package must be derated at θ

junction to ambient with no heat sink. The device in the LLP-16 must be derated at θ

Note 6: Limits are 100% production tested at 25˚C. Limits over the operating temperature range are guaranteed through correlation using Statistical Quality Control

(SQC) methods. The limits are used to calculate National’s Average Outgoing Quality Level (AOQL).

Note 7: The human body model is a 100pF capacitor discharged through a 1.5kΩ resistor into each pin.

offset is the voltage measurement defined as V

TT

subtracted from V

TT

J

= 0mA 1.21 1.235 1.26 V

=0A

= 0 to 1.5A 0.5 %

= 0 to −1.5A −0.5

= −5µA to +5µA 5 kΩ

=0A

Junction Temp. Range (Note 5) 0˚C to +125˚C

AVIN to GND 2.2V to 5.5V

PVIN to GND 2.2V to AVIN

= 25˚C and limits in boldface

J

= 0˚C to +125˚C). Unless otherwise specified,

−15

01520mV

−20

250 400 µA

.

REF

.

TT

= 51˚ C/W junction to ambient.

JA

= 151˚ C/W

JA

www.national.com3

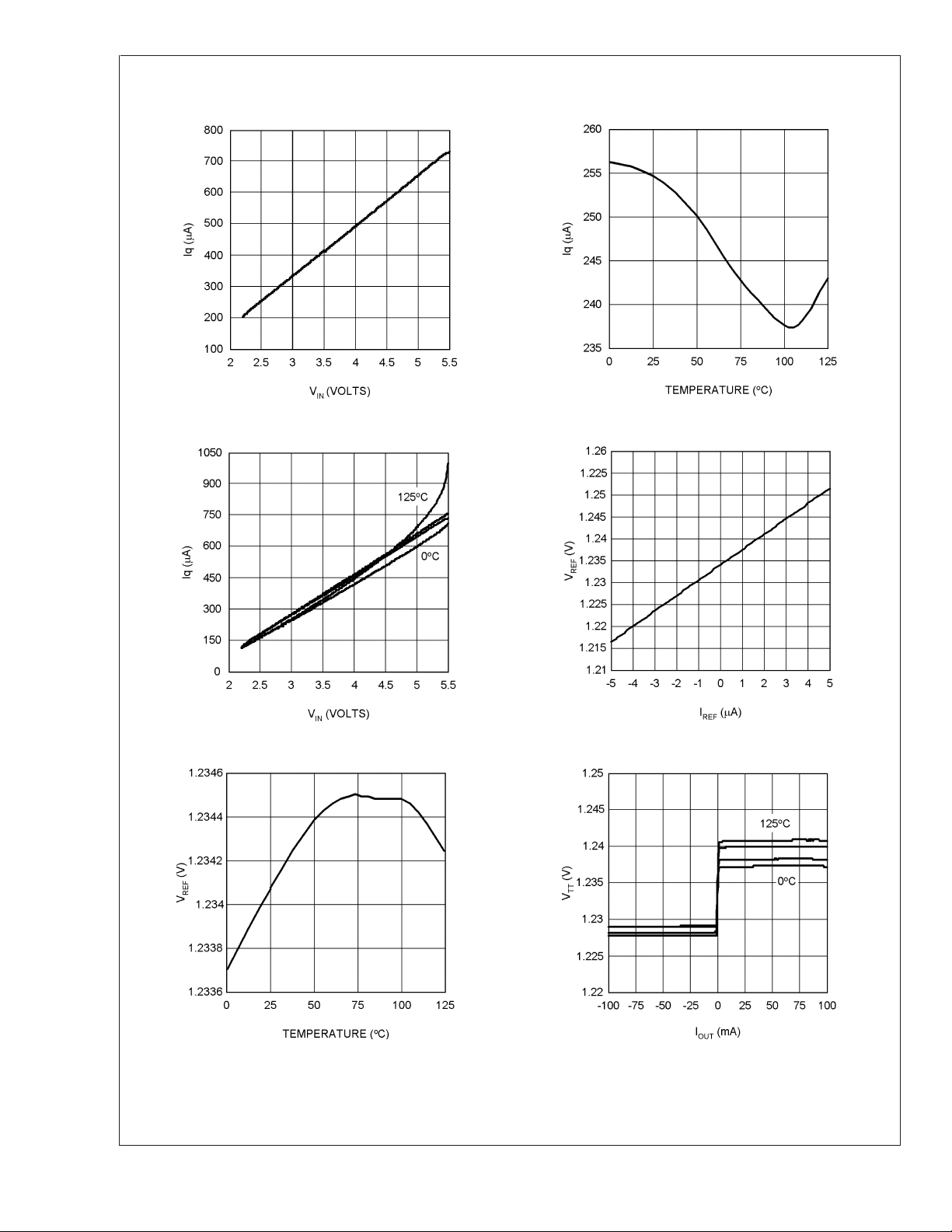

Typical Performance Characteristics

LP2995

Iq vs VIN(0, 25, 85, and 125˚C) V

Iq vs VIN(25˚C) Iq vs Temperature ( VIN= 2.5V)

20039309 20039310

vs I

REF

REF

20039311 20039312

V

vs Temperature (No Load) VTTvs I

REF

20039313 20039314

www.national.com 4

(0, 25, 85, and 125˚C)

OUT

Loading...

Loading...