NSC LMX2350TM, LMX2350SLB Datasheet

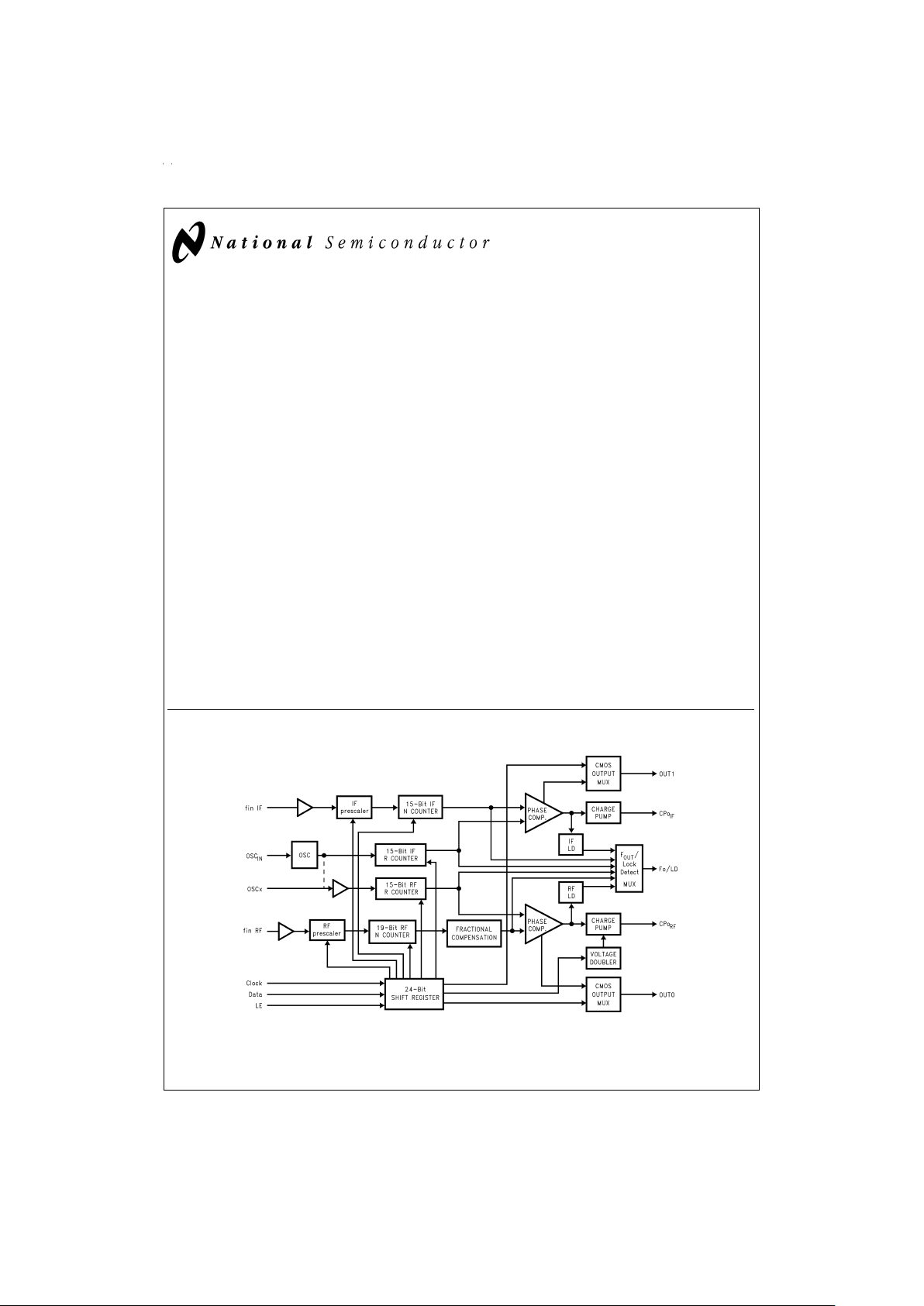

LMX2350/LMX2352

PLLatinum

™

Fractional N RF / Integer N IF

Dual Low Power Frequency Synthesizer

LMX2350 2.5 GHz/550 MHz

LMX2352 1.2 GHz/550 MHz

General Description

The LMX2350/2352 is part of a family of monolithic integrated fractional N/ Integer N frequency synthesizers designed to be used in a local oscillator subsystem for a radio

transceiver. It is fabricated using National’s 0.5µ ABiC V silicon BiCMOS process. The LMX2350/2352 contains dual

modulus prescalers along with modulo 15 or 16 fractional

compensation circuitry in the RF divider. A 16/17 or 32/33

prescale ratio can be selected for the LMX2350, and the

LMX2352 provides 8/9 or 16/17 prescale ratios. The IF circuitry for both the LMX2350 and LMX2352 contains an 8/9

prescaler, and is fully programmable. Using a fractional N

phase locked loop technique, the LMX2350 /52 can generate very stable low noise control signals for UHF and VHF

voltage controlled oscillators (VCO’s).

For the RF PLL, a highly flexible 16 level programmable

charge pump supplies output current magnitudes from

100µA to 1.6mA. Two uncommitted CMOS outputs can be

used to provide external control signals, or configured to

FastLock

™

mode. Serial data is transferred into the

LMX2350/2352 via a three wire interface (Data, LE, Clock).

Supply voltage can range from 2.7 V to 5.5 V.TheLMX2350/

2352 family features very low current consumption; typically

LMX2350 (2.5 GHz) 6.75 mA, LMX2352 (1.2 GHz) 5.00 mA

at 3.0V.TheLMX2350/2352areavailablein a 24-pin TSSOP

surface mount plastic package.

Features

n 2.7 V to 5.5 V operation

n Low current consumption

LMX2350: Icc = 6.75mA typ at 3v

LMX2352: Icc = 5.00mA typ at 3v

n Programmable or logical power down mode

Icc=5µAtypat3v

n Modulo 15 or 16 fractional RF N divider supports ratios

of 1, 2, 3, 4, 5, 8, 15, or 16

n Programmable charge pump current levels

RF 100µA to 1.6mA in 100µA steps

IF 100µA or 800 µA

n Digital filtered lock detect

Applications

n Portable wireless communications (PCS/PCN, cordless)

n Dual mode cellular telephone systems

n Zero blind slot TDMA systems

n Spread spectrum communication systems (CDMA)

n Cable TV Tuners (CATV)

Block Diagram

FastLock™is a trademark of National Semiconductor Corporation.

MICROWIRE

™

is a trademark of National Semiconductor Corporation.

PLLatinum

™

is a trademark of National Semiconductor Corporation.

TRI-STATE

®

is a registered trademark of National Semiconductor Corporation.

DS100831-1

PRELIMINARY

June 1999

LMX2350/LMX2352 PLLatinumTM Fractional N RF / Integer N IF Dual Low Power Frequency

Synthesizer

© 1999 National Semiconductor Corporation DS100831 www.national.com

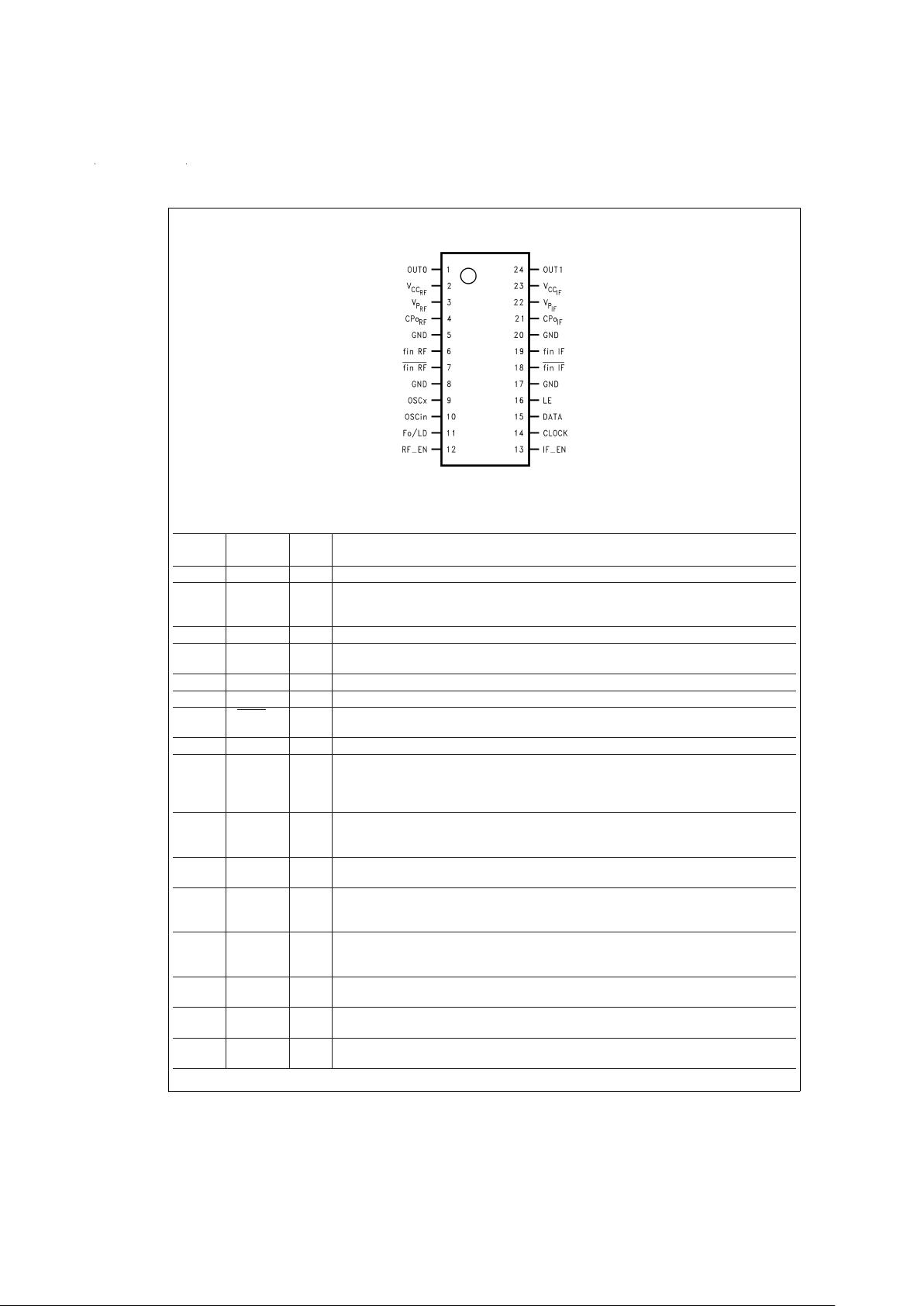

Connection Diagram

Pin Descriptions

Pin

No.

Pin

Name

I/O Description

1 OUT0 O Programmable CMOS output. Level of the output is controlled by IF_N [17] bit.

2 Vcc

RF

- RF PLL power supply voltage input. Must be equal to VccIF. May range from 2.7 V to 5.5 V.

Bypass capacitors should be placed as close as possible to this pin and be connected directly

to the ground plane.

3V

p

RF

- Power supply for RF charge pump. Must be ≥V

cc

RF

and V

cc

IF

.

4CP

o

RF

O RF charge pump output. Connected to a loop filter for driving the control input of an external

VCO.

5 GND - Ground for RF PLL digital circuitry.

6 fin RF I RF prescaler input. Small signal input from the VCO.

7 fin RF

I RF prescaler complimentary input. A bypass capacitor should be placed as close as possible

to this pin and be connected directly to the ground plane.

8 GND - Ground for RF PLL analog circuitry.

9 OSCx I/O Dual mode oscillator output or RF R counter input. Has a Vcc/2 input threshold when

configured as an input and can be driven from an external CMOS or TTL logic gate. Can also

be configured as an output to work in conjunction with OSCin to form a crystal oscillator. (See

functional description 1.1 and programming description 3.1.)

10 OSCin I Oscillator input which can be configured to drive both the IF and RF R counter inputs or only

the IF R counter depending on the state of the OSC programming bit. (See functional

description 1.1 and programming description 3.1.)

11 FoLD O Multiplexed output of N or R divider and RF/IF lock detect. Active High/Low CMOS output

except in analog lock detect mode. (See programming description 3.1.5.)

12 RF_EN I RF PLL Enable. Powers down RF N and R counters, prescaler, and will TRI-STATE

®

the

charge pump output when LOW. Bringing RF_EN high powers up RF PLL depending on the

state of RF_CTL_WORD. (See functional description 1.9.)

13 IF_EN I IF PLL Enable. Powers down IF N and R counters, prescaler, and will TRI-STATE the charge

pump output when LOW. Bringing IF_EN high powers up IF PLL depending on the state of

IF_CTL_WORD. (See functional description 1.9.)

14 CLOCK I High impedance CMOS Clock input. Data for the various counters is clocked into the 24 - bit

shift register on the rising edge.

15 DATA I Binary serial data input. Data entered MSB first. The last two bits are the control bits. High

impedance CMOS input.

16 LE I Load enable high impedance CMOS input. Data stored in the shift registers is loaded into one

of the 4 internal latches when LE goes HIGH. (See functional description 1.7.)

DS100831-2

Order Number LMX2350TM or LMX2352TM

NS Package Number MTC24

www.national.com 2

Connection Diagram (Continued)

Pin

No.

Pin

Name

I/O Description

17 GND - Ground for IF analog circuitry.

18 fin IF

I IF prescaler complimentary input. A bypass capacitor should be placed as close as possible

to this pin and be connected directly to the ground plane.

19 fin IF I IF prescaler input. Small signal input from the VCO.

20 GND - Ground for IF digital circuitry.

21 CPo

IF

O IF charge pump output. For connection to a loop filter for driving the input of an external VCO.

22 Vp

IF

- Power supply for IF charge pump. Must be ≥ V

cc

RF

and V

cc

IF

.

23 Vcc

IF

- IF power supply voltage input. Must be equal to VccRF. Input may range from 2.7 V to 5.5 V.

Bypass capacitors should be placed as close as possible to this pin and be connected directly

to the ground plane.

24 OUT1 O Programmable CMOS output. Level of the output is controlled by IF_N [18] bit.

www.national.com3

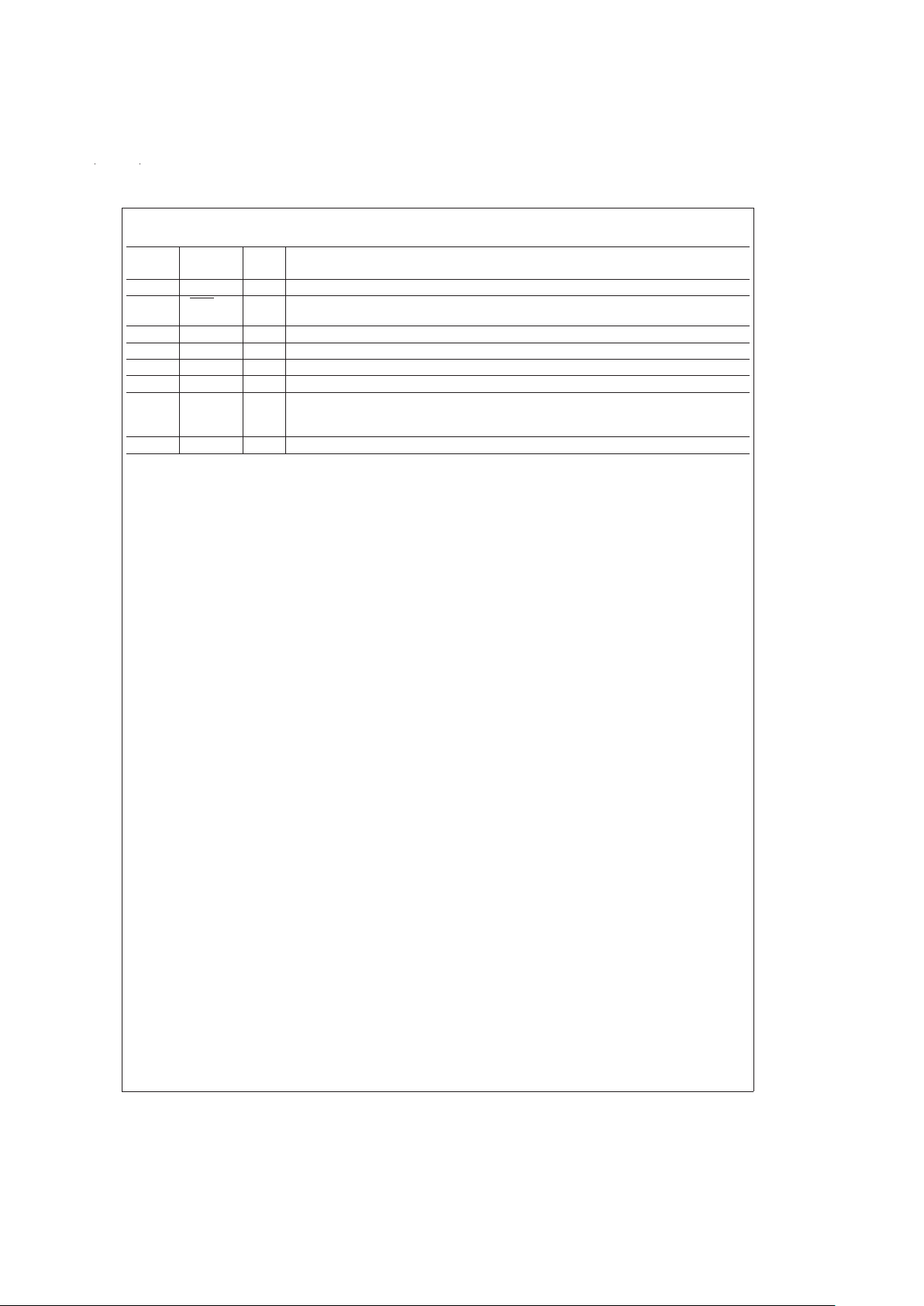

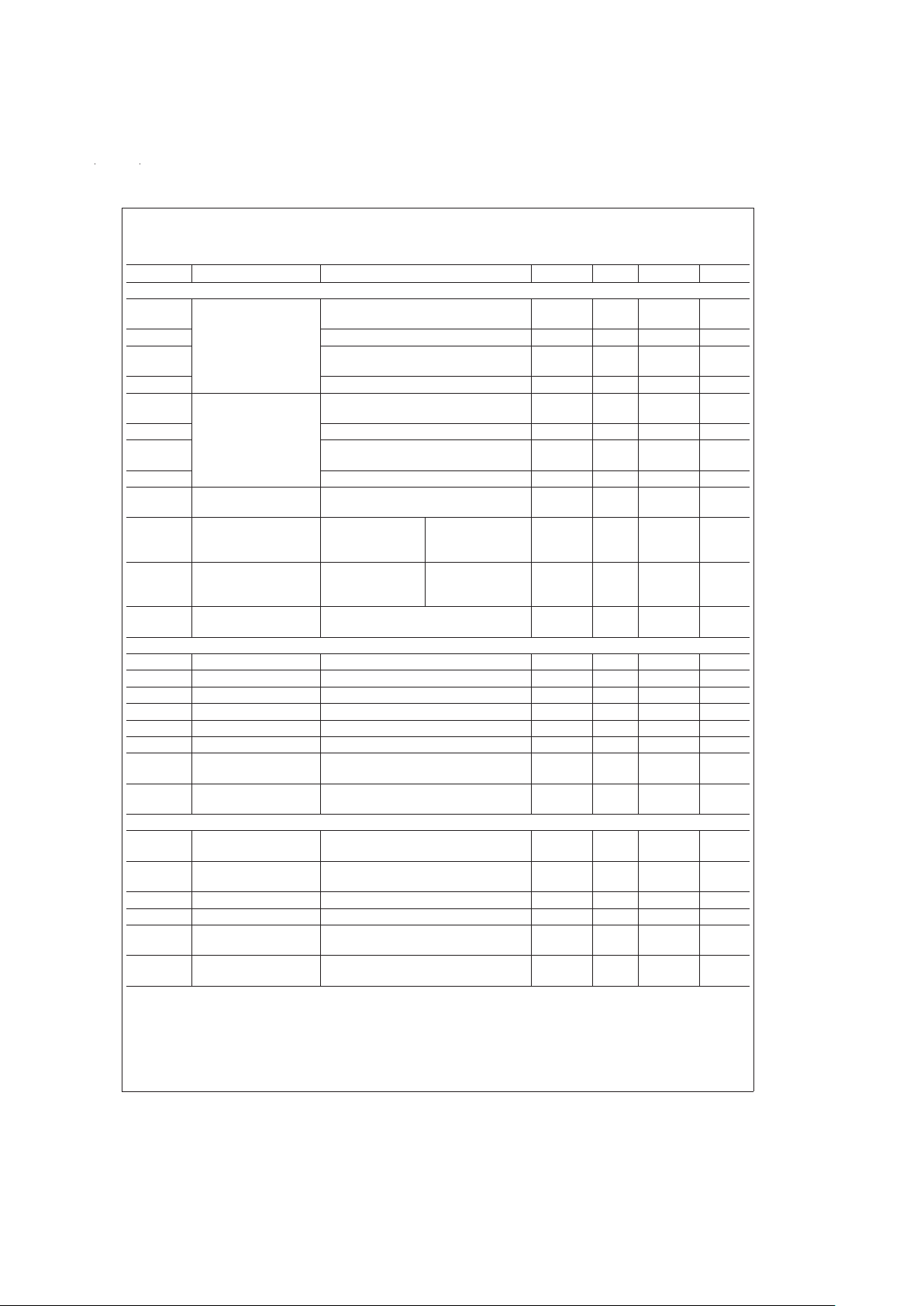

Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Value

Parameter Symbol Min Typ Max Units

Power Supply Voltage Vcc

RF

-0.3 6.5 V

Vcc

IF

-0.3 6.5 V

Vp

RF

-0.3 6.5 V

Vp

IF

-0.3 6.5 V

Voltage on any pin with GND = 0 volts Vi -0.3 Vcc + 0.3 V

Storage Temperature Range Ts -65 +150 C˚

Lead Temperature (Solder 4 sec.) T

L

+260 C˚

ESD - Whole Body Model (Note 2) 2 Kev

Recommended Operating Conditions

Value

Parameter Symbol Min Typ Max Units

Power Supply Voltage Vcc

RF

2.7 5.5 V

Vcc

IF

Vcc

RF

Vcc

RF

V

Vp

RF

Vcc 5.5 V

Vp

IF

Vcc 5.5 V

Operating Temperature TA -40 + 85 C

Note 1: “Absolute Maximum Ratings” indicate limits beyond which damage

to the device may occur. Operating Ratings indicate conditions for which the

device is intended to be functional, but do not guarantee specific performance limits.Forguaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test

conditions listed.

Note 2: This Device is a high performance RF integrated circuit and is ESD

sensitive. Handling and assembly of this device should only be done at ESDfree workstations.

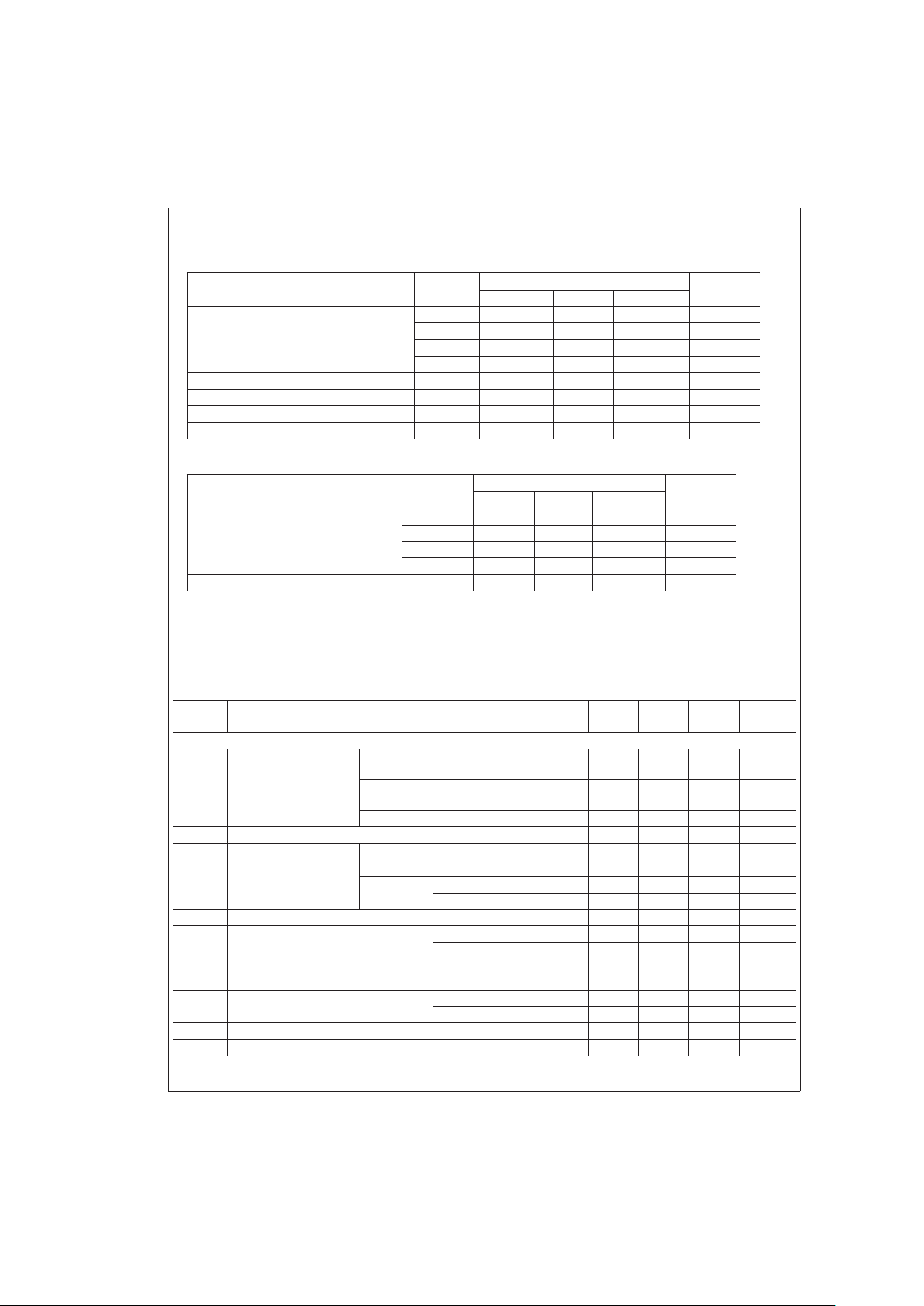

Electrical Characteristics (V

cc

RF

=

V

cc

IF

=

V

P

RF

=

V

P

IF

=

3.0V; −40˚ C

<

T

A

<

85˚ C except as specified)

Symbol

Parameter Conditions Min Typ Max Units

General

I

cc

Power Supply Current LMX2350 RF and IF,

V

cc

=

2.7V to 5.5V

6.75 7.75 mA

LMX2352 RF and IF,

V

cc

=

2.7V to 5.5V

5.0 6.0 mA

LMX2350/52 IF only, V

cc

=

2.7V to 5.5V 1.25 1.45 mA

I

CC-PWDN

Power Down Current RF_EN = IF_EN = LOW 5 µA

f

in

RF RF Operating LMX2350 Prescaler = 32 (Note 3) 1.2 2.5 GHz

Frequency Prescaler = 16 (Note 3) 0.5 1.2 GHz

LMX2352 Prescaler = 16 (Note 3) 0.5 1.2 GHz

Prescaler = 8 (Note 3) 0.25 0.5 GHz

f

in

IF IF Operating Frequency 10 550 MHz

f

OSC

Oscillator Frequency No load on OSCx (Note 3) 2 50 MHz

With resonator load on

OSCx (Note 3)

2 20 MHz

fφ Phase Detector Frequency RF and IF 10 MHz

Pf

in RF

RF Input Sensitivity VCC= 3.0V −15 0 dBm

V

CC

= 5.0V −10 0 dBm

Pf

in IF

IF Input Sensitivity 2.7 V≤VCC≤ 5.5V −10 0 dBm

V

OSC

Oscillator Sensitivity OSCin, OSCx 0.5 V

CC

V

PP

www.national.com 4

Electrical Characteristics (V

cc

RF

=

V

cc

IF

=

V

P

RF

=

V

P

IF

=

3.0V; −40˚ C

<

T

A

<

85˚ C except as specified)

(Continued)

Symbol Parameter Conditions Min Typ Max Units

Charge Pump

ICPo-

source

RF

RF Charge Pump

Output Current (see

Programming

Description 3.2.2)

VCPo Vp/2, RF_CP_WORD = 0000 −100 µA

ICPo-

sink RF

VCPo = Vp/2, RF_CP_WORD = 0000 100 µA

ICPo-

source

RF

VCPo = Vp/2, RF_CP_WORD = 1111 −1.6 mA

ICPo-

sink RF

VCPo = Vp/2, RF_CP_WORD = 1111 1.6 mA

ICPo-

source

IF

IF Charge Pump Output

Current (see

Programming

Description 3.1.4)

VCPo = Vp/2, CP_GAIN_8 = 0 −100 µA

ICPo-

sink IF

VCPo = Vp/2, CP_GAIN_8 = 0 100 µA

ICPo-

source

IF

VCPo = Vp/2, CP_GAIN_8 = 1 −800 µA

ICPo-

sink IF

VCPo = Vp/2, CP_GAIN_8 = 1 800 µA

ICPo-

Tri

Charge Pump

TRI-STATE Current

0.5 ≤ VCPo ≤ Vp - 0.5

-40˚ C

<TA<

85˚ C

-2.5 2.5 nA

ICPo-

sink

vs.

ICPo-

source

CP Sink vs. Source

Mismatch

VCPo = Vp/2

TA = 25˚ C

RFICPo

= 400 µA - 1.6 mA

310

%

ICPo vs.

VCPo

CP Current vs. Voltage 0.5 ≤ VCPo ≤ Vp -

0.5

T

A

= 25˚ C

RFICPo

= 800 µA - 1.6 mA

815

%

ICPo vs. T CP Current vs

Temperature

VCPo = Vp/2

-40˚ C

<TA<

85˚ C

8

%

Digital Interface

V

IH

High-level Input Voltage (Note 4) 0.8 Vcc V

V

IL

Low-level Input Voltage (Note 4) 0.2 Vcc V

I

IH

High-level Input Current V

IH

=

V

CC

=

5.5 V, (Note 4) −1.0 1.0 µA

I

IL

Low-level Input Current V

IL

=

0, V

CC

=

5.5 V, (Note 4) −1.0 1.0 µA

I

IH

Oscillator Input Current V

IH

=

V

CC

=

5.5 V 100 µA

I

IL

Oscillator Input Current V

IL

=

0, V

CC

=

5.5 V −100 µA

V

OH

High-level Output

Voltage

I

OH

=

−500 µA V

CC

−0.4 V

V

OL

High-level Output

Voltage

I

OL

=

500 µA 0.4 V

MICROWIRE Timing

t

CS

Data to Clock Setup

Time

See Data Input Timing 50 ns

t

CH

Data to Clock Hold

Time

See Data Input Timing 10 ns

t

CWH

Clock Pulse Width High See Data Input Timing 50 ns

t

CWL

Clock Pulse Width Low See Data Input Timing 50 ns

t

ES

Clock to Load Enable

Set Up Time

See Data Input Timing 50 ns

t

EW

Load Enable Pulse

Width

See Data Input Timing 50 ns

Note 3: Minimum operating frequencies are not production tested - only characterized.

Note 4: except fin, OSCin and OSCx

www.national.com5

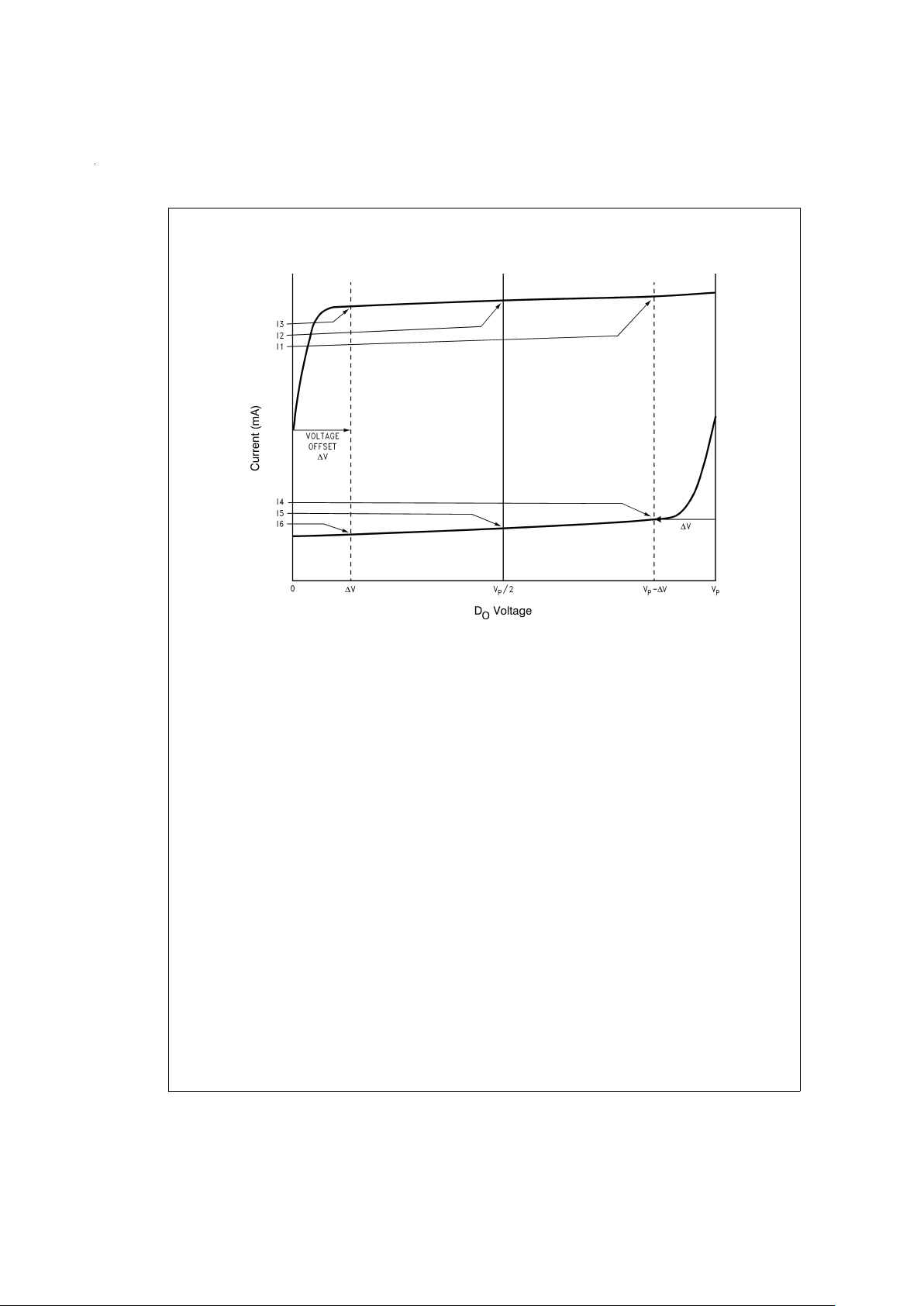

Charge Pump Current Specification Definitions

DS100831-7

I1=CP sink current at V

Do

=

Vp − ∆V

I2=CP sink current at V

Do

=

Vp/2

I3=CP sink current at V

Do

=

∆V

I4=CP source current at V

Do

=

Vp − ∆V

I5=CP source current at V

Do

=

Vp/2

I6=CP source current at V

Do

=

∆V

∆V=Voltage offset from positive and negative rails. Dependent on VCO tuning range relative to V

CC

and ground. Typical values are between 0.5V and 1.0V.

Note 5: I

Do

vs V

Do

=

Charge Pump Output Current magnitude variation vs Voltage=[

1

⁄

2

*

{||1| − ||3|}]/[1⁄

2

*

{||1| + ||3|}]*100%and [1⁄

2

*

{||4| − ||6|}]/[1⁄

2

*

{||4| +

||6|}]

*

100

%

Note 6: I

Do-sink

vs V

Do-source

=

Charge Pump Output Current Sink vs Source Mismatch=[||2| − ||5|]/[

1

⁄

2

*

{||2| + ||5|}]*100

%

Note 7: I

Do

vs T

A

=

Charge Pump Output Current magnitude variation vs Temperature=[||2

@

temp| − ||2@25˚C|]/||2@25˚C|*100%and [||5@temp| − ||5

@

25˚C|]/||5@25˚C|*100

%

www.national.com 6

Loading...

Loading...