NSC LM81CIMT-3 Datasheet

June 1999

LM81

Serial Interface ACPI-Compatible Microprocessor System

Hardware Monitor

General Description

The LM81 is a highly integrated data acquisition system for

hardware monitoring of servers, Personal Computers, or virtually any microprocessor-based system. In a PC, the LM81

can be used to monitor power supply voltages, temperatures, and fan speeds. Actual values for these inputs can be

read at any time. Programmable WATCHDOG

LM81 activate a fully programmable and maskable interrupt

system with two outputs (INT and T_CRIT_).

The LM81 has an on-chip digital output temperature sensor

with 9-bit or 12-bit resolution, a 6 analog inputADC with 8-bit

resolution and an 8-bit DAC. Two fan tachometer outputs

can be measured with the LM81’s FAN1 and FAN2 inputs.

The DAC, witha0to1.25V output voltage range, can be

used for fan speed control. Additional inputs are provided for

Chassis Intrusion detection circuits, and VID monitor inputs.

The LM81 has a Serial Bus interface that is compatible with

™

SMBus

.

™

limits in the

Features

n Temperature sensing

n 6 positive voltage inputs with scaling resistors for

monitoring +5V, +12V, +3.3V, +2.5V, Vccp power

supplies directly

n 8-bit DAC output for controlling fan speed

n 2 fan speed monitoring inputs

n Chassis Intrusion Detector input

n WATCHDOG

n SMBus Serial Bus interface compatibility

n VID0-VID4 monitoring inputs

™

comparison of all monitored values

Key Specifications

n Voltage monitoring

Error +2%(max)

n Temperature Error

−40˚C to +125˚C

n Supply Voltage Range 2.8V to 3.8V

n Supply Current Operating: 0.4 mA (typ)

n ADC and DAC Resolution 8 Bits

n Temperature Resolution 0.5˚C

±

3˚C (max)

Applications

n System Thermal and Hardware Monitoring for Servers

and PCs

n Office Electronics

n Electronic Test Equipment and Instrumentation

LM81 Serial Interface ACPI-Compatible Microprocessor System Hardware Monitor

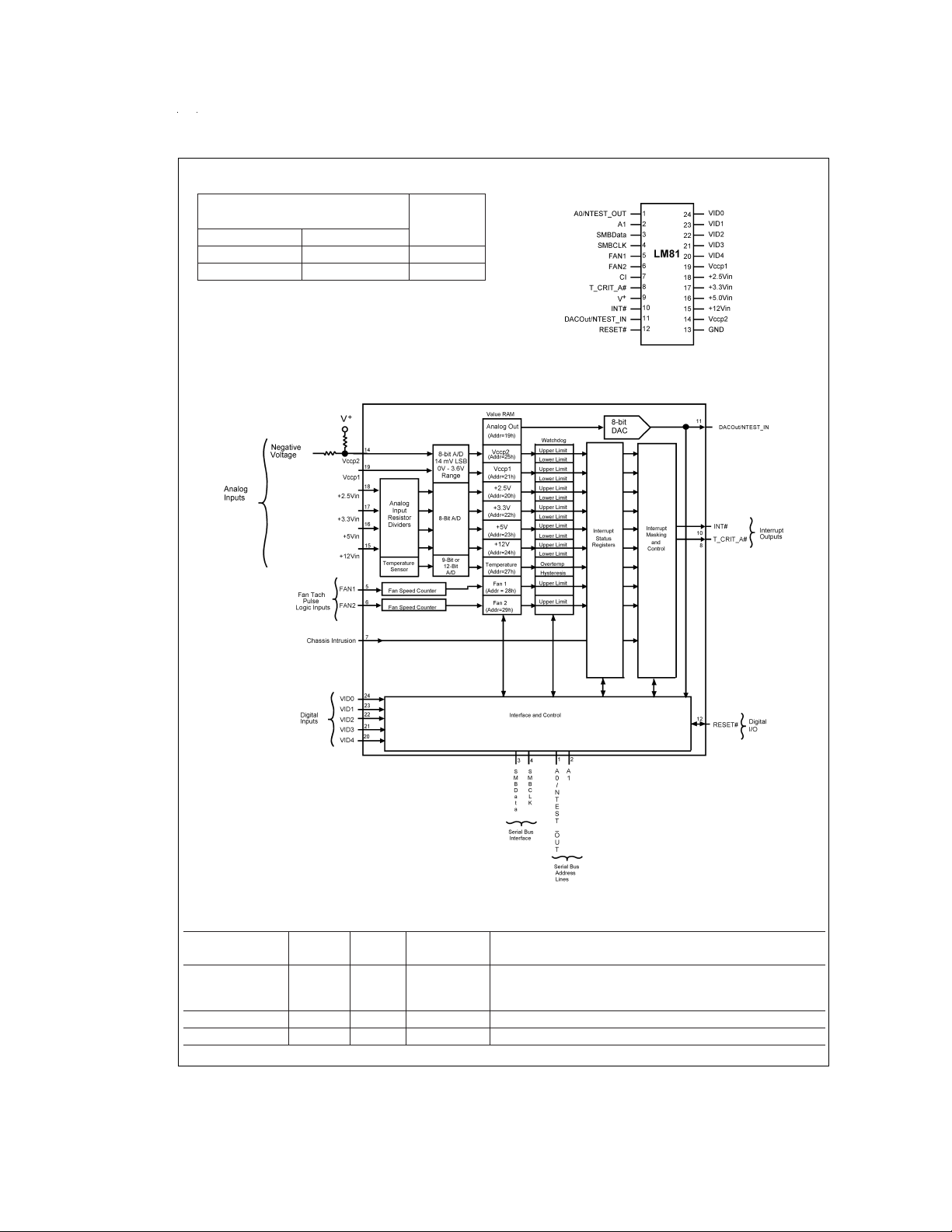

Typical Application

#

Indicates Active Low (“Not”)

TRI-STATE®is a registered trademark of National Semiconductor Corporation.

™

WATCHDOG

SMBus

© 1999 National Semiconductor Corporation DS100072 www.national.com

is a trademark of National Semiconductor Corporation.

™

is a trademark of the Intel Corporation.

DS100072-1

Ordering Information

Temperature Range

−40˚C ≤ T

≤ +125˚C

A

Order Number Device Marking

LM81CIMT-3

LM81CIMTX-3

Note:1-Rail transport media, 62 parts per rail

2

-Tape and reel transport media, 3400 parts per reel

1

LM81CIMT-3 MTC24B

2

LM81CIMT-3 MTC24B

Block Diagram

Connection Diagram

NS Package

Number

DS100072-3

DS100072-2

Pin Description

Pin

Name(s)

A0/NTEST_OUT 1 1 Digital I/0 The lowest order programmable bit of the serial bus address. This

A1 2 1 Digital Input The highest order programmable bit of the serial bus address.

SMBData 3 1 Digital I/O Serial Bus bidirectional Data. Open-drain output.

www.national.com 2

Pin

Number

Number

of Pins

Type Description

pin functions as an output during NAND Tree tests (board-level

connectivity testing). Refer to

SECTION 11

on NAND Tree testing.

Pin Description (Continued)

Pin

Name(s)

SMBCLK 4 1 Digital Input Serial Bus Clock.

FAN1-FAN2 5-6 2 Digital Inputs Schmitt Trigger fan tachometer inputs.

CI 7 1 Digital I/O An active high input from an external circuit which latches a

T_CRIT_A

+

(+2.8V to

V

+3.8V)

INT

DACOut/NTEST_IN 11 1 Analog

RESET

GND 13 1 GROUND Internally connected to all circuitry. The ground reference for all

Vccp2 14 1 Analog Input Analog input for monitoring −12V or Vccp2. Selectable by

+12Vin 15 1 Analog Input Analog input for monitoring +12V.

+5Vin 16 1 Analog Input Analog input for monitoring +5V.

+3.3Vin 17 1 Analog Input Analog input for monitoring +3.3V.

+2.5Vin 18 1 Analog Input Analog input for monitoring +2.5V.

Vccp1 19 1 Analog Input Analog input for monitoring Vccp, a processor voltage that is

VID4-VID0 20-24 5 Digital Inputs Supply Voltage readouts from the Pentium/PRO power supplies

TOTAL PINS 24

Pin

Number

Number

of Pins

8 1 Digital Output Critical Temperature Alarm active low open-drain output. This pin

9 1 POWER +3.3V V+power. Bypass with the parallel combination of 10 µF

10 1 Digital Output Interrupt active low open-drain output. This output is enabled when

12 1 Digital I/O Master Reset, 5 mA driver (open-drain), active low output with a

Type Description

Chassis Intrusion event. This line can go high without any

clamping action regardless of the powered state of the LM81.

There is also an internal open-drain output on this line, controlled

by Bit 6 of the Configuration Register (40h) or Bit 7 CI Clear

Register (46h), to provide a minimum 20 ms reset pulse. See

Output/Digital

Input

Section 3.3

can be grounded when not used.

(electrolytic or tantalum) and 0.1 µF (ceramic) bypass capacitors.

Bit 1 in the Configuration Register is set to 1. The default state is

disabled.

0V to +1.25V amplitude 8-bit DAC output. When forced high by an

external voltage the NAND Tree Test mode is enabled which

provides board-level connectivity testing. Refer to Section 11.0 on

NAND Tree testing.

20 ms minimum pulse width. Available when enabled via Bit 4 in

the Configuration register. It acts as an active low power on

RESET input.

analog inputs and the DAC output. This pin needs to be

connected to a low noise analog ground plane for optimum

performance of the DAC output.

choosing the appropriate external resistor divider values such that

the input to the LM81 is scaled to +2.5V. See

nominally at +2.5V.

that indicate the operating voltage or the processor (e.g. 1.5V to

2.9V). The values are read in the VID/Fan Divisor Register and

the VID4 Register.

and

Section 9.0

.

Section 4.0.

www.national.com3

Absolute Maximum Ratings (Notes 1, 2)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Positive Supply Voltage (V

Voltage on Any Input or Output Pin:

+12Vin, T_CRIT_A

A0, A1, DACOut −0.3V to (V

+2.5Vin, +3.3Vin (Note 3)

All other pins −0.3V to +6V

Input Current at any Pin (Note 4)

Package Input Current (Note 4)

Maximum Junction Temperature

max) 150˚C

(T

J

ESD Susceptibility (Note 6)

Human Body Model 2000V

Machine Model 200V

+

) +6.0V

−0.3V to +15V

+

+ 0.3V)

±

5mA

±

20 mA

Soldering Information

MTC Package (Note 7) :

Vapor Phase (60 seconds) 215˚C

Infrared (15 seconds) 235˚C

Storage Temperature −65˚C to +150˚C

Operating Ratings (Notes 1, 2)

Operating Temperature Range T

LM81 −55˚C ≤ TA≤ +125˚C

Specified Temperature Range T

LM81 −40˚C ≤ TA≤ +125˚C

Junction to Ambient Thermal Resistance (θ

NS Package Number: MTC24B 95˚C/W

Supply Voltage (V

Voltage Range:

V

IN

+

) +2.8V to +3.8V

+12Vin −0.05V to +15V

+5Vin −0.05V to +6.8V

MIN

MIN

(Note 5))

JA

≤ TA≤ T

≤ TA≤ T

+3.3Vin −0.05V to +4.6V

+2.5Vin −0.05V to +3.6V

VID0 - VID4, Vccp −0.05V to +6.0V

All other inputs −0.05V to (V

+

+ 0.05V)

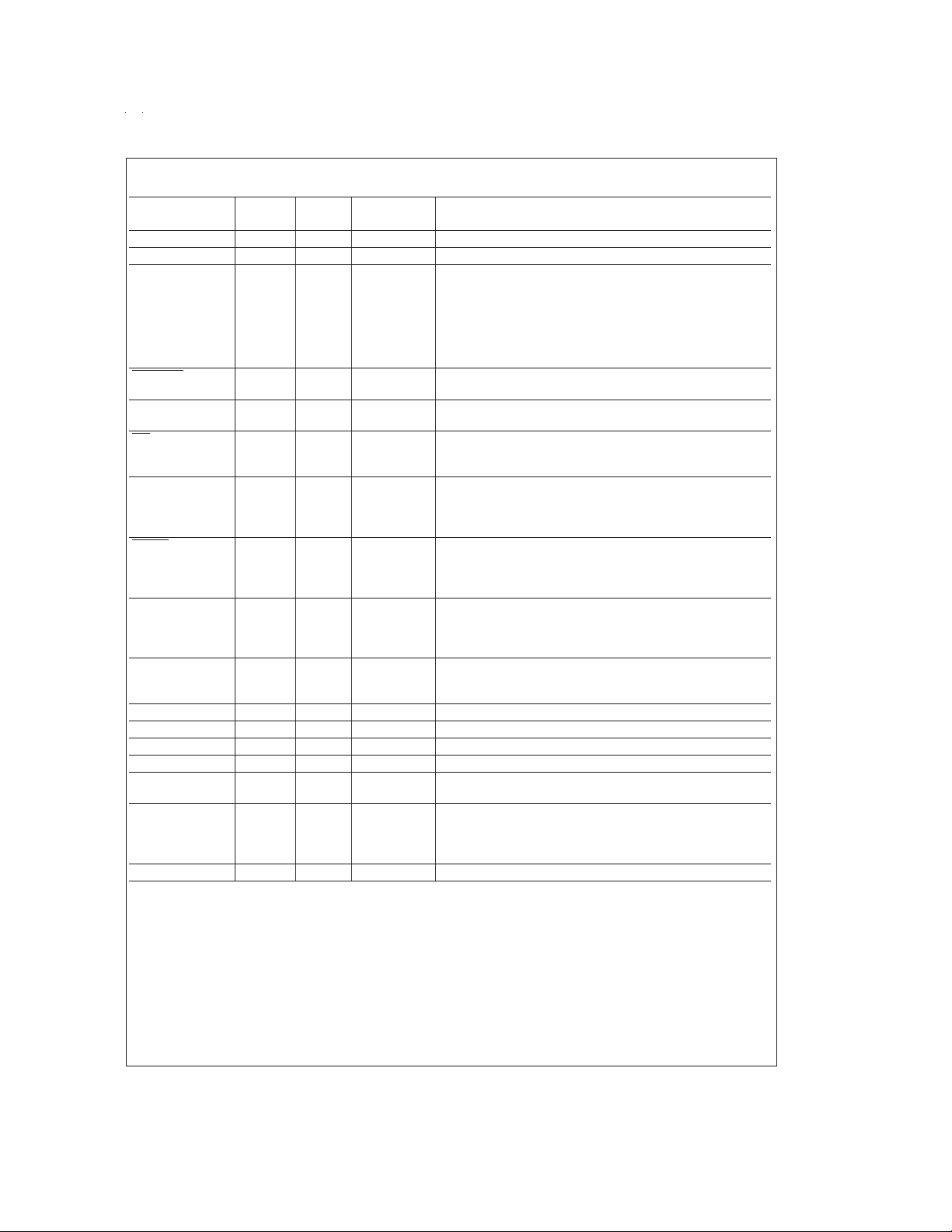

DC Electrical Characteristics

The following specifications apply for +2.8VDC≤ V+≤ +3.8VDC,R

=

for T

=

to T

T

A

T

J

MIN

; all other limits T

MAX

=

A

=

T

25˚C. (Note 8)

J

Symbol Parameter Conditions Typical Limits Units

POWER SUPPLY CHARACTERISTICS

+

I

Supply Current Interface Inactive 400 900 µA (max)

TEMPERATURE-TO-DIGITAL CONVERTER CHARACTERISTICS

Error −40˚C ≤ T

Resolution 9-bit mode

12-bit mode

LM81 ANALOG-TO-DIGITAL CONVERTER CHARACTERISTICS

Resolution 8 bits

TUE Total Unadjusted Error +2.5Vin,

+3.3Vin, +5Vin

Vccp1, Vccp2 (Note 11) +2.4

+12Vin (Notes 11, 12) +3.1

DNL Differential Non-Linearity

PSS Power Supply Sensitivity

t

Total Monitoring Cycle Time (Note 13)

C

ADC INPUT CHARACTERISTICS

Input Resistance (All analog inputs except

Vccp1 and Vccp2)

Vccp1 and Vccp2 DC Input Current

=

500Ω, unless otherwise specified. Boldface limits apply

S

(Note 9) (Note 10) (Limits)

≤ +125˚C

A

±

0.5

0.0625

(Notes 11, 12) +2

+0.8

+1.2

±

±

0.4

9-bit Temp Resolution

12-bit Temp Resolution

0.4

0.82

1.2

115 90 kΩ (min)

±

1µA

3 ˚C (max)

˚C (min)

˚C (min)

%

(max)

%

(min)

%

(max)

0

%

%

%

(min)

(max)

(min)

1 LSB (max)

%

/V

sec

sec (max)

sec (max)

MAX

MAX

www.national.com 4

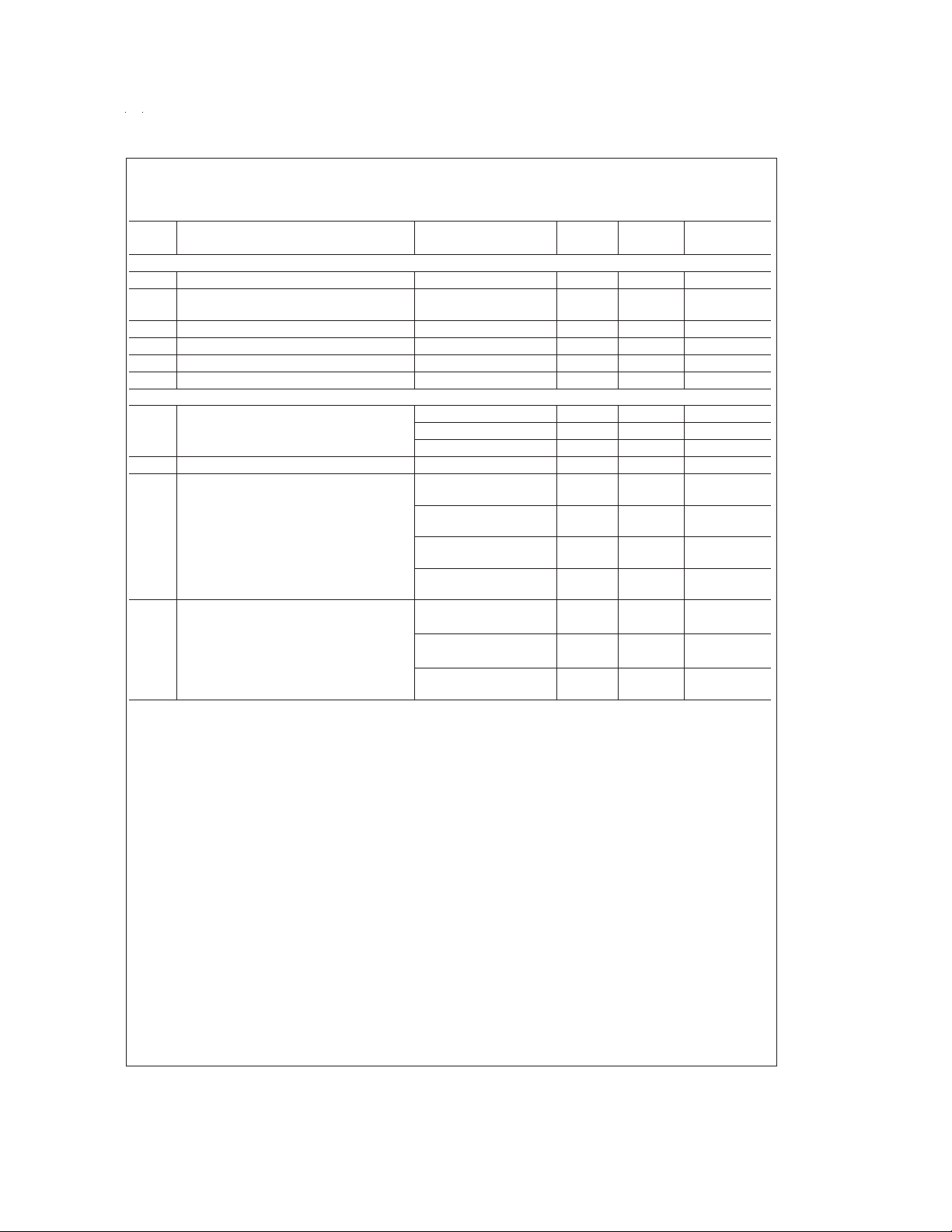

DC Electrical Characteristics (Continued)

The following specifications apply for +2.8VDC≤ V+≤ +3.8VDC,R

=

for T

=

to T

T

A

T

J

MIN

; all other limits T

MAX

=

A

=

T

25˚C. (Note 8)

J

Symbol Parameter Conditions Typical Limits Units

DAC CHARACTERISTICS

Resolution 8 Bits

DAC Error V

DAC Error Temperature Sensitivity 100 ppm/˚C (max)

DAC Error Power Supply Sensitivity 1.5

R

Output Load Resistance V

L

C

Output Load Capacitance 20 pF (max)

L

FAN RPM-TO-DIGITAL CONVERTER

Fan RPM Error +25˚C ≤ T

Full-scale Count 255 (max)

FAN1 and FAN2 Nominal Input

RPM (See

Section 6.0

)

Internal Clock Frequency +25˚C ≤ T

=

500Ω, unless otherwise specified. Boldface limits apply

S

(Note 9) (Note 10) (Limits)

+

=

3.3V

±

5

62.5

=

1.25V 625 Ω (min)

O

≤ +75˚C

−10˚C ≤ T

−40˚C ≤ T

A

≤ +100˚C

A

≤ +125˚C

A

Divisor=1, Fan Count

=

8800 RPM

±

10

±

15

±

20

153 (Note 14)

Divisor=2, Fan Count

=

4400 RPM

153 (Note 14)

Divisor=3, Fan Count

=

2200 RPM

153 (Note 14)

Divisor=4, Fan Count

=

1100 RPM

153 (Note 14)

≤ +75˚C 22.5 20.2 kHz (min)

A

24.8 kHz (max)

−10˚C ≤ T

≤ +100˚C 22.5 19.1 kHz (min)

A

25.9 kHz (max)

−40˚C ≤ T

≤ +125˚C 22.5 18

A

27

%

(max)

mV (max)

%

/V (max)

%

(max)

%

(max)

%

(max)

kHz (min)

kHz (max)

www.national.com5

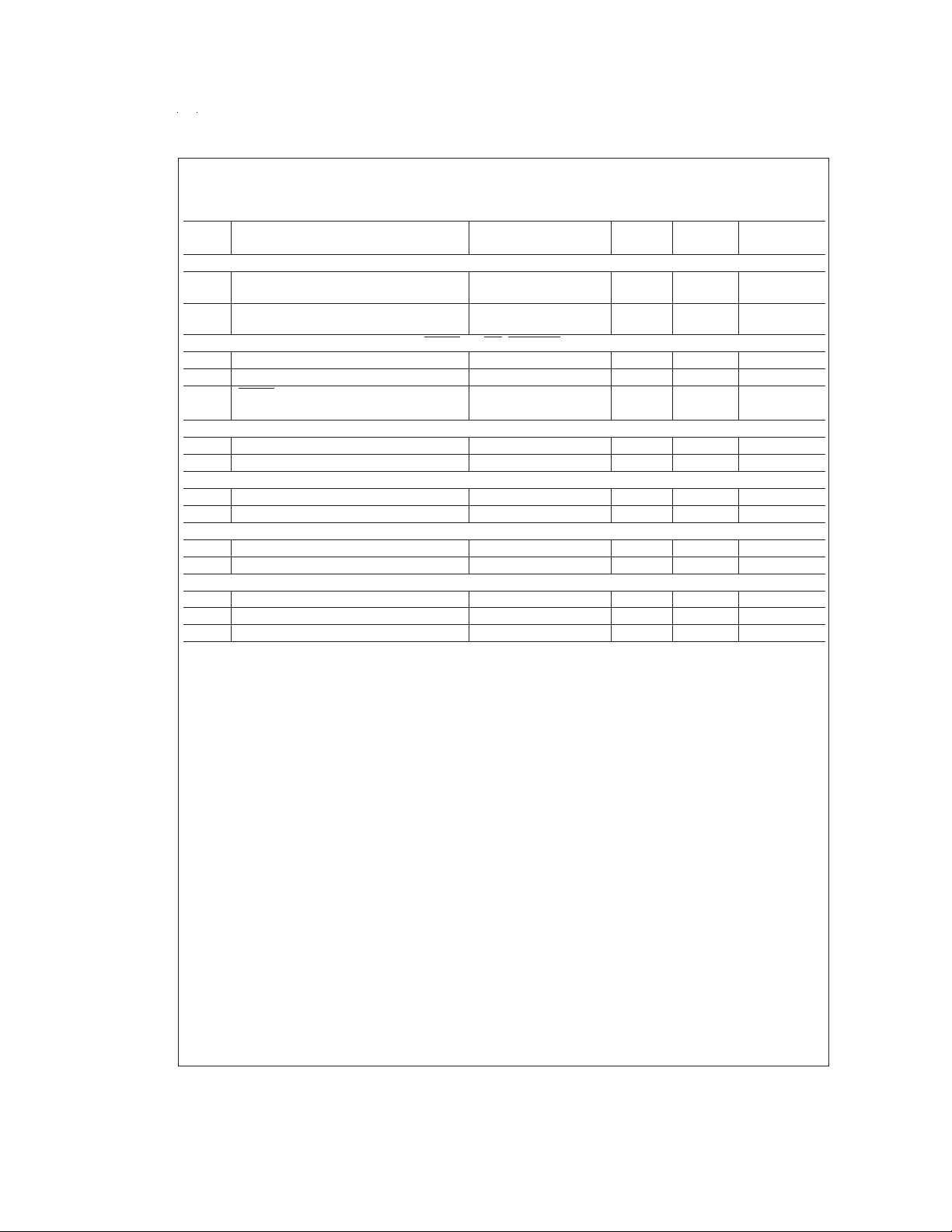

DC Electrical Characteristics (Continued)

The following specifications apply for +2.8VDC≤ V+≤ +3.8VDC,R

=

for T

=

to T

T

A

T

J

MIN

; all other limits T

MAX

=

A

=

T

25˚C. (Note 8)

J

Symbol Parameter Conditions Typical Limits Units

DIGITAL OUTPUTS (NTEST_OUT)

V

V

Logical “1” Output Voltage I

OUT(1)

Logical “0” Output Voltage I

OUT(0)

OPEN- DRAIN DIGITAL OUTPUTS (SMBData, RESET, CI, INT, T_CRIT_A)

V

Logical “0” Output Voltage I

OUT(0)

I

High Level Output Current V

OH

RESET and Chassis Intrusion

Pulse Width

DIGITAL INPUTS: VID0–VID4, NTEST_IN, A0/NTEST_OUT, A1, Chassis Intrusion (CI)

V

V

Logical “1” Input Voltage 2.0 V (min)

IN(1)

Logical “0” Input Voltage 0.8 V (max)

IN(0)

SMBus DIGITAL INPUTS (SMBCLK, SMBData)

V

V

Logical “1” Input Voltage 1.4 V (min)

IN(1)

Logical “0” Input Voltage 0.6 V (max)

IN(0)

Tach Pulse Logic Inputs (FAN1, FAN2)

V

V

Logical “1” Input Voltage 0.7xV

IN(1)

Logical “0” Input Voltage 0.3xV

IN(0)

ALL DIGITAL INPUTS

I

Logical “1” Input Current V

IN(1)

I

Logical “0” Input Current V

IN(0)

C

Digital Input Capacitance 20 pF

IN

=

500Ω, unless otherwise specified. Boldface limits apply

S

(Note 9) (Note 10) (Limits)

=

±

3.0 mA at

OUT

+

=

+2.8V

V

=

±

3.0 mA at

OUT

+

=

+3.8V

V

=

−3.0 mA 0.4 V (min)

OUT

+

OUT

=

V

0.1 100 µA (max)

2.4 V (min)

0.4 V (max)

45 20 ms (min)

+

=

V

IN

=

0V

IN

DC

−0.005 −1 µA (min)

0.005 1 µA (max)

+

V (min)

+

V (max)

www.national.com 6

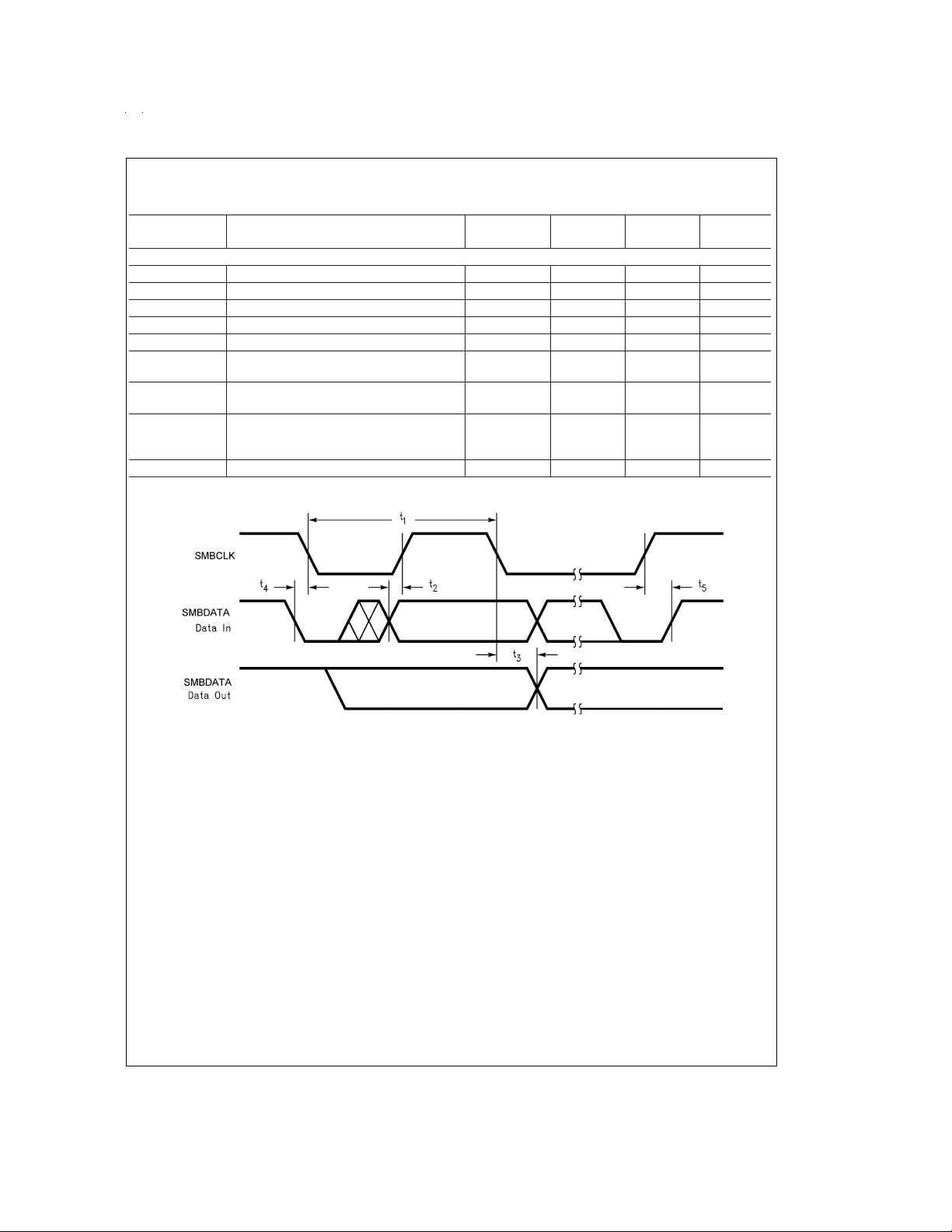

AC Electrical Characteristics

The following specifications apply for +2.8VDC≤ V+≤ +3.8VDCon SMBCLK and SMBData, unless otherwise specified. Boldface limits apply for T

Symbol Parameter Conditions Typical Limits Units

SERIAL BUS TIMING CHARACTERISTICS

t

1

t

rise

t

fall

t

2

t

3

t

4

t

5

t

TIMEOUT

C

L

=

=

to T

T

T

A

J

MIN

; all other limits T

MAX

=

A

=

T

25˚C. (Note 15)

J

(Note 9) (Note 10) (Limits)

SMBCLK (Clock) Period 2.5 µs (min)

SMBCLK and SMBData Rise Time 1 µs (max)

SMBCLK and SMBData Fall Time 300 ns (max)

Data In Setup Time to SMBCLK High 100 ns (min)

Data Out Stable After SMBCLK Low 0 ns (min)

SMBData Low Setup Time to SMBCLK Low

100 ns (min)

(start)

SMBData High Hold Time After SMBCLK

100 ns (min)

High (stop)

SMBData or SMBCLK low time required to

reset the Serial Bus Interface to the Idle

State

31

25

35

ms (min)

ms (max)

Capacitive Load on SMBCLK and SMBData 400 pF (max)

ms

FIGURE 1. Serial Bus Timing Diagram

DS100072-4

www.national.com7

AC Electrical Characteristics (Continued)

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is

functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed

specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: All voltages are measured with respect to GND, unless otherwise specified.

Note 3: The Absolute maximum input range for :

+2.5Vin - −0.3V to (1.4 x V

+3.3Vin - −0.3V to (1.8 x V

Note 4: When the input voltage (V

maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 5 mA to four.

Note 5: Themaximum power dissipation must be derated at elevated temperatures and is dictated by T

allowable power dissipation at any temperature is P

Note 6: The human body model is a 100 pF capacitor discharged through a 1.5 kΩ resistor into each pin. The machine model is a 200 pF capacitor discharged di-

rectly into each pin.

Note 7: See the section titled “Surface Mount” found in any post 1986 National Semiconductor Linear Data Book for other methods of soldering surface mount de-

vices.

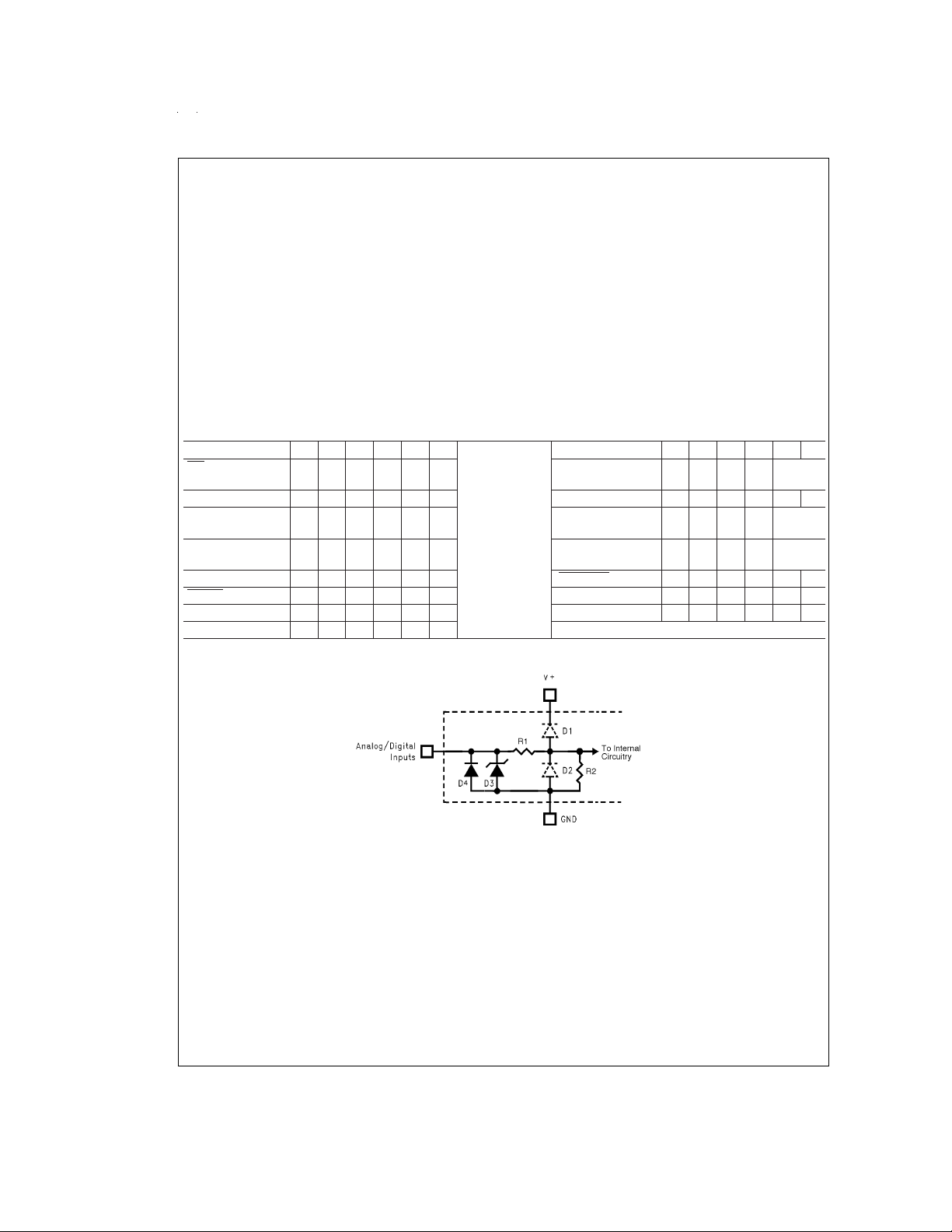

Note 8: Parasitics and or ESD protection circuitry are shown in the figure below for the LM81’s pins. The nominal breakdown voltage of the zener D3 is 6.5V. Care

should be taken not to forward bias the parasitic diode, D1, present on pins: A0/NTEST_OUT,A1 and DACOut/NTEST_IN. Doing so by more than 50 mV may corrupt

a temperature or voltage measurement.

Pin Name D1 D2 D3 D4 R1 R2 Pin Name D1 D2 D3 D4 R1 R2

INT

CI x x 0

FAN1–FAN2 x 0

SMBCLK x 0

SMBData x x 0

RESET xx 0

A0/NTEST_OUT x x x 0

A1 xxx 0

+

+ 0.42V or 6V, whichever is smaller

+

+ 0.55V or 6V, whichever is smaller.

) at any pin exceedsthepowersupplies(V

IN

=

max−TA)/θJA.

(T

D

J

xx 0

∞

∞

∞

∞

∞

∞

∞

∞

IN

<

GND or V

>

V+), the current at that pin should be limited to 5 mA. The 20 mA

IN

max, θJAand the ambient temperature, TA. The maximum

J

+12Vin x x x R1+R2

Vccp1, Vccp2 x x 0

+5Vin x x x R1+R2

+3.3Vin, +2.5Vin x x x R1+R2

T_CRIT_A xx0

VID4–VID0 x x 0

DACOut/NTEST_IN x x x 0

∼120k

∞

∼120k

∼120k

∞

∞

∞

An x indicates that the diode exists.

DS100072-5

FIGURE 2. ESD Protection Input Structure

=

Note 9: Typicals are at T

Note 10: Limits are guaranteed to National’s AOQL (Average Outgoing Quality Level).

Note 11: TUE (Total Unadjusted Error) includes Offset, Gain and Linearity errors of the ADC.

Note 12: Guaranteed at 3/4 scale

Note 13: Total Monitoring Cycle Time includes temperature conversion, 6 analog input voltage conversions and 2 tachometer readings. Each 9-bit temperature and

8-bit input voltage conversion takes 50 ms typical and 56 ms maximum. Twelve bit temperature conversion takes 400 ms. Fan tachometer readings take 20 ms typical, at 4400 rpm, and 200 ms maximum.

Note 14: The total fan count is based on 2 pulses per revolution of the fan tachometer output.

Note 15: Timing specifications are tested at the specified logic levels, V

www.national.com 8

=

T

25˚C and represent most likely parametric norm.

J

A

±

15%.

for a falling edge and VIHfor a rising edge.

IL

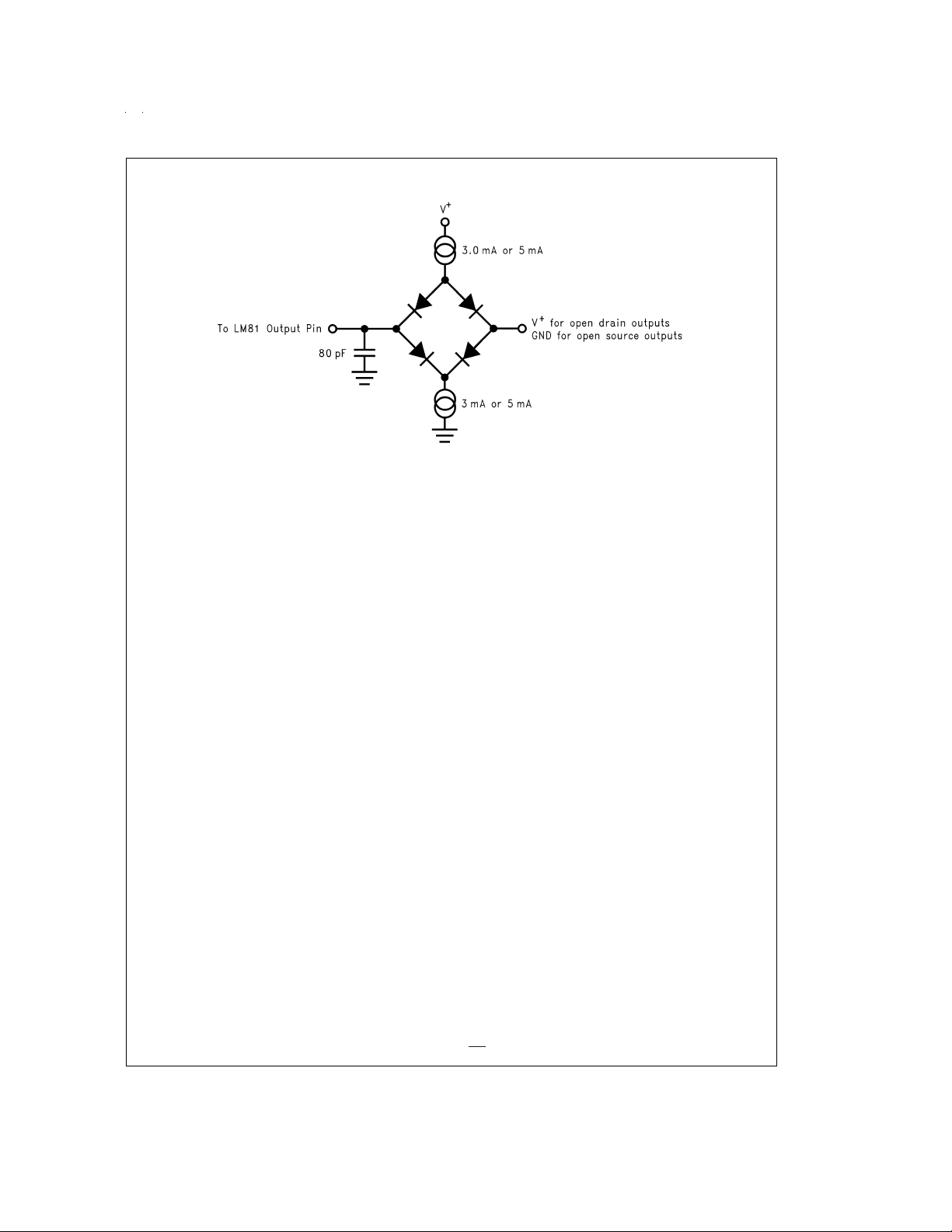

Test Circuit

FIGURE 3. Digital Output Load Test Circuitry

Functional Description

1.0 GENERAL DESCRIPTION

The LM81 provides 6 analog inputs, a temperature sensor, a

Delta-Sigma ADC (Analog-to-Digital Converter), a DAC output, 2 fan speed counters, WATCHDOG registers, and a variety of inputs and outputs on a single chip. A two wire Serial

Bus interface is included. The LM81 performs power supply,

temperature, fan control and fan monitoring for personal

computers.

The analog inputs are useful for monitoring several power

supplies present in a typical computer. The LM81 includes

internal resistor dividers that scale and/or offset external

Vccp, +2.5V, +3.3V, +5.0V and +12V power supply voltages

to a 3/4 scale nominal ADC output. The LM81 ADC then continuously converts the scaled inputs to 8-bit digital words.

Measurement of negative voltages (such as -5V and -12V

power supplies) can be accommodated with an external resistor divider applied to the Vccp2 input. Temperature is converted to a 9-bit or 12-bit two’s-complement digital word with

a 0.5˚C LSB or 0.0625˚C LSB, respectively.

Fan inputs measure the period of tachometer pulses from

the fans, providing a higher count for lower fan speeds. The

fan inputs are Schmitt-Trigger digital inputs with an acceptable range of 0V to V

+

V

/2. Full scale fan counts are 255 (8-bit counter) and this

represents a stopped or very slow fan. Nominal speeds,

based on a count of 153, are programmable from 1100 to

8800 RPM on FAN1 and FAN2. Schmitt-Trigger input circuitry is included to accommodate slow rise and fall times. A

0V to 1.25V DAC output voltage range can be used for control of fan speed.

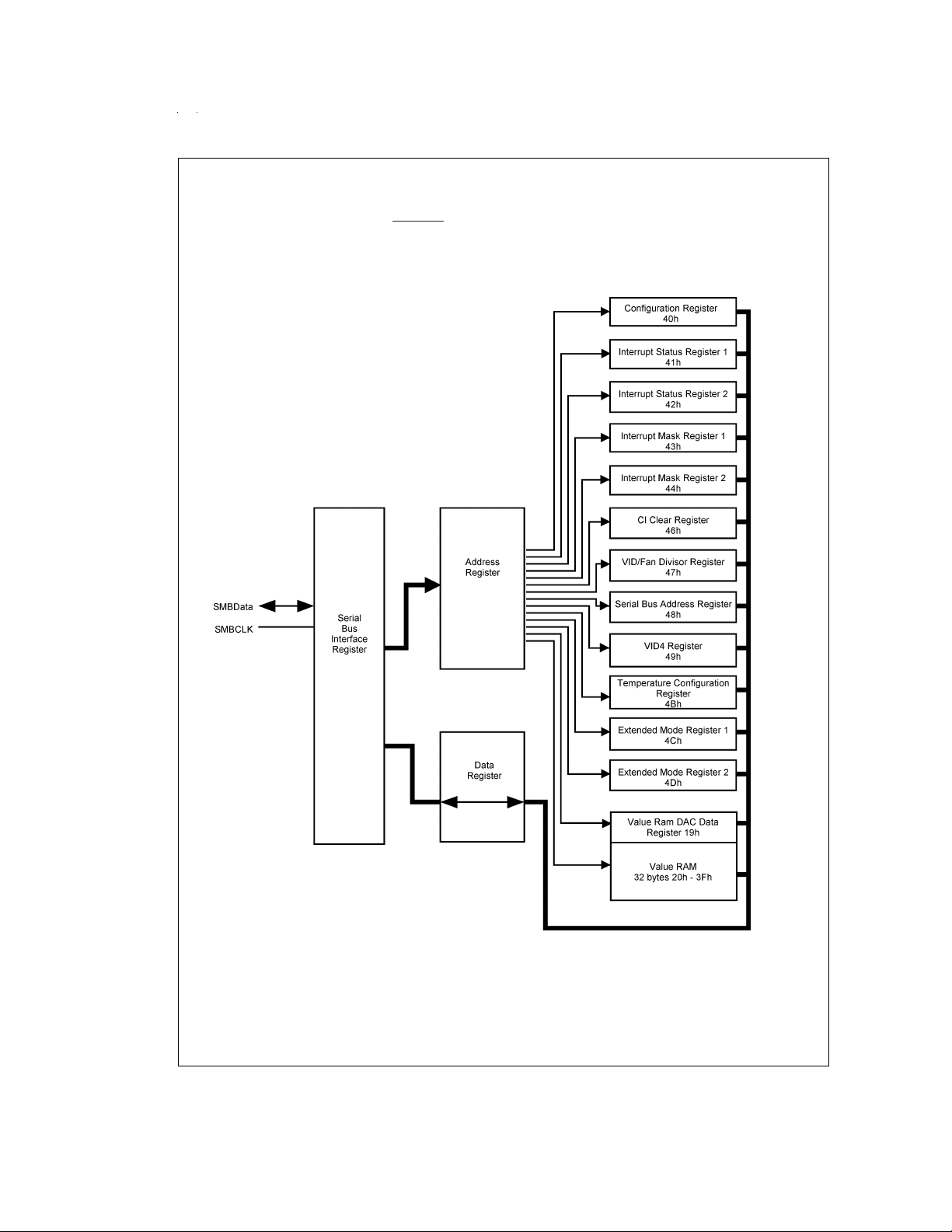

The LM81 has several internal registers, as shown in

4

,

Table 1

and

Configuration Register: Provides control and con-

•

figuration.

Interrupt Status Registers: Two registers to provide

•

status of each WATCHDOG limit or Interrupt event.

Interrupt Mask Registers: Allows masking of indi-

•

vidual Interrupt sources, as well as separate masking for

each of the two hardware Interrupt outputs.

+

and a transition level of approximately

Section 13.0

. These include:

Figure

DS100072-6

CI Clear Register: Allows transmitting a 20 ms low

•

pulse on the chassis intrusion pin (CI).

VID/Fan Divisor Register: This register contains the

•

state of the VID0-VID3 input lines and the divisor bits for

FAN1 and FAN2 inputs.

Serial Bus Address Register: Contains the Serial Bus

•

address. At power on it assumes the default value of

01011XX binary, and can be altered by the state of A0

and A1.

VID4 Register: Contains the state of the VID4 input.

•

Temperature Configuration Register: Selects the in-

•

terrupt mode and contains the 0.5˚C LSB of the temperature reading.

Extended Mode Registers: Enable and control the

•

Extended Mode which includes the LSBs of the 12-bit

temperature reading, T_CRIT, and T

Value RAM: The DAC digital input, monitoring results

•

(temperature, voltages, fan counts), WATCHDOG limits,

and Company/Stepping IDs are all contained in the Value

RAM. The Value RAM consists of a total of 34 bytes, addresses 15h - 3Fh, containing:

— byte 1 at address 15h a manufacturers test register

— locations 16h - 18h are unassigned and do not have

associated registers

— byte 2 at address 19h contains the DAC Data Register

— locations 1Ah - 1Fh are unassigned and do not have

associated registers

— the next 10 bytes at addresses 20h -29h contain all of

the results, with address 26h reserved

— the next 18 bytes at addresses 2Bh-3Ch are the

WATCHDOG limits

— the last 2 bytes at addresses 3Eh and 3Fh contain the

Company ID and Stepping ID numbers, respectively

When the LM81 is started, it cycles through each measurement in sequence, and it continuously loops through the sequence approximately once every 400 ms. Each measured

value is compared to values stored in WATCHDOG, or Limit

registers. When the measured value violates the programmed limit the LM81 will set a corresponding Interrupt in

the Interrupt Status Registers. The hardware Interrupt line

INT is fully programmable with separate masking of each In-

HYST

www.national.com9

Functional Description (Continued)

terrupt source. In addition, the Configuration Register has a

control bit to enable or disable the hardware Interrupt. Another hardware Interrupt line available T_CRIT_A (Critical

Temperature Alarm Output) is used to signal a catastrophic

overtemperature event. Having a dedicated interrupt for this

2.0 INTERFACE

purpose allows for the fastest possible response time to a

thermal runaway event. This output can be enabled by setting bit 4 of Extended Mode Register 1.

The Chassis Intrusion input is designed to accept an active

high signal from an external circuit that latches when the

case is removed from the computer.

FIGURE 4. LM81 Register Structure

www.national.com 10

DS100072-7

Loading...

Loading...