NSC LM3743MM-300, LM3743 Datasheet

September 2006

LM3743

N-Channel FET Synchronous Buck Controller for Low

Output Voltages

Reference accuracy: ±1.75%, over full temperature and

General Description

The LM3743 is a voltage mode PWM buck controller which

implements synchronous rectification. It provides a low cost,

fault tolerant, and efficient point of load solution. To reduce

component count several parameters are fixed, such as

switching frequency and the short circuit protection level. For

example the LM3743 has an operating switching frequency

of 300 kHz or 1 MHz and a fixed 500 mV high side current

limit for switch node short-circuit protection. LM3743 is a very

fault tolerant IC with switch node short-circuit, output undervoltage protection, and the ability to self recover after the

removal of the fault. It avoids the need to over design components due to thermal runaway during a fault condition, thus

resulting in a lower cost solution. It employs a proprietary

monotonic glitch free pre-bias start-up method suited for FPGAs and ASIC logic devices. A 0.8V internal reference with

±1.75% accuracy is ideal for sub-volt conversion. An external

programmable soft-start allows for tracking and timing flexibility. The driver features 1.6Ω of pull-up resistance and 1Ω

of pull-down drive resistance for high power density and very

efficient power processing.

Features

Input voltage from 3.0V to 5.5V

■

Output voltage adjustable down to 0.8V

■

■

input voltage range

Low-side sensing programmable current limit

■

Fixed high-side sensing for supplemental short-circuit

■

protection

Undervoltage protection

■

Hiccup mode protection eliminates thermal runaway

■

during fault conditions

Externally programmable soft-start with tracking capability

■

Switching frequency options of 1 MHz or 300 kHz

■

Pre-bias start-up capability

■

MSOP-10 package

■

Applications

ASIC/FPGA/DSP core power

■

Broadband Communications

■

Multi-media Set Top Boxes

■

Networking Equipment

■

Printers/Scanners

■

Servers

■

Low Voltage Distributed Power

■

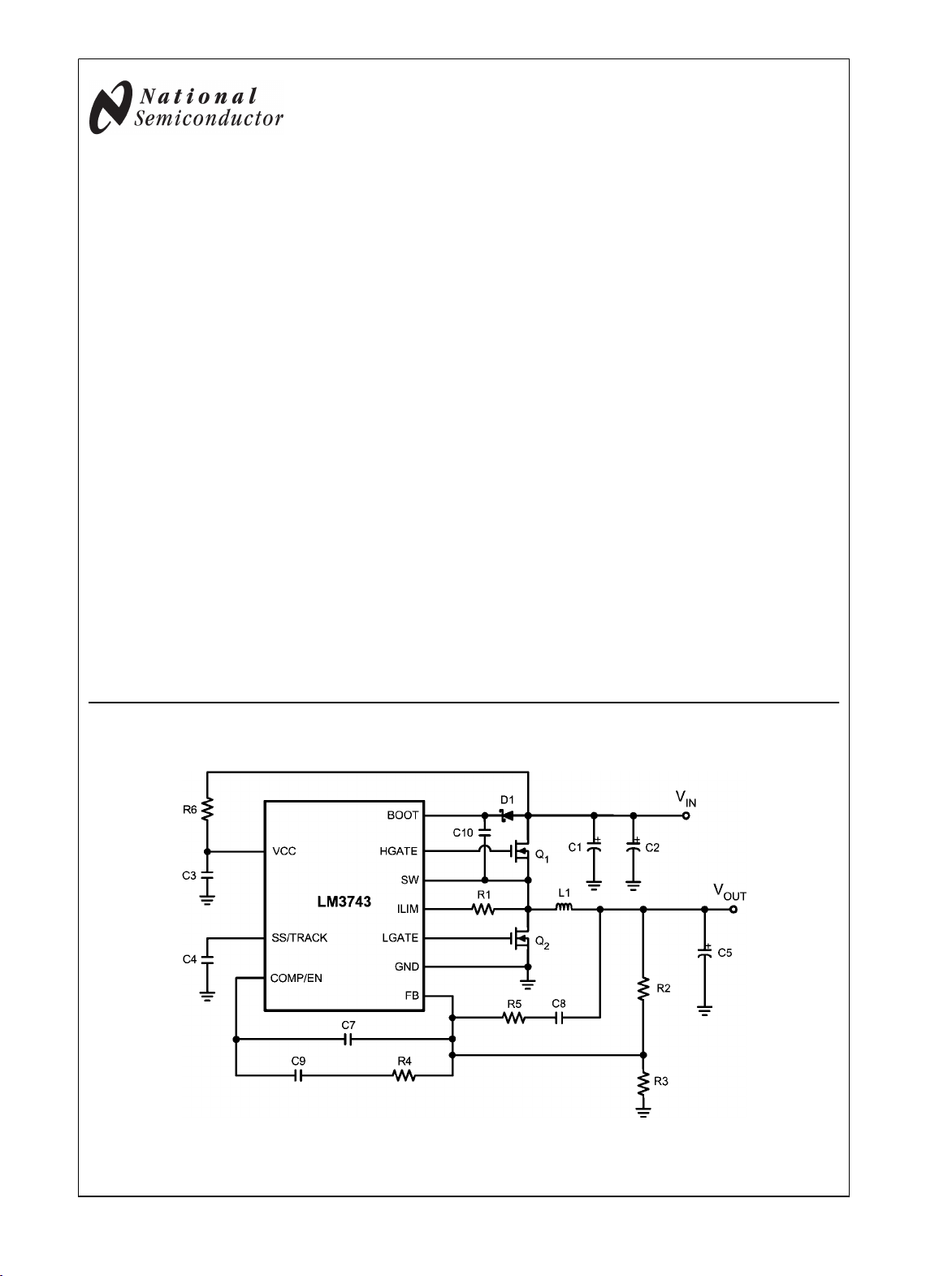

LM3743 N-Channel FET Synchronous Buck Controller for Low Output Voltages

Typical Application

20177401

© 2007 National Semiconductor Corporation 201774 www.national.com

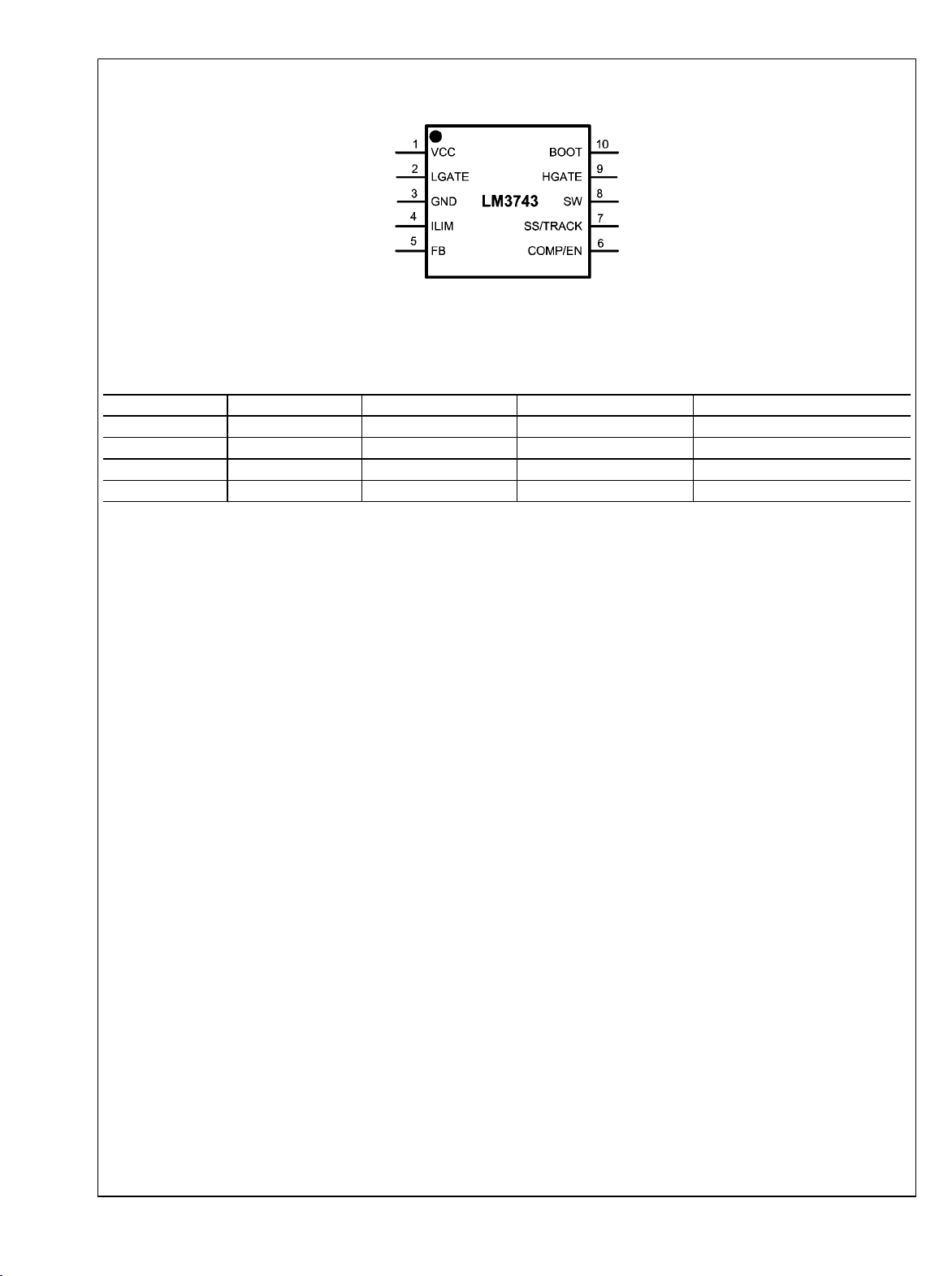

Connection Diagram

LM3743

10-Lead Plastic MSOP

NS Package Number MUB10A

Top View

20177402

Ordering Information

Order Number Frequency Option Top Mark NSC Package Drawing Supplied As

LM3743MM-300 300 kHz SKPB MUB10A 1000 units in Tape and Reel

LM3743MMX-300 300 kHz SKPB MUB10A 3500 units in Tape and Reel

LM3743MM-1000 1 MHz SKNB MUB10A 1000 units in Tape and Reel

LM3743MMX-1000 1 MHz SKNB MUB10A 3500 units in Tape and Reel

Pin Descriptions

VCC (Pin 1) Supply rail for the controller section of the IC. A

minimum capacitance of 1 µF, preferably a multi-layer ceramic capacitor type (MLCC), must be connected as close as

possible to the VCC and GND pin and a 1 to 4.99Ω resistance

must be connected in series from the supply rail to the Vcc

pin. See VCC FILTERING in the Design Consideration section for further details.

LGATE (Pin 2) Gate drive for the low-side N-channel MOSFET. This signal is interlocked with HGATE to avoid a shootthrough problem.

GND (Pin 3) Power ground (PGND) and signal ground

(SGND). Connect the bottom feedback resistor between this

pin and the feedback pin.

ILIM (Pin 4) Low side current limit threshold setting pin. This

pin sources a fixed 50 µA current. A resistor of appropriate

value should be connected between this pin and the drain of

the low-side N-FET.

FB (Pin 5) Feedback pin. This is the inverting input of the error

amplifier used for sensing the output voltage and compensating the control loop.

COMP/EN (Pin 6) Output of the error amplifier and enable

pin. The voltage level on this pin is compared with an internally

generated ramp signal to determine the duty cycle. This pin

is necessary for compensating the control loop. Forcing this

pin to ground will shut down the IC.

SS/TRACK (Pin 7) Soft-start and tracking pin. This pin is

connected to the non-inverting input of the error amplifier during initial soft-start, or any time the voltage is below the

reference. To track the rising ramp of another power supply's

output, connect a resistor divider from the output of that supply to this pin as described in Application Information.

SW (Pin 8) Switch pin. The lower rail of the high-side N-FET

driver. Also used for the high side current limit sensing.

HGATE (Pin 9) Gate drive for the high-side N-channel MOSFET. This signal is interlocked with LGATE to avoid a shootthrough problem.

BOOT (Pin 10) Supply rail for the N-channel MOSFET high

gate drive. The voltage should be at least one gate threshold

above the regulator input voltage to properly turn on the highside N-FET. See MOSFET Gate Drivers in the Application

Information section for more details on how to select MOSFETs.

www.national.com 2

LM3743

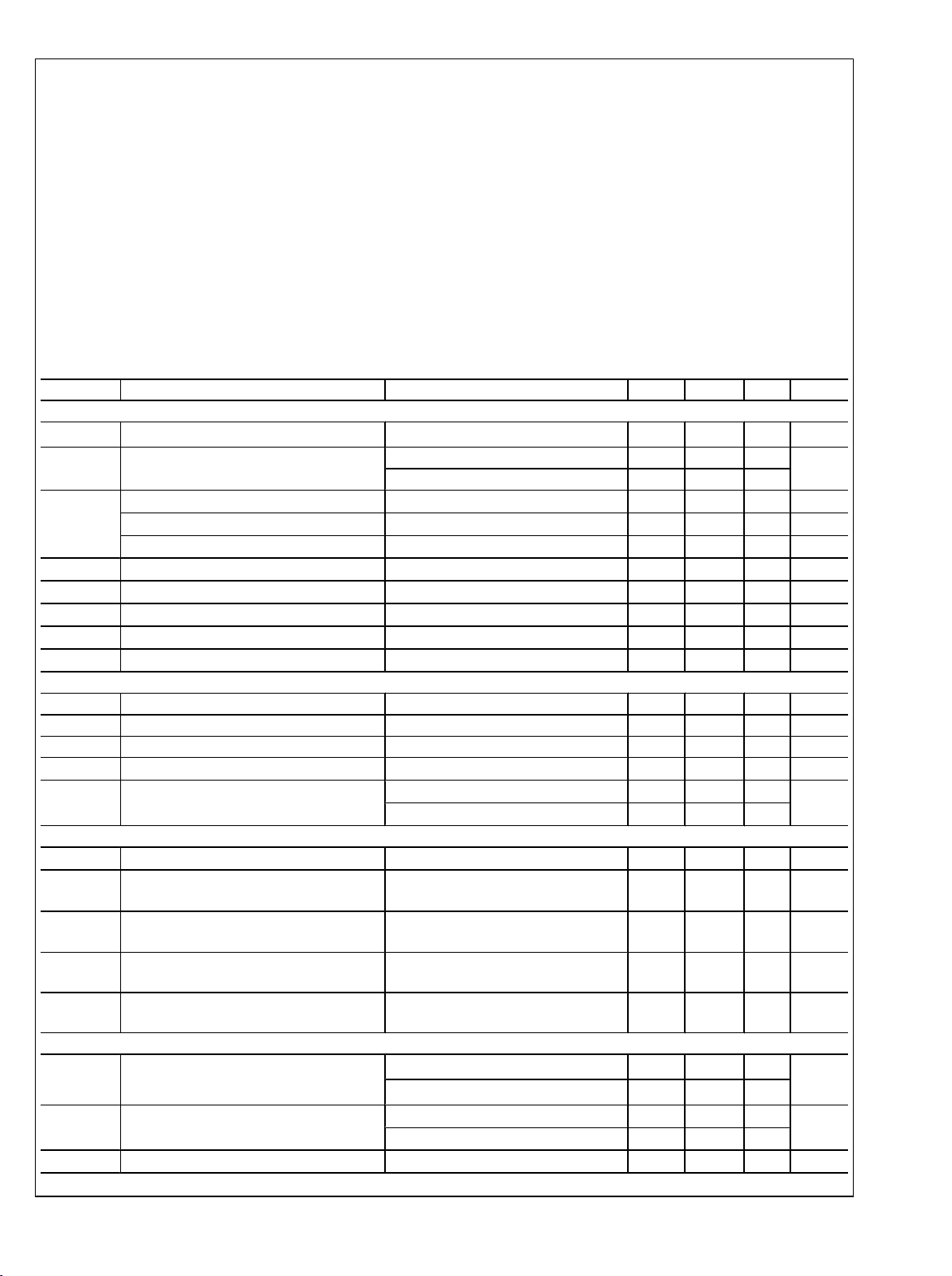

Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

V

CC

SW to GND -0.3V to 6V

Boot to GND -0.3V to 12V

Boot to SW -0.3V to 6V

SS/TRACK, ILIM, COMP/EN,FB

to GND

-0.3V to 6V

-0.3V to V

CC

Storage Temperature −65°C to 150°C

Soldering Information

Lead Temperature (soldering, 10sec) 260°C

Infrared or Convection (20sec) 235°C

ESD Rating (Note 3) + / – 2 kV

Operating Ratings

Supply Voltage Range, VCC (Note 2)

Junction Temperature Range (TJ)

3.0V to 5.5V

−40°C to +125°C

Junction Temperature 150°C

Electrical Characteristics V

= 3.3V, COMP/EN floating unless otherwise indicated in the conditions column.

CC

Limits in standard type are for TJ = 25°C only; limits in boldface type apply over the junction temperature (TJ) range of -40°C to

+125°C. Minimum and Maximum limits are guaranteed through test, design, or statistical correlation. Typical values represent the

most likely parametric norm at TJ = 25°C, and are provided for reference purposes only.

Symbol Parameter Conditions Min Typ Max Units

SYSTEM PARAMETERS

V

V

UVLO

FB pin voltage in regulation

FB

3.0V ≤ VCC ≤ 5.5V

0.786 0.8 0.814 V

UVLO thresholds Input voltage rising 2.84 3.0

Input voltage falling 2.45 2.66

I

VCC

Operating VCC current fSW = 300 kHz, LM3743-300 1.5 2.5 mA

Operating VCC current fSW = 1 MHz, LM3743-1000 1.8 3.0 mA

Shutdown VCC current COMP/EN = 0V 6 50 µA

I

SS/TRACK

I

ILIM

V

ILIM

I

COMP/EN

V

HS-CLIM

SS/TRACK pin source current V

ILIM pin source current V

SS/TRACK

ILIM

= 0V 8 10.2 12.5 µA

= 0V 42.5 50 57.5 µA

Current Limit Trip Level –25 0 25 mV

COMP/EN pin pull-up current V

= 0V 4 µA

COMP/EN

High-side current limit threshold Measured at VCC pin with respect to SW 500 mV

ERROR AMPLIFER

GBW Error Amplifier Unity Gain Bandwidth 30 MHz

G Error Amplifier DC Gain 90 dB

SR Error Amplifier Slew Rate 6 V/ms

I

I

EAO

FB

FB pin Bias Current 10 200 nA

EAO pin sourcing/sinking current capability V

V

= 1.5, VFB = 0.75V 1.7

COMP/EN

= 1.5, VFB = 0.85V -1

COMP/EN

GATE DRIVE

I

SHDN-BOOT

R

HG-UP

R

HG-DN

R

LG-UP

BOOT Pin Shutdown Current V

High Side MOSFET Driver Pull-up ON

resistance

High Side MOSFET Driver Pull-down ON

resistance

Low Side MOSFET Driver Pull-up ON

BOOT-VSW

V

BOOT-VSW

(sourcing)

V

BOOT-VSW

(sinking)

VCC = 3.3V, I

= 3.3V, V

= 3.3V, I

= 3.3V, I

HGATE

HGATE

= 350mA (sourcing) 1.6

LGATE

= 0V 25 50 µA

COMP/EN

= 350mA

= 350mA

1.6

1

resistance

R

LG-DN

Low Side MOSFET Driver Pull-down ON

VCC = 3.3V, I

= 350mA (sinking) 1

LGATE

resistance

OSCILLATOR

f

SW

D

MAX

Oscillator Frequency

3.0V ≤ VCC ≤ 5.5V, LM3743-300

3.0V ≤ VCC ≤ 5.5V, LM3743-1000

255 300 345

850 1000 1150

Max Duty Cycle fSW = 300 kHz, LM3743-300 85 91

fSW = 1 MHz, LM3743-1000 69 76

V

RAMP

PWM Ramp Amplitude 1.0 V

V

mA

Ω

Ω

Ω

Ω

kHz

%

3 www.national.com

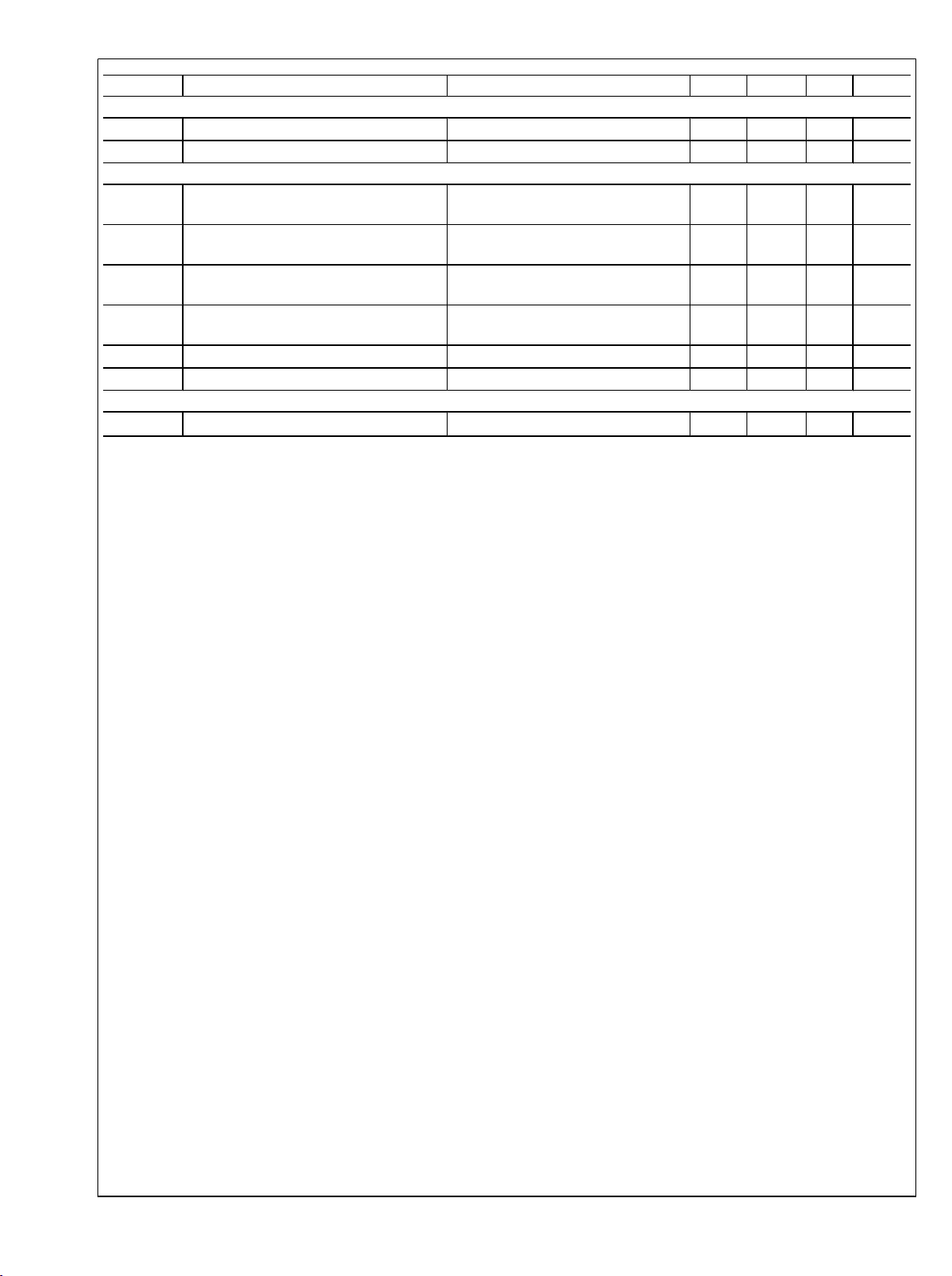

Symbol Parameter Conditions Min Typ Max Units

LOGIC INPUTS AND OUTPUTS

LM3743

V

COMP/EN-HI

V

COMP/EN-LO

COMP/EN pin logic high trip-point 0.65 0.9 V

COMP/EN pin logic low trip-point 0.1 0.45 V

HICCUP MODE

N

LSCYCLES

Low-side sensing cycles before hiccup

15 Cycles

mode

N

LSRESET

Low-side sensing cycles reset without

32 Cycles

activating current limit

V

UVP

Under Voltage Protection comparator

400 mV

threshold

t

GLICH-UVP

Under Voltage Protection fault time before

7 µs

hiccup mode

t

HICCUP

t

SS

Hiccup timeout 5.5 ms

Soft-start time coming out of hiccup mode 3.6 ms

THERMAL RESISTANCE

θ

JA

Note 1: Absolute maximum ratings indicate limits beyond which damage to the device may occur. Operating ratings indicate conditions for which the device

operates correctly. Operating Ratings do not imply guaranteed performance limits.

Note 2: Practical lower limit of VCC depends on selection of the external MOSFET. See the MOSFET GATE DRIVERS section under Application Information for

further details.

Note 3: ESD using the human body model which is a 100 pF capacitor discharged through a 1.5 kΩ resistor into each pin. Test method is per JESD22–A114.

Junction to Ambient Thermal Resistance 235 °C/W

www.national.com 4

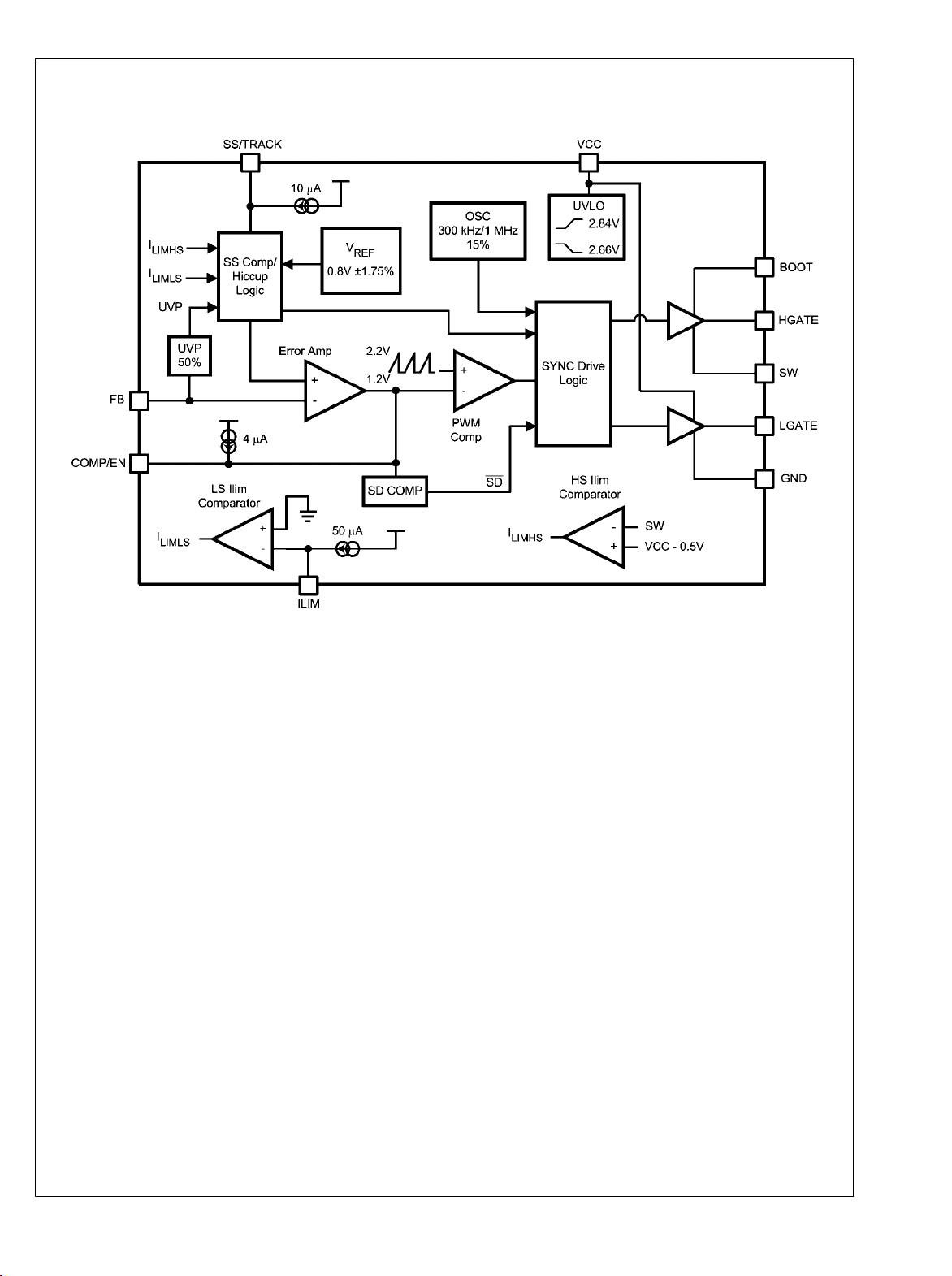

Block Diagram

LM3743

20177403

5 www.national.com

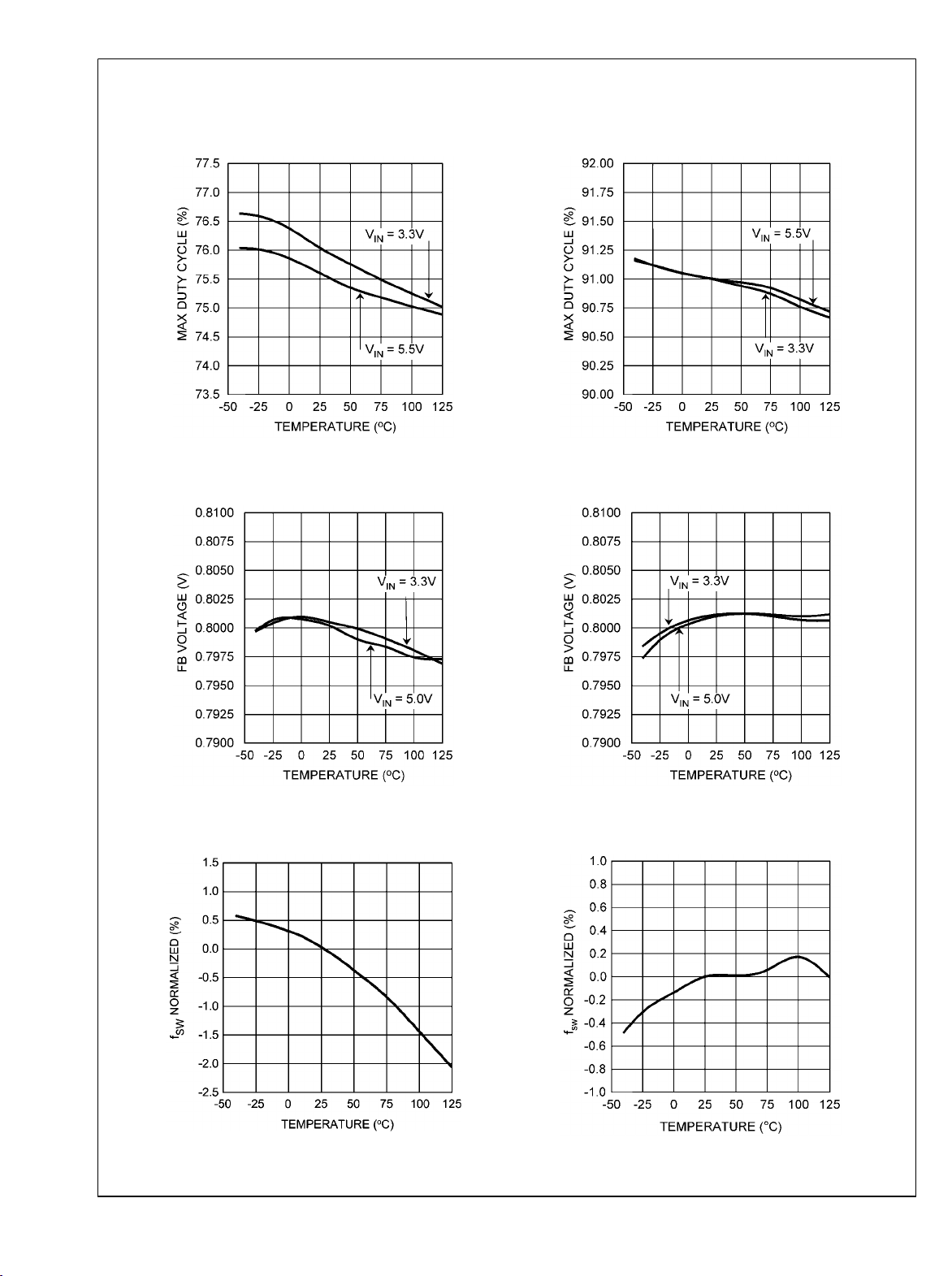

Typical Performance Characteristics V

= 3.3, TJ = 25°C, I

IN

= 1A unless otherwise specified.

LOAD

LM3743

D

vs Temperature

Max

fSW = 1 MHZ

FB vs Temperature

fSW = 1 MHZ

20177455

D

vs Temperature

Max

fSW = 300 kHz

FB vs Temperature

fSW = 300 kHz

20177456

20177457

Frequency vs Temperature

fSW = 1 MHz

20177459

www.national.com 6

20177458

Frequency vs Temperature

fSW = 300 kHz

201774a2

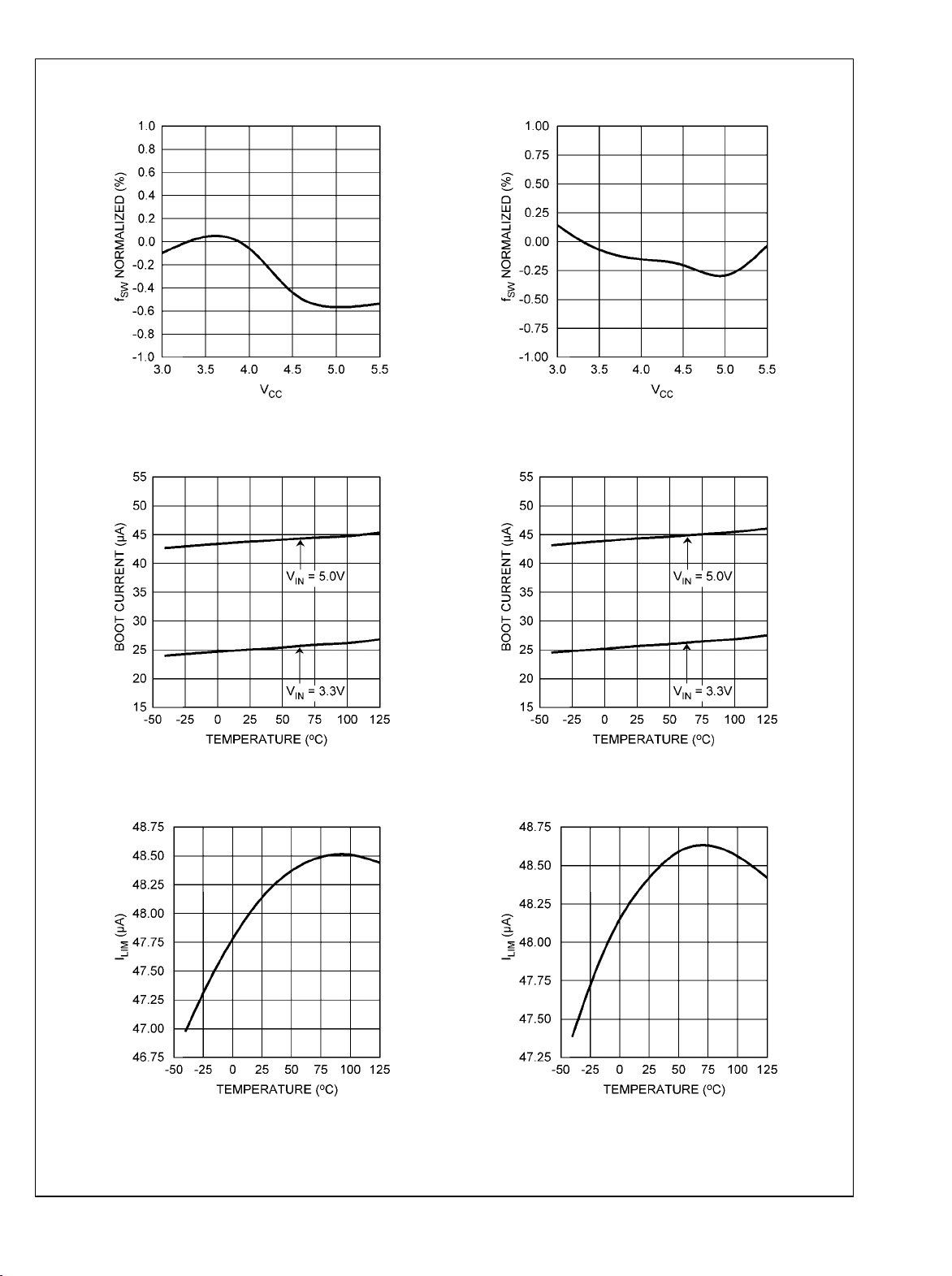

LM3743

Frequency vs V

fSW = 1 MHz

I

SHDN_BOOT

fSW = 1 MHz

CC

vs Temperature

20177461

Frequency vs V

fSW = 300 kHz

I

SHDN_BOOT

fSW = 300 kHz

CC

20177462

vs Temperature

I

vs Temperature

LIM

fSW = 1 MHz

20177463

20177465

20177464

I

vs Temperature

LIM

fSW = 300 kHz

20177466

7 www.national.com

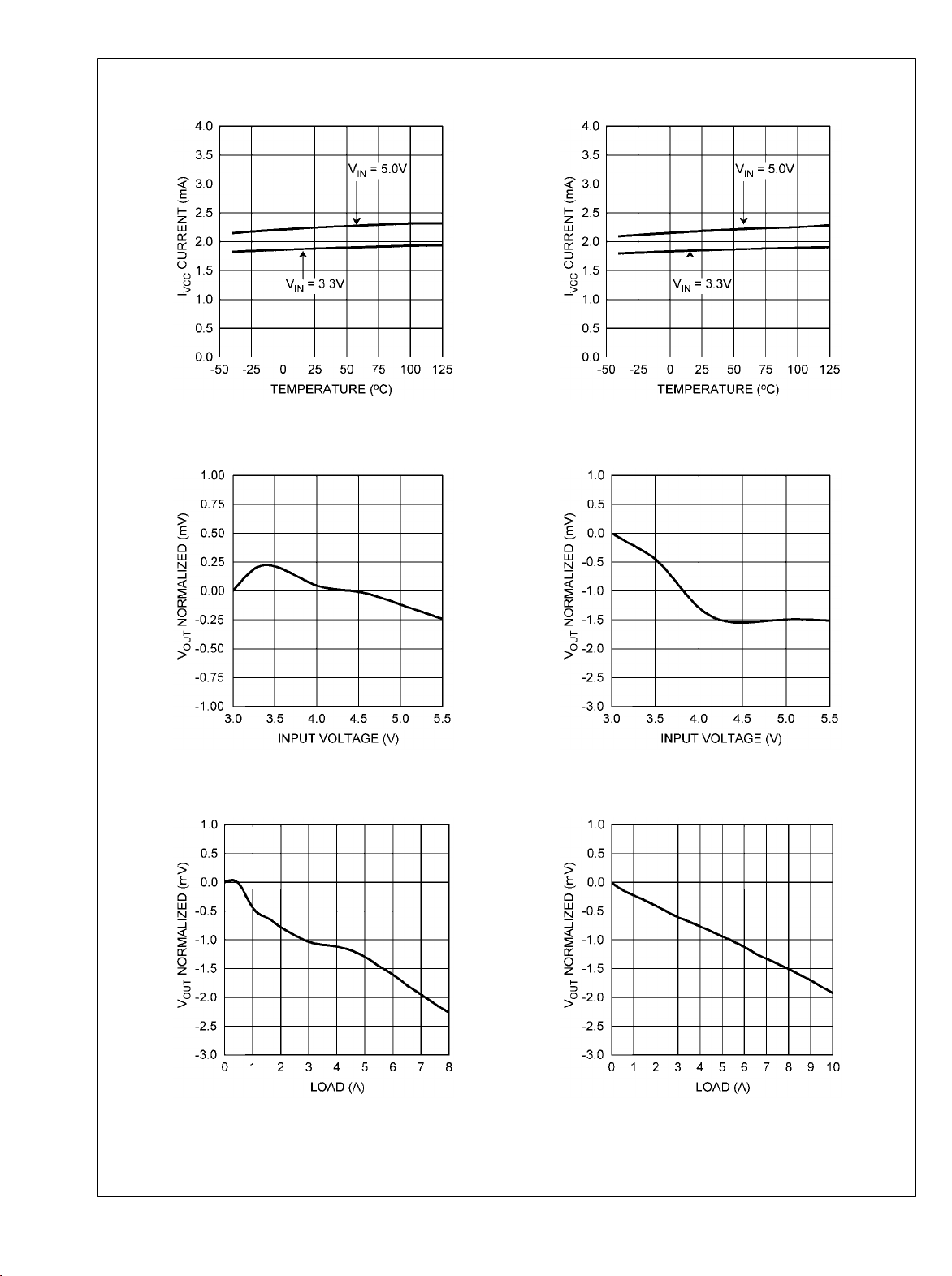

LM3743

I

vs Temperature

VCC

fSW = 1 MHz

I

vs Temperature

VCC

fSW = 300 kHz

V

= 1.2V, I

OUT

OUT

Load Regulation

VIN = 3.3V, fSW = 1 MHz

Line Regulation

= 1A, fSW = 300 kHz

20177467

20177469

V

= 1.5V, I

OUT

= 1A, fSW = 1 MHz

OUT

Load Regulation

VIN = 3.3V, fSW = 300 kHz

Line Regulation

20177468

20177470

20177471

www.national.com 8

20177472

Loading...

Loading...