DS92LV1212

16-40 MHz 10-Bit Bus LVDS Random Lock Deserializer

with Embedded Clock Recovery

General Description

The DS92LV1212 is an upgrade of the DS92LV1210. It

maintains all of the features of the DS92LV1210withtheadditional capability of locking to the incoming data stream

without the need of SYNC patterns. This makes the

DS92LV1212 useful in applications where the Deserializer

must be operated “open-loop”—without a feedback path

from the Deserializer to the Serializer. The DS92LV1212 is

designed to be used with the DS92LV1021 Bus LVDSSerializer. The DS92LV1212 receives a Bus LVDS serial data

stream and transforms it into a 10-bit wide parallel data bus

and separate clock. The reduced cable, PCB trace count

and connector size saves cost and makes PCB layout

easier. Clock-to-data and data-to-data skews are eliminated

since one input receives both clock and data bits serially.

The powerdown pin is used to save power by reducing the

supply current when the device is not in use. The Deserializer will establish lock to a synchronization pattern within

specified lock times but it can also lock to a data stream without SYNC patterns.

Features

n Clock recovery without SYNC patterns-random lock

n Guaranteed transition every data transfer cycle

n Chipset (Tx + Rx) power consumption

<

300mW (typ)

@

40MHz

n Single differential pair eliminates multi-channel skew

n 400 Mbps serial Bus LVDS bandwidth (at 40 MHz clock)

n 10-bit parallel interface for 1 byte data plus 2 control bits

or UTOPIA I Interface

n Synchronization mode and LOCK indicator

n Flow-through pinout for easy PCB layout

n High impedance on receiver inputs when power is off

n Programmable edge trigger on clock

n Footprint compatible with DS92LV1210

n Small 28-lead SSOP package-MSA

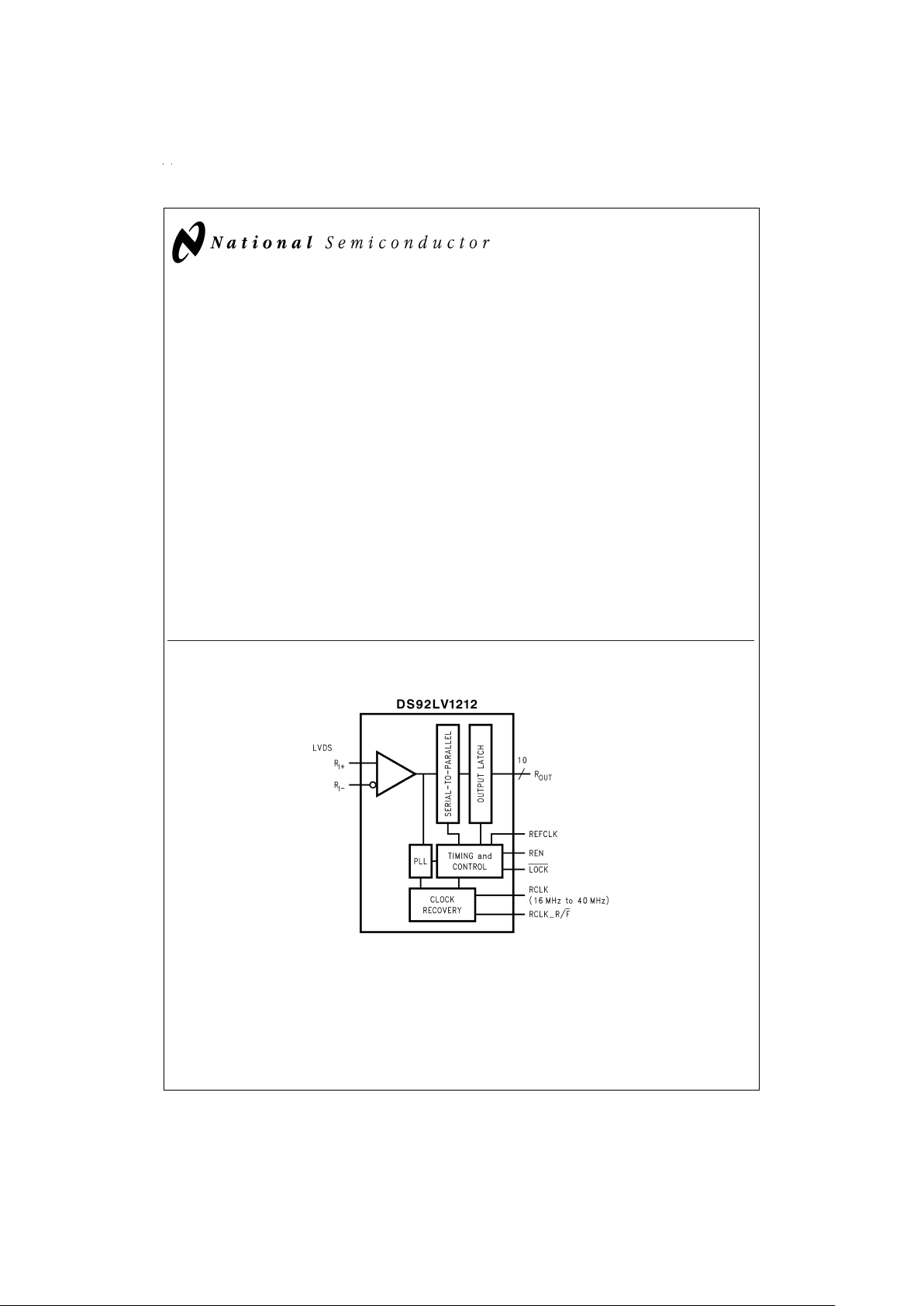

Block Diagram

TRI-STATE®is a registered trademark of National Semiconductor Corporation.

DS100982-1

April 1999

DS92LV1212 16-40 MHz 10-Bit Bus LVDS Random Lock Deserializer with Embedded Clock

Recovery

© 1999 National Semiconductor Corporation DS100982 www.national.com

Block Diagram (Continued)

Functional Description

The DS92LV1212 is a 10-bit Deserializer chip designed to

receive data over a heavily loaded differential backplanes at

clock speeds from 16 MHz to 40 MHz. It may also be used to

receive data over Unshielded Twisted Pair (UTP) cable.

The chip has three active states of operation: Initialization,

Data Transfer, and Resynchronization; and two passive

states: Powerdown and TRI-STATE

®

.

The following sections describe each operation and passive

state.

Initialization

Before data can be transferred the Deserializer must be initialized. The Deserializer should be powered up with the

PWRDN pin held low. After V

CC

stabilizes the PWRDN pin

can be forced high. The Deserializer is ready to lock to the

incoming data stream.

Step 1: When V

CC

is applied to the Deserializer, the respective outputs are held in TRI-STATE and internal circuitry is

disabled by on-chip power-on circuitry. When V

CC

reaches

V

CC

OK (2.5V) the PLL is ready to lock to incoming data or

synchronization patterns. The local clock is applied to the

REFCLK pin.

The Deserializer LOCK output will remain high while its PLL

is locking to the incoming data or to SYNC patterns on the input.

Step 2: The Deserializer PLL must synchronize to the Serializer to complete the initialization. The Deserializer will lock to

non-repetitive data patterns, however, the transmission of

SYNC patterns to the Deserializer enables the Deserializer

to lock to the Serializer signal within a specified time.

Control of the Serializer SYNC1/2 pins is left to the user. A

feedback loop between the LOCK pin is one recommendation. Another option is that one or both of the Serializer

SYNC inputs are asserted for at least 1024 cycles of TCLK

to initiate transmission of SYNC patterns. The Serializer will

continue to send SYNC patterns after the minimum of 1024

if either of the SYNC inputs remain high.

When the Deserializer detects edge transitions at the Bus

LVDS input it will attempt to lock to the embedded clock in-

formation. When the Deserializer locks to the Bus LVDS

clock, the LOCK output will go low. When LOCK is low the

Deserializer outputs represent incoming Bus LVDS data.

Data Transfer

Serialized data and clock bits (10+2 bits) are received at 12

times the TCLK frequency. For example, if TCLK is 40 MHz,

the serial rate is 40 x 12 = 480 Mega bits per second. Since

only 10 bits are from input data, the serial “payload” rate is

10 times the TCLK frequency. For instance, if TCLK = 40

MHz, the payload data rate is 40 x 10 = 400 Mbps. TCLK is

provided by the data source and must be in the range 16

MHz to 40 MHz nominal.

The LOCK pin on the Deserializer is driven low when it is

synchronized with the Serializer. The Deserializer locks to

the embedded clock and uses it to recover the serialized

data. ROUT data is valid when LOCK is low. Otherwise

ROUT0–ROUT9 is invalid.

RCLK pin is the reference to data on the ROUT0-ROUT9

pins. The polarity of the RCLK edge is controlled by the

RCLK_R/F input.

ROUT(0-9), LOCK and RCLK outputs will drive a minimum

of three CMOS input gates (15 pF load) with 40 MHz clock.

Resynchronization

The Deserializer LOCK pin driven low indicates that the Deserializer PLL is locked to the embedded clock edge. If the

Deserializer loses lock, the LOCK output will go high and the

outputs (including RCLK) will be TRI-STATE.

The LOCK pin must be monitored by the system to detect a

loss of synchronization. The system can arrange to pulse the

Serializer SYNC1 or SYNC2 pin to resynchronize. There are

multiple approaches possible. One recommendation is to

provide a feedback loop using the LOCK pin itself to control

the sync request of the Serializer (SYNC1 or SYNC2). A

minimum of 1024 sync patterns are needed to resynchronize. Dual SYNC pins are provided for multiple control in a

multi-drop application.

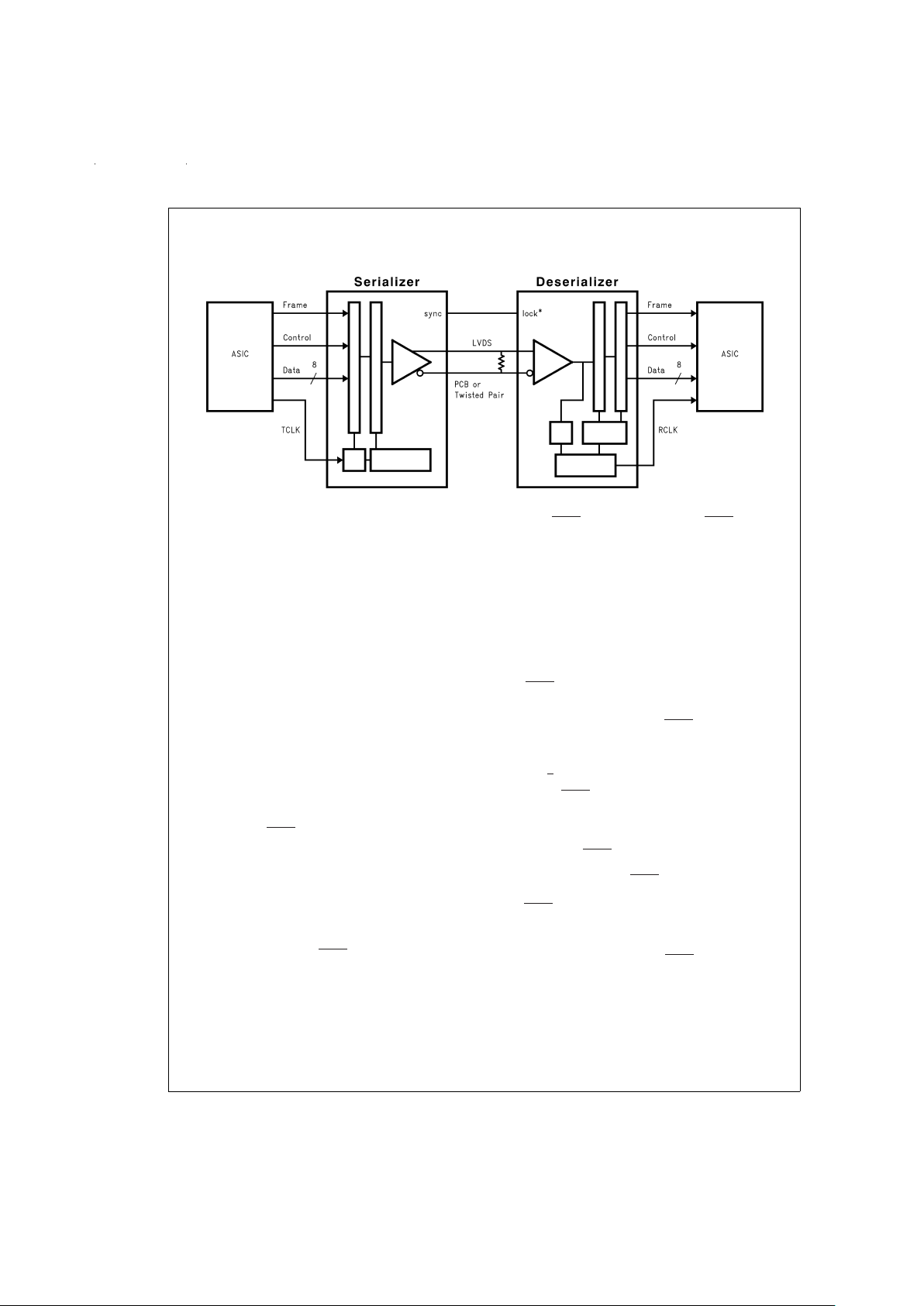

Application

DS100982-2

www.national.com 2

Random Lock Initialization and

Resynchronization

The initialization and resynchronization methods described

in their respective sections are the fastest ways to establish

the link between the Serializer and Deserializer, however,

the DS92LV1212can attain lock to a data stream without requiring special SYNC patterns to be sent by the Serializer.

This allows the DS92LV1212 to be used in applications

where the Deserializer must operate “open-loop” and supports hot insertion into a running backplane. Because the

data stream is essentially random the time for the

DS92LV1212 to attain lock is variable and cannot be predicted. The primary constraint on the “random” lock time is

the initial phase relation when the Deserializer is powered

up. The data contained in the data stream can also affect

lock time. Typical lock times for random data have a mean of

570us and a max of 4.9ms.

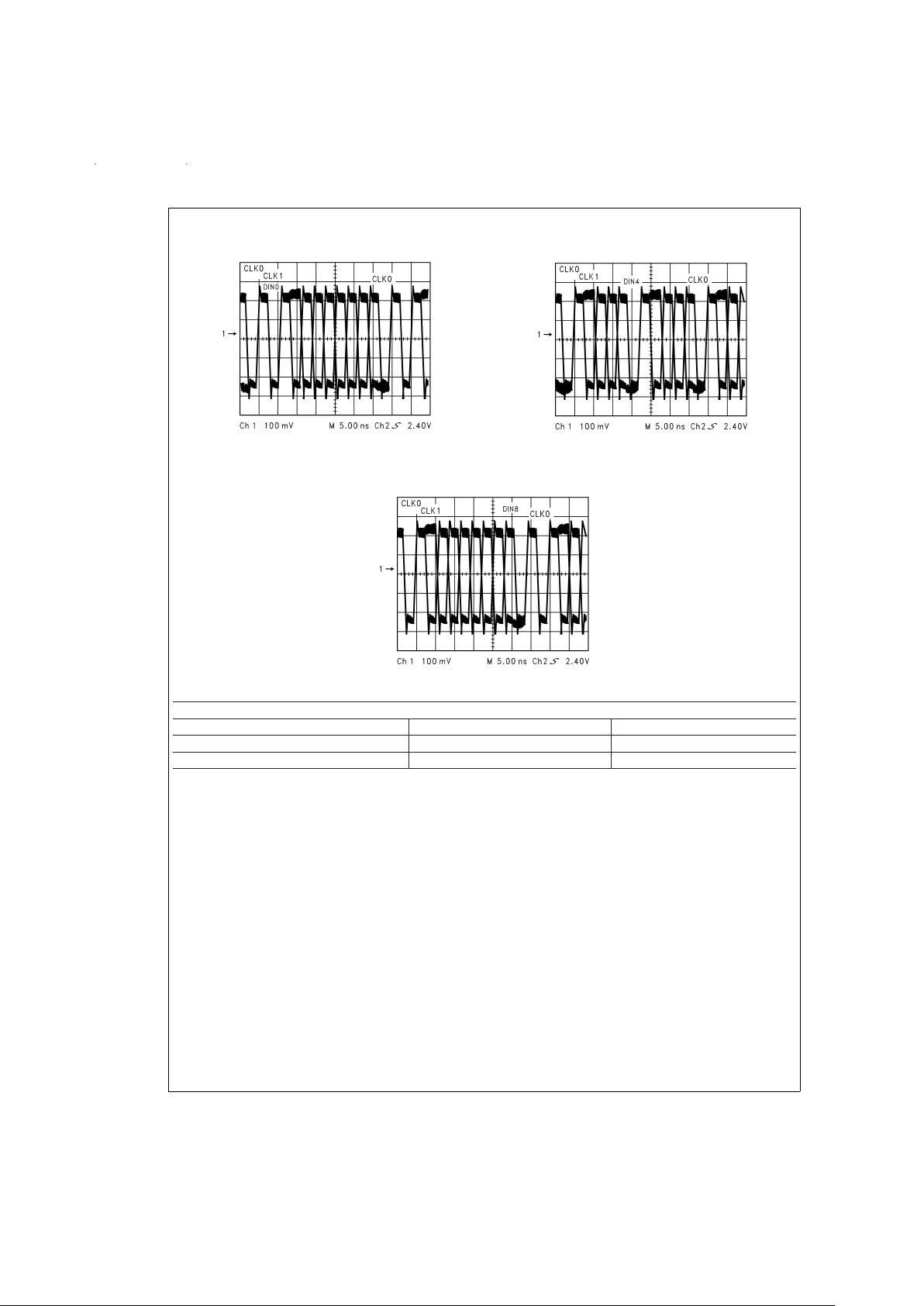

If a specific pattern is repetitive the Deserializer could be

misled into a “false lock” - falsely recognizing the data pattern as the clocking bits. We refer to such a pattern as a repetitive multi-transition, RMT.Thisis when there is more than

one Low-High transition in a single clock cycle. This occurs

when any bit, except DIN 9, is held at a low state and the adjacent bit is held high creating a 0-1 transition. In the worst

case the Deserializer could become locked to the data pattern rather than the clock. Circuitry within the DS92LV1212

can detect that the possibility of “false lock” exists (by detecting that there is more than 1 potential position for clocking

bits) and will prevent the LOCK* output from becoming active until the potential “false lock” pattern changes. It is expected that the data will eventually change causing the Deserializer to lose lock to the data pattern and continue

searching for the clock bits in the serial data stream. A

graphical representation of a few cases of RMT is shown

below. Please note that RMT applies to bits DIN0-DIN8.

Powerdown

The Powerdown state is a low power sleep mode that can be

used to reduce power when there is no data to be transferred. Powerdown is entered when PWRDN and REN are

driven low on the Deserializer. In Powerdown, the PLL is

stopped and the outputs go into TRI-STATE, disabling load

current and also reducing supply current to the milliamp

range. To exit Powerdown, PWRDN is driven high.

Both the Serializer and Deserializer must re-initialize and resynchronize before data can be transferred. Initialization of

the Serializer takes 1024 TCLK cycles. The Deserializer will

initialize and assert LOCK high until it is locked to the Bus

LVDS clock.

TRI-STATE

For the Deserializer, TRI-STATE is entered when the REN

pin is driven low. This will TRI-STATE the receiver output

pins (ROUT0–ROUT9), LOCK and RCLK.

www.national.com3

RMT Patterns

Order Numbers

NSID Function Package

DS92LV1021TMSA Serializer MSA28

DS92LV1212TMSA Deserializer MSA28

DS100982-23

DIN0 Held Low-DIN1 Held High Creates an RMT Pattern

DS100982-24

DIN4 Held Low-DIN5 Held High Creates an RMT Pattern

DS100982-25

DIN8 Held Low-DIN9 Held High Creates an RMT Pattern

www.national.com 4

Loading...

Loading...