NSC DS34LV87TMX, DS34LV87TM Datasheet

DS34LV87T

Enhanced CMOS Quad Differential Line Driver

General Description

The DS34LV87T is a high speed quad differential CMOS

driver that meets the requirements of both TIA/EIA-422-B

and ITU-T V.11. The CMOS DS34LV87T features low static

I

CC

of 100 µA max which makes it ideal for battery powered

and power conscious applications. The TRI-STATE

®

enable,

EN, allows the device to be disabled when the device is not

in use tominimizepower.The dual enable scheme allows for

flexibility in turning devices on or off.

Protection diodes protect all the driver inputs against electrostatic discharge. The driver and enable inputs (DI and EN)

are compatible with LVTTL and LVCMOS devices. Differential outputs have the same V

OD

(≥2V) guarantee as the 5V

version. The outputs have enhanced ESD Protection providing greater than 7 kV tolerance.

Features

n Meets TIA/EIA-422-B (RS-422) and ITU-T V.11

recommendation

n Interoperable with existing 5V RS-422 networks

n Guaranteed V

OD

of 2V min over operating conditions

n Balanced output crossover for low EMI (typical within 40

mV of 50%voltage level)

n Low power design (330 µW 3.3V static)

n ESD ≥ 7 kV on cable I/O pins (HBM)

n Industrial temperature range

n Guaranteed AC parameter:

— Maximum driver skew: 2 ns

— Maximum transition time: 10 ns

n Pin compatible with DS26C31

n Available in SOIC packaging

Connection Diagram Truth Table

Enables Input Outputs

EN DI DO+ DO−

LX Z Z

HH H L

HL L H

L = Low logic state

X = Irrelevant

H = High logic state

Z = TRI-STATE

TRI-STATE®is a registered trademark of National Semiconductor Corporation.

Dual-In-Line Package

DS012645-1

Top View

Order Number DS34LV87TM or DS34LV87TN

See NS Package Number M16A or N16A

January 1997

DS34LV87T Enhanced CMOS Quad Differential Line Driver

© 1998 National Semiconductor Corporation DS012645 www.national.com

Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Supply Voltage (V

CC

) −0.5V to +7V

Enable Input Voltage (EN) −0.5V to V

CC

+ 0.5V

Driver Input Voltage (D

I

) −0.5V to VCC+ 0.5V

Clamp Diode Current

±

20 mA

DC Output Current, per pin

±

150 mA

Driver Output Voltage

(Power Off: DO+, DO−) −0.5V to +7V

Maximum Package Power Dissipation +25˚C

M Package 1226 mW

N Package 1736 mW

Derate M Package 9.8 mW/˚C above +25˚C

Derate N Package 13.89 mW/˚C above +25˚C

Storage Temperature Range −65˚C to +150˚C

Lead Temperature Range

(Soldering, 4 sec.) +260˚C

ESD Ratings

(HBM, 1.5k, 100 pF)

Driver Outputs ≥ 7kV

Other Pins ≥ 2.5 kV

Recommended Operating

Conditions

Min Typ Max Units

Supply Voltage (V

CC

) 3.0 3.3 3.6 V

Operating Free Air

Temperature Range (T

A

)

DS34LV87T −40 25 +85 ˚C

Input Rise and Fall Time 500 ns

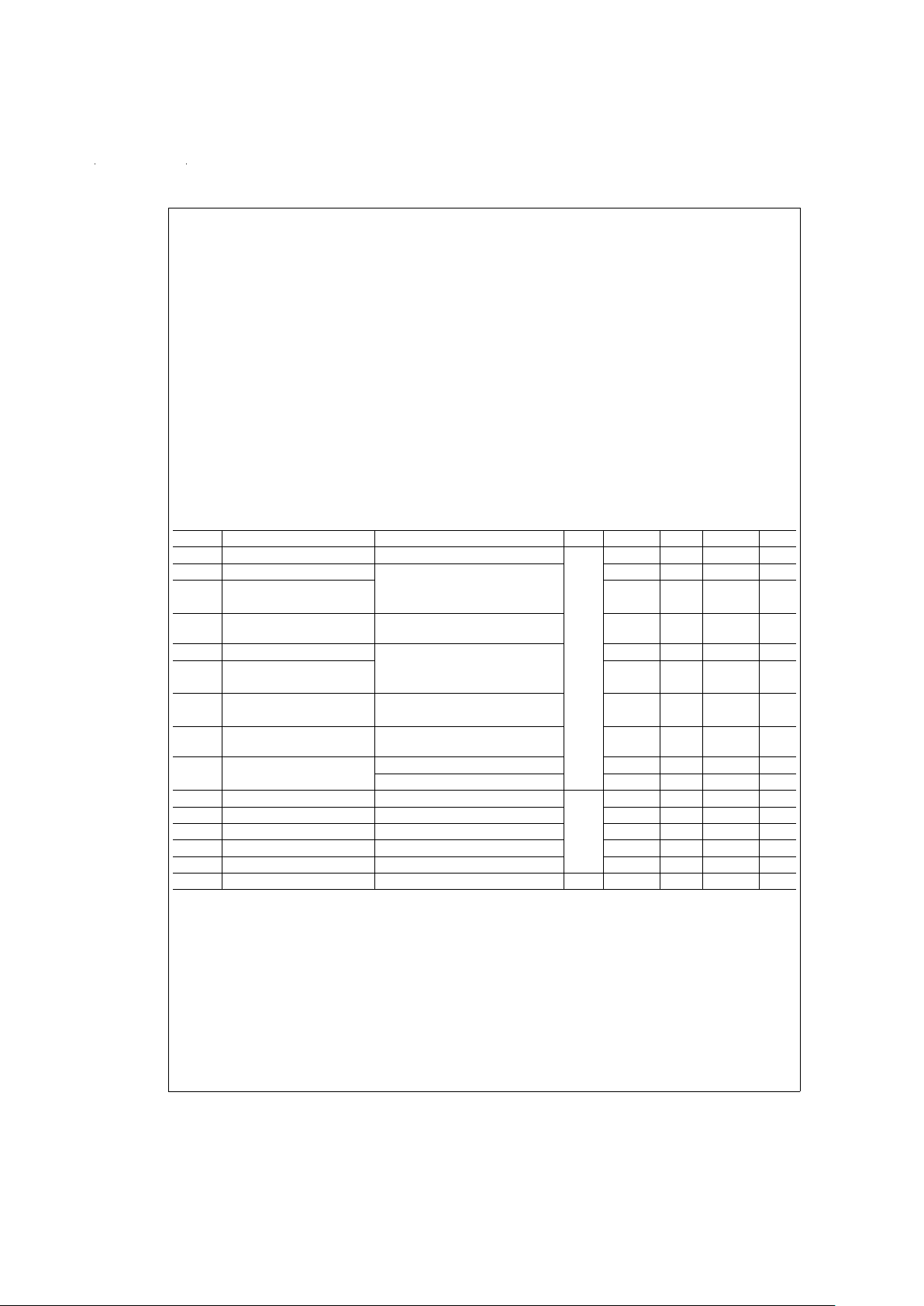

Electrical Characteristics (Notes 2, 3)

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified

Symbol Parameter Conditions Pin Min Typ Max Units

V

OD1

Output Differential Voltage RL=∞, (No Load) DO+, 3.3 4.0 V

V

OD2

Output Differential Voltage RL= 100Ω

Figure 1

DO− 2 2.6 V

∆V

OD2

Change in Magnitude of −400 7 400 mV

Output Differential Voltage

V

OD3

Output Differential Voltage RL= 3900Ω (V.11),

Figure 1

(Note 7)

3.2 3.5 V

V

OC

Common Mode Voltage RL= 100Ω

Figure 1

1.5 2 V

∆V

OC

Change in Magnitude of −400 6 400 mV

Common Mode Voltage

I

OZ

TRI-STATE Leakage V

OUT=VCC

or GND

±

0.5

±

20 µA

Current Drivers Disabled

I

SC

Output Short Circuit Current V

OUT

=0V

V

IN=VCC

or GND (Note 4)

−40 −70 −150 mA

I

OFF

Output Leakage Current VCC= 0V, V

OUT

= 3V 0.03 100 µA

V

CC

= 0V, V

OUT

= −0.25V −0.08 −100 µA

V

IH

High Level Input Voltage DI, 2.0 V

CC

V

V

IL

Low Level Input Voltage EN GND 0.8 V

I

IH

High Level Input Current VIN=V

CC

10 µA

I

IL

Low Level Input Current VIN= GND −10 µA

V

CL

Input Clamp Voltage IIN= −18 mA −1.5 V

I

CC

Power Supply Current No Load, VIN(all) = VCCor GND V

CC

100 µA

www.national.com 2

Switching Characteristics (Notes 5, 6)

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified

Symbol Parameter Conditions Min Typ Max Units

t

PHLD

Differential Propagation Delay RL= 100Ω,CL=50pF

(

Figures 2, 3

)

6 10.5 16 ns

High to Low

t

PLHD

Differential Propagation Delay 6 11 16 ns

Low to High

t

SKD

Differential Skew 0.5 2.0 ns

|t

PHLD–tPLHD

|

t

SK1

Skew, Pin to Pin (same device) 1.0 2.0 ns

t

SK2

Skew, Part to Part (Note 8) 3.0 5.0 ns

t

TLH

Differential Transition Time 4.2 10 ns

Low to High (20%to 80%)

t

THL

Differential Transition Time 4.7 10 ns

High to Low (80%to 20%)

t

PHZ

Disable Time High to Z (

Figures 4, 5

)1220ns

t

PLZ

Disable Time Low to Z 920ns

t

PZH

Enable Time Z to High 22 32 ns

t

PZL

Enable Time Z to Low 22 32 ns

f

MAX

Maximum Operating Frequency 32 MHz

(Note 9)

Note 1: “Absolute Maximum Ratings” are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device

should be operated at these limits. The table of “Electrical Characteristics” specifies conditions of device operation.

Note 2: Current into device pins is defined as positive. Current out of device pins is defined as negative. All voltages are referenced to ground except differential voltages V

OD1,VOD2,VOD3

.

Note 3: All typical values are given for V

CC

= 3.3V and TA= +25˚C.

Note 4: Only one output shorted at a time. The output (true or complement) is configured High.

Note 5: f = 1 MHz, t

r

and tf≤ 6ns(10%to 90%).

Note 6: See TIA/EIA-422-B specifications for exact test conditions.

Note 7: This specification limit is for compliance with TIA/EIA-422-B and ITU-T V.11.

Note 8: Devices are at the same V

CC

and within 5˚C within the operating temperature range.

Note 9: All channels switching, output duty cycle criteria is 40%/60%measured at 50%. This parameter is guaranteed by design and characterization.

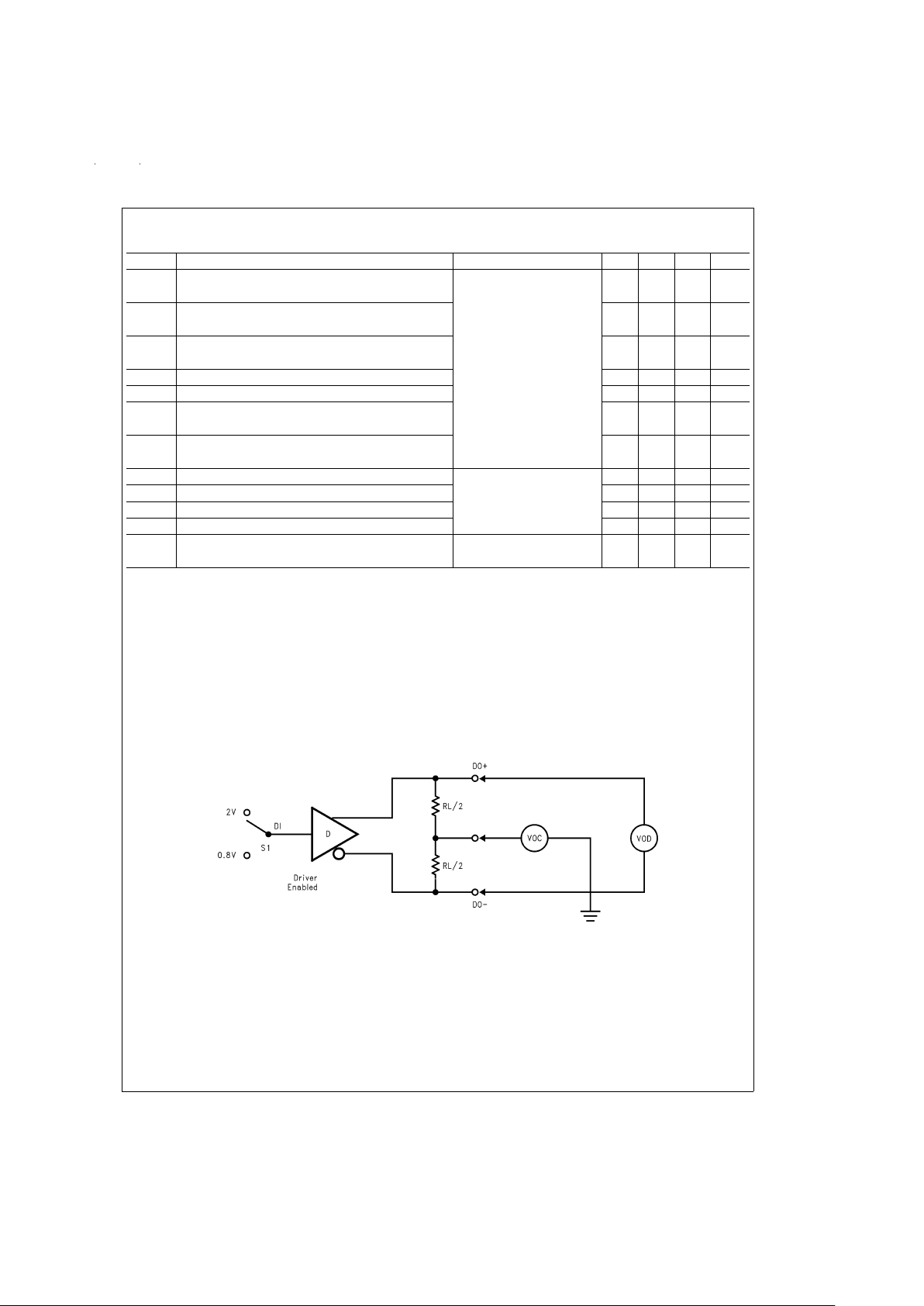

Parameter Measurement Information

DS012645-2

FIGURE 1. Differential Driver DC Test Circuit

www.national.com3

Loading...

Loading...