NPC SM8702AM Datasheet

2 ×

6 ×

2 ×

1 ×

1 ×

SM8702AM

NIPPON PRECISION CIRCUITS INC.

Clock Generator IC

OVERVIEW

The SM8702AM is a clock generator IC that can generate clock signals up to and exceeding 100MHz for personal computer (PC) motherboards. It uses a single 14.318MHz crystal oscillator element and 2 built-in PLLs

to simultaneously and independently generate 2 CPU clocks, 6 PCI bus clocks, 2 reference clocks with the

same frequency as the crystal element, 48MHz USB interface clock, and 24MHz Super I/O chip clock outputs.

It also has 14 outputs that can function as SDRAM clocks by buffering an external input SDRAM clock.

FEATURES

■

Intel

Pentium

compatibles supported

■

2.5/3.3V CPU clock outputs and IOAPIC clock

output

■

14 × SDRAM clock outputs (3 DIMMs)

■

CPU clock outputs

(60), 66, 75, 83, 95, 100, 103, 112, (124), 133MHz

CPU/SDRAM clock frequencies. Values in parentheses are available as mask options.

■

PCI bus clock outputs (one free-running output)

33MHz or 1/2, 1/3, 1/4 of the CPU clock frequency

■

reference clock outputs and 1 × IOAPIC clock

output

14.318MHz REF/IOAPIC clock frequency

■

48MHz USB interface clock output

■

24MHz clock output for Super I/O chip

2

■

I

C serial data bus for frequency/mode output con-

trol

■

CPU-stop and PCI-stop functions

■

Spread Spectrum Clock Generator (SSCG) outputs

Center spread/Down spread, ± 0.5% or ± 1.5%

■

3.3V (VDD) and 2.5/3.3V (VDDL) supply voltages

■

48-pin SSOP package (pin compatible with

ICS9148-26)

II, Pentium

III, and AMD x86-

APPLICATIONS

■

PC motherboards using Intel

tium

II/III, AMD-K6 devices, and x86 architec-

ture CPUs

Pentium

, Pen-

PINOUT

48-pin SSOP (300 mil)

(Top view)

148

VDD1

REF0

VSS

XT

XTN

PCICLK_F/MODE

VDD2

PCICLK0 SDRAM13

VSS

PCICLK1

PCICLK2

PCICLK3

PCICLK4

VDD2

BUFFERIN

VSS

SDRAM11/CPU_STOP#

SDRAM10/PCI_STOP#

VDD3

SDRAM9

SDRAM8

VSS

SDATA

SCLK

24 25

SM8702AM

ORDERING INFORMATION

De vice Pack ag e

SM8702AM 48-pin SSOP

VDDL1

IOAPIC

REF1/FS2

VSS

CPUCLK0

CPUCLK1

VDDL2

SDRAM12

VSS

SDRAM0

SDRAM1

VDD3

SDRAM2

SDRAM3

VSS

SDRAM4

SDRAM5

VDD3

SDRAM6

SDRAM7

VDD4

48MHz/FS0

24MHz/FS1

Intel

and Pentium

are registered trademarks of Intel co..

AMD and AMD-K6 are registered trademarks of Advanced Micro Devices, Inc..

2

I

C Bus is a registered trademark of Philips Electronics N. V..

preliminary

NIPPON PRECISION CIRCUITS—1

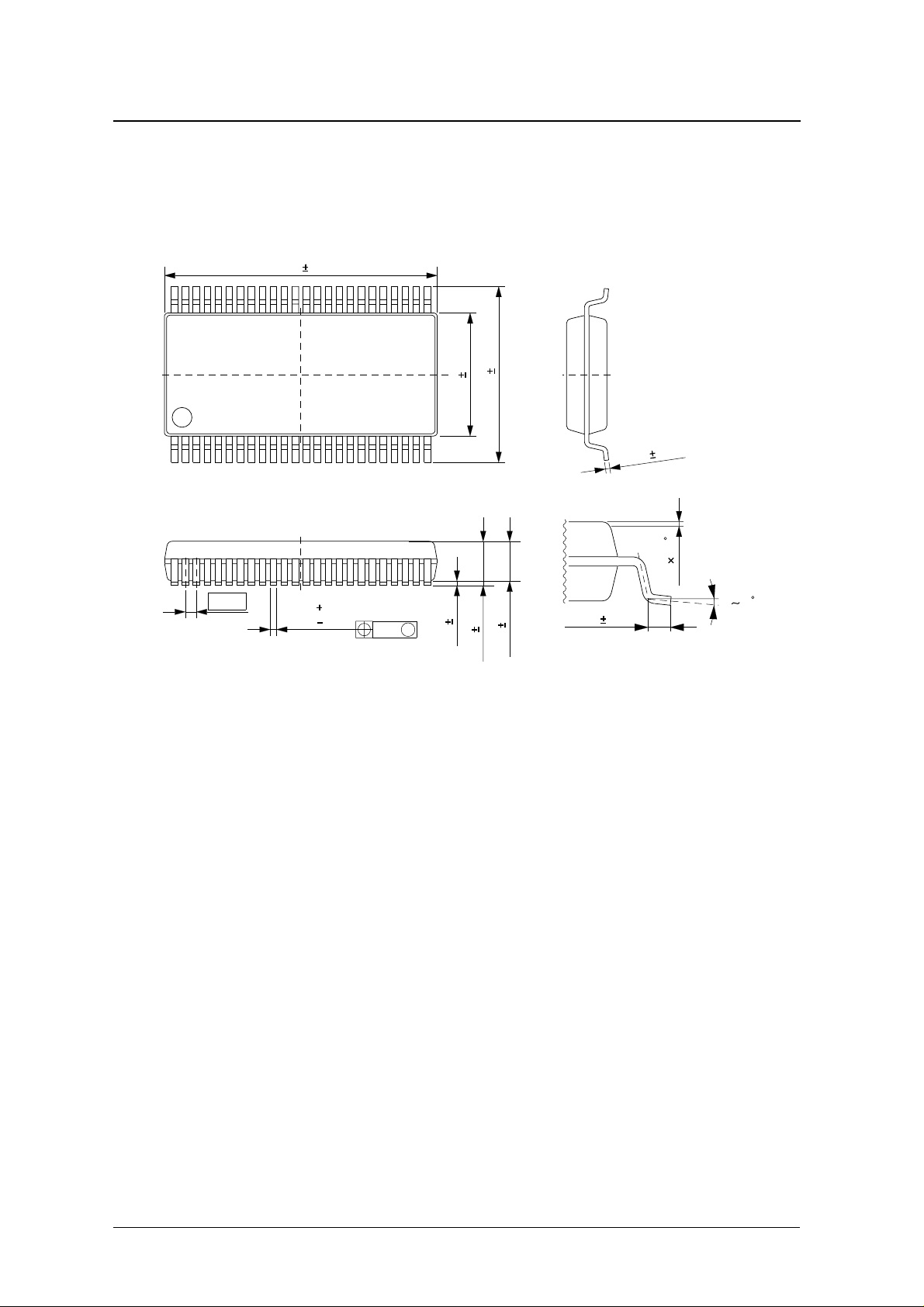

PACKAGE DIMENSIONS

(Unit: mm)

15.85 0.1

SM8702AM

7.50 0.05

10.285 0.125

0.635

0.05

0.25 0.03

0.12

0.20 0.02

0.5 45

0

M

0.3 0.1

2.59 0.15

2.29 0.05

0.80 0.1

8

preliminary

NIPPON PRECISION CIRCUITS—2

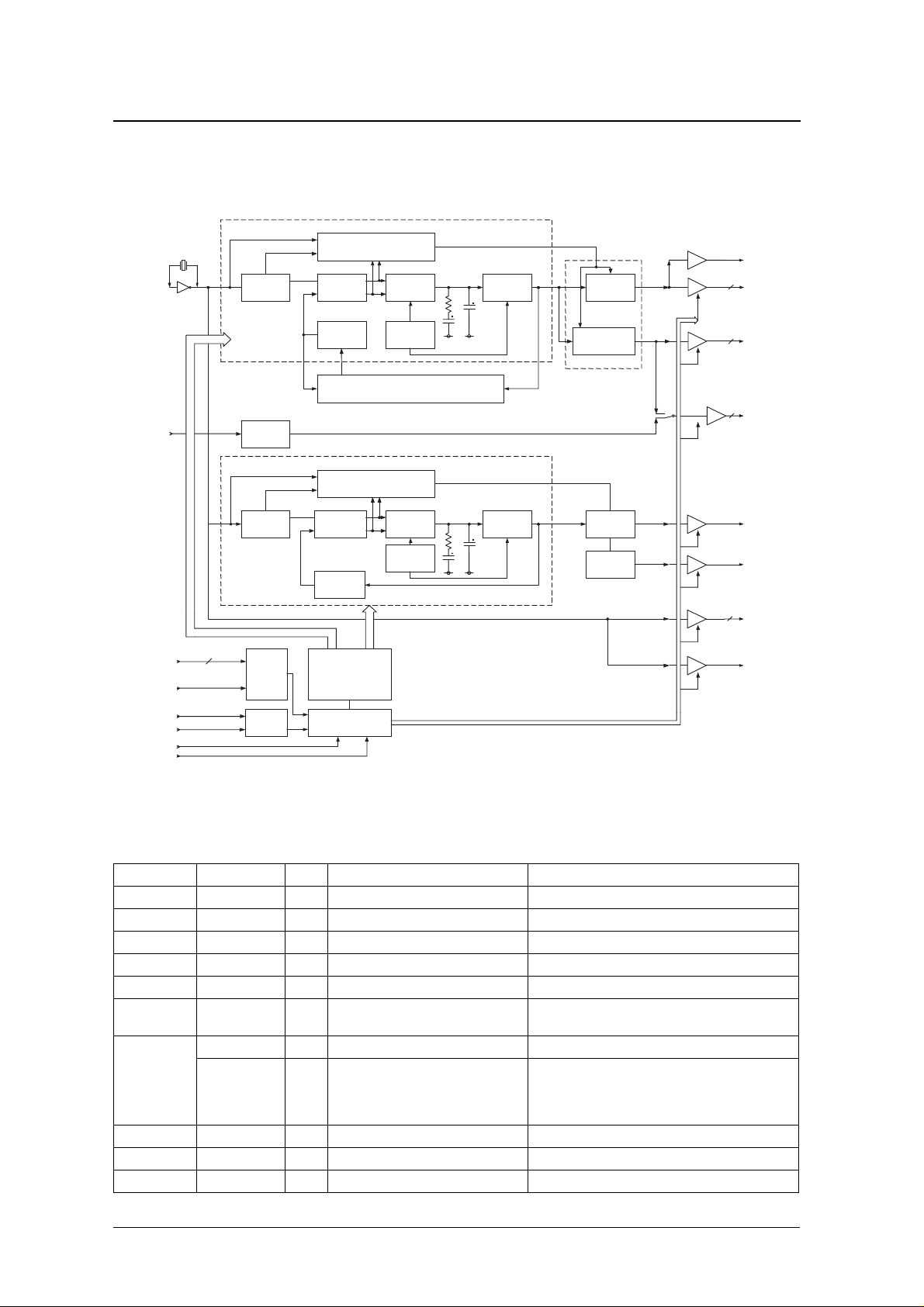

BLOCK DIAGRAM

SM8702AM

XT XTN

BUFFERIN

FS[0:2]

MODE

Unlock Detector

R-Countor

Buff. Amp.

R-Countor

3

I/O

Latch

Phase

Detector

N-Countor

Phase

Detector

N-Countor

ROM

Unlock Detector

Charge

Pump

Current

Source

SS_CONTROLLER

Charge

Pump

Current

Source

(1st PLL)

VCO

(2nd PLL)

VCO

DIV/3

to DIV/6

DIV/2

DIV/3

1/2

(MS)

5

2

14

2

PCICLK_F

PCICLK

[0:4]

CPUCLK

[0:1]

SDRAM

[0:13]

48MHz

(USB)

24MHz

(Super I/O)

REF[0:1]

IOAPIC

SDATA

SCLK

CPU_STOP#

PCI_STOP#

I C

2

Control Logic

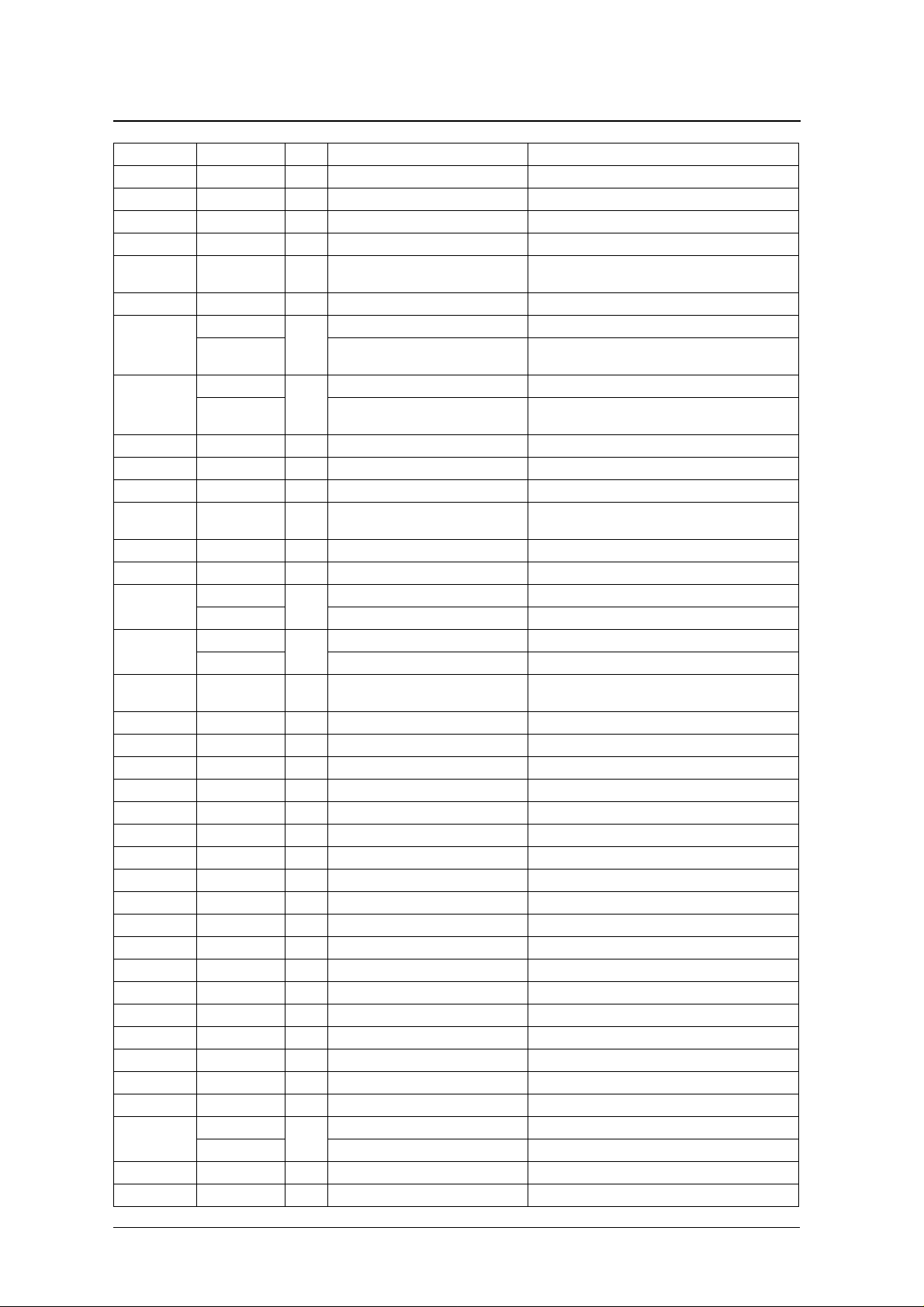

PIN DESCRIPTION

Number Name I/O Function Notes

1 VDD1 – 3.3V supply XT, XTN oscillator, REF[0:1] buffer, stop logic, 3.3V line

2 REF0 I/O 14.318MHz reference clock output

3 VS S – Ground Crystal oscillator, REF[0:1], 3.3Vline

4 X T I Cr ystal oscillator input

5 XT N O C r ystal oscillator output

6 VDD2 – 3.3V supply

PCICLK_F O PCI bus free-running clock output

7

MODE I Mode settings (latch input)

preliminary

8 PCICLK0 O PCI bus clock output

9 V S S – Ground (3.3V supply) PCI clock output buffers, pre-buffer, stop logic

10 PCICLK1 O PCI bus clock output

PCI clock output buffers, pre-buffer, stop logic, and

internal circuit logic supply

CPU_STOP# (pin 17) and PCI_STOP# (pin 18) mode

select pin.

MODE = HIGH: Desktop mode

MODE = LOW: Mobile mode

NIPPON PRECISION CIRCUITS—3

SM8702AM

Number Name I/O Function Notes

11 PCICLK2 O PCI bus clock output

12 PCICLK3 O PCI bus clock output

13 PCICLK4 O PCI bus clock output

14 VDD2 – 3.3V supply PCI clock output buffers, pre-buffer, stop logic

15 BUFFERIN I SDRAM clock input

16 VS S – Ground (3.3V supply) SDRAM clock output buffers, pre-buffer, stop logic

SDRAM11

17

18

19 VDD3 – 3.3V supply SDRAM clock output buffers, pre-buffer, stop logic

20 SDRAM9 O SDRAM clock output

21 SDRAM8 O SDRAM clock output

22 VS S – Ground (3.3V supply)

23 SDATA I/O I

24 SCLK I I

25

26

27 VDD4 – 3.3V supply

28 SDRAM7 O SDRAM clock output

29 SDRAM6 O SDRAM clock output

30 VDD3 – 3.3V supply SDRAM clock output buffers, pre-buffer, stop logic

31 SDRAM5 O SDRAM clock output

32 SDRAM4 O SDRAM clock output

33 VS S – Ground (3.3V supply) SDRAM clock output buffers, pre-buffer, stop logic

34 SDRAM3 O SDRAM clock output

35 SDRAM2 O SDRAM clock output

36 VDD3 – 3.3V supply SDRAM clock output buffers, pre-buffer, stop logic

37 SDRAM1 O SDRAM clock output

38 SDRAM0 O SDRAM clock output

39 VS S – Ground (3.3V supply) SDRAM clock output buffers, pre-buffer, stop logic

40 SDRAM12 O SDRAM clock output

41 SDRAM13 O SDRAM clock output

42 VDDL2 – 2.5/3.3V supply CPU clock output buffers, pre-buffer, stop logic

43 CPUCLK1 O CPU clock output

44 CPUCLK0 O CPU clock output

45 V S S – Ground (2.5/3.3V supply) CPU clock output buffers, pre-buffer, stop logic

46

47 IOAPIC O 14.318MHz IOAPIC clock output

48 VDDL1 – 2.5/3.3V supply IOAPIC output buffer, pre-buffer, stop logic

CPU_STOP# CPU clock outputs stop control

SDRAM10

PCI_STOP# PCI clock outputs stop control

24MHz

FS 1 Frequency select 1 (latch input)

48MHz

FS 0 Frequency select 0 (latch input)

preliminary

REF1

FS 2 Frequency select 2 (latch input)

SDRAM clock output

I/O

SDRAM clock output

I/O

2

C s er ial data input

2

C clock input

24MHz clock output

I/O

48MHz USB clock output

I/O

14.318MHz reference clock output

I/O

Input on BUFFERIN is buffered and then output on

SDRAM[0:13]

In mobile mode (MODE = LOW), CPUCLK[0:1] tied LOW

when CPU_STOP# = LOW.

In mobile mode (MODE = LOW), PCICLK[0:4] tied LOW

when PCI_STOP# = LOW.

PLL and internal logic ground, I

24MHz/48MHz output ground

2

I

C interface , 24MHz/48MHz output supply, PLL and

internal logic supply

2

C interface ,

NIPPON PRECISION CIRCUITS—4

) −

) −

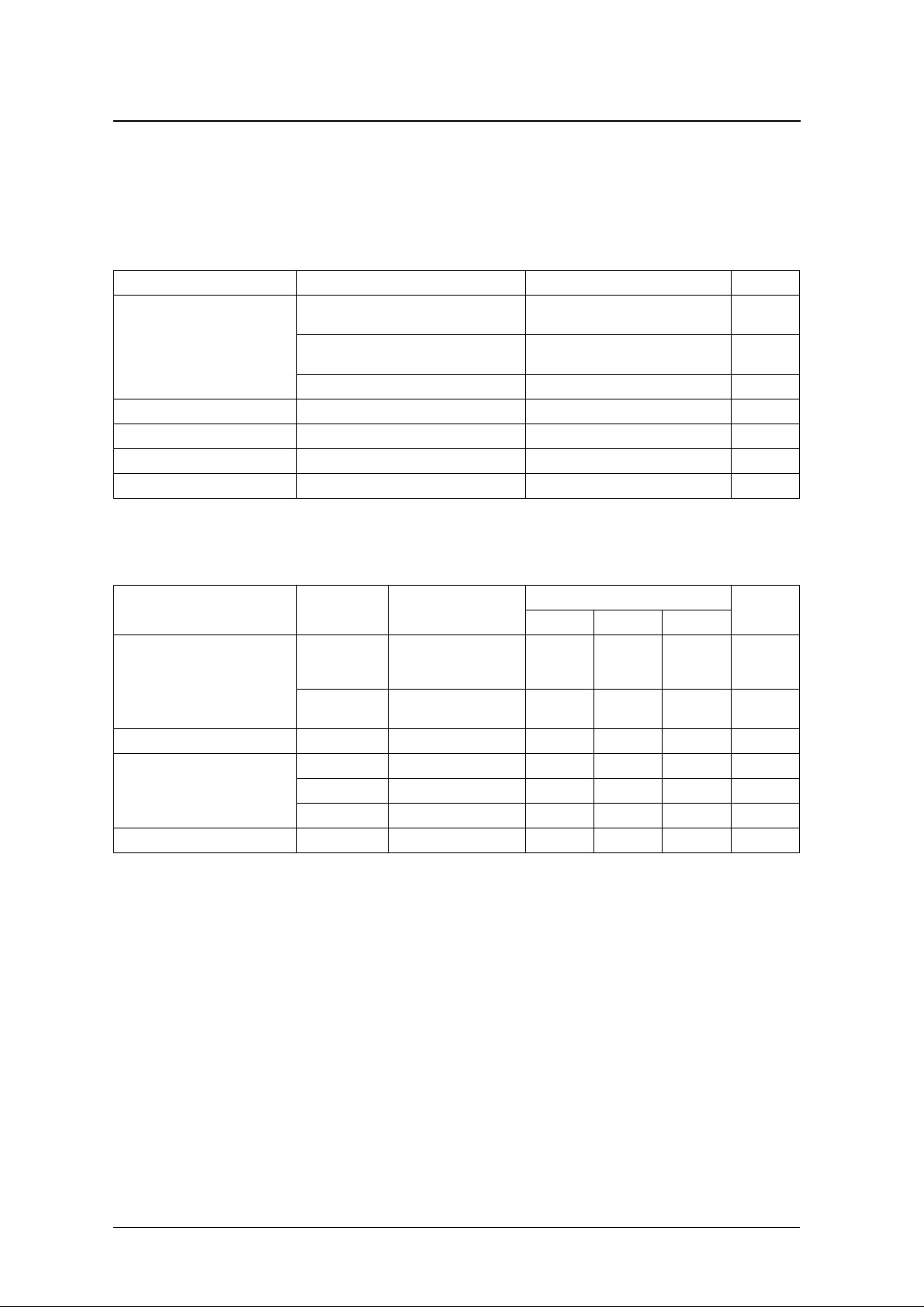

SPECIFICATIONS

Absolute Maximum Ratings

VDD:VDD1, VDD2, VDD3, VDD4

VDDL:VDDL1, VDDL2 unless otherwise noted.

Parameter Symbol Rating Unit

DD1

, V

(V

DD2

V

DDL1

V

DDL

V

OUT

(V

Supply voltage range

Input voltage range V

Output voltage range V

Storage temperature range T

Po w er dissipation P

SM8702AM

DD

, V

, V

DD3

DD4

, V

DDL2

SS

IN

stg

D

−

−

−

°

°

0.3 to 6.0 V

0.3 to 6.0 V

0V

0.3 to V

0.3 to V

+ 0.3 V

DD

+ 0.3 V

DD

55 to 125

0.8 W

C

Recommended Operating Conditions

V

= 0V

SS

Parameter Symbol Condition

(V

DD1

V

(V

DD3

DDL1

Supply voltages

Operating temperature range T

Maximum load capacitance

Reference frequency f

V

V

C

C

C

DD

, V

, V

DDL

, V

opr

L1

L2

L3

REF

Excludes internal core, CPU

,

clock and IOAPIC output

DD2

)

stages

DD4

Internal core, CPU clock

)

and IOAPIC output stages

DDL2

CPUCLK 10 – 20 pF

PCICLK, SDRAM 20 – 30 pF

RE F, 24/48MHz, IOAPIC 10 – 20 pF

Rating

Unit

min typ max

3.135 3.300 3.465 V

2.375 2.500 2.625 V

0–70

– 14.318 – MH z

C

preliminary

NIPPON PRECISION CIRCUITS—5

Loading...

Loading...