NIPPON PRECISION CIRCUITS INC.

NIPPON PRECISION CIRCUITS-1

SM5903BF

compression and non compression type

shock-proof memory controller

Overview

- 2-channel processing

- Serial data input

⋅ 2s complement, 16-bit/MSB first, right-justified

format

⋅ Wide capture function

(up to 3 × speed input rate)

- System clock input

⋅ 384fs (16.9344 MHz)

- Shock-proof memory controller

⋅ ADPCM compression method

⋅ 4-level compression mode selectable

4-bit compression mode 2.78 s/Mbit

5-bit compression mode 2.22 s/Mbit

6-bit compression mode 1.85 s/Mbit

Full-bit non compression mode 0.74 s/Mbit

⋅ 4 external DRAM configurations selectable

1 × 16M DRAM (4M × 4 bits, refresh cycle =

2048 cycle)

1 × or 2 × 4M DRAM (1M × 4 bits)

1 × 1M DRAM (256k × 4 bits)

- Microcontroller interface

⋅ Serial command write and status read-out

⋅ Data residual detector:

15-bit operation, 16-bit output

⋅ Forced mute

- Extension I/O

Microcontroller interface for external control

using 5 extension I/O pins

- +2.4 to +3.6 V operating voltage range

- Schmitt inputs

All input pins (including I/O pins) except CLK

(system clock)

- Reset signal noise elimination

Approximately 3.8 µs or longer (65 system

clock pulses) continuous LOW-level reset

- 44-pin QFP package (0.8 mm pin pitch)

The SM5903BF is a compression and non compression type shock-proof memory controller LSI for

compact disc players. The compression level can

be set in 4 levels, and external memory can be

selected from 4 options (1M, 4M, 4M× 2, 16M). It

operates from a 2.4 to 3.6 V supply voltage range.

Features

Ordering Information

SM5903BF 44pin QFP

NIPPON PRECISION CIRCUITS-2

SM5903BF

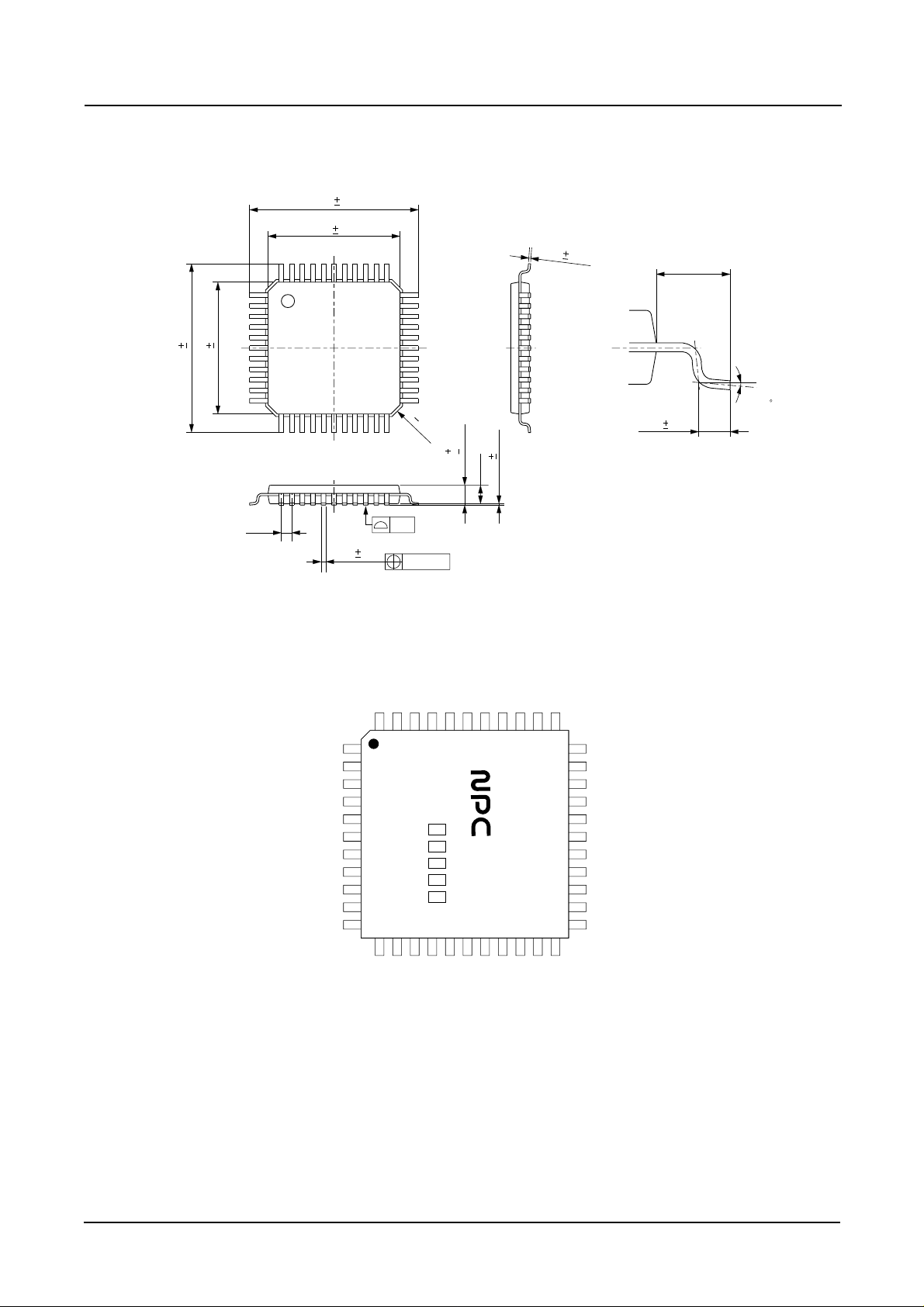

Package dimensions

(Unit: mm)

44-pin QFP

Pinout

(Top View)

0.80

0.20MAX

0.15

(1.40)

12.80 0.30

0.35

0.10

0.15 0.05

12.80 0.30

0.17

0.05

0 to 10

0.60 0.20

4

C0.7

10.00 0.30

10.00 0.30

1.50

0.10

0.20

(1.40)

1

2

3

4

5

6

7

8

9

10

11

1213141516171819202122

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

VDD2

UC1

UC2

UC3

UC4

UC5

N.C

NTEST

CLK

VSS

YSRDATA

NWE

D1

D0

D3

D2

NCAS

A10/ NCAS2

YMCLK

YMDATA

YMLD

YDMUTE

YLRCK

YSCK

ZSCK

ZLRCK

ZSRDATA

YFLAG

YFCLK

YBLKCK

NRESET

ZSENSE

VDD1

A3A2A1A0A4A5A6A7A8

A9

NRAS

SM590

3BF

NIPPON PRECISION CIRCUITS-3

SM5903BF

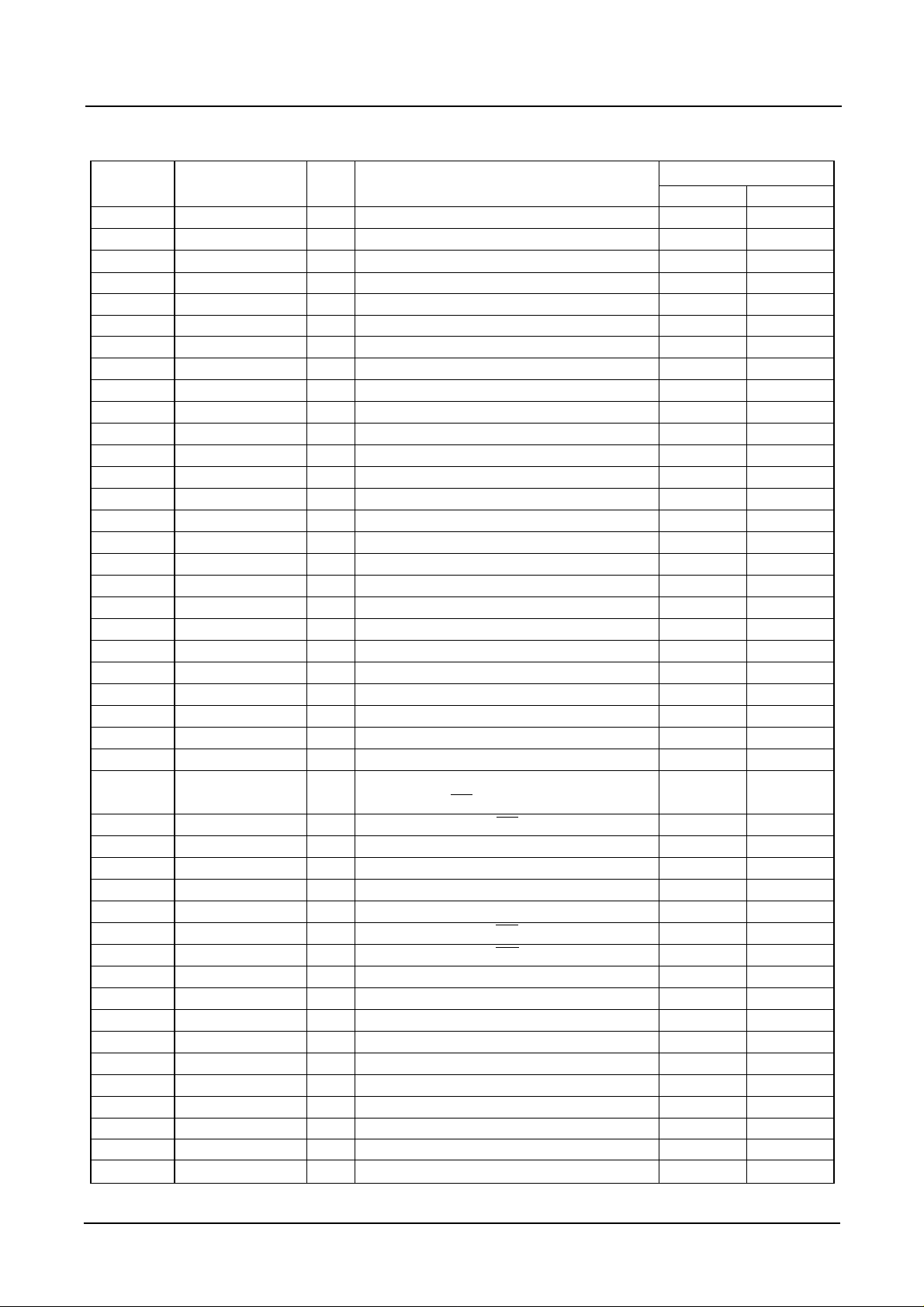

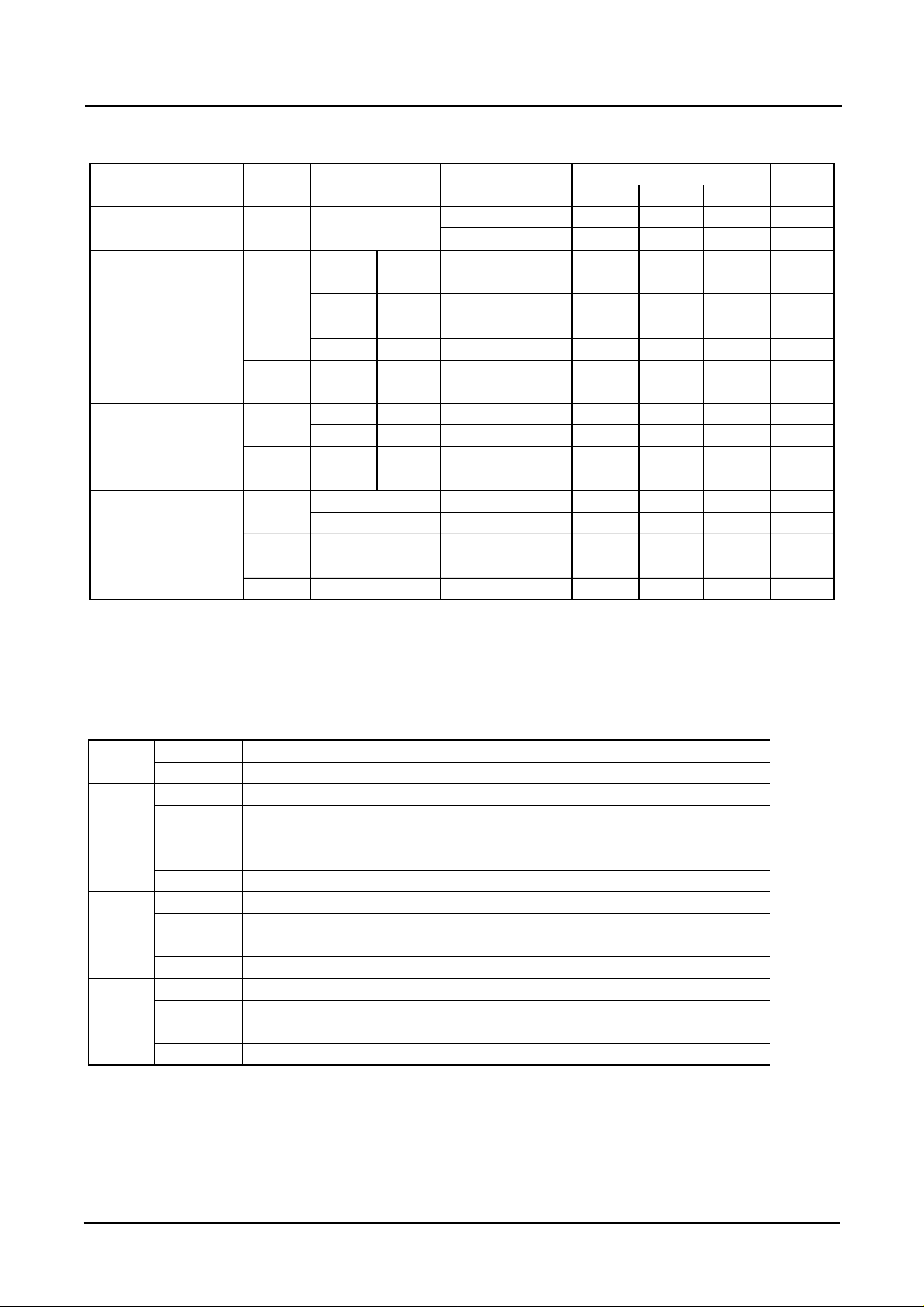

Pin description

Pin number Pin name I/O Function Setting

HL

1 VDD2 - VDD supply pin

2 UC1 Ip/O Microcontroller interface extension I/O 1

3 UC2 Ip/O Microcontroller interface extension I/O 2

4 UC3 Ip/O Microcontroller interface extension I/O 3

5 UC4 Ip/O Microcontroller interface extension I/O 4

6 UC5 Ip/O Microcontroller interface extension I/O 5

7 N.C -

8 NTEST Ip Test pin Test

9 CLK I 16.9344 MHz clock input

10 VSS - Ground

11 YSRDATA I Audio serial input data

12 YLRCK I Audio serial input LR clock Left channel Right channel

13 YSCK I Audio serial input bit clock

14 ZSCK O Audio serial output bit clock

15 ZLRCK O Audio serial output LR clock Left channel Right channel

16 ZSRDATA O Audio serial output data

17 YFLAG I Signal processor IC RAM overflow flag Overflow

18 YFCLK I Crystal-controlled frame clock

19 YBLKCK I Subcode block clock signal

20 NRESET I System reset pin Reset

21 ZSENSE O Microcontroller interface status output

22 VDD1 - VDD supply pin

23 YDMUTE I Forced mute pin Mute

24 YMLD I Microcontroller interface latch clock

25 YMDATA I Microcontroller interface serial data

26 YMCLK I Microcontroller interface shift clock

27 A10 O DRAM address 10

(NCAS2) O DRAM2 CAS control (with 2 DRAMs)

28 NCAS O DRAM CAS control

29 D2 I/O DRAM data input/output 2

30 D3 I/O DRAM data input/output 3

31 D0 I/O DRAM data input/output 0

32 D1 I/O DRAM data input/output 1

33 NWE O DRAM WE control

34 NRAS O DRAM RAS control

35 A9 O DRAM address 9

36 A8 O DRAM address 8

37 A7 O DRAM address 7

38 A6 O DRAM address 6

39 A5 O DRAM address 5

40 A4 O DRAM address 4

41 A0 O DRAM address 0

42 A1 O DRAM address 1

43 A2 O DRAM address 2

44 A3 O DRAM address 3

Ip : Input pin with pull-up resistor Ip/O : Input/Output pin (With pull-up resistor when in input mode)

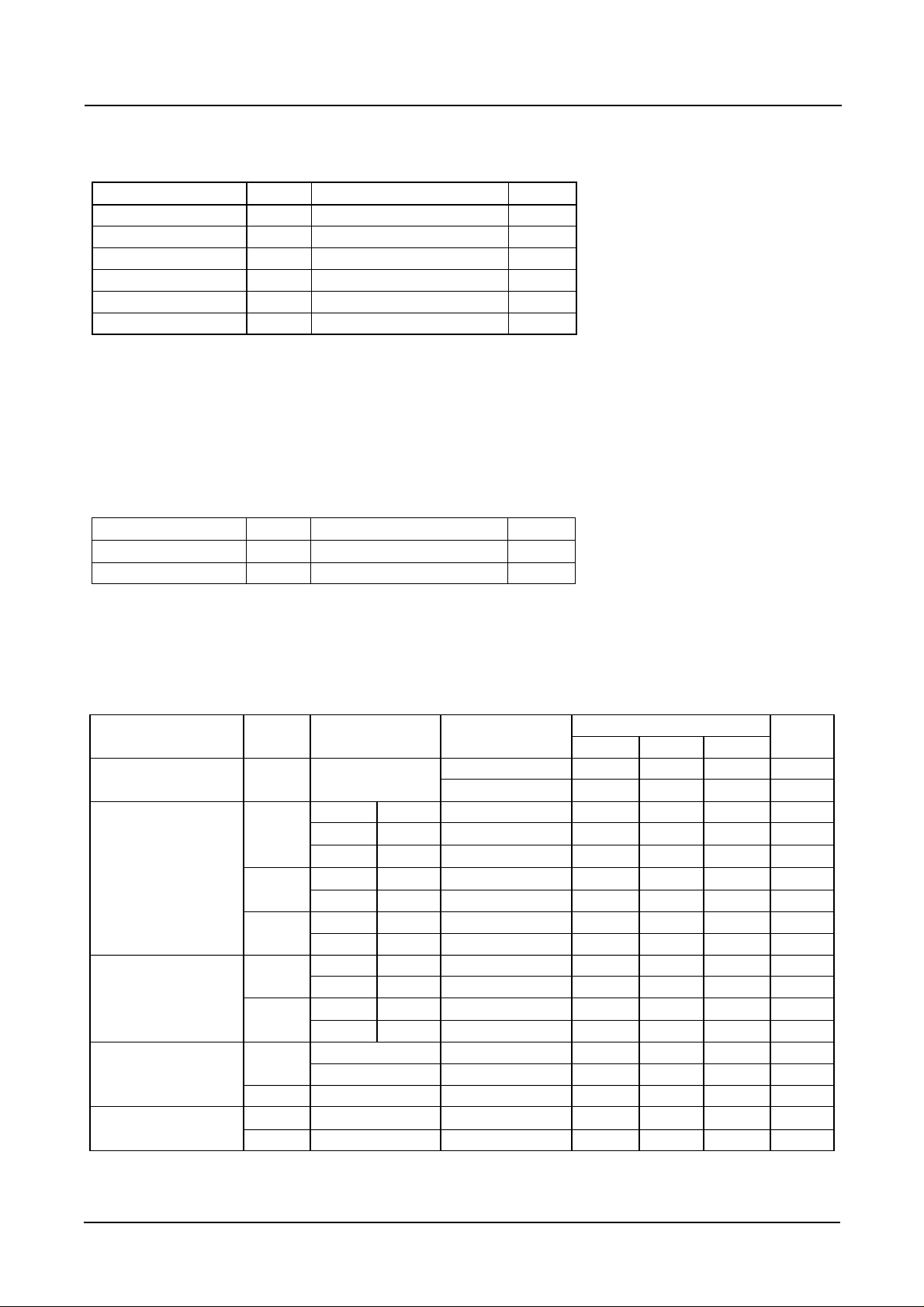

Parameter Pin Symbol Condition Rating Unit

Min Typ Max

Current consumption VDD I

DD (*A)SHPRF ON 4.5 8.0 mA

(*A)Through mode 1.8 3.0 mA

Input voltage CLK H level V

IH1 0.7VDD V

L level V

IL1 0.3VDD V

V

INAC AC coupling 1.0 VP-P

(*2,3,4) H level VIH2 0.7VDD V

L level V

IL2 0.3VDD V

(*5) H level V

IH3 0.6VDD V

L level V

IL3 0.2VDD V

Output voltage (*4,6) H level V

OH1 IOH = - 0.5 mA VDD - 0.4 V

L level V

OL1 IOL = 0.5 mA 0.4 V

(*5,7) H level V

OH2 IOH = - 0.5 mA VDD - 0.4 V

L level V

OL2 IOL = 0.5 mA 0.4 V

Input current CLK I

IH1 VIN = VDD 5 15 115 µA

I

IL1 VIN = 0V 5 15 115 µA

(*3,4) I

IL2 VIN = 0V 1 2.5 15 µA

Input leakage current (*2,3,4,5) I

LH VIN = VDD 1.0 µA

(*2,5) I

LL VIN = 0V 1.0 µA

(*A) VDD1 = VDD2 = 3 V, CLK input frequency fXTI= 384fs = 16.9344 MHz, all outputs unloaded,

SHPRF: Shock-proof,

typical values are for V

DD1 = VDD2 = 3 V.

NIPPON PRECISION CIRCUITS-4

SM5903BF

Parameter Symbol Rating Unit

Supply voltage V

DD - 0.3 to 4.6 V

Input voltage V

I VSS - 0.3 to VDD + 0.3 V

Storage temperature T

STG - 55 to 125 ˚C

Power dissipation P

D 350 mW

Soldering temperature T

SLD 255 ˚C

Soldering time

tSLD 10 sec

(VSS = 0V, VDD1, VDD2 pin voltage = VDD)

Note. Refer to pin summary on the next page.

Values also apply for supply inrush and switch-off.

Parameter Symbol Rating Unit

Supply voltage V

DD 2.4 to 3.6 V

Operating temperature T

OPR - 40 to 85 ˚C

(VSS = 0V, VDD1, VDD2 pin voltage = VDD)

Electrical characteristics

Recommended operating conditions

DC characteristics

Standard voltage:(VDD1 = VDD2 = 3.0 to 3.6 V, VSS = 0 V, Ta = - 40 to 85 ˚C)

Absolute maximum ratings

NIPPON PRECISION CIRCUITS-5

SM5903BF

(*1) Pin function Clock input pin (AC input)

Pin name CLK

(*2) Pin function Schmitt input pins

Pin name YSRDATA, YLRCK, YSCK, YFLAG, YFCLK, NRESET,

YBLKCK, YDMUTE, YMLD, YMDATA, YMCLK

(*3) Pin function Schmitt input pin with pull-up

Pin name NTEST

(*4) Pin function I/O pins (Schmitt input with pull-up in input state)

Pin name UC1, UC2, UC3, UC4, UC5

(*5) Pin function I/O pins (Schmitt input in input state)

Pin name D0, D1, D2, D3

(*6) Pin function Outputs

Pin name ZSCK, ZLRCK, ZSRDATA, ZSENSE

(*7) Pin function Outputs

Pin name NCAS, NWE, NRAS, A0, A1, A2, A3, A4, A5, A6, A7, A8, A9, A10

Low-voltage:(VDD1 = VDD2 = 2.4 to 3.0 V, VSS = 0 V, Ta = - 20 to 70 ˚C)

<Pin summary>

Parameter Pin Symbol Condition Rating Unit

Min Typ Max

Current consumption VDD I

DD (*B)SHPRF ON 4.5 8.0 mA

(*B)Through mode 1.8 3.0 mA

Input voltage CLK H level V

IH1 0.7VDD V

L level V

IL1 0.3VDD V

V

INAC AC coupling 1.0 VP-P

(*2,3,4) H level VIH2 0.7VDD V

L level V

IL2 0.3VDD V

(*5) H level V

IH3 0.6VDD V

L level V

IL3 0.2VDD V

Output voltage (*4,6) H level V

OH1 IOH = - 0.5 mA VDD - 0.4 V

L level V

OL1 IOL = 0.5 mA 0.4 V

(*5,7) H level V

OH2 IOH = - 0.5 mA VDD - 0.4 V

L level V

OL2 IOL = 0.5 mA 0.4 V

Input current CLK I

IH1 VIN = VDD 5 15 115 µA

I

IL1 VIN = 0V 5 15 115 µA

(*3,4) I

IL2 VIN = 0V 1 2.5 15 µA

Input leakage current (*2,3,4,5) I

LH VIN = VDD 1.0 µA

(*2,5) I

LL VIN = 0V 1.0 µA

(*B) VDD1 = VDD2 = 3 V, CLK input frequency fXTI= 384fs = 16.9344 MHz, all outputs unloaded,

SHPRF: Shock-proof,

typical values are for V

DD1 = VDD2 = 3 V.

NIPPON PRECISION CIRCUITS-6

SM5903BF

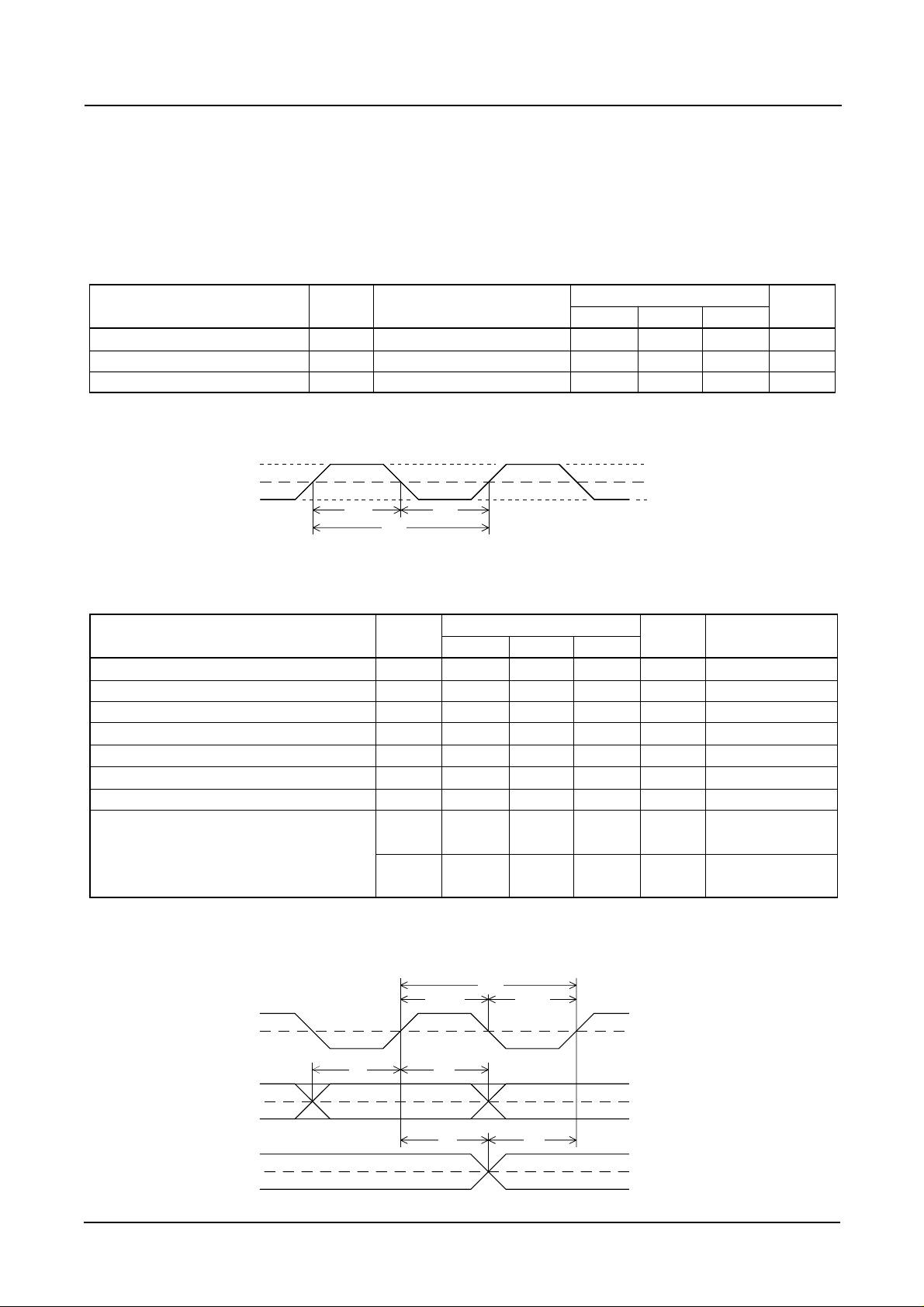

CWH

t

CWL

t

CY

t

0.5V

DD

CLK

Parameter Symbol Rating Unit Condition

Min Typ Max

YSCK pulsewidth (HIGH level)

tBCWH 75 ns

YSCK pulsewidth (LOW level)

tBCWL 75 ns

YSCK pulse cycle

tBCY 150 ns

YSRDATA setup time

tDS 50 ns

YSRDATA hold time

tDH 50 ns

Last YSCK rising edge to YLRCK edge

tBL 50 ns

YLRCK edge to first YSCK rising edge

tLB 50 ns

0 3fs Memory system ON

YLRCK pulse frequency (MSON=H)

See note below. fs fs Memory system OFF

(MSON=L)

Note. When the memory system is OFF (through mode), the input data rate is synchronized to the system clock input (384fs), so input

data needs to be at 1/384 of this frequency. But, this IC can tolerate a certain amount of jitter. For details, refer to Through-mode

operation.

YSCK

YSRDATA

YLRCK

BCY

t

DS

t

DH

t

BCWH

t

BCWL

t

LB

t

BL

t

0.5V

DD

0.5V

DD

0.5V

DD

Serial input (YSRDATA, YLRCK, YSCK pins)

AC characteristics

Standard voltage: VDD1 = VDD2 = 3.0 to 3.6 V, VSS = 0 V, Ta = -40 to 85 ˚C

Low-voltage: VDD1 = VDD2 = 2.4 to 3.0 V, VSS = 0 V, Ta = -20 to 70 ˚C

(*) Typical values are for fs = 44.1 kHz

System clock (CLK pin)

Parameter Symbol Condition Rating Unit

System clock Min Typ Max

Clock pulsewidth (HIGH level)

tCWH 26 29.5 125 ns

Clock pulsewidth (LOW level)

tCWL 26 29.5 125 ns

Clock pulse cycle

tCY 384fs 58 59 250 ns

System clock input

NIPPON PRECISION CIRCUITS-7

SM5903BF

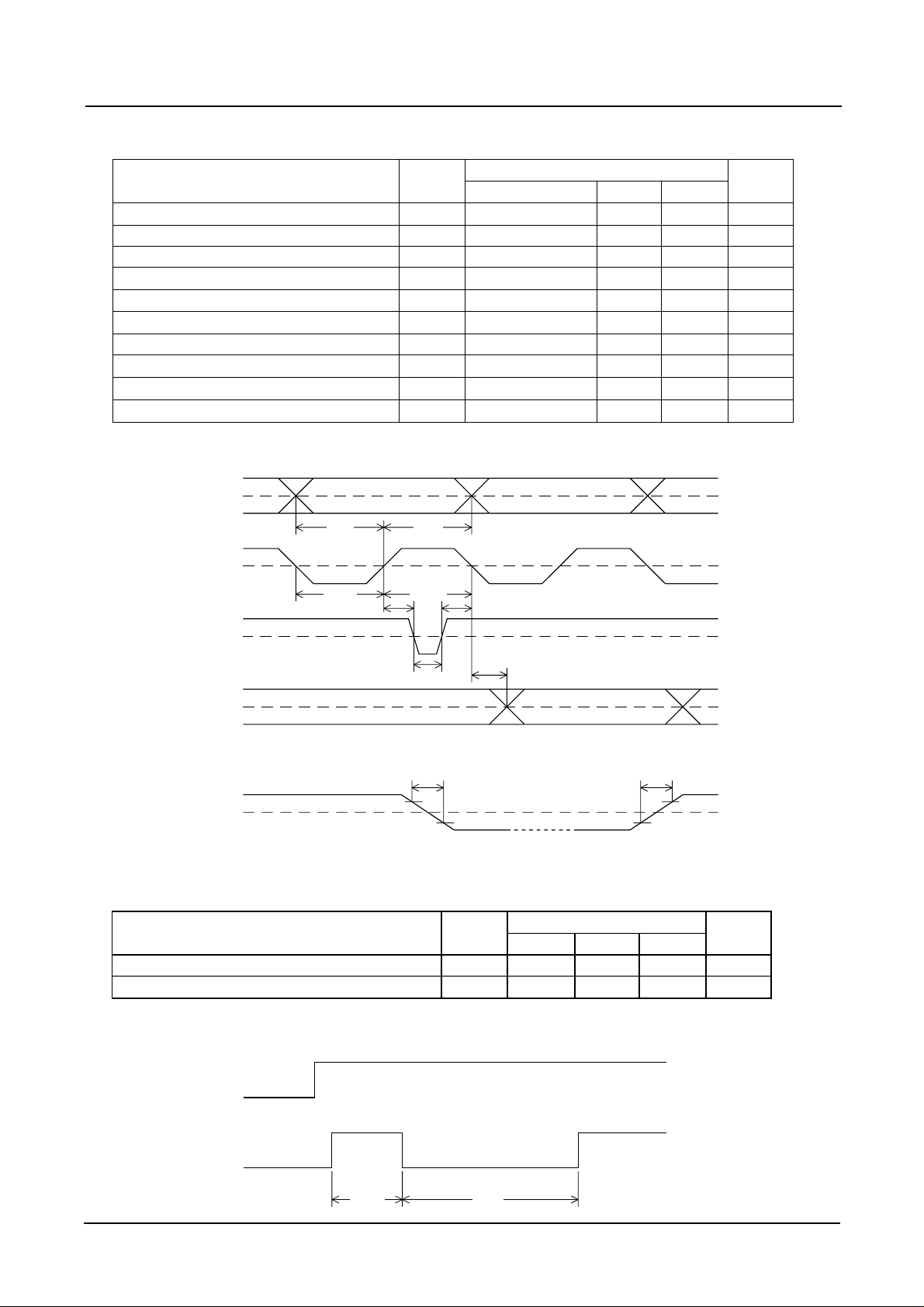

Parameter Symbol Rating Unit

Min Typ Max

YMCLK LOW-level pulsewidth

tMCWL 30 + 2tCY ns

YMCLK HIGH-level pulsewidth

tMCWH 30 + 2tCY ns

YMDATA setup time

tMDS 30 + tCY ns

YMDATA hold time

tMDH 30 + tCY ns

YMLD LOW-level pulsewidth

tMLWL 30 + 2tCY ns

YMLD setup time

tMLS 30 + tCY ns

YMLD hold time

tMLH 30 + tCY ns

Rise time

tr 100 ns

Fall time

tf 100 ns

ZSENSE output delay

tPZS 100 + 3tCY ns

Note. tCY is the system clock cycle time (59ns typ).

YMDATA

YMCLK

ZSENSE

YMLD

YMDATA

YMCLK

YMLD

MDS

t

MDH

t

MCWL

t

MLS

t

MCWH

t

MLH

t

MLWL

t

PZS

t

0.5VDD0.5V

DD

0.5V

DD

0.5V

DD

0.5V

DD

0.5V

DD

0.3VDD 0.3VDD

0.7VDD 0.7VDD

f

t

r

t

Reset input (NRESET pin)

Parameter Symbol Rating Unit

Min Typ Max

First HIGH-level after supply voltage rising edge

tHNRST 0 tCY (Note)

NRESET pulsewidth

tNRST 64 tCY (Note)

Note. tCY is the system clock (CLK) input (384fs) cycle time.

tCY = 59 ns, tNRST (min) = 3.8 µs when fs = 44.1 kHz

NRESET

VDD1,VDD2

HNRST

t t

NRST

Microcontroller interface (YMCLK, YMDATA, YMLD, ZSENSE pins)

NIPPON PRECISION CIRCUITS-8

SM5903BF

Parameter Symbol Condition Rating Unit

Min Typ Max

ZSCK pulsewidth

tSCOW 15 pF load 1/96fs

ZSCK pulse cycle

tSCOY 15 pF load 1/48fs

ZSRDATA and ZLRCK output delay time

tDHL 15 pF load 0 60 ns

tDLH 15 pF load 0 60 ns

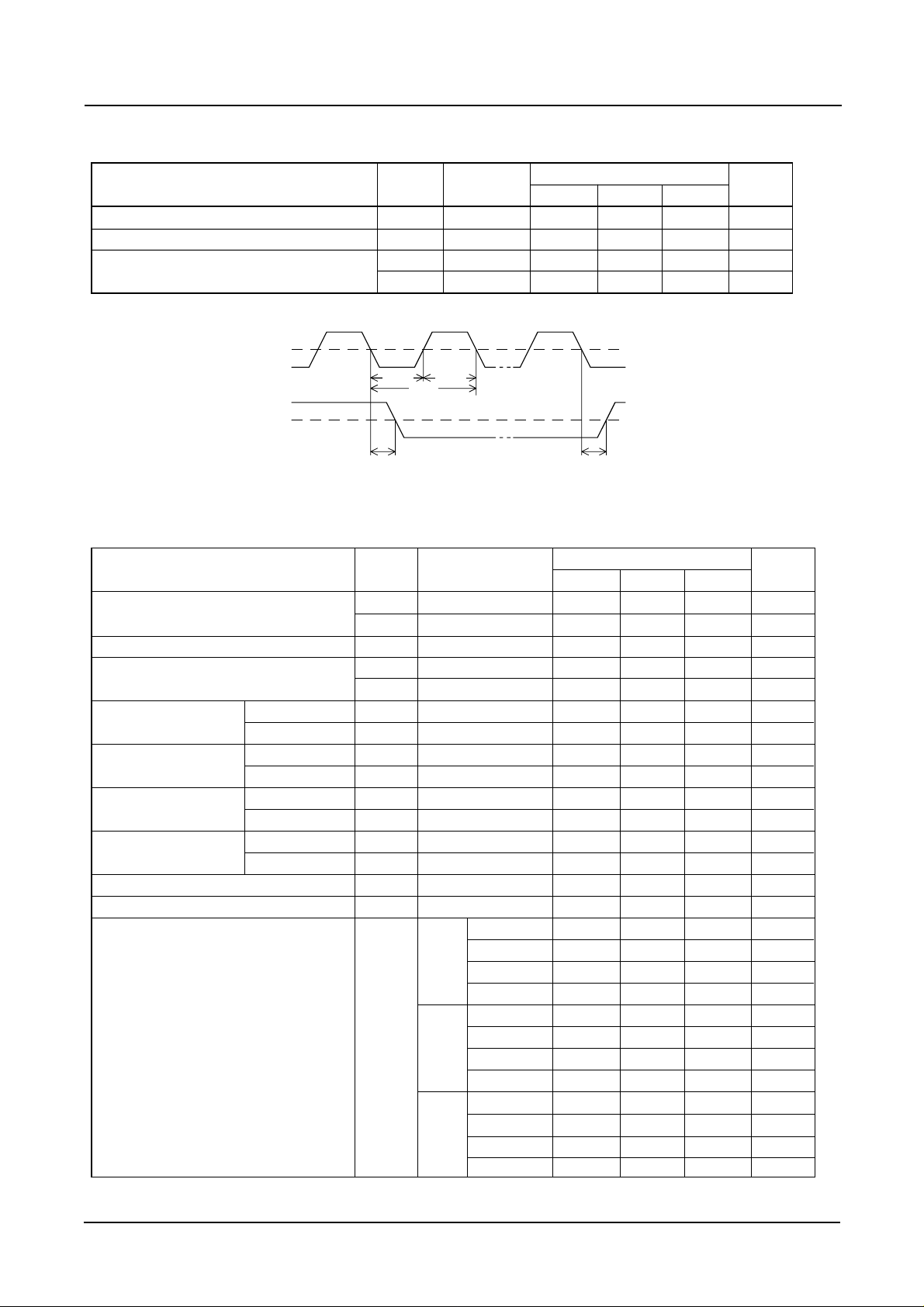

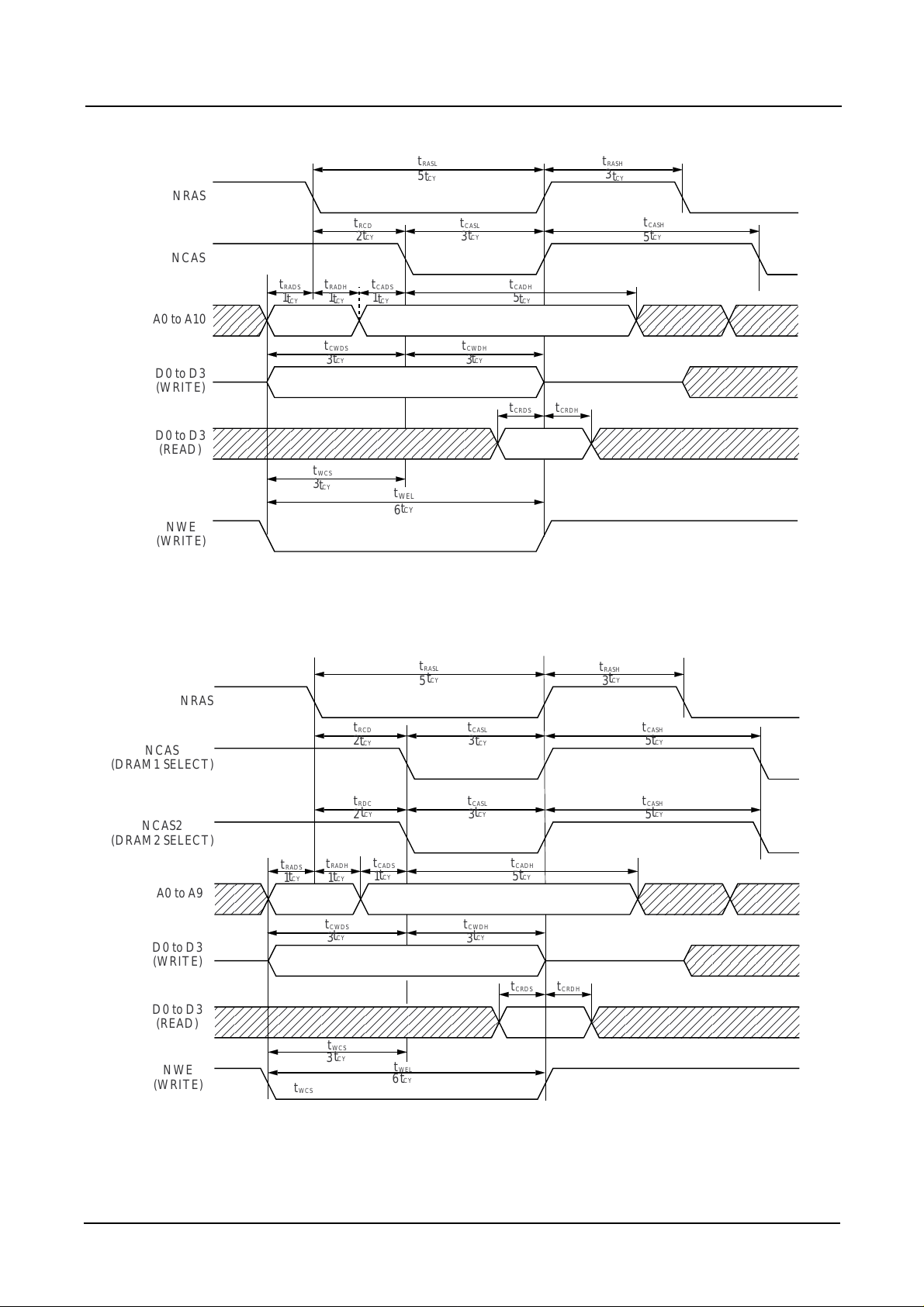

DRAM access timing (NRAS, NCAS, NCAS2, NWE, A0 to A10, D0 to D3)

Parameter Symbol Condition Rating Unit

Min Typ Max

NRAS pulsewidth

tRASL 15 pF load 5 tCY(note)

tRASH 15 pF load 3 tCY

NRAS falling edge to NCAS falling edge tRCD 15 pF load 2 tCY

NCAS pulsewidth tCASH 15 pF load 5 tCY

tCASL 15 pF load 3 tCY

NRAS Setup time tRADS 15 pF load 1 tCY

falling edge to address Hold time tRADH 15 pF load 1 tCY

NCAS Setup time tCADS 15 pF load 1 tCY

falling edge to address Hold time tCADH 15 pF load 5 tCY

NCAS Setup time tCWDS 15 pF load 3 tCY

falling edge to data write Hold time tCWDH 15 pF load 3 tCY

NCAS Input setup tCRDS 40 ns

rising edge to data read Input hold

tCRDH 0ns

NWE pulsewidth

tWEL 15 pF load 6 tCY

NWE falling edge to NCAS falling edge tWCS 15 pF load 3 tCY

Non compression 1.5 ms

Refresh cycle

1M 6-bit compression 3.7 ms

(fs = 44.1 kHz playback)

DRAM 5-bit compression 4.4 ms

tREF × 1 4-bit compression 5.5 ms

Memory system ON

Non compression 3.0 ms

Decode sequence operation

4M 6-bit compression 7.3 ms

(RDEN=H)

DRAM 5-bit compression 8.8 ms

× 1 or × 2 4-bit compression 10.9 ms

Non compression 5.9 ms

16M 6-bit compression 14.6 ms

DRAM 5-bit compression 17.5 ms

× 1 4-bit compression 21.8 ms

Note. tCY is the system clock (CLK) input (384fs) cycle time. tCY = 59 ns when fs = 44.1 kHz

ZSCK

ZSRDATA

0.5V

DD

DLH

ZLRCK

0.5V

DD

DHL

tt

DLH

SCOW

tt

SCOW

t

SCOY

t

Serial output (ZSRDATA, ZLRCK, ZSCK pins)

NIPPON PRECISION CIRCUITS-9

SM5903BF

DRAM access timing (with single DRAM)

The NWE terminal output is fixed HIGH during read timing.

DRAM access timing (with 2 DRAMs)

The NWE terminal output is fixed HIGH during read timing.

NCAS terminal output is fixed HIGH when selecting "DRAM2".

NCAS2 terminal output is fixed HIGH when selecting "DRAM1".

,,,,,,,,,,,,,,

,,,,,,,,,,,,,,

,,,,,,,,,,,,,,

,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,

,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,

,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,

,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,

,,,,,,,

,,,,,,,

,,,,,,,

NCAS

A0 to A10

D0 to D3

(WRITE)

NRAS

D0 to D3

(READ)

NWE

(WRITE)

3

WCS

t

6

CRDH

t

CRDS

t

CWDH

t

CWDS

t

33

5

CADH

t

CADS

t

RADH

t

RADS

t

111

5

32

t

RCD

t

CASL

CASH

t

RASH

t

3

t

CY

5

RASL

t

t

CY

tCY

tCY

tCY

tCY tCY tCY tCY

tCY tCY

tCY

tCY

WEL

t

,,,,,,,,,,,,,,,,,,,,,,,,

,,,,,,,,,,,,,,,,,,,,,,,,

,,,,,,,,,,,,,,,,,,,,,,,,

,,,,,,,,,,,,,,,,,,,,,,,,

NCAS

(DRAM1 SELECT)

A0 to A9

NRAS

D0 to D3

(READ)

NCAS2

(DRAM2 SELECT)

D0 to D3

(WRITE)

NWE

(WRITE)

5

3

253

1

1

1

3

3

5

253

3

RASH

t

RASL

t

RCD

tt

CASL CASH

t

CASH

tt

CASLRDC

t

t

RADS

RADH

t

CADS

t

CADH

t

CWDH

t

CWDS

t

CRDStCRDH

t

WCS

t

tCY tCY

tCY

tCY tCY tCY

tCY tCY

tCY tCY

tCY tCY

tCY

tCY tCY

WEL

t

6

tCY

WCS

t

NIPPON PRECISION CIRCUITS-10

SM5903BF

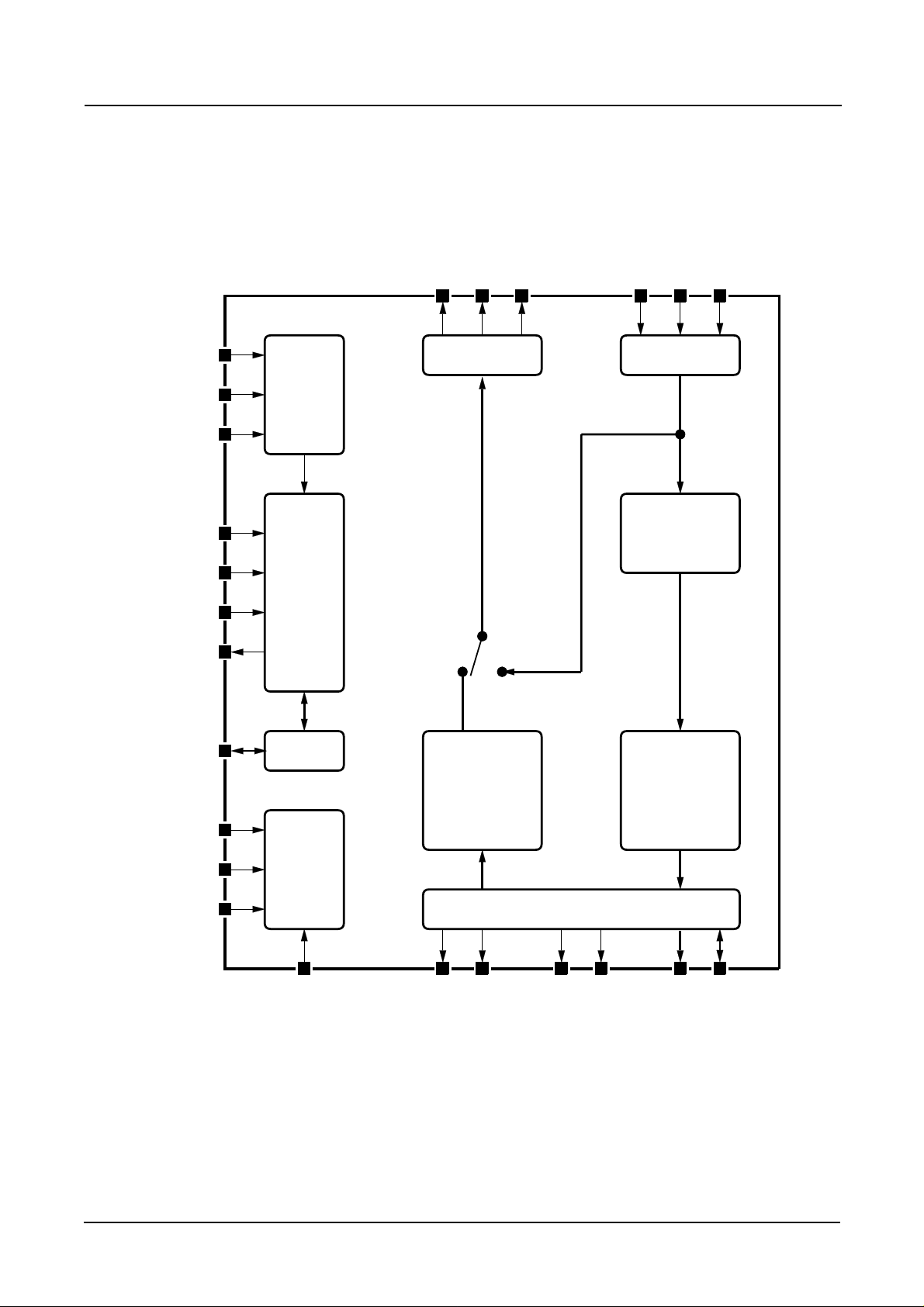

Control

Input 1

Control

Input 2

Micro-

controller

Interface

General

Port

Output Interface Input Interface

Input Buffer

Decoder Encoder

DRAM Interface

YBLKCK

YFCLK

YFLAG

YMDATA

YMCLK

YMLD

ZSENSE

UC1 to UC5

YDMUTE

NRESET

NTEST

CLK

NRAS

NCAS

NCAS2

NWE

A0 to A10

D0 to D3

Through

Mode

Compression

Mode

ZLRCK

ZSCK

ZSRDATA

YLRCK

YSCK

YSRDATA

SM5903

Block diagram

Loading...

Loading...