Page 1

NIPPON PRECISION CIRCUITS INC.

NIPPON PRECISION CIRCUITS-1

SM5859AF

compression and non compression type antishock memory controller

Overview

- 2-channel processing

- Serial data input

•2s complement, 16-bit/MSB first, rear-packed

format

- System clock input

•384fs (16.9344 MHz)

- Anti-shock memory controller

- ADPCM compression method

•4-level compression mode selectable

4-bit compression mode 2.78 s/Mbit

5-bit compression mode 2.22 s/Mbit

6-bit compression mode 1.85 s/Mbit

Full-bit non compression mode 0.74 s/Mbit

•4 external DRAM configurations selectable

2×4M DRAM (1M×4 bits)

1×4M DRAM (1M×4 bits)

2×1M DRAM (256K×4 bits)

1×1M DRAM (256K×4 bits)

- Compression mode selectable

- Microcontroller interface

•Serial command write and state read-out

•Data residual quantity detector:

15-bit operation, 16-bit output

•Digital attenuator

Full-bit setting

•Soft attenuator function

Noiseless attenuation-level switching

(256- step switching in 23 ms max.)

•Soft mute function

Mute ON in 23 ms max.

Direct return after soft mute release

•Forced mute

- Extension I/O

Microcontroller interface for external control

using 5 extension I/O pins

- +2.7 to +5.5 V wide operating voltage range

- Schmitt inputs

All input pins (including I/O pins) except CLK

(system clock)

- Reset signal noise elimination

Approximately 3.8 µs or longer (65 system

clock pulses) continuous LOW-level reset

- 44-pin QFP package (0.8 mm pin pitch)

The SM5859 is a compression and non compression type anti-shock memory controller LSI for compact disc players. The compression level can be set

in 4 levels, and external memory can be selected

from 4 options (1M, 1M×2, 4M, 4M×2). Digital attenuator, soft mute and related functions are also

incorporated. It operates from a 2.7 to 5.5 V wide

supply voltage range.

Features

Page 2

NIPPON PRECISION CIRCUITS-2

SM5859AF

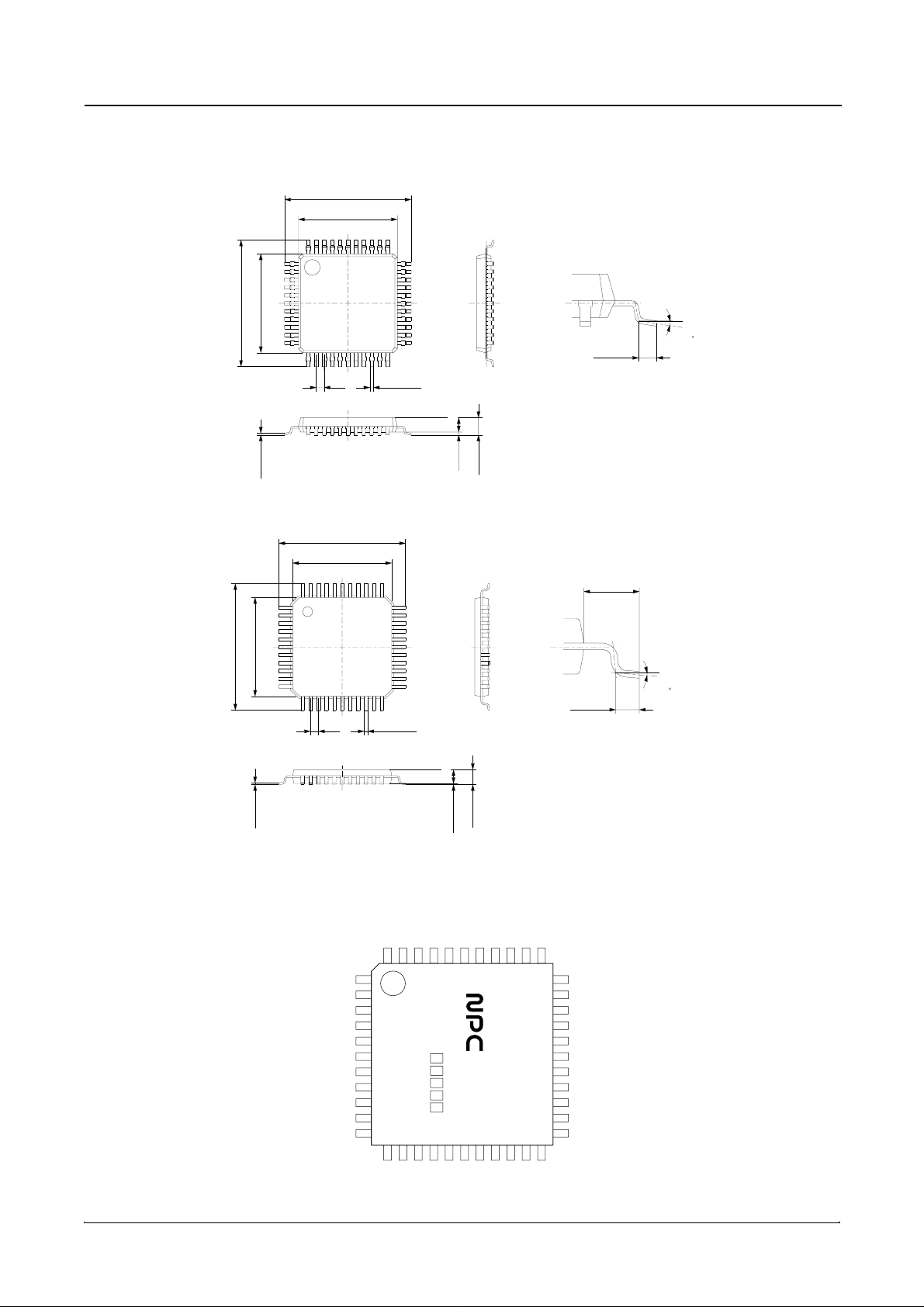

Package dimensions

(Unit: mm)

44-pin QFP 1

0.17 0.05

+

-

10.00

10.00

12.80 0.30

+

-

1.75MAX

0 to 0.20 1.45

0.80

12.80 0.30

+

-

0.35 0.10

+

-

+

-

0.60 0.20

0 to 10

10.00

12.80 0.30

+

-

10.00

12.80 0.30

+

-

0.80

0.35 0.10

+

-

0.17 0.05

+

-

1.70MAX

0.10 to 0.20

1.40

+

-

0.60 0.20

0 to 10

1.40

44-pin QFP 2

Pinout

(Top View)

1

2

3

4

5

6

7

8

9

10

11

1213141516171819202122

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

VDD

UC1

UC2

UC3

UC4

UC5

NTEST1

NTEST2

CLK

VSS

YSRDATA

NWE

D1

D0

D3

D2

NCAS

NOE/ NCAS2

YMCLK

YMDATA

YMLD

YDMUTE

YLRCK

YSCK

ZSCK

ZLRCK

ZSRDATA

YFLAG

YFCLK

YBLKCK

NRESET

ZSENSE

UC6

A3A2A1A0A4A5A6A7A8

A9

NRAS

SM585

9AF

Page 3

SM5859AF

NIPPON PRECISION CIRCUITS-3

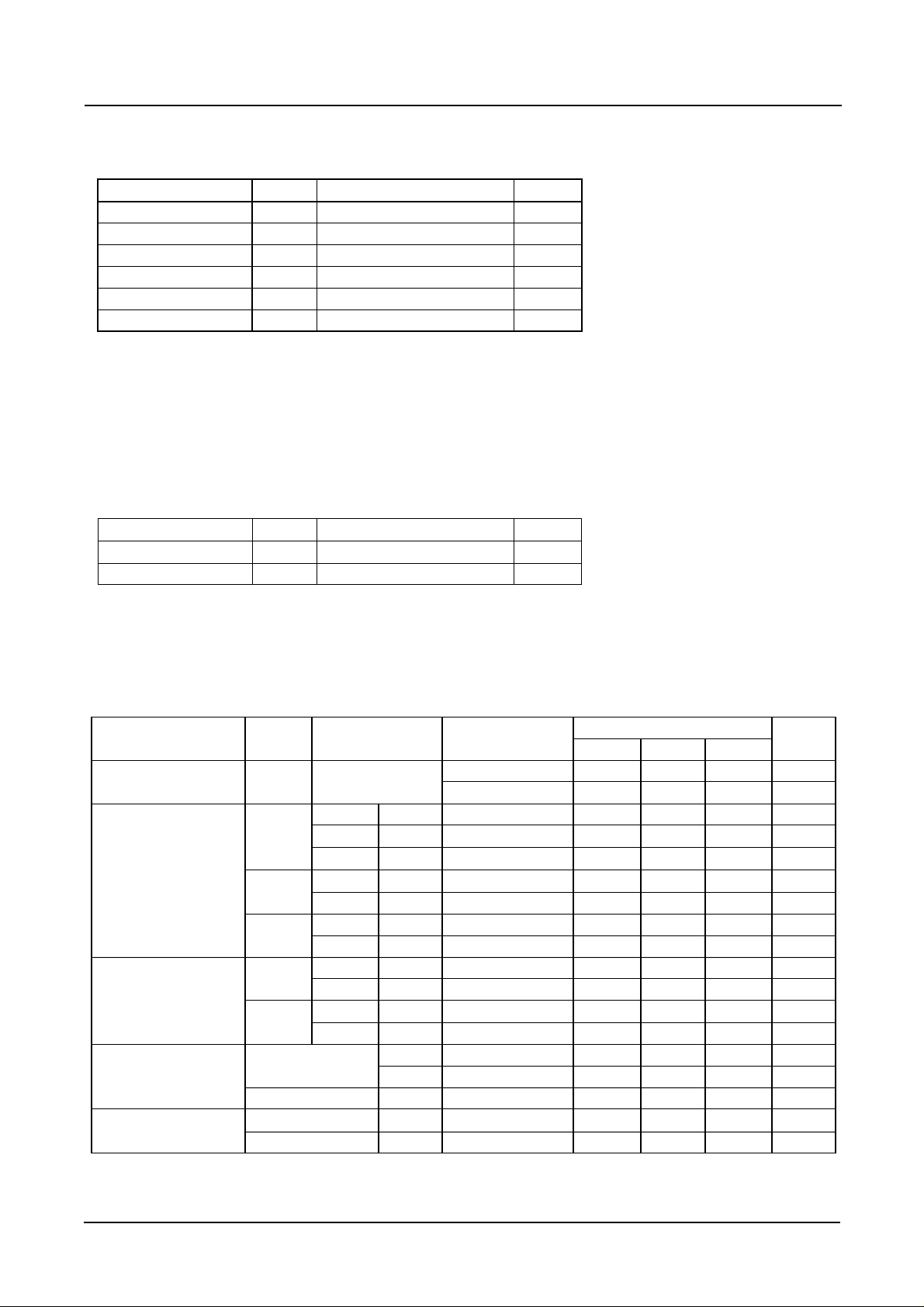

Pin number Pine name I/O Function Setting

HL

1 VDD - VDD supply pin

2 UC1 Ip/O Microcontroller interface extension I/O 1

3 UC2 Ip/O Microcontroller interface extension I/O 2

4 UC3 Ip/O Microcontroller interface extension I/O 3

5 UC4 Ip/O Microcontroller interface extension I/O 4

6 UC5 Ip/O Microcontroller interface extension I/O 5

7 NTEST1 Ip Test pin Test

8 NTEST2 Ip Test pin Test

9 CLK I 16.9344 MHz clock input

10 VSS - Ground

11 YSRDATA I Audio serial input data

12 YLRCK I Audio serial input LR clock Left channel Right channel

13 YSCK I Audio serial input bit clock

14 ZSCK O Audio serial output bit clock

15 ZLRCK O Audio serial output LR clock Left channel Right channel

16 ZSRDATA O Audio serial output data

17 YFLAG I Signal processor IC RAM overflow flag Overflow

18 YFCLK I Crystal-controlled frame clock

19 YBLKCK I Subcode block clock signal

20 NRESET I System reset pin Reset

21 ZSENSE O Microcontroller interface status output

22 UC6 Ip/O Microcontroller interface extension I/O 6

23 YDMUTE I Forced mute pin Mute

24 YMLD I Microcontroller interface latch clock

25 YMDATA I Microcontroller interface serial data

26 YMCLK I Microcontroller interface shift clock

27 NOE O DRAM OE control (with single DRAM)

(NCAS2) O DRAM2 CAS control (with 2 DRAMs)

28 NCAS O DRAM CAS control

29 D2 I/O DRAM data input/output 2

30 D3 I/O DRAM data input/output 3

31 D0 I/O DRAM data input/output 0

32 D1 I/O DRAM data input/output 1

33 NWE O DRAM WE control

34 NRAS O DRAM RAS control

35 A9 O DRAM address 9

36 A8 O DRAM address 8

37 A7 O DRAM address 7

38 A6 O DRAM address 6

39 A5 O DRAM address 5

40 A4 O DRAM address 4

41 A0 O DRAM address 0

42 A1 O DRAM address 1

43 A2 O DRAM address 2

44 A3 O DRAM address 3

Ip : Input pin with pull-up resistor Ip/O : Input/Output pin (With pull-up resistor when a input mode)

Pin description

Page 4

NIPPON PRECISION CIRCUITS-4

SM5859AF

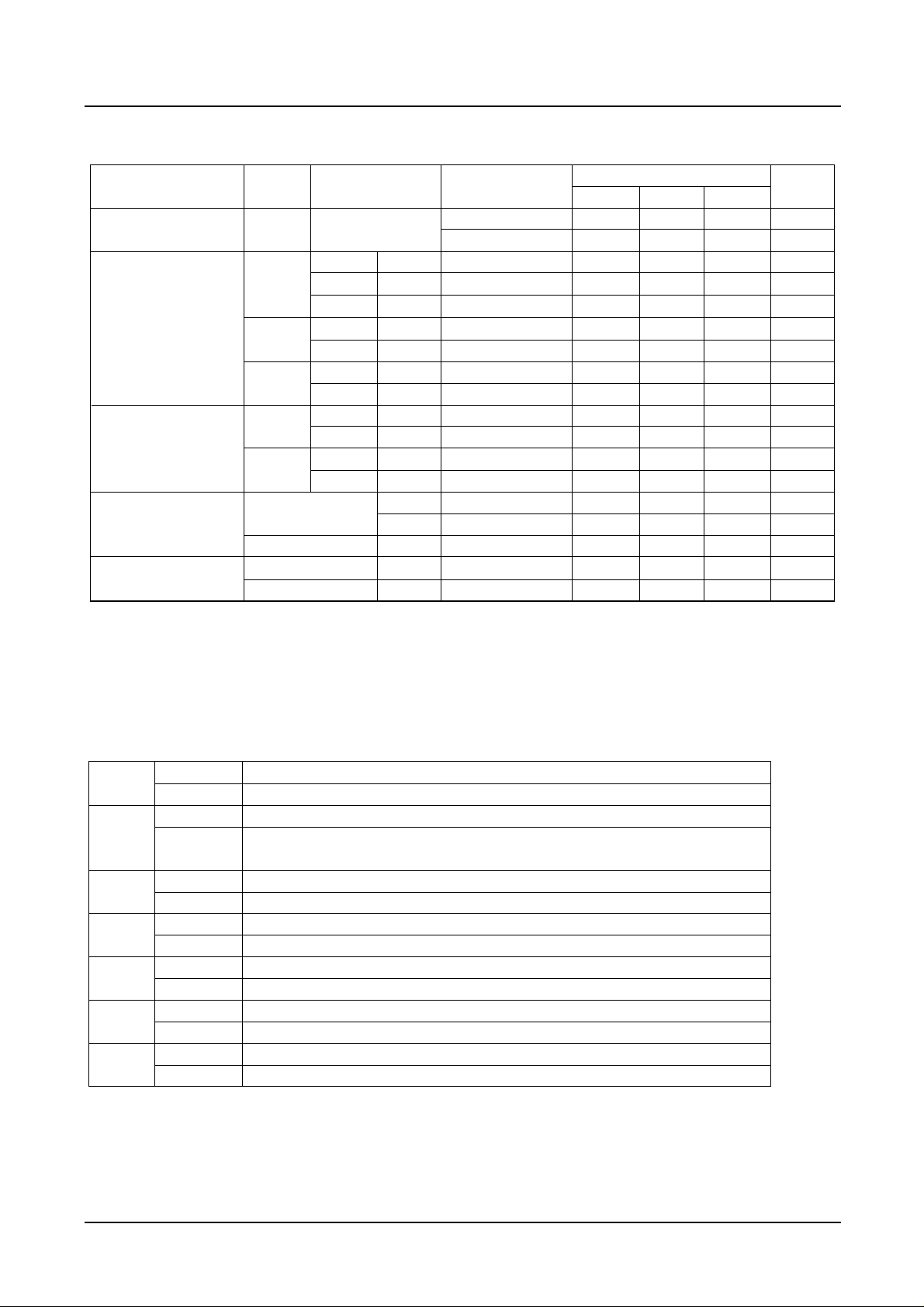

Parameter Symbol Rating Unit

Supply voltage V

DD - 0.3 to 7.0 V

Input voltage V

I VSS - 0.3 to VDD + 0.3 V

Storage temperature T

STG - 55 to 125 ˚C

Power dissipation P

D 350 mW

Soldering temperature T

SLD 255 ˚C

Soldering time

tSLD 10 sec

(VSS = 0V, VDD pin voltage = VDD)

(*1) Refer to pin summary on the next page.

Note. Values also apply for supply inrush and switch-off.

Parameter Symbol Rating Unit

Supply voltage V

DD 2.7 to 5.5 V

Operating temperature T

OPR - 40 to 85 ˚C

(VSS = 0V, VDD pin voltage = VDD)

Parameter Pin Symbol Condition Rating Unit

Min Typ Max

Current consumption VDD I

DD (*A)SHPRF ON 6.5 13.0 mA

(*A)Through mode 4.0 6.0 mA

Input voltage CLK H level V

IH1 0.7VDD V

L level V

IL1 0.3VDD V

V

INAC AC coupling 0.3 VP-P

(*2,3,4) H level VIH2 0.7VDD V

L level V

IL2 0.3VDD V

(*5) H level V

IH3 0.6VDD V

L level V

IL3 0.2VDD V

Output voltage (*4,6) H level V

OH1 IOH = - 0.5 mA VDD - 0.4 V

L level V

OL1 IOL = 0.5 mA 0.4 V

(*5,7) H level V

OH2 IOH = - 0.5 mA VDD - 0.4 V

L level V

OL2 IOL = 0.5 mA 0.4 V

Input current CLK I

IH1 VIN = VDD 40 95 190 µA

I

IL1 VIN = 0V 40 95 190 µA

(*3,4) I

IL2 VIN = 0V 6 12 25 µA

Input leakage current (*2,3,4,5) I

LH1 VIN = VDD 1.0 µA

(*2,5) I

LL VIN = 0V 1.0 µA

(*A) VDD = 5 V, CLK input frequency fXTI= 384fs = 16.9344 MHz, all outputs unloaded,

SHPRF: Shock-proof,

typical values are for VDD = 5 V.

Electrical characteristics

Recommended operating conditions

DC characteristics

Standard voltage: (VDD = 4.5 to 5.5 V, VSS = 0 V, Ta = - 40 to 85 ˚C)

Absolute maximum ratings

Page 5

SM5859AF

NIPPON PRECISION CIRCUITS-5

<Pin summary>

Parameter Pin Symbol Condition Rating Unit

Min Typ Max

Current consumption VDD I

DD (*B)SHPRF ON 4.0 8.0 mA

(*B)Through mode 1.6 2.4 mA

Input voltage CLK H level V

IH1 0.7VDD V

L level V

IL1 0.3VDD V

V

INAC AC coupling 0.3 VP-P

(*2,3,4) H level VIH2 0.7VDD V

L level V

IL2 0.3VDD V

(*5) H level V

IH3 0.6VDD V

L level V

IL3 0.2VDD V

Output voltage (*4,6) H level V

OH1 IOH = - 0.5 mA VDD - 0.4 V

L level V

OL1 IOL = 0.5 mA 0.4 V

(*5,7) H level V

OH2 IOH = - 0.5 mA VDD - 0.4 V

L level V

OL2 IOL = 0.5 mA 0.4 V

Input current CLK I

IH1 VIN = VDD 15 30 115 µA

I

IL1 VIN = 0V 15 30 115 µA

(*3,4) I

IL2 VIN = 0V 1.5 3 15 µA

Input leakage current (*2,3,4,5) I

LH1 VIN = VDD 1.0 µA

(*2,5) I

LL VIN = 0V 1.0 µA

(*B) VDD = 3 V, CLK input frequency fXTI= 384fs = 16.9344 MHz, all outputs unloaded,

SHPRF: Shock-proof,

typical values are for VDD = 3 V.

(*1) Pin function Clock input pin (AC input)

Pin name CLK

(*2) Pin function Schmitt input pins

Pin name YSRDATA, YLRCK, YSCK, YFLAG, YFCLK, NRESET,

YBLKCK, YDMUTE, YMLD, YMDATA, YMCLK

(*3) Pin function Schmitt input pin with pull-up

Pin name NTEST1, NTEST2

(*4) Pin function I/O pins (Schmitt input with pull-up in input state)

Pin name UC1, UC2, UC3, UC4, UC5, UC6

(*5) Pin function I/O pins (Schmitt input in input state)

Pin name D0, D1, D2, D3

(*6) Pin function Outputs

Pin name ZSCK, ZLRCK, ZSRDATA, ZSENSE

(*7) Pin function Outputs

Pin name NOE, NCAS, NWE, NRAS, A0, A1, A2, A3, A4, A5, A6, A7, A8, A9

Low-voltage:(VDD = 2.7 to 4.5 V, VSS = 0 V, Ta = - 20 to 70 ˚C)

Page 6

NIPPON PRECISION CIRCUITS-6

SM5859AF

Parameter Symbol Condition Rating Unit

System clock Min Typ Max

Clock pulsewidth (HIGH level)

tCWH 26 29.5 125 ns

Clock pulsewidth (LOW level)

tCWL 26 29.5 125 ns

Clock pulse cycle

tCY 384fs 56 59 250 ns

CWH

t

CWL

t

CY

t

0.5V

DD

CLK

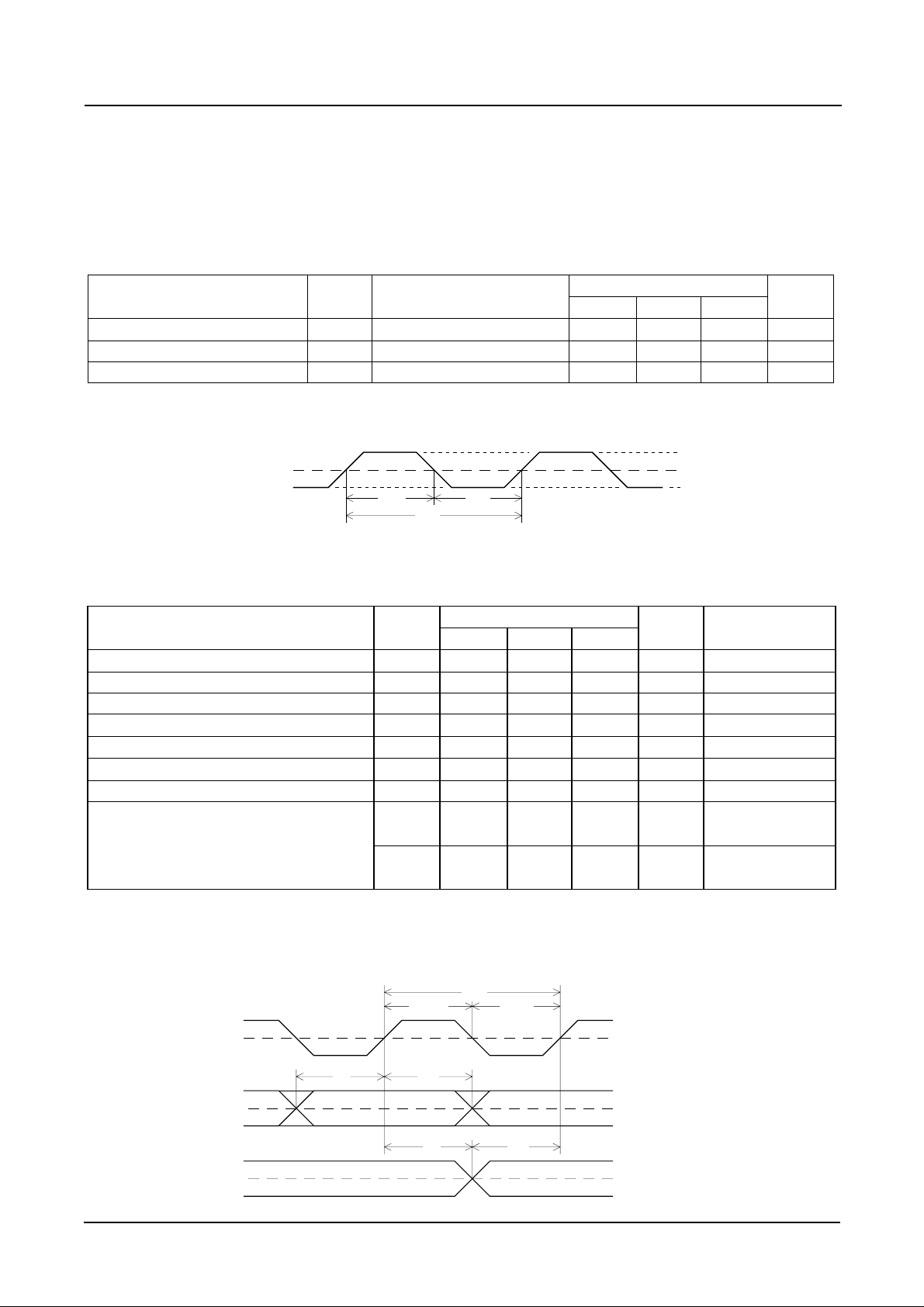

Parameter Symbol Rating Unit Condition

Min Typ Max

YSCK pulsewidth (HIGH level)

tBCWH 75 ns

YSCK pulsewidth (LOW level)

tBCWL 75 ns

YSCK pulse cycle

tBCY 150 ns

YSRDATA setup time

tDS 40 ns

YSRDATA hold time

tDH 40 ns

Last YSCK rising edge to YLRCK edge

tBL 40 ns

YLRCK edge to first YSCK rising edge

tLB 40 ns

0 2fs Memory system ON

YLRCK pulse frequency (MSON=H)

See note below. fs fs Memory system OFF

(MSON=L)

Note. When the memory system is OFF (through mode), the input data rate is synchronized to the system clock input (384fs), so input

data needs to be at 1/384 of this frequency. But, this IC can tolerate a certain amount of jitter. For details, refer to Through-mode

operation.

YSCK

YSRDATA

YLRCK

BCY

t

DS

t

DH

t

BCWH

t

BCWL

t

LB

t

BL

t

0.5V

DD

0.5V

DD

0.5V

DD

Serial input (YSRDATA, YLRCK, YSCK pins)

AC characteristics

Standard voltage: VDD = 4.5 to 5.5 V, VSS = 0 V, Ta = -40 to 85 °C

Low-voltage: VDD = 2.7 to 4.5 V, VSS = 0 V, Ta = -20 to 70 °C

(*) Typical values are for fs = 44.1 kHz

System clock (CLK pin)

System clock input

Page 7

SM5859AF

NIPPON PRECISION CIRCUITS-7

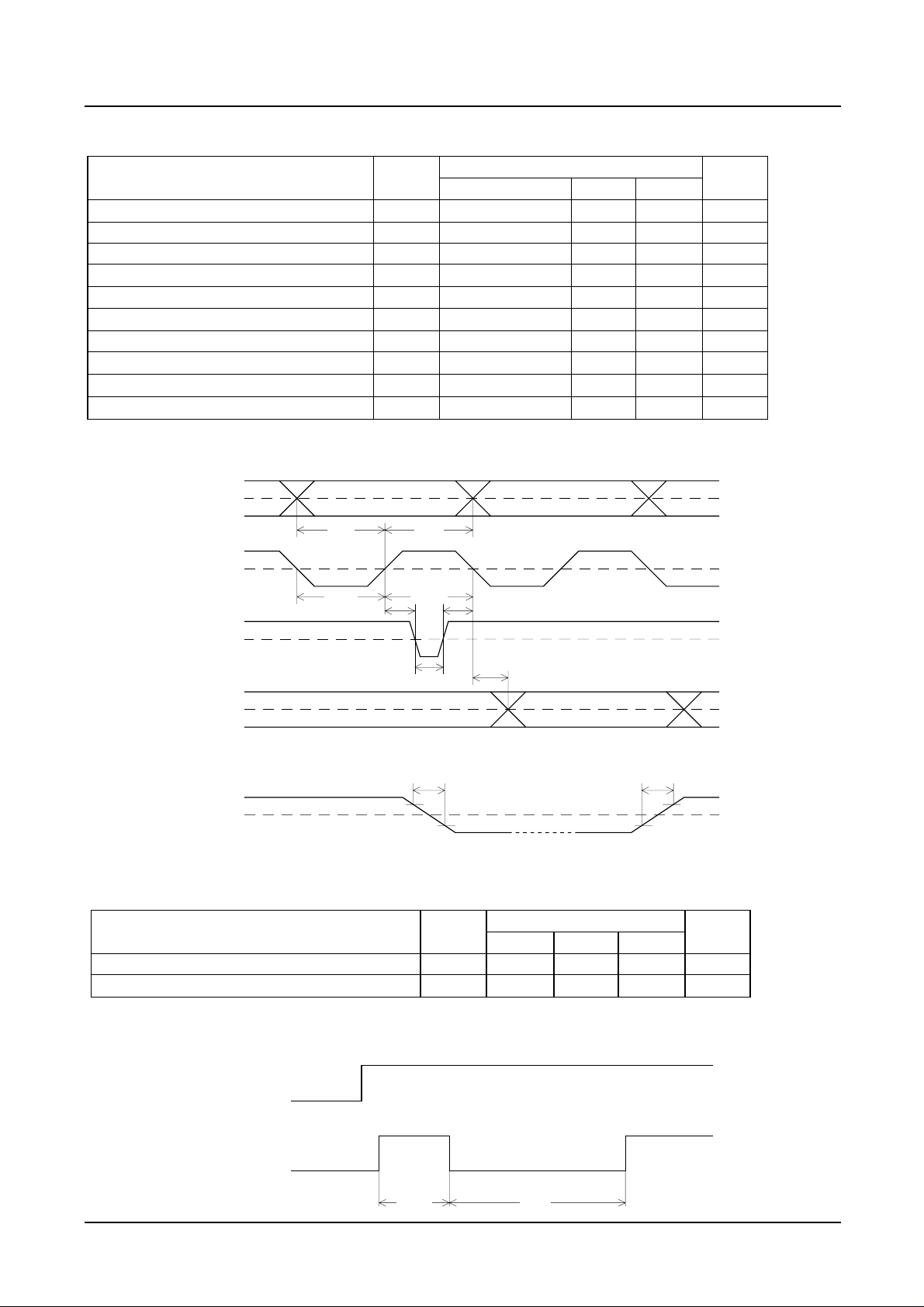

Parameter Symbol Rating Unit

Min Typ Max

YMCLK LOW-level pulsewidth

tMCWL 30 + 3tCY ns

YMCLK HIGH-level pulsewidth

tMCWH 30 + 3tCY ns

YMDATA setup time

tMDS 30 + tCY ns

YMDATA hold time

tMDH 30 + tCY ns

YMLD LOW-level pulsewidth

tMLWL 30 + 3tCY ns

YMLD setup time

tMLS 30 + tCY ns

YMLD hold time

tMLH 30 + tCY ns

Rise time

tr 100 ns

Fall time

tf 100 ns

ZSENSE output delay

tPZS 100 + 3tCY ns

Note. tCY is the system clock cycle time (59ns typ).

YMDATA

YMCLK

ZSENSE

YMLD

YMDATA

YMCLK

YMLD

MDS

t

MDH

t

MCWL

t

MLS

t

MCWH

t

MLH

t

MLWL

t

PZS

t

0.5VDD0.5V

DD

0.5V

DD

0.5V

DD

0.5V

DD

0.5V

DD

0.3VDD 0.3VDD

0.7VDD 0.7VDD

f

t

r

t

Reset input (NRESET pin)

Parameter Symbol Rating Unit

Min Typ Max

First HIGH-level after supply voltage rising edge

tHNRST 0 tCY (Note)

NRESET pulsewidth

tNRST 64 tCY (Note)

Note. tCY is the system clock (CLK) input (384fs) cycle time.

tCY = 59 ns, tNRST (min) = 3.8 µs when fs = 44.1 kHz

NRESET

VDD

HNRST

t t

NRST

Microcontroller interface (YMCLK, YMDATA, YMLD, ZSENSE pins)

Page 8

NIPPON PRECISION CIRCUITS-8

SM5859AF

Parameter Symbol Condition Rating Unit

Min Typ Max

ZSCK pulsewidth

tSCOW 15 pF load 1/96fs

ZSCK pulse cycle

tSCOY 15 pF load 1/48fs

ZSRDATA and ZLRCK output delay time

tDHL 15 pF load 0 60 ns

tDLH 15 pF load 0 60 ns

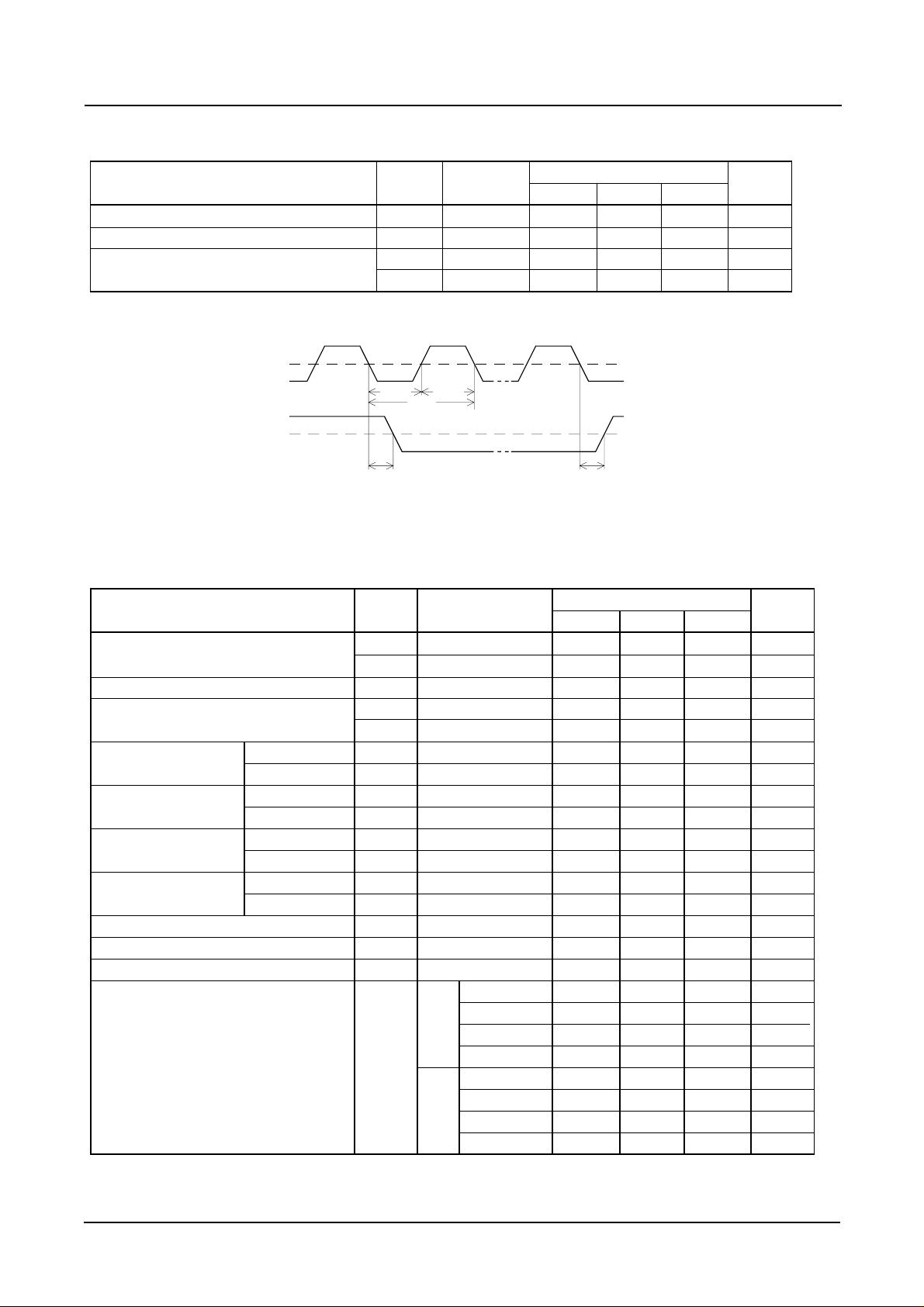

DRAM access timing (NRAS, NCAS, NOE, NWE, A0 to A9, D0 to D3)

Parameter Symbol Condition Rating Unit

Min Typ Max

NRAS pulsewidth

tRASL 15 pF load 5 tCY(note)

tRASH 15 pF load 3 tCY

NRAS falling edge to NCAS falling edge tRCD 15 pF load 2 tCY

NCAS pulsewidth tCASH 15 pF load 5 tCY

tCASL 15 pF load 3 tCY

NRAS Setup time tRADS 15 pF load 1 tCY

falling edge to address Hold time tRADH 15 pF load 1 tCY

NCAS Setup time tCADS 15 pF load 1 tCY

falling edge to address Hold time tCADH 15 pF load 5 tCY

NCAS Setup time tCWDS 15 pF load 3 tCY

falling edge to data write Hold time tCWDH 15 pF load 3 tCY

NCAS Input setup tCRDS 40 ns

rising edge to data read Input hold

tCRDH 0ns

NOE pulsewidth

tOEL 15 pF load 6 tCY

NWE pulsewidth tWEL 15 pF load 6 tCY

NWE falling edge to NCAS falling edge tWCS 15 pF load 3 tCY

Non compression 1.4 ms

Refresh cycle

1M 6-bit compression 3.7 ms

(fs = 44.1 kHz playback)

DRAM 5-bit compression 4.4 ms

tREF 4-bit compression 5.5 ms

Memory system ON

Non compression 2.7 ms

Decode sequence operation

4M 6-bit compression 7.3 ms

(RDEN=H)

DRAM 5-bit compression 8.8 ms

4-bit compression 10.9 ms

Note. tCY is the system clock (CLK) input (384fs) cycle time. tCY = 59 ns when fs = 44.1 kHz

ZSCK

ZSRDATA

0.5V

DD

DLH

ZLRCK

0.5V

DD

DHL

tt

DLH

SCOW

tt

SCOW

t

SCOY

t

Serial output (ZSRDATA, ZLRCK, ZSCK pins)

Page 9

SM5859AF

NIPPON PRECISION CIRCUITS-9

NCAS

A0 to A9

D0 to D3

(WRITE)

NRAS

NOE

(WRITE)

D0 to D3

(READ)

NOE

(READ)

NWE

(WRITE)

NWE

(READ)

tCY3

WCS

t

CY

t6

CY

t6

OEL

t

CRDH

t

CRDS

t

CWDH

t

CWDS

t

CY

t3

CY

t3

CY

t5

CADH

t

CADS

t

RADH

t

RADS

t

CY

t1

CY

t1

CY

t1

CY

t5

CY

t3

CY

t2

t

RCD

t

CASL CASH

t

RASH

t

CY

t

3

CY

t5

RASL

t

WEL

t

DRAM access timing (with single DRAM)

Page 10

NIPPON PRECISION CIRCUITS-10

SM5859AF

NCAS

(DRAM1 SELECT)

A0 to A9

NRAS

D0 to D3

(READ)

NWE

(READ)

NCAS

(DRAM2 SELECT)

NCAS2

(DRAM1 SELECT)

NCAS2

(DRAM2 SELECT)

D0 to D3

(WRITE)

NWE

(WRITE)

CY

t5

CY

t3

CY

t2

CY

t5

CY

t3

CY

t1

CY

t

1

CY

t1

CY

t3

CY

t3

CY

t

5

CY

t

2

CY

t

5

CY

t

3

t

CY

t6

CY

3

RASH

t

RASL

t

RCD

tt

CASL CASH

t

CASH

tt

CASLRCD

t

t

RADS

RADH

t

CADS

t

CADH

t

CWDH

t

CWDS

t

CRDS

t

CRDH

t

WCS

t

WEL

t

DRAM access timing (with 2 DRAMs)

Page 11

SM5859AF

NIPPON PRECISION CIRCUITS-11

Control

Input 1

Control

Input 2

Microcont-

roller

Interface

General

Port

Output Interface Input Interface

Attenuator Input Buffer

Decoder Encoder

DRAM Interface

SM5859

YBLKCK

YFCLK

YFLAG

YMDATA

YMCLK

YMLD

ZSENSE

UC1 to UC6

YDMUTE

NRESET

NTEST1, 2

CLK

NRAS

NCAS

NOE

NCAS2

NWE

A0 to A9

D0 to D3

Through

Mode

Compression

Mode

ZLRCK

ZSCK

ZSRDATA

YLRCK

YSCK

YSRDATA

Block diagram

Page 12

NIPPON PRECISION CIRCUITS-12

SM5859AF

Write command format

This IC has two modes of operation; shock-proof

mode and through mode.

The operating sequences are controlled using commands from a microcontroller.

D7 D6 D5 D4 D3 D2 D1 D0 B7 B6 B5 B4 B3 B2 B1 B0

COMMAND 8bit DATA 8bit

YMDATA

YMCLK

YMLD

B7 B6 B5 B4 B3 B2 B1 B0

COMMAND 8bit

YMDATA

YMCLK

YMLD

S7 S6 S5 S4 S3 S2 S1 S0

STATUS 8bit

ZSENSE

B7 B6 B5 B4 B3 B2 B1 B0

COMMAND 8bit

YMDATA

YMCLK

YMLD

S7 S6 S1 S0

RESIDUAL DATA 15bit

ZSENSE

M1 M2 M7

0

16bit RESIDUAL DATA ENTRY

(lowest bit is 0)

Functional description

Read command format (Command 92 (memory residual read))

Read command format (Commands 90, 91, 93)

Microcontroller interface

Commands from the microcontroller are input using

3 bit serial inputs; data (YMDATA), bit clock

(YMCLK) and load signal (YMLD).

In the case of a read command from the microcontroller, bit serial data is output (ZSENSE) synchronized to the bit clock input (YMCLK).

Page 13

SM5859AF

NIPPON PRECISION CIRCUITS-13

Bit Name Function H operation Reset level

D7 MSWREN Encode sequence start/stop Start L

D6 MSWACL Write address reset Reset L

D5 MSRDEN Decode sequence start/stop Start L

D4 MSRACL Read address reset Reset L

D3 MSDCN2 MSDCN2=H, MSDCN1=H: 3-pair comparison start L

MSDCN2=H, MSDCN1=L: 2-pair comparison start

D2 MSDCN1 MSDCN2=L, MSDCN1=H: Direct-connect start L

MSDCN2=L, MSDCN1=L: Connect operation stop

D1 WAQV Q data valid Valid L

D0 MSON Memory system ON ON L

1000 0000

B0

B1

B2

B3

B4

B5

B6

B7

80hex

=

Anti-shock memory system settings

Bit Name Function H operation Reset level

D7

D6

D5 UC6OE Extension I/O port UC6 input/output setting Output L

D4 UC5OE Extension I/O port UC5 input/output setting Output L

D3 UC4OE Extension I/O port UC4 input/output setting Output L

D2 UC3OE Extension I/O port UC3 input/output setting Output L

D1 UC2OE Extension I/O port UC2 input/output setting Output L

D0 UC1OE Extension I/O port UC1 input/output setting Output L

1000 0001

B0

B1

B2

B3

B4

B5

B6

B7

81hex

=

Extension I/O port input/output settings

Bit Name Function H operation Reset level

D7

D6

D5 UC6WD Extension I/O port UC6 output data setting H output L

D4 UC5WD Extension I/O port UC5 output data setting H output L

D3 UC4WD Extension I/O port UC4 output data setting H output L

D2 UC3WD Extension I/O port UC3 output data setting H output L

D1 UC2WD Extension I/O port UC2 output data setting H output L

D0 UC1WD Extension I/O port UC1 output data setting H output L

1000 0010

B0

B1

B2

B3

B4

B5

B6

B7

82hex

=

Extension port HIGH/LOW output level

A port setting is invalid if that port has already been defined as an input using the 81H command above.

Command table

Write command summary

MS command 80

Extension I/O settings 81

Extension I/O output data settings 82

Page 14

NIPPON PRECISION CIRCUITS-14

SM5859AF

Bit Name Function H operation Reset level

D7 ATT Attenuator enable Attenuator ON L

D6 MUTE Forced muting (changes instantaneously) Mute ON L

D5 SOFT Soft muting (changes smoothly when ON only) Soft mute L

D4

D3 CMP12 12-bit comparison connect/ 16-bit comparison connect

12-bit comparison L

D2

D1

D0

1000 0011

B0

B1

B2

B3

B4

B5

B6

B7

83hex

=

Refer to Attenuation, Soft mute, Force mute.

Bit Name Function H operation Reset level

D7 K7 MSB 2 L

D6 K6 2 H

D5 K5 2 L

D4 K4 2 L

D3 K3 2 L

D2 K2 2 L

D1 K1 2 L

D0 K0 LSB 2 L

1000 0100

B0

B1

B2

B3

B4

B5

B6

B7

84hex

=

Refer to Attenuation, Soft mute, Force mute

-1

-2

-3

-4

-5

-6

-7

-8

Bit Name Function H operation Reset level

D7 RAM4M 4M (1M×4 bits)/1M (256K×4 bits) DRAM type setting 4M L

D6 RAMX2 Number of DRAMs setting (2 or 1) 2 L

D5 YFLGS FLAG6 set conditions (reset using status read command 90H) L

- When YFLGS=0, YFCKP=0, YFCLK input falling edge, YFLAG=L

- When YFLGS=0, YFCKP=1, YFCLK input rising edge, YFLAG=L

D4 YFCKP - When YFLGS=1, YFCKP=0, YFLAG=L L

- When YFLGS=1, YFCKP=1, YFLAG=H

D3 COMPFB Full-bit non compression mode L

D2 COMP6B 6-bit compression mode H

D1 COMP5B 5-bit compression mode L

D0 COMP4B 4-bit compression mode L

1000 0101

B0

B1

B2

B3

B4

B5

B6

B7

85hex

=

When the number of compression bits is set incorrectly (2 or more bits in D0 to D3 are set to 1 or all bits are set to 0),

6-bit compression mode is selected.

ATT, MUTE settings 83

Attenuation level settings 84

Option settings 85

Page 15

SM5859AF

NIPPON PRECISION CIRCUITS-15

Bit Name Function HIGH-level state

S7 FLAG6 Signal processor IC jitter margin exceeded Exceeded

S6 MSOVF Write overflow (Read once only when RA exceeds WA) DRAM overflow

S5

S4

S3 DCOMP Data compare-connect sequence operating Compare-connect sequence operating

S2 MSWIH Encode sequence stop due to internal factors Encoding stopped

S1 MSRIH Decode sequence stop due to internal factors Decoding stopped

S0

1001 0000

B0

B1

B2

B3

B4

B5

B6

B7

90hex

=

Refer to Status flag operation summary

Bit Name Function HIGH-level state

S7 MSEMP Valid data empty state (Always HIGH when RA exceeds VWA) No valid data

S6 OVFL Write overflow state (Always HIGH when WA exceeds RA) Memory full

S5 ENCOD Encode sequence operating state Encoding

S4 DECOD Decode sequence operating state Decoding

S3

S2

S1

S0

1001 0001

B0

B1

B2

B3

B4

B5

B6

B7

91hex

=

Refer to Status flag operation summary.

Read command summary

Anti-shock memory status (1) 90

Anti-shock memory status (2) 91

Page 16

NIPPON PRECISION CIRCUITS-16

SM5859AF

Bit Name Function HIGH-level state

S7

S6

S5 UC6RD

S4 UC5RD

S3 UC4RD

S2 UC3RD

S1 UC2RD

S0 UC1RD

1001 0011

B0

B1

B2

B3

B4

B5

B6

B7

93hex

=

Input data entering (or output data) an extension port terminal is echoed to the microcontroller.

(That is, the input data entering an I/O port configured as an input port using the 81H command,

OR the output data from a pin configured as an output port using the 82H command.)

Bit Name Function

S7 AM20 Valid data accumulated VWA-RA (MSB) 4M bits

S6 AM19

S5 AM18

S4 AM17

S3 AM16

S2 AM15

S1 AM14

S0 AM13

M1 AM12

M2 AM11

M3 AM10

M4 AM09

M5 AM08

M6 AM07

M7 AM06

M8 AM05 to 0 constant output

... AM00

1001 0010

B0

B1

B2

B3

B4

B5

B6

B7

92hex

=

Note. The time conversion factor varies depending on the compression bit mode.(M = 1,048,576 K= 1,024)

Residual time (sec) = Valid data residual (Mbits) × Time conversion value k

where the Time conversion value k (sec/Mbit) = 2.78(4 bits), 2.22 (5 bits), 1.85 (6 bits) and 0.74 (Full bits).

2M bits

1M bits

512K bits

256K bits

128K bits

64K bits

32K bits

16K bits

8K bits

4K bits

512 bits

2K bits

1K bits

256 bits

128 to 4 bits

Anti-shock memory valid data residual 92

Extension I/O inputs 93

Page 17

SM5859AF

NIPPON PRECISION CIRCUITS-17

Flag Read

name method

FLAG6 READ Meaning - Indicates to the CD signal processor DSP (used for error correction, de-interleaving) that a

90H disturbance has exceeded the RAM jitter margin.

bit 7 Set - Set according to the YFLAG input and the operating state of YFCKP and YFLGS.

FLAG6 set conditions

When YFLGS=0, YFCKP=0, YFCLK input falling edge, YFLAG=L

When YFLGS=0, YFCKP=1, YFCLK input rising edge, YFLAG=L

When YFLGS=1, YFCKP=0, YFLAG=L

When YFLGS=1, YFCKP=1, YFLAG=H

Reset - By 90H status read

- By 80H command when MSON=ON

- After external reset

MSOVF READ Meaning - Indicates once only that a write to external DRAM has caused an overflow. (When reset

90H by the 90H status read command, this flag is reset even if the overflow condition continues.)

bit 6 Set - When the write address (WA) exceeds the read address (RA)

Reset - By 90H status read

- When a read address clear (MSRACL) or write address clear (MSWACL) command is issued

- After external reset

DCOMP READ Meaning - Indicates that a compare-connect sequence is operating

90H Set - When a (3-pair or 2-pair) compare-connect start command is received (MSDCN2=1)

bit 3 - When a direct connect command is received (MSDCN2=0, MSDCN1=1)

Reset - When a (3-pair or 2-pair) comparison detects conforming data

- When the connect has been performed after receiving a direct connect command

- When a compare-connect stop command (MSDCN2=0, MSDCN1=0) is received

- When a MSWREN=1 command is received (However, if a compare-connect command is

received at the same time, the compare-connect command has priority.)

- After external reset

MSWIH READ Meaning - Indicates that the encode sequence has stopped due to internal factors

90H (not microcontroller commands)

bit 2 Set - When FLAG6 (above) is set

- When MSOVF (above) is set

Reset - When conforming data is detected after receiving a compare-connect start command

- When the connect has been performed after receiving a direct connect command

- When a read address clear (MSRACL) or write address clear (MSWACL) command is received

- After external reset

MSRIH READ Meaning - Indicates that the decode sequence has stopped due to internal factors

90H (not microcontroller commands)

bit 1 Set - When the valid data residual becomes 0

Reset - By 90H status read

- When a read address clear (MSRACL) or write address clear (MSWACL) command is issued

- After external reset

Status flag operation summary

Page 18

NIPPON PRECISION CIRCUITS-18

SM5859AF

Flag Read

name method

MSEMP READ Meaning - Indicates that the valid data residual has become 0

91H Set - When the VWA (final valid data's next address)

bit 7 = RA (address from which the next read would take place)

Reset - Whenever the above does not apply

OVFL READ Meaning - Indicates a write to external DRAM overflow state

91H Set - When the write address (WA) exceeds the read address (RA).

bit 6 (Note: This flag is not set when WA=RA through an address initialize or reset operation.)

Reset - When the read address (RA) is advanced by the decode sequence

- When a read address clear (MSRACL) or write address clear (MSWACL) command is issued

- After external reset

ENCOD READ Meaning - Indicates that the encode sequence (input data entry, encoding, DRAM write) is operating

91H Set - By the 80H command when MSWREN=1

bit 5 - When conforming data is detected during compare-connect operation

- When the connect has been performed after receiving a direct connect command

Reset - When the FLAG6 flag=1 (above)

- When the OVFL flag=1 (above)

- By the 80H command when MSWREN=0

- By the 80H command when MSDCN1=1 or MSDCN2=1 (compare-connect start command)

- By the 80H command when MSON=0

- After external reset

Note. Reset conditions have priority over set conditions. For example, if the 80H command has

MSWREN=1 and MSDCN1=1, the ENCOD flag is reset and compare-connect operation starts.

DECOD READ Meaning - Indicates that the decode sequence (read from DRAM, decoding,

91H attenuation, data output) is operating

bit 4 Set - By a new 80H command when MSRDEN=1 and the MSEMP flag=0 (above)

Reset - Whenever the above does not apply

Page 19

SM5859AF

NIPPON PRECISION CIRCUITS-19

- MSWREN

When 1: Encode sequence starts

Invalid when MSON is not 1 within the

same 80H command

Invalid when FLAG6=1

Invalid when OVFL=1

Invalid when a compare-connect start

command (MSDCN2=1 or MSDCN1=1)

occurs simultaneously

Direct connect if a compare-connect

sequence is already operating

When 0: Encode sequence stops

- MSWACL

When 1: Initializes the write address (WA)

When 0: No operation

- MSRDEN

When 1: Decode sequence starts

Does not perform decode sequence if

MSON=1.If there is no valid data, decode

sequence temporarily stops. But, because

the MSRDEN flag setting is maintained as

is, the sequence automatically re-starts

when valid data appears.

When 0: Decode sequence stops

-MSRACL

When 1: Initializes the read address (RA)

When 0: No operation

- MSDCN2, MSDCN1

When 1 and 1: 3-pair compare-connect sequence

starts

When 1 and 0: 2-pair compare-connect sequence

starts

When 0 and 1: Direct connect sequence starts

When 0 and 0: Compare-connect sequence stops.

No operation if a compare-connect

sequence is not operating.

- WAQV

When 1: The immediately preceding YBLKCK

falling-edge timing WA (write address)

becomes the VWA (valid write address).

When 0: No operation

- MSON

When 1: Memory system turns ON and compres-

sion-type shock-proof operation starts

When 0: Memory system turns OFF and through-

mode playback starts. (In this mode, the

attenuator is still active.)

Write command supplementary information

80H (MS command)

81H (I/O setting on extension I/O)

82H (Setting output data on extension I/O)

Page 20

NIPPON PRECISION CIRCUITS-20

SM5859AF

85H (option settings)

- RAM4M

When 1: Uses 4M DRAMs (1M×4 bits)

When 0; Uses 1M DRAMs (256K×4 bits)

- RAMX2

When 1: Uses 2 DRAMs

When 0: Uses a single DRAM

- YFLGS, YFCKP

see 9-2-3.

When 0 and 0: Sets FLAG6 on the falling edge of

YFCLK when YFLAG=0

When 0 and 1: Sets FLAG6 on the rising edge of

YFCLK when YFLAG=0

When 1 and 0: Sets FLAG6 when YFLAG=0

When 1 and 1: Sets FLAG6 when YFLAG=1

- COMPFB, COMP6B, COMP5B, COMP4B

When 0, 0, 0 and 1: Selects 4-bit compression

mode

When 0, 0, 1 and 0: Selects 5-bit compression

mode

When 1, 0, 0 and 0: Selects full-bit compression

mode

In all other cases: Selects 6-bit compression mode

Changing mode without initialize in operation is possible.

83H (ATT, MUTE settings)

- ATT (attenuator enable)

When 1: Attenuator settings become active (84H

command)

When 0: Attenuator settings become inactive, and

output continues without attenuation

- MUTE (forced muting)

When 1: Outputs are instantaneously muted to

0.(note 1)

Same effect as taking the YDMUTE pin

HIGH.

When 0: No muting(note 1)

(note1) Effective at the start of a Left-channel output data.

- SOFT (soft muting)

When 1: Outputs are smoothly muted to 0.

When 0: No muting.

Soft mute release occurs instantaneously

to either the value set by the 84H command (When ATT=1) or 0dB (When

ATT=0)

- MUTE, SOFT, YDMUTE relationship

When all mute inputs are 0, mute is released.

- CMP12 (12-bit comparison connection)

When 1: Performs comparison connection using

only the most significant 12 bits of input

data.

When 0: Performs comparison connection using

all 16 bits of input data.

Page 21

SM5859AF

NIPPON PRECISION CIRCUITS-21

Shock-proof mode is the mode that realizes shockproof operation using external DRAM. Shock-proof

mode is invoked by setting MSON=H in microcon-

troller command 80H.

This mode comprises the following 3 sequences.

Shock-proof operation overview

- Encode sequence

1. Input data from a signal processor IC is stored in

internal buffers.

2. Encoder starts after a fixed number of data have

been received.

3. The encoder, after the most suitable predicting

filter type and quantization steps have been determined, performs APC encoding and then writes to

external DRAM.

- Decode sequence

1. Reads compressed data stored in external buffer

RAM at rate fs.

2. Decoder starts, using the predicting filter type

and quantization levels used when encoded.

3. Performs attenuation operation (including muting

operation)

4. Outputs the result.

- Compare-connect sequence

1. Encoding immediately stops when either external

buffer RAM overflows or when a CD read error

occurs due to shock vibrations.

2. Then, using microcontroller command 80H, the

compare-connect start command is executed and

compare-connect sequence starts.

3. Compares data re-read from the CD with the processed final valid data stored in RAM (confirms its

correctness).

4. As soon as the comparison detects conforming

data, compare-connect sequence stops and

encode sequence re-starts, connecting the data

directly behind previous valid data.

Page 22

NIPPON PRECISION CIRCUITS-22

SM5859AF

13.3ms

VWA latch set

WAQV set

VWA(x) VWA(x + 1)

YBLKCK

Microcontroller data set

Refer to Microcontroller interface

VWA

Values shown are for rate fs. The values are 1/2 those shown at rate 2fs.

Fig 2. YBLKCK and VWA relationship

The VWA is determined according to the YBLKCK

pin and WAQV command. Refer to the timing chart

below.

1.YBLKCK is a 75 Hz clock(HIGH) when used for

normal read mode and it is a 150Hz clock when

used for double-speed read mode. Both modes

clock are synchronized to the CD format block end

timing.

When this clock goes LOW, WA which is the write

address of internal encode sequence, is stored

(see note 2).

2.The microcontroller checks the subcode and, if

confirmed to be correct, generates a WAQV command (80H).

3.When the WAQV command is received, VWA is

updated according to the previously latched WA.

(note 2) Actually, there is a small time difference, or

gap, between the input data and YBLKCK. This gap

serves to preserves the preceding WA to protect

against incorrect operation.

RAM addresses

The SM5859 uses either 1 or 2 external 1M or 4M

DRAMs as external buffers.

Three kinds of addresses are used for external

RAM control.

WA (write address)

RA (read address)

VWA (valid write address)

Among these, VWA is the write address for conforming data whose validity has been confirmed.

Determination of the correctness of data read from

the CD is delayed relative to the encode write processing, so VWA is always delayed relative to WA.

The region available for valid data is the area

between VWA-RA.

- Connect data work area

This is an area of memory reserved for connect

data. This area is 2Kbits if using 1M DRAMs, or

4Kbits if using 4M DRAMs.

Fig1. RAM addresses

RA

WA

VWA

Valid data

area

Connect data work area

VWA (valid write address)

Page 23

SM5859AF

NIPPON PRECISION CIRCUITS-23

Correct data demodulation becomes impossible for

the CD signal processor IC when a disturbance

exceeding the RAM jitter margin occurs. The

YFLAG signal input pin is used to indicate when

such a condition has occurred.

The YFCLK signal is a 7.35 kHz clock synchronized

to the CD format frame 1.

The IC checks the YFLAG input and stops the

encode sequence when such a disturbance has

occurred, and then makes FLAG6 active.

The YFLAG check method used changes depending on the YFLGS flag and YFCKP flag (85H command). See table1.

If YFLGS is set to 1, then YFCLK should be tied

either High or Low.

YFLAG, YFCLK, FLAG6

85H command

YFLGS YFCKP FLAG6 set conditions FLAG6 reset conditions

1 0 0 When YFLAG=LOW on YFCLK input falling edge - By status read (90H command)

2 1 When YFLAG=LOW on YFCLK input rising edge - When MSON=LOW

3 1 0 When YFLAG=LOW YFCLK be tied either High or Low - After system reset

4 1 When YFLAG=HIGH

Table1. YFLAG signal check method

Page 24

NIPPON PRECISION CIRCUITS-24

SM5859AF

Compare-connect sequence

The SM5859 supports three kinds of connect

modes; 3-pair compare-connect, 2-pair compareconnect and direct connect.

Note that the SM5859 can also operate in 12-bit

comparison connect mode using only the most significant 12 bits of data for connection operation.

In 3-pair compare-connect mode, the final 6 valid

data (3 pairs of left- and right-channel data input

before encode processing) and the most recently

input data are compared until three continuous data

pairs all conform. At this point, the encode

sequence is re-started and data is written to VWA.

In 2-pair compare-connect mode, comparison

occurs just as for 3-pair comparison except that

only 2 pairs from the three compared need to conform with the valid data. At this point, the encode

sequence is re-started and data is written to VWA.

In direct-connect mode, comparison is not performed at all, and encode sequence starts and data

is written to the VWA. This mode is for systems that

cannot perform compare-connect operation.

- Compare-connect preparation time

1. Comparison data preparation time

Internally, when the compare-connect start com-

mand is issued, a sequence starts to restore the

data for comparison. The time required for this

preparation after receiving the command is approximately 2.5 × (1/fs). (approximately 60 µs when fs =

44.1 kHz)

2. After the above preparation is finished, data is

input beginning from the left-channel data and comparison starts.

3. If the compare-connect command is issued

again, the preparation time above is not necessary

and operation starts from step 2.

4. The same sequence takes place in direct-connect mode also. However, at the point when 3

words have been input, all data is directly connected as if comparison and conformance had taken

place.

- Compare-connect sequence stop

If a compare-connect stop command (80H with

MSDCN1= 1, MSDCN2= 0) is input from the microcontroller, compare-connect sequence stops.

If compare-connect sequence was not operating,

the compare-connect stop command performs no

operation. However, make sure that the other bit

settings within the same 80H command are valid.

Page 25

SM5859AF

NIPPON PRECISION CIRCUITS-25

- DRAM initialization refresh

A 15-cycle RAS-only refresh is carried out for

DRAM initialization under the following condition.

When MSON changes from 0 to 1 in command

80H.

When from MSON=1, MSRDEN=0 and

MSWREN=0 states only MSWREN changes to 1.

In this case, encode sequence immediately starts

and initial data is written (at 2fs rate input) after a

delay of 0.7ms.

- Refresh during Shock-proof mode operation

In this IC, a data access operation to any address

also serves as a data refresh. Accordingly, there

are no specific refresh cycles other than the initialization refresh cycle (described above).

This has the resulting effect of saving on DRAM

power dissipation.

A data access to DRAM can occur in an encode

sequence write operation or in a decode sequence

read operation. In an encode sequence write operation the connect operation is stopped, while in a

decode sequence read operation the data is always

output to the D/A converter in a fixed manner. The

refresh rate for each DRAM during decode

sequence is shown in the table below.

The decode sequence, set by MSON=1 and MSRDEN=1, operates when valid data is in DRAM

(when MSEMP=0).

- When MSON=0 or both ENCOD and DECOD=0

(both encode sequence and decode sequence are

stopped), DRAM is not refreshed because no data

is being accessed.

DRAM refresh

Table 2. Decode sequence refresh rate

DRAMs used (same for 1 or 2 DRAMs)

Data compression mode 1M (256K×4 bits) 4M (1M×4 bits)

4 bit 5.44 ms 10.88 ms

5 bit 4.35 ms 8.71 ms

6 bit 3.63 ms 7.26 ms

Full bit 1.36 ms 2.72 ms

Encode sequence temporary stop

- When RAM becomes full, MSWREN is set LOW

using the 80H command and encode sequence

stops. (For details of the stop conditions, refer to

the description of the ENCOD flag.)

- Then, if MSWREN is set HIGH without issuing a

compare-connect start command, the encode

sequence re-starts. At this time, newly input data is

written not to VWA, but to WA. In this way, the data

already written to the region between VWA and WA

is not lost.

- But if the MSWREN is set HIGH (80H command)

after using the compare-connect start command

even only once, data is written to VWA. If data is

input before comparison and conformance is

detected, the same operation as direct-connect

mode takes place when the command is issued.

After comparison and conformance are detected,

no operation is performed because the encode

sequence has already been started. However,

make sure that the other bit settings within the

same 80H command are valid.

Page 26

NIPPON PRECISION CIRCUITS-26

SM5859AF

WA CAS

RA CAS

Encode compression mode

Decode compression mode

ZSRDATA

3FE 3FF

001 002 004 005

3FD 3FE 3FF 001 002

A

YMLD

When 85H generated

AB

B

003

Selecting compression mode

Even when the compression mode in selected with

the 85H command during shock-proof operation,no

malfunction occurs.

The compression mode change is not performed

immediately after input of the 85H command, but it

is performed at the following timing.

After changing the mode, zero data of one block is

output.

(note) CAS-000 is connect data.

Page 27

SM5859AF

NIPPON PRECISION CIRCUITS-27

Through-mode operation

If MSON is set LOW (80H command), an operating

mode that does not perform shock-proof functions

becomes active. In this case, input data is passed

as-is (after attenuator and mute operations) to the

output. External DRAM is not accessed.

- In this case, input data needs to be at a rate fs

and the input word clock must be synchronized to

the CLK input (384fs). However, short range jitter

can be tolerated (jitter-free system).

- Jitter-free system timing starts from the first

YLRCK rising edge after either (A) a reset

(NESET= 0) release by taking the reset input from

LOW to HIGH or (B) by taking MSON from HIGH to

LOW. Accordingly, to provide for the largest possible jitter margin, it is necessary that the YLRCK

clock be at rate fs by the time jitter-free timing

starts.

The jitter margin is 0.2/ fs.

This jitter margin is the allowable difference

between the system clock (CLK) 1/ 384 divided, fs

rate clock and the YLRCK input clock.

If the timing difference exceeds the jitter margin,

irregular operation like data being output twice or

conversely complete “1” data output may occur. In

the worst case, a click noise will also be generated.

- The attenuation register is set by the 84H command.

- The attenuation register set value becomes active

when the 83H command sets the ATT flag to 1.

When the ATT flag is 0, the attenuation register

value is considered to be the equivalent of 256 for a

maximum gain of 0 dB.

- The gain (dB) is given from the set value (Datt)

by the following equation.

Gain = 20 × log(Datt/256) [dB]; left and right channels

- For the maximum attenuation register set value

(Datt = 255), the corresponding gain is -0.03 dB.

But when the ATT flag is 0 (Datt = 256), there is no

attenuation.

- After a system reset initialization, the attenuation

register is set to 64 (-12 dB). However, because the

ATT flag is reset to 0, there is no attenuation.

- When the attenuation register setting changes or

when the ATT flag changes, the gain changes

smoothly from the previous set gain towards the

new set value. If a new value for the attenuation

level is set before the previously set level is

reached, the gain changes smoothly towards the

latest setting.

The gain changes at a rate of 4 × (1/fs) per step. A

full-scale change (255 steps) takes approximately

23.3 ms (when fs = 44.1 kHz). See fig 3.

Attenuation

Fig 3 Attenuation operation example

set 3

Gain

set 5

set 1

set 4set 2

time

Page 28

NIPPON PRECISION CIRCUITS-28

SM5859AF

Force mute

Soft mute

Soft mute operation is controlled by the SOFT flag

using a built-in attenuation counter.

Mute is ON when the SOFT flag is 1. When ON, the

attenuation counter output decrement by 1 step at a

time, thereby reducing the gain. Complete mute

takes 1024/fs (or approximately 23.2 ms for fs =

44.1 kHz).

Conversely, mute is released when the SOFT flag

is 0. In this case, the attenuation counter instantaneously increases. The attenuation register takes

on the value when the ATT flag was 1. If the ATT

flag was 0, the new set value is 256 (0 dB).

Fig 4. Soft mute operation example

256 step

/ 1024TS

SOFT

Attenation level

or full scale

− ∞

(Gain)

Serial output data is muted by setting the YDMUTE

pin input HIGH or by setting the MUTE flag to 1.

Mute starts and finishes on the leading left-channel

bit.

When MSON is HIGH and valid data is empty

(MSEMP=H), the output is automatically forced into

the mute state.

12-bit comparison connection

When the CMP12 flag is set to 1, the least significant 4 bits of the 16-bit comparison connection

input data are discarded and comparison connection is performed using the remaining 12 bits.

Note that if the CMP12 flag is set to 1 during a comparison connection operation, only the most significant 12 bits are used for comparison connection

from that point on.

Page 29

SM5859AF

NIPPON PRECISION CIRCUITS-29

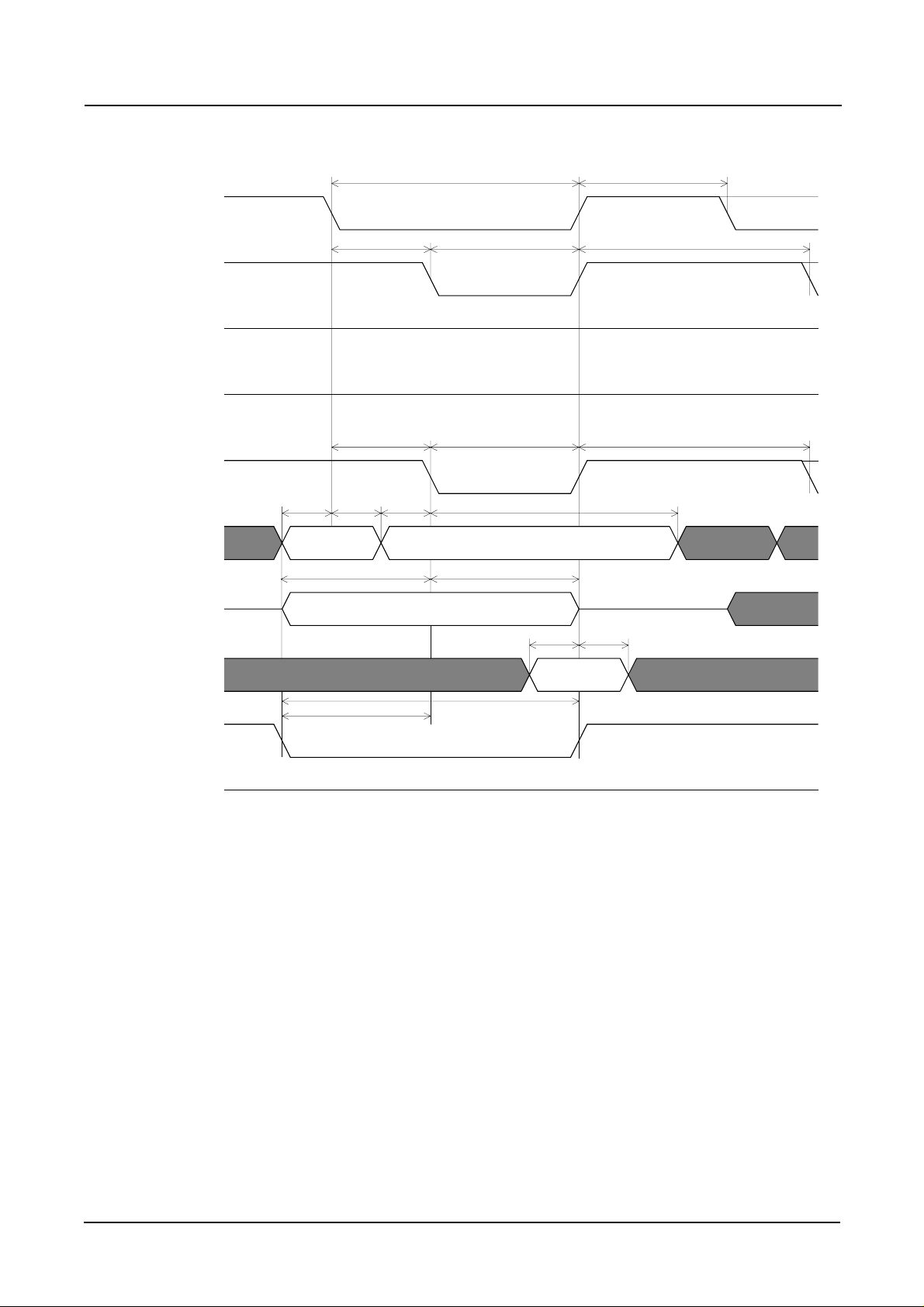

YLRCK

16

LSB

MSB

LSB

MSB

R channel

LSB

YSCK

YSRDATA

L channel

1/2fs

16

9

ZLRCK

1 33 48

LSB

MSB

LSB

MSB

R channel

LSB

1/fs

ZSCK

ZSRDATA

L channel

24

Timing charts

Input timing (YSCK, YSRDATA, YLRCK)

Output timing (ZSCK, ZSRDATA, ZLRCK)

Page 30

NIPPON PRECISION CIRCUITS-30

SM5859AF

NCAS

A0 to A9

D0 to D3

(WRITE)

NRAS

NOE

(WRITE)

NWE

(WRITE)

RCD

t

RASH

t

RASL

t

t

CASL

CASH

t

CADS

t

RADH

t

t

RADS CADH

t

CWDS

t

CWDH

t

WEL

t

NCAS

(DRAM1 SELECT)

A0 to A9

D0 to D3

(WRITE)

NRAS

NWE

(WRITE)

NCAS

(DRAM2 SELECT)

NCAS2

(DRAM1 SELECT)

NCAS2

(DRAM2 SELECT)

RCD

tt

CASL CASH

t

RASH

t

RASL

t

WEL

t

CWDH

t

CWDS

t

RADS

t

RADH

t

CADS

tt

CADH

t

CASLRCD

t

CASH

t

DRAM write timing (NRAS, NCAS, NOE, NWE, A0 to A9, D0 to D3)

Write timing (with single DRAM)

Write timing (with 2 DRAMs)

Page 31

SM5859AF

NIPPON PRECISION CIRCUITS-31

NCAS

A0 to A9

NRAS

D0 to D3

(READ)

NOE

(READ)

NWE

(READ)

RASL

t

RASH

t

CASH

tt

CASLRCD

t

RADS

tt

RADH CADS

t

CADH

t

CRDS

t

CRDH

t

OEL

t

NCAS

(DRAM1 SELECT)

A0 to A9

NRAS

D0 to D3

(READ)

NWE

(READ)

NCAS

(DRAM2 SELECT)

NCAS2

(DRAM1 SELECT)

NCAS2

(DRAM2 SELECT)

RASH

t

RASL

t

RCD

tt

CASL CASH

t

CASH

tt

CASLRCD

t

RADStRADH

t

CADS

t

CADH

t

CRDS

t

CRDH

t

DRAM read timing (NRAS, NCAS, NOE, NWE, A0 to A9, D0 to D3)

Read timing (with single DRAM)

Read timing (with 2 DRAMs)

Page 32

NIPPON PRECISION CIRCUITS-32

SM5859AF

Microcon-

troller

DSP

Matsushita

MN662740

D/A

converter

SM5859

DRAM 1 DRAM 2

YMDATA

YMCLK

YMLD

ZSENSE

YBLKCK

YFCLK

YFLAG

YLRCK

YSCK

YSRDATA

ZLRCK

ZSCK

ZSRDATA

UC1 to UC6

NRAS

NWE

A0 to A9

D0 to D3

NCAS2

A0 to A9

D0 to D3

A0 to A9

D0 to D3

CLK

NRESET

YDMUTE

NCAS

GND GND

DSP

SONY

CXD2517

D/A

converter

SM5859

DRAM 1 DRAM 2

YMDATA

YMCLK

YMLD

ZSENSE

YBLKCK

YFCLK

YFLAG

YLRCK

YSCK

YSRDATA

ZLRCK

ZSCK

ZSRDATA

UC1 to UC6

NRAS

NWE

A0 to A9

D0 to D3

NCAS2

A0 to A9

D0 to D3

A0 to A9

D0 to D3

CLK

NRESET

YDMUTE

NCAS

GND GND

GND

SCOR

XROF

Microcon-

troller

RAS

WE

OECAS

RAS

WE

OECAS

RAS

WE

OECAS

RAS

WE

OECAS

Connection example

note1

- When 2 DRAMs are used, the DRAM OE pins should be tied LOW.

- When single DRAM is used, the DRAM OE pin should be tied LOW

or controlled by the SM5859 NOE signal.

note 2 When CXD 2517 (Sony) is used

Set 85H of microcontroller command (option setting) as setting YFLAG take in;

D5: YFLAGS= 1

D4: YFCKP= 0

Page 33

NIPPON PRECISION CIRCUITS-33

SM5859AF

NC9605DE 1997.5

NIPPON PRECISION CIRCUITS INC.

NIPPON PRECISION CIRCUITS INC. reserves the right to make changes to the products described in this data sheet in order to

improve the design or performance and to supply the best possible products. Nippon Precision Circuits Inc. assumes no responsibility for

the use of any circuits shown in this data sheet, conveys no license under any patent or other rights, and makes no claim that the circuits

are free from patent infringement. Applications for any devices shown in this data sheet are for illustration only and Nippon Precision

Circuits Inc. makes no claim or warranty that such applications will be suitable for the use specified without further testing or modification. The products described in this data sheet are not intended to use for the apparatus which influence human lives due to the failure or

malfunction of the products. Customers are requested to comply with applicable laws and regulations in effect now and hereinafter, including compliance with export controls on the distribution or dissemination of the products. Customers shall not export, directly or indirectly, any products without first obtaining required licenses and approvals from appropriate government agencies.

NIPPON PRECISION CIRCUITS INC.

4-3, 2-chome Fukuzumi, Koto-ku

Tokyo, 135 -8430, JAPAN

Telephon: 03-3642-6661

Facsimile: 03-3642-6698

Loading...

Loading...