NPC SM5837AF Datasheet

SM5837AF

NIPPON PRECISION CIRCUITS INC.

OVERVIEW

The SM5837AF is a variable-length delay line LSI.

It has 12-bit input/output signal which can be set to

undergo a delay in the range of 31 to 2078 delay bits.

Maximum operating frequency is 40 MHz, making it

ideal for use in video signal processing applications.

FEATURES

■

Variable-length 1H delay

■

12-bit input/output signal width

■

31 to 2078- bit delay length range

■

40 MHz maximum operating frequency

■

Selectable delay setting method

• 11-bit parallel input

• 3-line serial input

■

TTL-compatible input/outputs

■

Tristate outputs

■

4.75 to 5.25 V operating voltage

■

44-pin QFP

■

Molybenum-gate CMOS process

Variable-length 1H Delay Line LSI

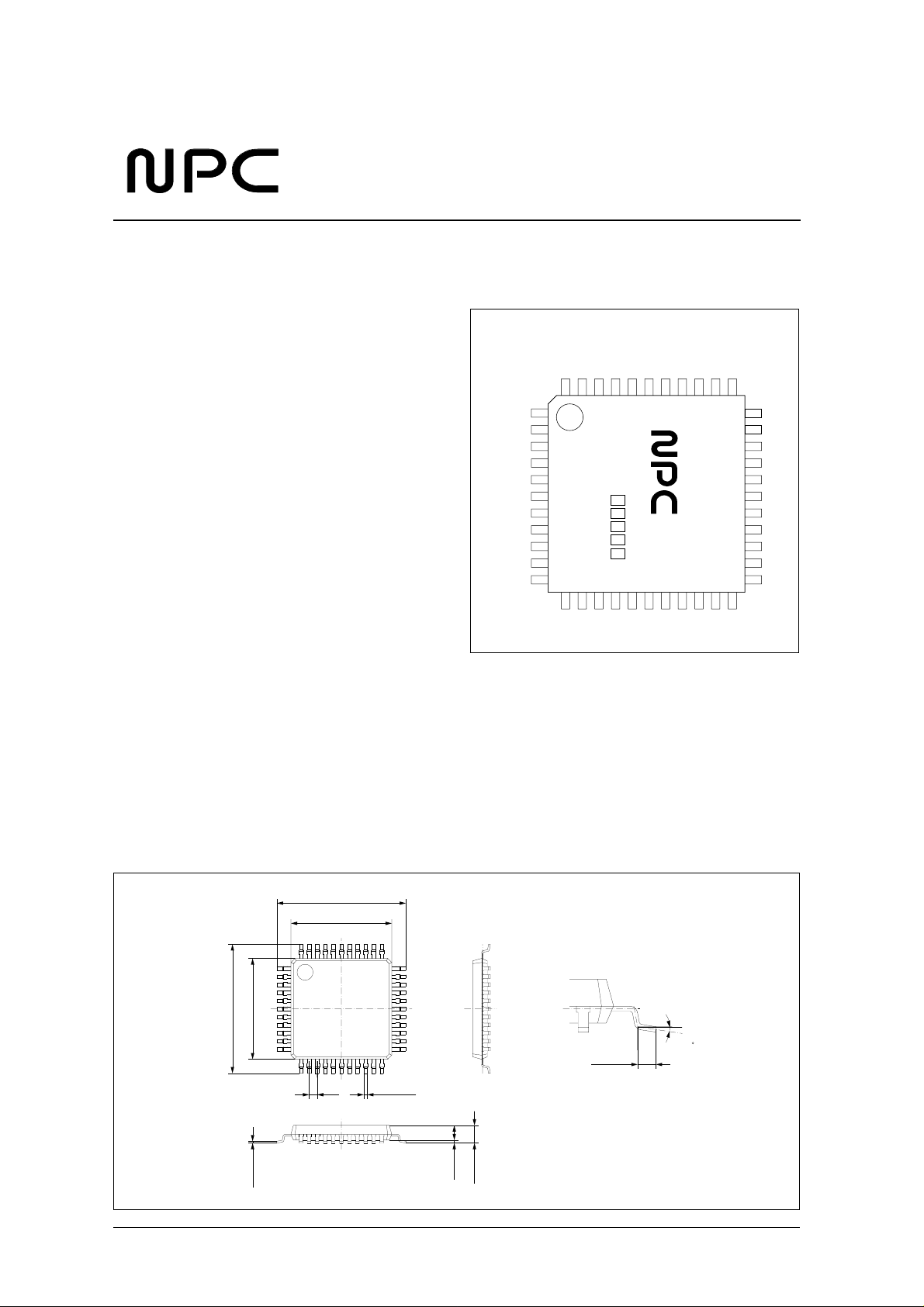

PINOUT

TOP VIEW

RSTN

(NC)

PARA

DI0

DI1

DI2

DI3

DI4

DI5

DI6

DI7

34

35

36

37

38

39

40

41

42

43

44

DO8

(NC)

33

DI8

32

DI9

31

DI10

30

DI11

29

OE

28

CLK

27

VDD

26

DO11

25

DO10

24

DO9

23

DO8

DL0/SDI

DL1/SICK

DL2/LEN

DL3

DL4

VSS1

DL5

DL6

DL7

DL8

DL9

1

2

3

4

5

6

7

8

9

10

11

1213141516171819202122

DL10

DO0

DO1

DO2

SM5837AF

DO3

VSS2

DO4

DO5

DO7

APPLICATIONS

■

Video signal image processing

PACKAGE DIMENSIONS

Unit: mm

44-pin QFP

-

+

10.00

12.80 0.30

+

12.80 0.30

-

10.00

0.80

+

0.35 0.10

-

+

0.60 0.20

-

0 to 10

+

-

0.17 0.05

0 to 0.20 1.45

1.75MAX

NIPPON PRECISION CIRCUITS—1

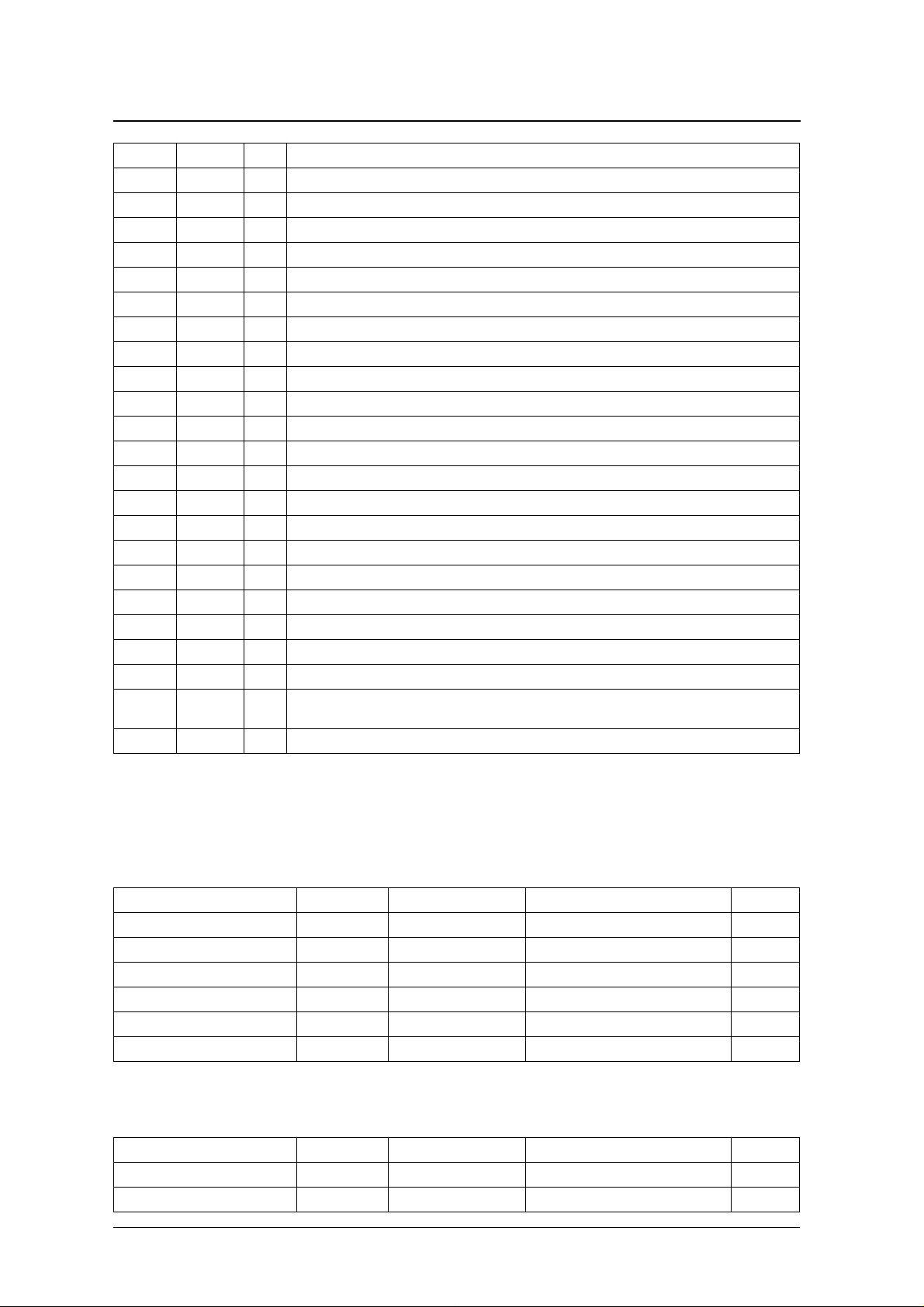

BLOCK DIAGRAM

SM5837AF

DI0 - 11

12 12 12

CLK

RSTN

PARA

SDI

SICK

LEN

Variable-length

12-bit

1H Delay

Delay Length Control

11

Parallel/Serial Select

11

SIPO

DL0 - 10

Output Buffer

11

PIN DESCRIPTION

Number Name I/O

1 DL0/SDI Ip Delay length set parallel data bit DL0 (LSB) when PARA is HIGH, and SDI serial data input when PARA is LOW.

2 DL1/SICK Ip Delay length set parallel data bit DL1 (bit 1) when PARA is HIGH, and SICK shift clock when PARA is LOW.

3 DL2/LEN Ip Delay length set parallel data bit DL2 (bit 2) when PARA is HIGH, and LEN latch clock when PARA is LOW.

4 DL3 Ip Delay length set data bit 3

5 DL4 Ip Delay length set data bit 4

6 VSS1 – Ground (0 V) pin 1

7 DL5 Ip Delay length set data bit 5

8 DL6 Ip Delay length set data bit 6

9 DL7 Ip Delay length set data bit 7

10 DL8 Ip Delay length set data bit 8

11 DL9 Ip Delay length set data bit 9

12 DL10 Ip Delay length set data bit 10

13 DO0 O Signal output data bit 0

14 DO1 O Signal output data bit 1

15 DO2 O Signal output data bit 2

16 DO3 O Signal output data bit 3

17 VSS2 – Ground (0 V) pin 2

18 DO4 O Signal output data bit 4

19 DO5 O Signal output data bit 5

20 DO6 O Signal output data bit 6

21 DO7 O Signal output data bit 7

(1)

Function

DO0 - 11

OE

VDD

VSS2

VSS1

NIPPON PRECISION CIRCUITS—2

−

−

−

°

°

−

° C

SM5837AF

Number Name I/O

22 NC – No connection

23 DO8 O Signal output data bit 8

24 DO9 O Signal output data bit 9

25 DO10 O Signal output data bit 10

26 DO11 O Signal output data bit 11

27 VDD – Supply (5 V) pin

28 CLK I Clock input

29 OE Ip Tristate output enable. Enable when HIGH, and disable when LOW.

30 DI11 Ip Signal input data bit 11

31 DI10 Ip Signal input data bit 10

32 DI9 Ip Signal input data bit 9

33 DI8 Ip Signal input data bit 8

34 DI7 Ip Signal input data bit 7

35 DI6 Ip Signal input data bit 6

36 DI5 Ip Signal input data bit 5

37 DI4 Ip Signal input data bit 4

38 DI3 Ip Signal input data bit 3

39 DI2 Ip Signal input data bit 2

40 DI1 Ip Signal input data bit 1

41 DI0 Ip Signal input data bit 0

42 RSTN Ip Reset pin. Normal operation when HIGH, and reset operation when LOW.

43 PARA Ip

44 NC – No connection

(1)

Delay length setting method select.

Parallel data (DL0 to DL10) when HIGH, and serial input (SDI, SICK, LEN) when LOW.

Function

1. Ip = input pin with built-in pull-up resistor, O = output.

SPECIFICATIONS

Absolute Maximum Ratings

V

= V

SS

Supply voltage range V

Input voltage range V

Storage temperature range T

Power dissipation P

Soldering temperature T

Soldering time t

Recommended Operating Conditions

V

= 0 V

SS

Supply voltage range V

Operating temperature T

= V

SS1

Parameter Symbol Condition Rating Unit

Parameter Symbol Condition Rating Unit

SS2

= 0 V

DD

IN

stg

D

sld

sld

DD

opr

0.3 to 7.0 V

V

0.3 to V

SS

4.75 to 5.25 V

+ 0.3 V

DD

40 to 125

450 mW

255

10 s

20 to 70

C

C

NIPPON PRECISION CIRCUITS—3

Loading...

Loading...