−

SM5170AV

NIPPON PRECISION CIRCUITS INC.

OVERVIEW

The SM5170AV is a PLL synthesizer IC developed

for application in pagers. It incorporates independently-controlled reference frequency and FIN input

frequency dividers, and operates from a low-voltage

FEATURES

■

Supply voltages

•V

= 0.95 to 1.2 V

DD1

(prescaler, counters)

•V

■

FIN input frequency

•f

•f

= 2.0 to 3.3 V (charge pump)

DD2

= 300 MHz (V

FIN

= 330 MHz (V

FIN

= 0.95 V)

DD1

= 1.0 V)

DD1

PINOUT

PLL Synthesizer IC

supply to realize low power dissipation. It features a

charge pump that operates at 3 V, making possible a

wide range of VCO designs.

■

Reference frequency

•f

= 25 MHz (V

XIN

■

20 to 262140 reference frequency divider ratio

range (with 1/4 prescaler built-in)

■

1056 to 131071 FIN input frequency divider ratio

range

■

10 to 60 ° C operating temperature range

■

16-pin VSOP

= 0.95 V)

DD1

(Top view)

XIN

XOUT

VDD2

DB

DO

VSS

FIN

VDD1

1

8

16

5170

AV

9

ORDERING INFORMATION

De vice Pack ag e

SM5170AV 16-pin VSOP

TEST

NC

OPR

LE

DATA

CLK

LD

NC

NIPPON PRECISION CIRCUITS—1

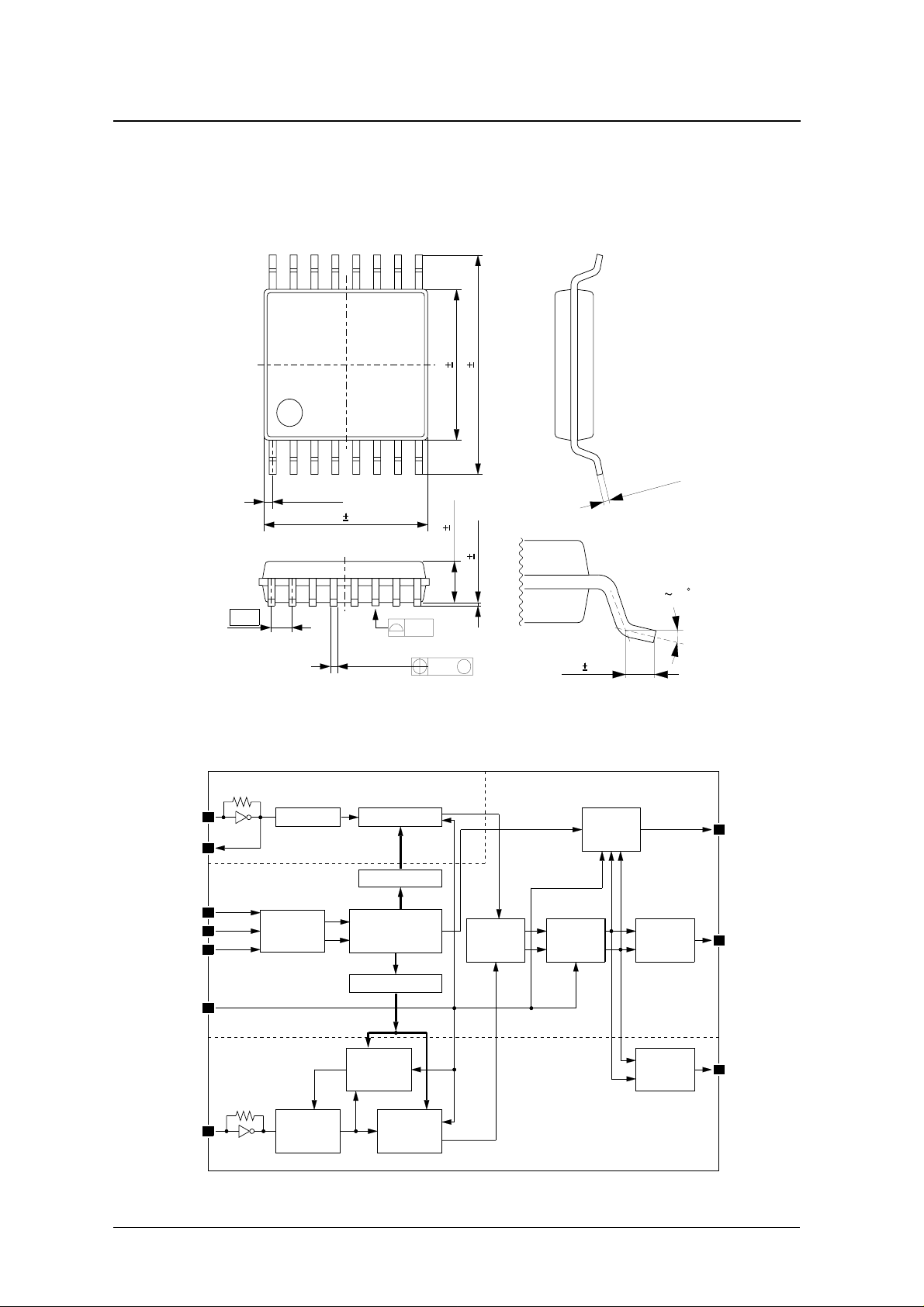

PACKAGE DIMENSIONS

Unit: mm

16-pin VSOP

SM5170AV

4.4 0.2

6.4 0.2

0.65

BLOCK DIAGRAM

VDD1 AREA(1V)

XIN

XOUT

VDD2 AREA(3V)

CLK

DATA

LE

0.275typ

5.1 0.2

0.10

+ 0.10

0.22

− 0.05

1/4 Prescaler

Latch Selector 22Bit Shift Register

16Bit R−Counter

16Bit R−Latch

0.12

1.15 0.1

0.10 0.05

M

Level

Shifter

0.5 0.2

Boost Signal

Generator

Phase

Detector

0.15

+ 0.10

- 0.05

010

Charge

Pump

DB

DO

OPR

FIN

VDD1 AREA(1V)

Dual Modulus

Prescaler

17Bit N−Latch

5Bit Swallow

Counter

12Bit Main

Counter

Lock

Detector

NIPPON PRECISION CIRCUITS—2

LD

−

−

−

−

−

°

−

°

SM5170AV

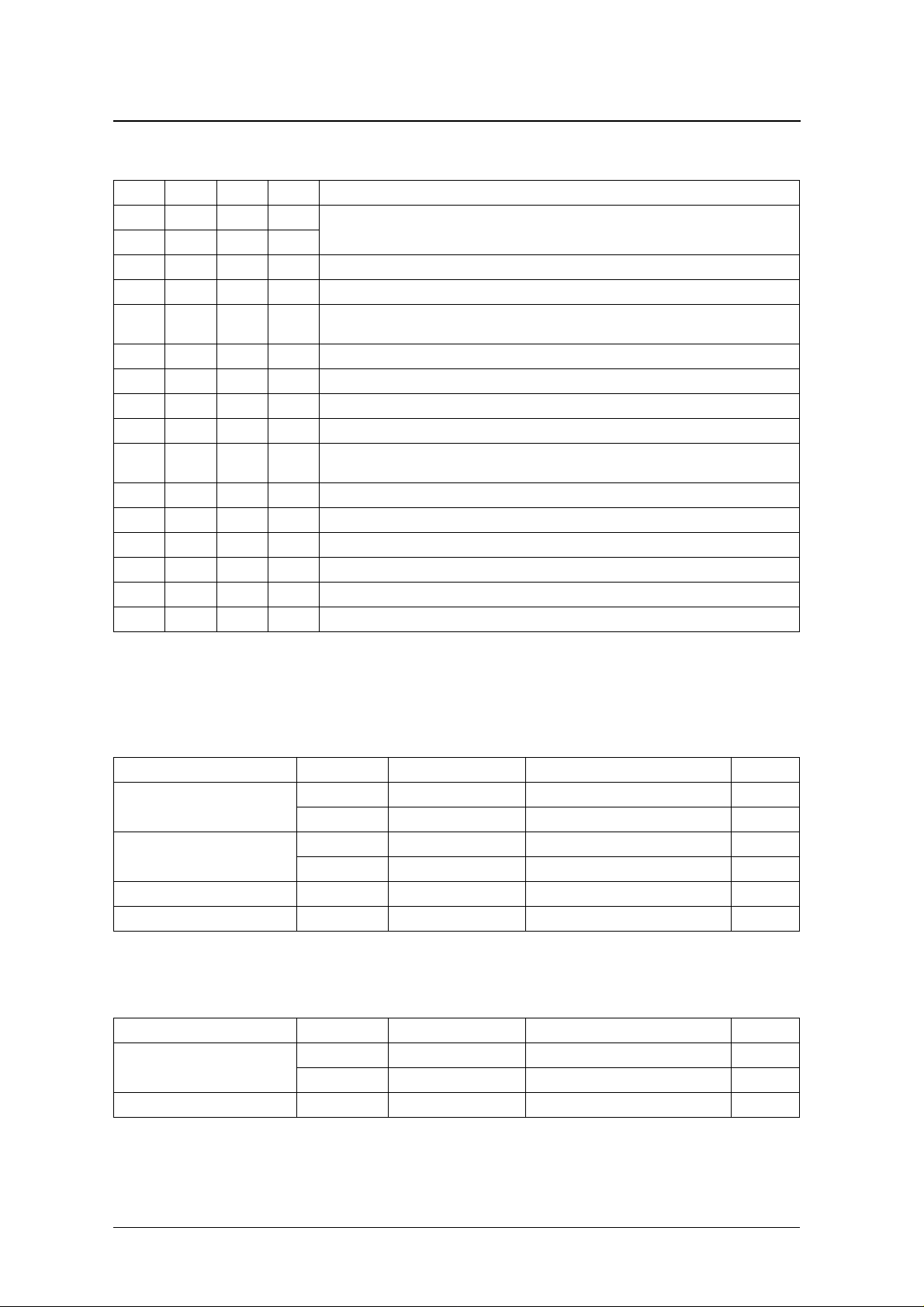

PIN DESCRIPTION

Number Name I/O Supply Description

1 XIN I 1 V

2 XOUT O 1 V

3 VDD2 – 3 V Phase comparator, charge pump and booster signal 3 V supply

4 D B O 3 V Booster signal output for faster locking

5DOO3 V

6 VS S – – Ground pin

7 FI N I 1 V FIN input frequency divider input pin. Feedback resistor built-in for AC-coupled inputs.

8 VDD1 – 1 V Reference frequency and FIN input frequency prescaler and counter 1 V supply

9 N C – – No connection

10 LD O 1 V

11 CLK I 3 V Control data clock input pin

12 D ATA I 3 V Control data input pin

13 LE I 3 V Control data latch enable signal input pin

14 OPR I 3 V Power-save control pin. Start when HIGH, standby mode when LOW .

15 N C – – No connection

16 TEST I 1 V Test pin. Pull-down resistor built-in. Le av e open or connect to ground for normal operation.

Reference frequency divider cr ystal oscillator connection pins. Alternatively, an external clock input can

be connected to XIN. The clock is output on XOUT. Feedback resistor built-in for AC-coupled inputs.

Phase comparator output pin. Built-in charge pump and tristate output means that this output can be

connected to a low-pass filter. The output polarity is preset for connection to a passive filter.

Unlock signal output pin. (Unlocked when LOW). The function of LD can be turned OFF using the LD

input control bit (LD should be tied LOW when not used).

SPECIFICATIONS

Absolute Maximum Ratings

V

= 0 V

SS

Parameter Symbol Condition Rating Unit

V

Supply voltage

Input voltage range

Storage temperature range T

Po w er dissipation P

V

V

V

DD1

DD2

IN1

IN2

stg

D

Recommended Operating Conditions

V

= 0 V

SS

Parameter Symbol Condition Rating Unit

V

Supply voltage

Operating temperature range T

V

DD1

DD2

opr

VDD1

VDD2

FIN, XIN, TEST V

OPR, CLK, DATA, LE V

VDD1 0.95 to 1.2 V

VDD2 2.0 to 3.3 V

0.3 to 2.0 V

0.3 to 4.6 V

SS

SS

0.3 to V

0.3 to V

+ 0.3 V

DD1

+ 0.3 V

DD2

40 to 125

150 m W

10 to 60

C

C

NIPPON PRECISION CIRCUITS—3

Loading...

Loading...