NOVATEK NT6868A, NT6868AH Datasheet

Features

NT6868A

Keyboard Controller

n Built-in 6502 8-bit CPU

n 2 MHz CPU operation frequency

n 4K bytes of ROM

n 128 bytes of SRAM

n One 8-bit programmable base timer with

1 - 256 µsec interval

n 29 programmable bi-directional I/O pins

n 3 LED direct sink pins with internal serial resistors

General Description

NT6868A is a single chip micro-controller for keyboard

applications. It incorporates a 6502 8-bit CPU core, 4K

bytes of ROM, and 128 bytes of RAM used as working

RAM and stack area. It also includes 29 programmable

bi-directional I/O pins and one 8-bit pre-loadable base

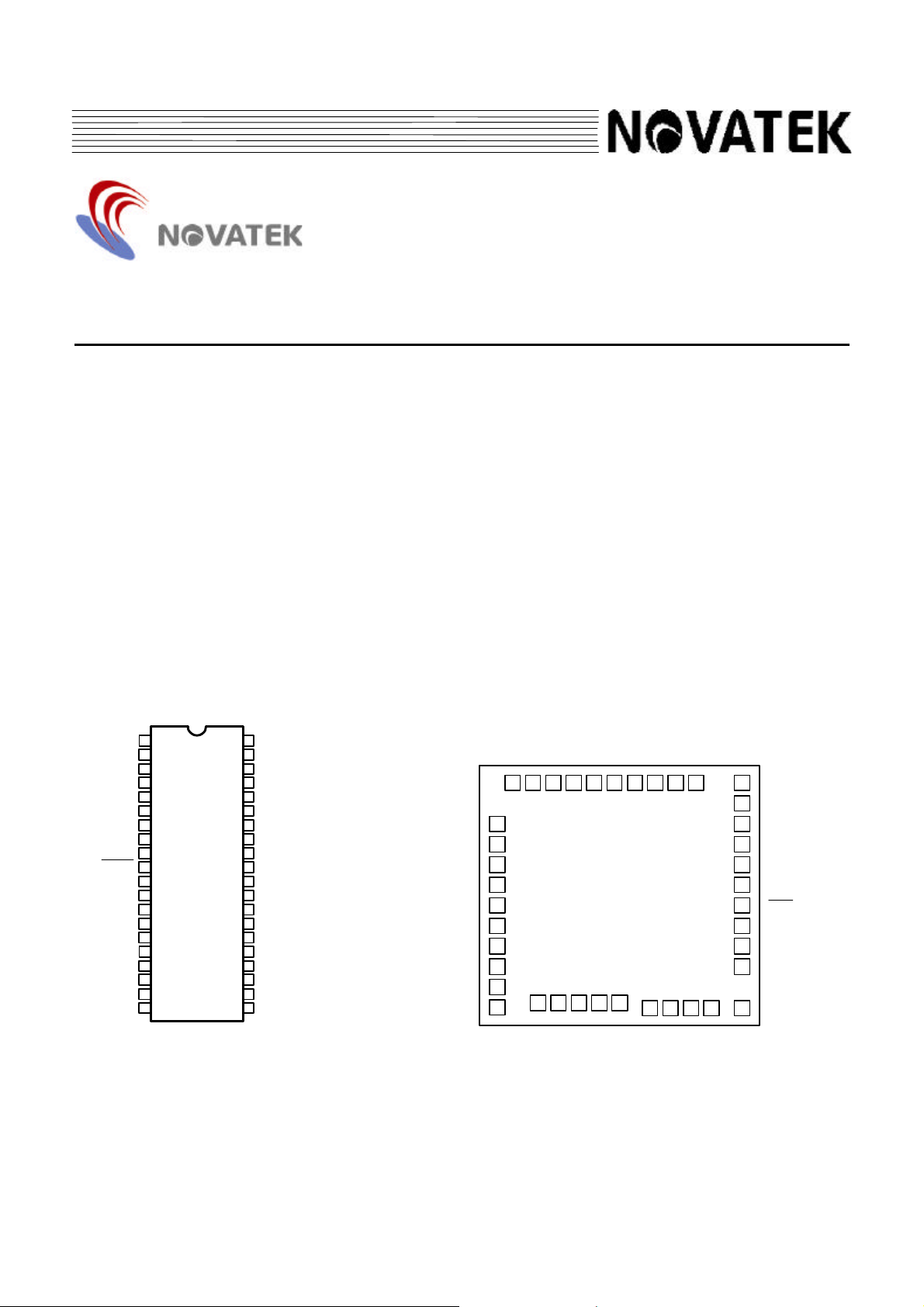

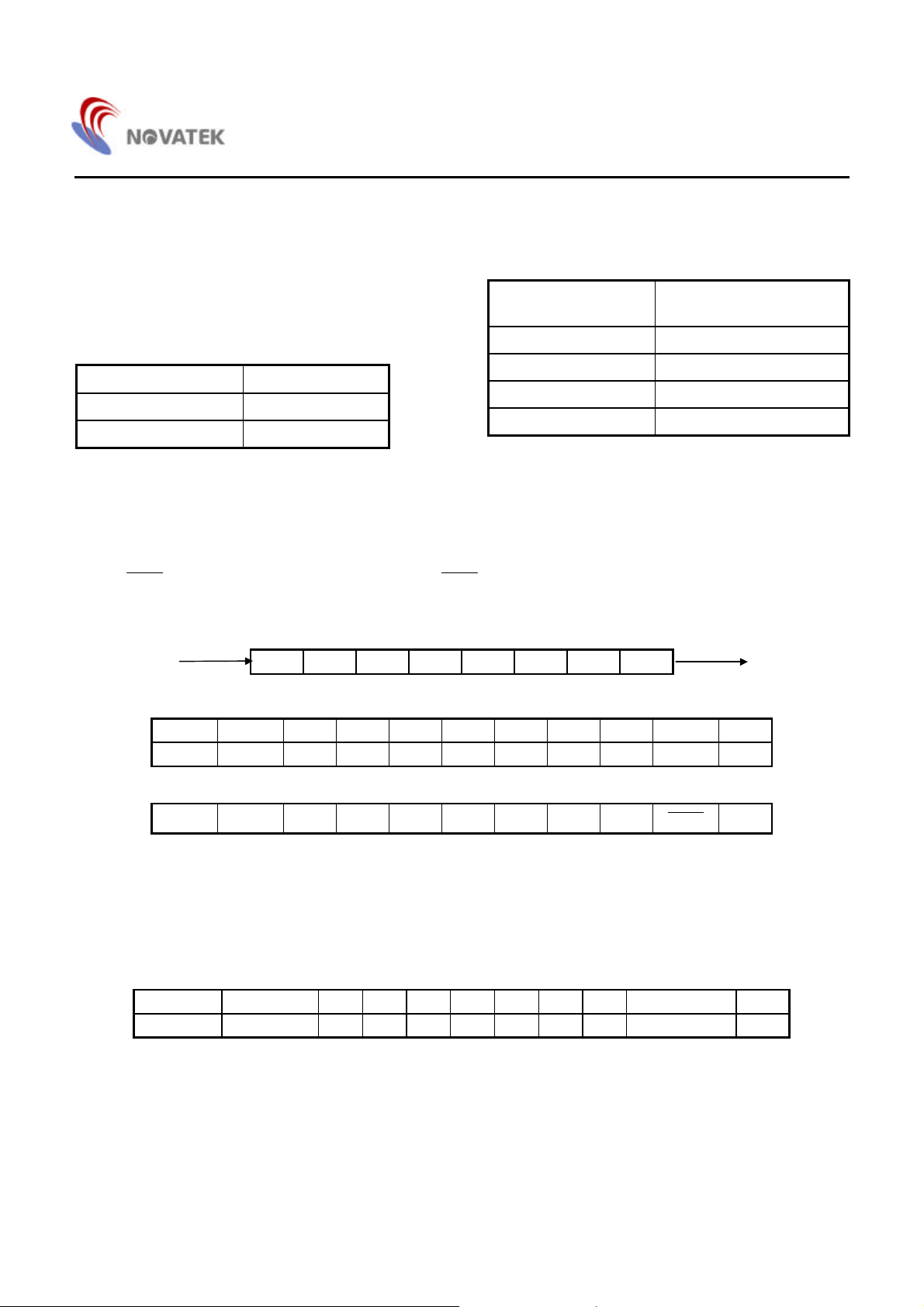

Pin Configuration

GND

NC

DATA

CLK

P30

P31

P32

P33

P34

RESET

P00

P01

P02

P03

P05

P06

P07

P10

P11

1

2

3

4

5

6

7

8

NT6868A

9

10

11

12

13

14

15

16 25

17

18

19

20

OSCI

40

39

R/OSCO

VDD

38

LED2

37

LED1

36

LED0

35

34

P27

P26

33

P25

32

31

P24

30

P23

29

P22

28

P21

27

P20

P17P04

26

P16

24

P15

23

P14

22

P13

P12

21

n Mask optional for built-in RC oscillator with an

external resistor or external ceramic resonator applied

n Watch-dog timer

n Built-in power-on reset

n Built-in low voltage reset

n CMOS technology for low power consumption

n Available in 40 pin DIP package and 40 pad CHIP

FORM

timer. Additionally, it includes a built-in low voltage

reset, a 4MHz RC oscillator that requires only a resistor

externally applied or a 4MHz ceramic resonator, and a

watch-dog timer that prevents system standstill.

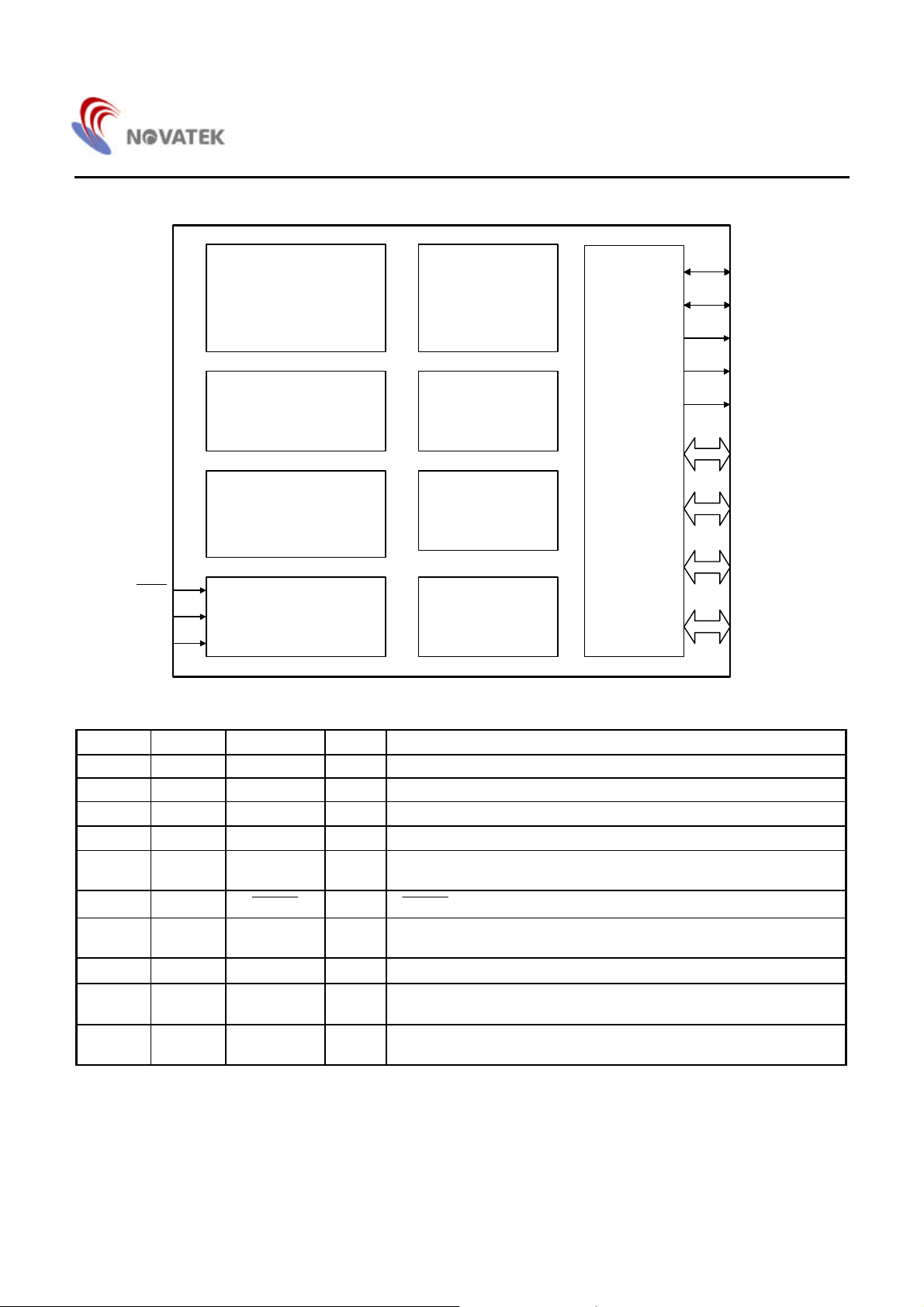

Pad Configuration

P

P

P

P

P

P

P

P

P

P

1

0

0

0

7

6

16

15

14

13

12

11

10

9

8

7

6 5 4 3 2

LED0

LED1

1

1

1

1

1

1

7

6

5

4

26 25 24 23 22 21 20 19 18 17

27

P20

28

P21

29

P22

30

P23

31

P24

32

P25

33

P26

34

P27

35

36

1

3

2

1

NT6868AH

40393837

1

P05

P04

P03

P02

P01

P00

RESET

P34

P33

P32

P31

G

O

R

V

L

D

S

/

E

D

C

O

D

2

I

S

C

O

NCD

C

N

D

P

A

L

3

T

K

0

A

1 V2.1

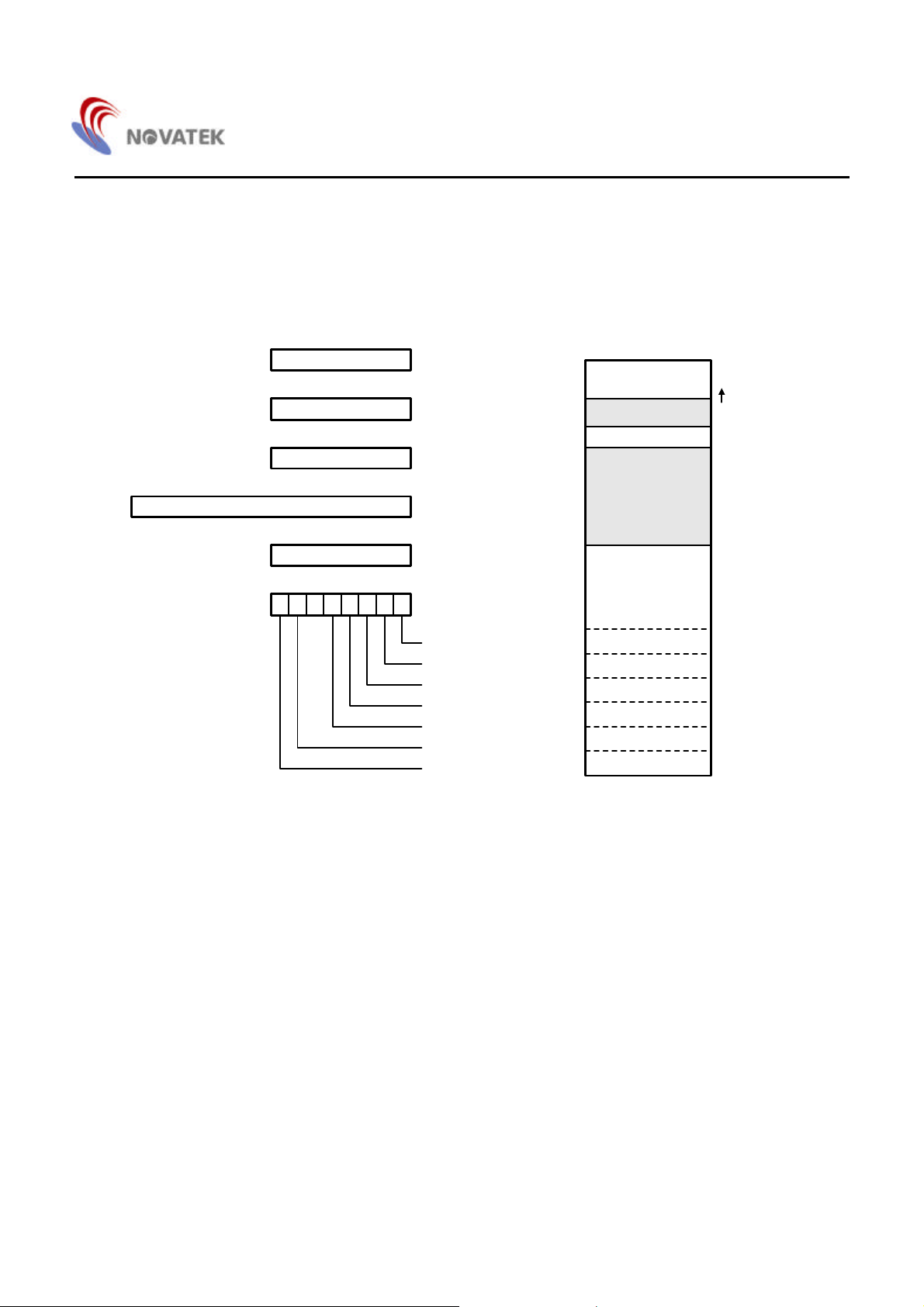

Block Diagram

TIMING GENERATOR

(RC OSC/CERAMIC RESONATOR:

4MHz)

4K BYTES

ROM

NT6868A

CLK

DATA

LED0

LED1

128 BYTES

SRAM + STACK

WATCH DOG

TIMER

BASE TIMER

I/O PORTS

RESET

V

GND

6502

CPU

INT. CONTROLLER

DD

POWER-ON RESET/

LOW VOLTAGE RESET

Pin and Pad Descriptions

Pin No. Pad No. Designation I/O Description

1 1 GND P Ground pin

2 2 NC - No connection, recommended to connect VDD or floating

3 3 DATA I/O

4 4 CLK I/O

5 - 9,

11 - 34

10 10

35 - 37 35 - 37 LED0 -

5 - 9,

11 - 34

P30 - P34,

P00 - P27

RESET

I/O Bi-directional I/O pins

O LED direct sink pins

LED2

38 38

VDD

P Power supply

39 39 R/OSCO I

40 40 OSCI - No connection for RC OSC, connected for 4MHz ceramic

I/O, 10KΩ pull-up resistor for communication

I/O, 10KΩ pull-up resistor for communication

I

RESET signal input pin with internal pull up resistor; Active low

47KΩ resistor connected for RC OSC or 4MHz ceramic resonator

connected

resonator

LED2

P00 - P07

P10 - P17

P20 - P27

P30 - P34

* Under the constraint of the maximum frequency variation, (∆F/F)max, ≤ ±1%, code 3 (ceramic resonator option) must be

selected and pin 39 and pin 40 are connected to a ceramic resonator. If (∆F/F)max, ≤ ±10%, code 1 (RC OSC option) is

recommended to be selected and pin39 connects a 47KΩ resistor with, ≤ ±1% accuracy to VDD and pin 40 is floating.

2

Functional Description

6502 CPU

6502 is an 8-bit CPU. Refer to 6502 data sheet for details.

7 0

ACCUMULATOR A

7 0

INDEX REGISTER X

7 0

INDEX REGISTER Y

0000

007F

00C0

00CF

SRAM

UNUSED

SYSTEM REGISTERS

NT6868A

STACK PTR

15 0

PROGRAM COUNTER PC

7 0

S

7 0

S V B D I Z C

STACK POINTER SP

STATUS REGISTER P

CARRY

ZERO

INTERRUPT MASK

DECIMAL MODE

BREAK

OVERFOLW

SIGN

F000

FFFA

FFFB

FFFC

FFFD

FFFE

FFFF

UNUSED

USER ROM

NMI-L

NMI-H

RST-L

RST-H

IRQ-L

IRQ-H

Figure 1. 6502 CPU Registers and Status Flags Figure 2. NT6868A Memory Map

NMI VECTOR

IRQ VECTOR

3

NT6868A

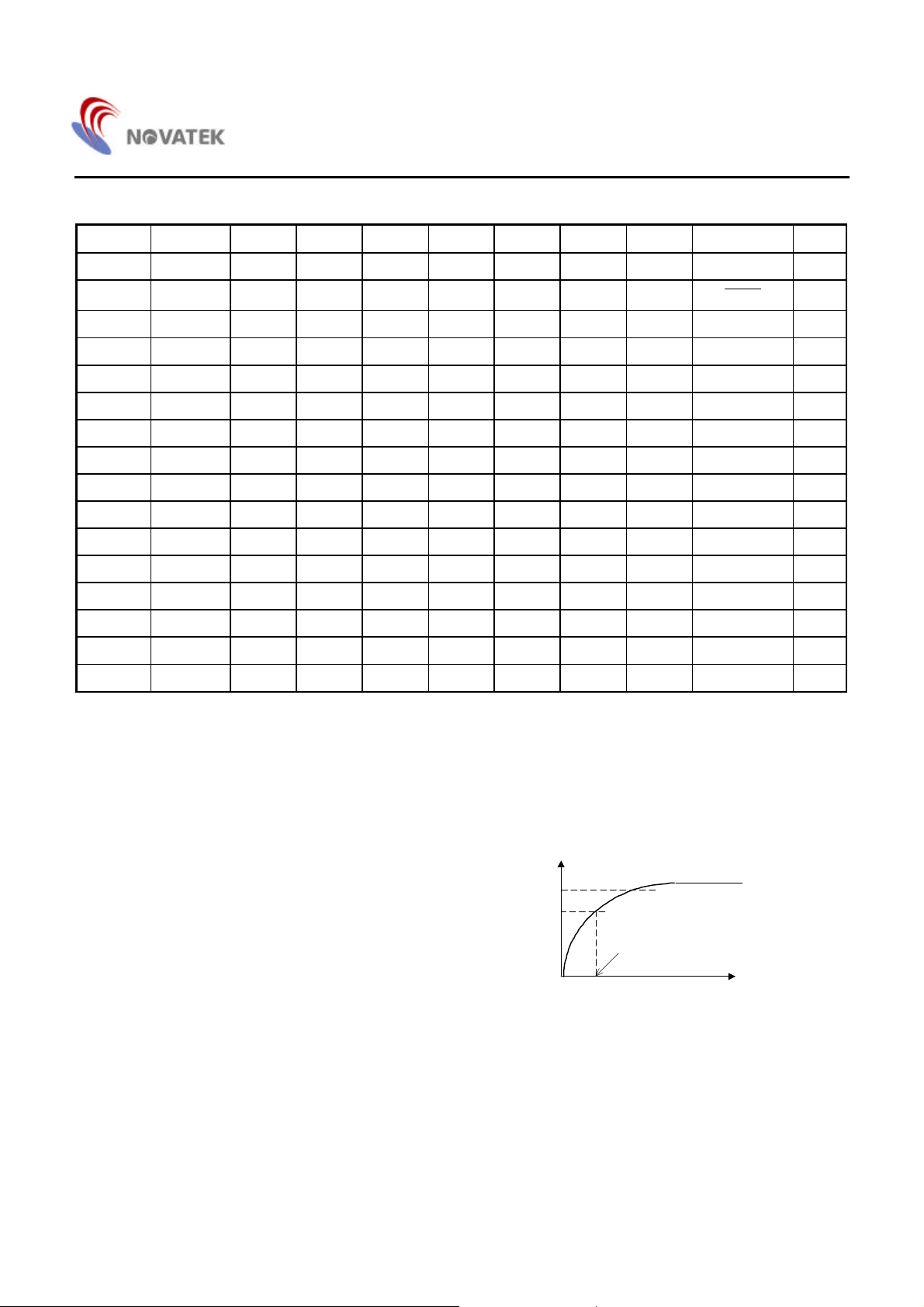

System Reserved Registers

Address Register Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

$00C0 BT BT7 BT6 BT5 BT4 BT3 BT2 BT1 BT0 W

$00C1 TCON - - - - - - -

$00C2 CLRIRQX - - - - - - - CLRIRQTMR W

$00C3 PORT0 PD07 PD06 PD05 PD04 PD03 PD02 PD01 PD00 RW

$00C4 PORT1 PD17 PD16 PD15 PD14 PD13 PD12 PD11 PD10 RW

$00C5 PORT2 PD27 PD26 PD25 PD24 PD23 PD22 PD21 PD20 RW

$00C6 PORT3 - - - PD34 PD33 PD32 PD31 PD30 RW

$00C7 CLK - - - - - - - CLK RW

$00C8 DATA - - - - - - - DATA RW

$00C9 LED - - - - - LED2 LED1 LED0 W

$00CA CLRWDT 0 1 0 1 0 1 0 1 W

$00CB X X X X X X X X X X

$00CC X X X X X X X X X X

$00CD X X X X X X X X X X

$00CE X X X X X X X X X X

$00CF X X X X X X X X X X

- : no effect X : access not allowed

4K X 8 ROM

The built-in ROM program code, executed by the 6502

CPU, has a capacity of 4K X 8 bits and is addressed

from F000H to FFFFH.

Power-On Reset

Built-in power-on reset circuit can generate a 150ms

pulse to reset the entire chip. The beginning of the

150ms pulse occurs at 60% of VDD when powered on.

ENBT

128 X 8 SRAM

The built-in SRAM is used for general purpose data

memory and for the stack area. SRAM is addressed from

0000H to 007FH. User can allocate stack area in the

SRAM by setting stack pointer register (S). Because the

6502C default stack pointer is 01FFH, it must be

mapped to 007FH. Mapping from 01XX to 00XX is done

internally by setting the S register to 7FH via software

programming.

For example :

LDX #$7F

TXS

V

60%

power

DD

The start of 150ms pulse

t

W

4

NT6868A

Timing Generation

This block generates the system timing and control

signal supplied to CPU and on-chip peripherals. There

are two types of system clock sources: built-in RC

oscillator or external ceramic resonator. Both of them are

mask optional and generate a 4MHz system clock. They

also generates 2MHz for CPU, and 1MHz for base timer.

The following shows the relationship of code type

number and oscillation type.

Oscillator Type Code Number

RC OSC 1

Ceramic Resonator 3

Base Timer

The base timer is an 8-bit counter with a 1MHz clock source. The base timer can be enabled/disabled by CPU. After reset,

the base timer is disabled and cleared. The base timer can be preset by writing BT7 - BT0 to the BT register at any time.

When enabled, the base timer starts counting from the preset value. When the value reaches FFH, it generates a timer

interrupt if the timer interrupt is enabled. When it reaches the maximum value of FFH, the base timer will wrap around and

begin counting at 00H. The timer interval can be programmed from 1 - 256 µsec. The base timer can be enabled by writing

a '0' to 'ENBT' in the TCON (Timer Control) register. The ENBT is a level trigger.

The following table provides the relationship between

external resistor and RC OSC frequency. (for reference

only)

External Resistor

(KΩ)

39 4.7

43 4.44

47 4

56 3.68

RC OSC Frequency (MHz)

Base timer structure:

8-Bit timer

1µs

BT pre-load data:

Addr. Bit 7 6 5 4 3 2 1 0

$00C0 BT BT7 BT6 BT5 BT4 BT3 BT2 BT1 BT0 (W)

Timer Control Regisrer:

$00C1 TCON - - - - - - -

BT7 BT6 BT5 BT4 BT2 BT2 BT1 BT0

ENBT

TMRINT

(W)

INT. Controller

When BASE TIMER overflow occurs, it will set the IRQTMR flag. The IRQTMR flag cannot be directly accessed by

software. Once set by an interrupt source, it remains High unless cleared by writing '1' to the corresponding bit in

CLRIRQX ($00C2H). This register is cleared to '0' on initialization by system reset.

When an interrupt occurs, CPU jumps to $FFFEH & $FFFFH to execute the interrupt service routine. When BASE TIMER

interrupt occurs and enters the interrupt service routine, the IRQTMR flag must be cleared by software.

Interrupt Control Register:

Addr. Bit 7 6 5 4 3 2 1 0

$00C2 CLRIRQX - - - - - - - CLRIRQTMR (W)

5

Loading...

Loading...