NOVATEK NT68275 Datasheet

NT68275

IIC Bus Controlled On-Screen Display

Features

n IIC Bus Interface with Slave Address $7A (Transmitter)

& $7B (Receiver)

n Horizontal Frequency Range: 30KHz ~ 150KHz*

n Flexible Display Resolution Up to 1524 Dots/Row

n Internal PLL Generates a Stable and Wide-Ranged

System Clock (120 MHz)*

n OSD Screen Consist Character Array of 15 Rows by

30 Columns

n Programmable Vertical and Horizontal Position for

OSD Displaying Center

n Total of 528* ROM Fonts including 512* Standard &

16 Multi-color ROM Fonts.

n 12 X 18 Dot Matrix Per Character

n 8-Color Selection for Each Character

General Description

NT68275 is designed for displaying symbols and

characters onto a CRT monitor. Its operation is controlled

by a microcontroller with an IIC bus interface. By sending

proper data and commands to NT68275, it can carry out

the full screen display automatically with the time base

generated by an on-chip PLL circuit. There are many

functions provided by this chip to fully support user

applications, such as: adjustment of the position of OSD

The “ * “ sign denotes that feature different from NT6827.

n 7-Color Selection for Each Character Background

n Character/Symbol Blinking, Shadowing & Bordering

Display Effect

n Double Character Height and Width for Each Row

n Programmable Height of Character/Symbol Display

n Row To Row Spacing Control to Avoid Expansion

Distortion

n Four Programmable Windows with Overlapping

Capability and Shadowing Effect

n Color Setting for Windows’ Background and Character

Shadowing & Bordering

n Fade-In/Out Effect of OSD Screen Display

n Hsync & Vsync Input Polarity Selectable

windows, built-in 512* ROM & 16 multi-color fonts,

variable character height with row-to-row spacing

adjustment, 8 color selections & 7 background color

controls for each character, double height/width controls

for each row, 4 overlapping window available with color &

size controls, size controls for each window shadowing,

color selection for windows’ shadowing & character

shadowing/ bordering, fade-in/out display effect, etc.

1 V1.0

NT68275

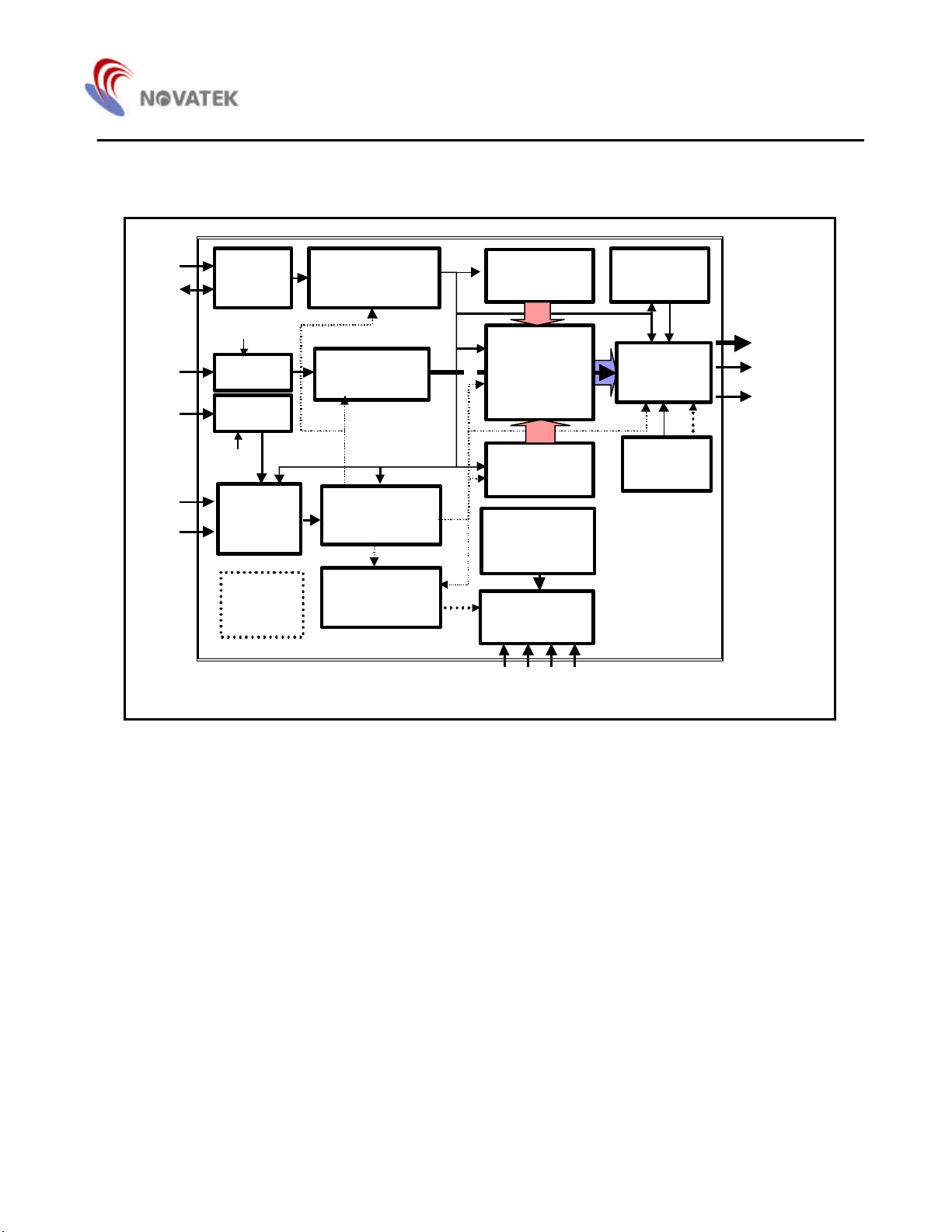

Block Diagram

SCL

SDA

VFLB

RP

VCO

I2C

BUS

RECEIVER

VPOL

VSYNC

HSYNCHFLB

HPOL

PLL

CIRCUIT

TEST

CIRCUIT

BUS CONTROL

BUFFER

VERTICAL

CONTROL

TIMING

GENERATOR

HORIZONTAL

CONTROL

ROM

FONT 12 * 18

DISPLAY

MEMORY

CONTOL

REG.

POWER ON

LOW VOLTAGE

RESET

POWER

SYSTEM

AVCC

DVCC

AGND

DGND

DISPLAY

EFFECT

OUTPUT

CONTROL

COLOR

CONTROL

R/G/B

FBKG

*PWM/INT

2

NT68275

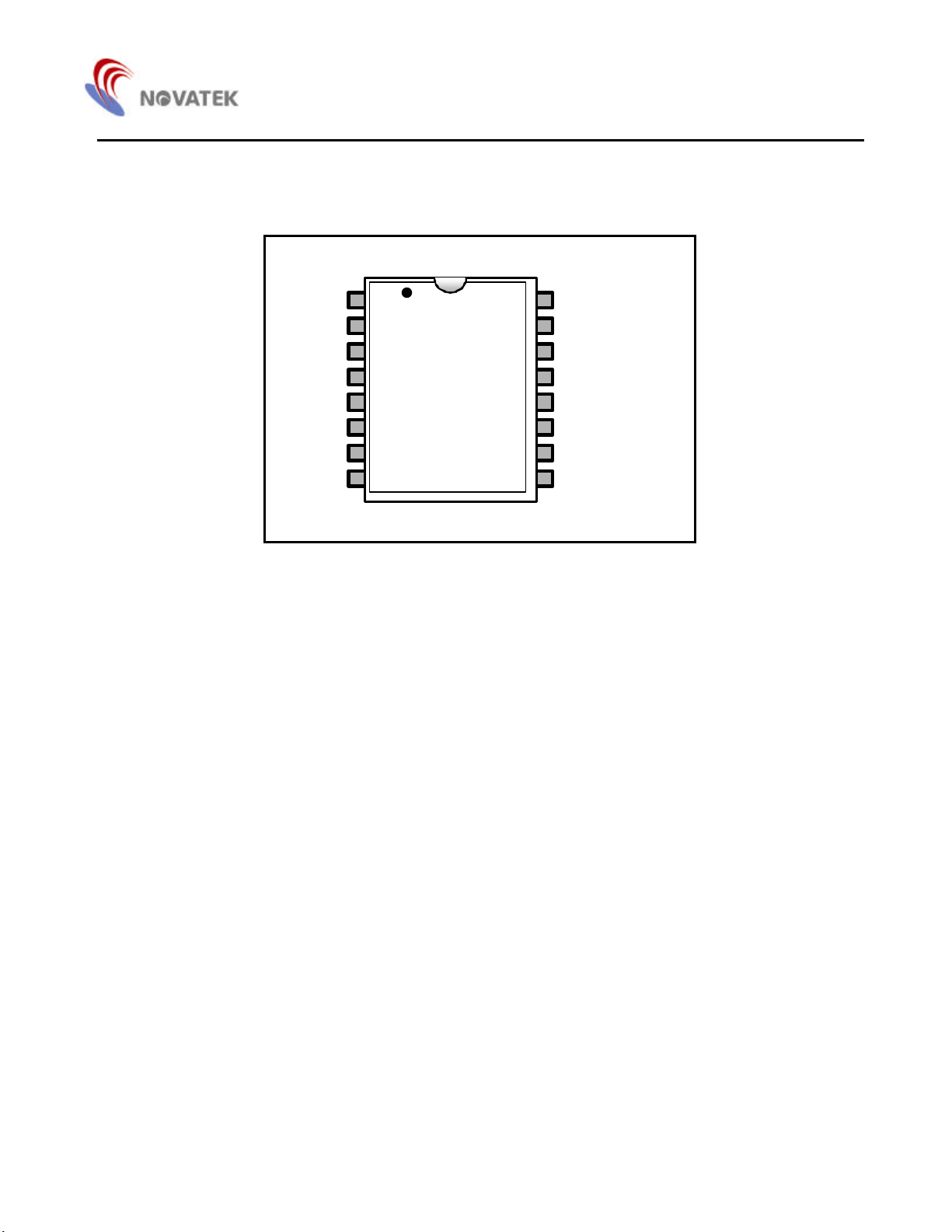

Pin Assignment

AGND

VCO

RP

AVCC

HFLB

N.C.

SDA

SCL

1

2

3

4

NT68275

5

6

7

8 9

16

15

14

13

12

11

10

DGND

R

G

B

FBKG

*PWMCK/INT

VFLB

DVCC

3

NT68275

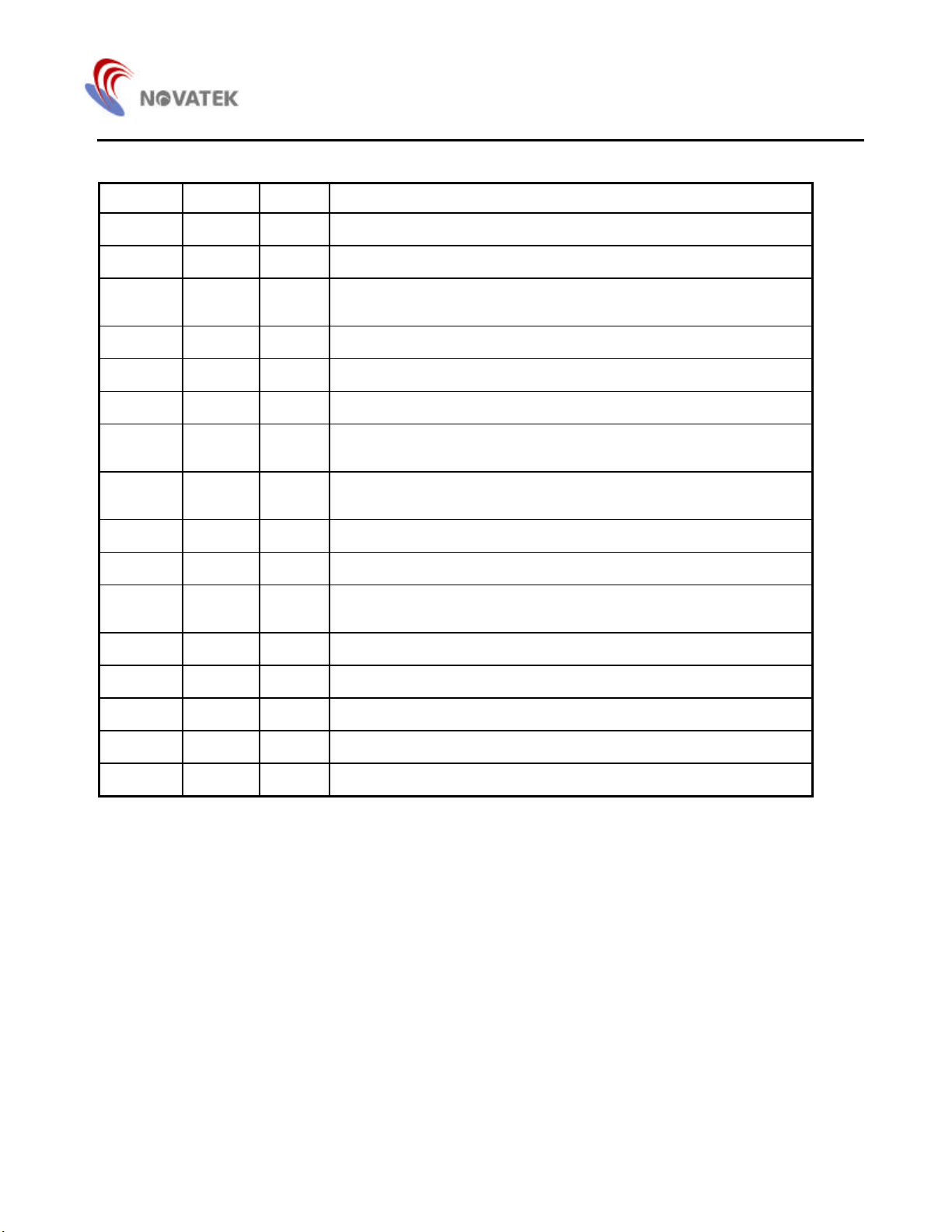

Pin Description

NT68275 NAME I/O/P/R Function

1 AGND P Analog Ground

2 VCO - Voltage I/P to Control Oscillator

3 RP -

Bias Resistor. Used to bias internal VCO to resonate at specific dot

frequency

4 AVCC P Analog Power Supply (5 V Typ.)

5 HFLB I Horizontal Fly-back Input (Schmitt Trigger Buffer)

6 N.C. - -

7 SDA I

8 SCL I

SDA Pin Of IIC Bus (Schmitt Trigger Buffer) with internal 100K ohm

pulled-high resistance

SCL Pin Of IIC Bus (Schmitt Trigger Buffer) with internal 100K ohm

pulled-high resistance

9 DVCC P Digital Power Supply (5 V Typ.)

10 VFLB I Vertical Fly-back Input (Schmitt Trigger Buffer)

11

*PWMC

K/INT

O PWM output or Intensity output

12 FBKG O Fast Blanking Output. Used to cut off external R, G, B signals.

13 B O Blue Color Output with Push-Pull Output Structure

14 G O Green Color Output with Push-Pull Output Structure

15 R O Red Color Output with Push-Pull Output Structure

16 DGND P Digital Ground

4

NT68275

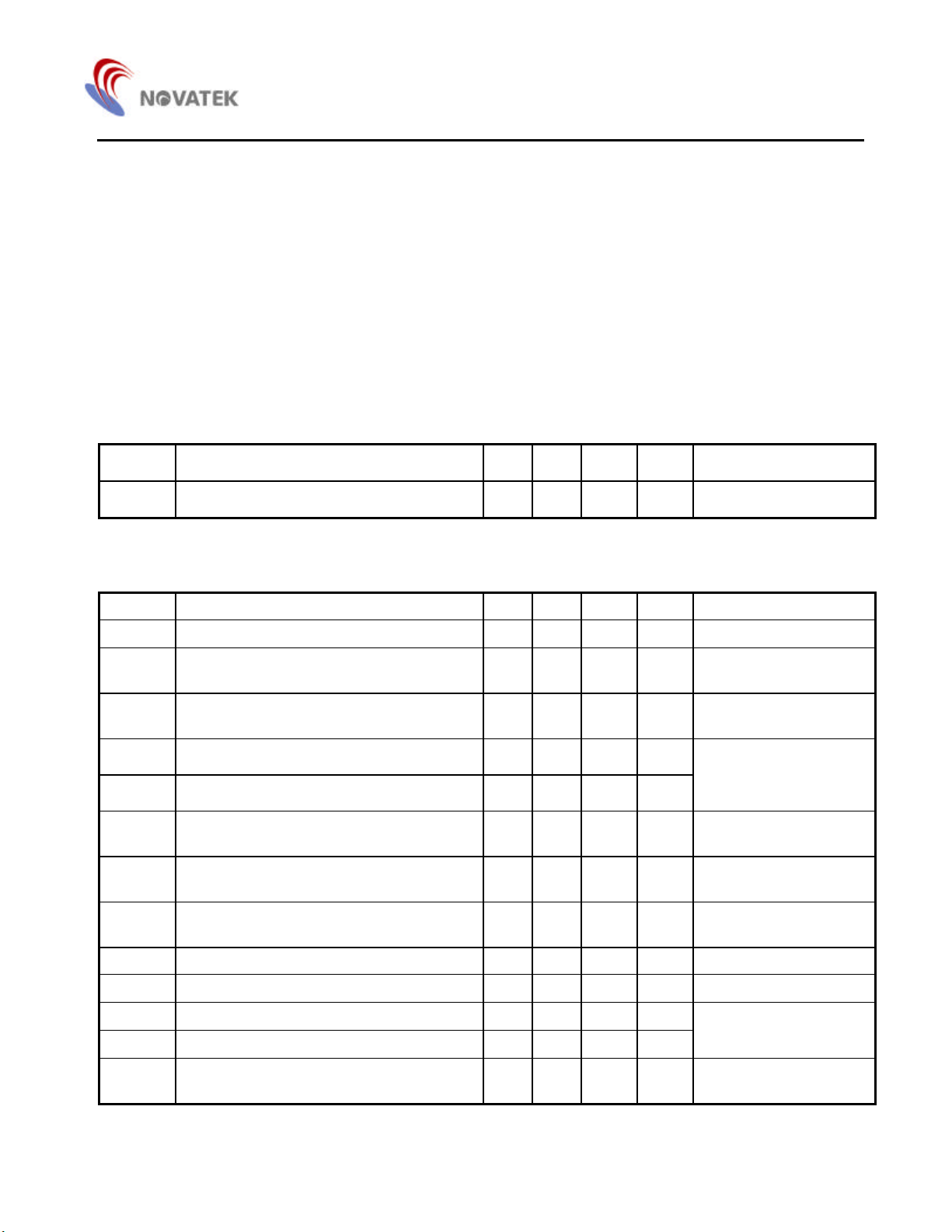

DC/AC Absolute Maximum Ratings*

Recommended Operating Conditions

VCC (measured to GND) . . . . . . . . . .. . 4.75V to 5.25V

Operating Temperature . . . . . . . . . . . . . 0 to +70 0C

*Comments

Stresses above those listed under "Absolute

Maximum Ratings" may cause permanent damage to

this device. These are stress ratings only. Functional

operation of this device at these or any other

conditions above those indicated in the operational

sections of this specification is not implied or

intended. Exposed to the absolute maximum rating

conditions for extended periods may affect device

reliability.

Electrical Characteristics (VDD = 5V, Tamb = 25°C)

Symbol Parameter Min. Typ. Max. Unit Notes

VCC Supply Voltage 4.75 5 5.25 V

DC Characteristic

Symbol Parameter Min. Typ. Max. Unit Notes

IDD

VIH1 Input High Voltage 2 V

VIL1 Input Low Voltage 0.8 V

Operating Current 22 25 mA No loading

VFLB, HFLB with

Schmitt Trigger Buffer

VFLB, HFLB Schmitt

Trigger Buffer

VIH2 IIC Bus Input High Voltage 3 V

SCL, SDA

VIL2 IIC Bus Input Low Voltage 1.5 V

Idrive1

Isink1

Ileak

Driving current of R, G, B, FBKG, HFTON

output pins at 2.4V output voltage

Sinking current of R, G, B, FBKG, HFTON

output pins at 0.4V output voltage

Leakage current of R, G, B, FBKG pins at

Hi-Z state

80 mA

20 mA

10 uA Measured at 2.5V state

Iiicl IIC Bus Output Sink Current 5 mA Viicoutl = 0.4V

Vth Input Threshold Voltage at HFLB & VFLB 1.8 2.0 2.2 V

VSTIH Schmitt Trigger Input High Voltage 1.7 2 V

VSTIL Schmitt Trigger Input Low Voltage 0.8 1.1 V

Iin

Input Current of Hsync, Vsync, SDA, SCL

pins

-10 +10 uA Schmitt Trigger Buffer

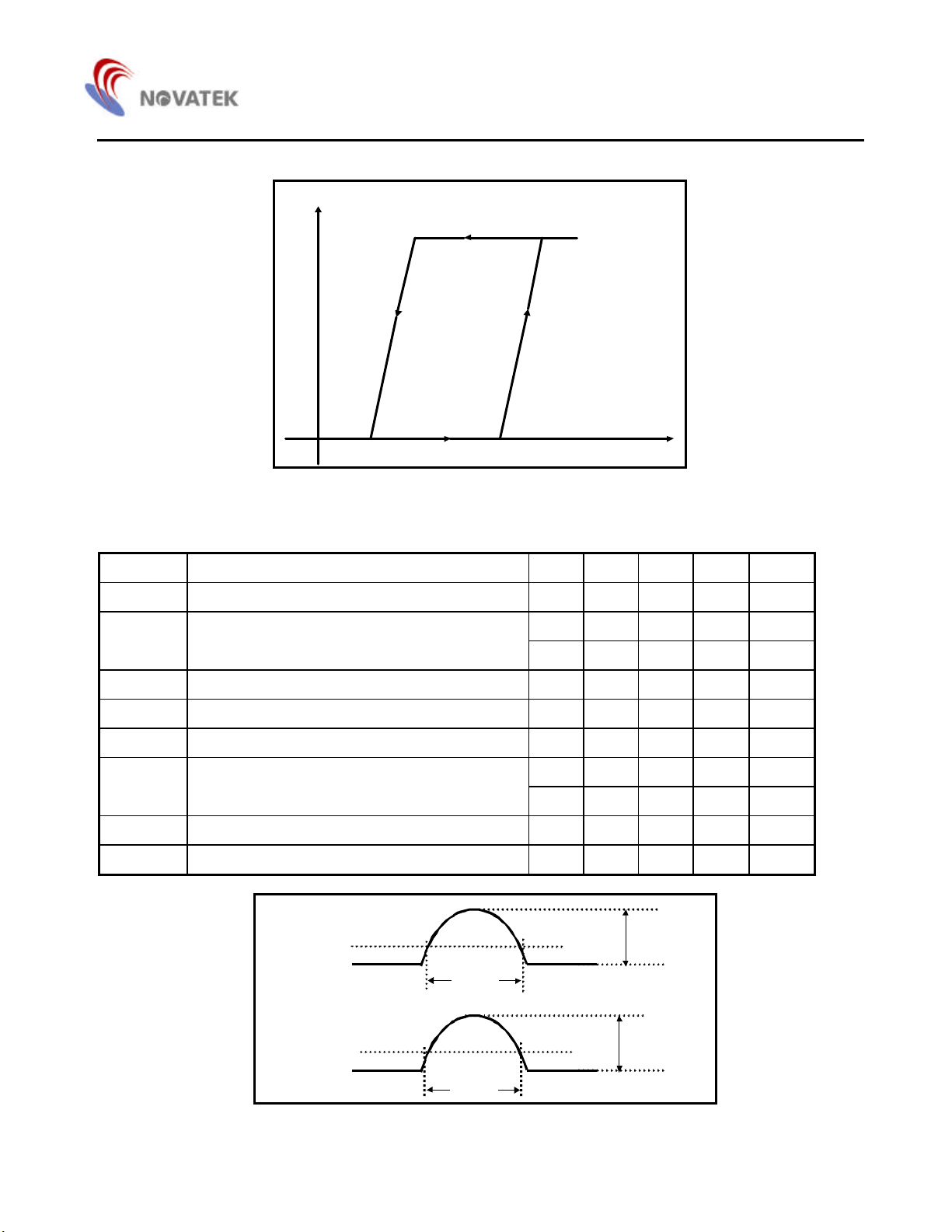

Refer Figure 1

5

NT68275

Output state

VH

VL

1.1V 1.7V

Figure 1. Schmitt Trigger Diagram

Input voltage

AC Characteristic

Symbol Parameter Min. Typ. Max. Unit Notes

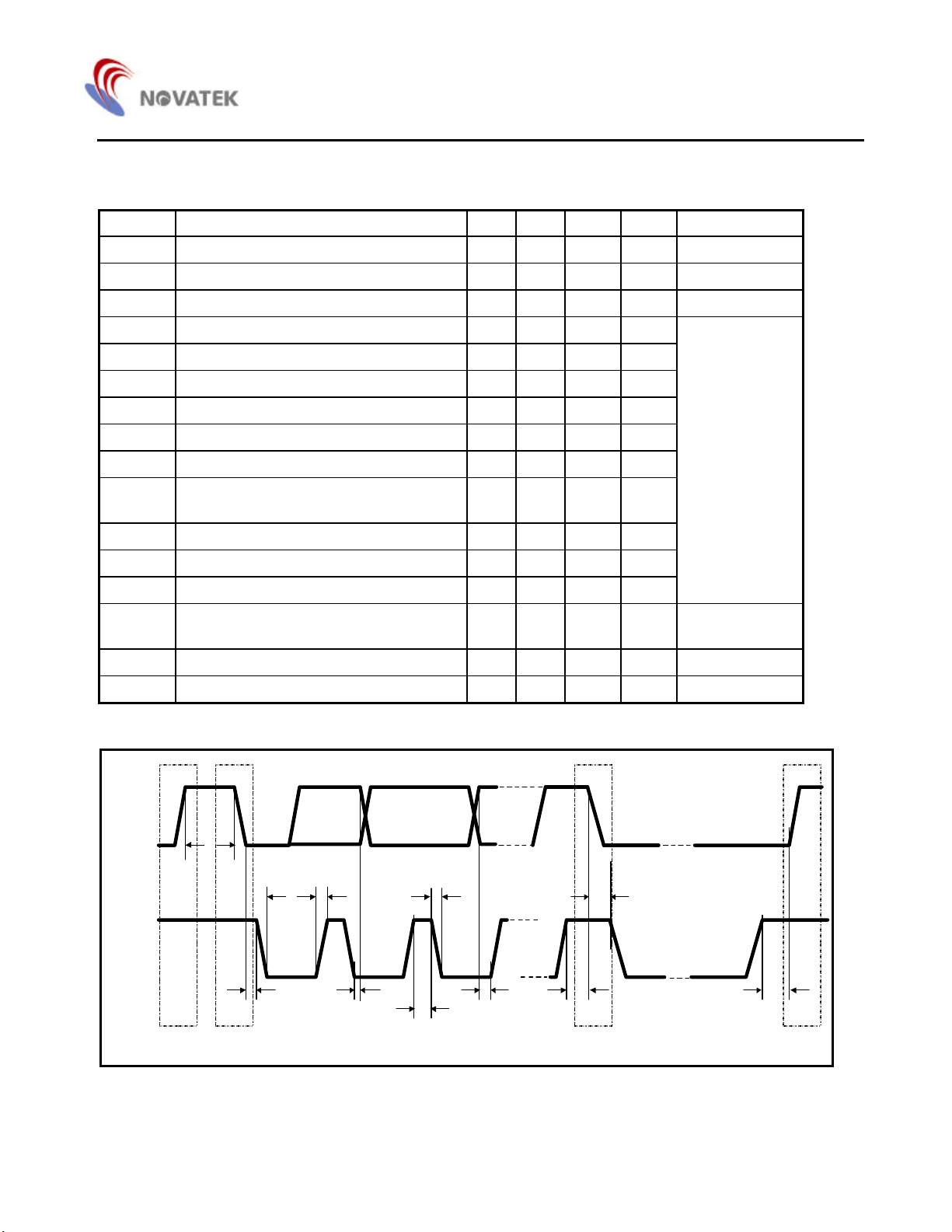

Fhfy Horizontal Fly-back Frequency 30 *150 KHz

5 V

Vhfly Horizontal Fly-back Input

0 V

Thflymin Minimum Pulse Width of Horizontal Fly-back 0.7 us

Thflymax Maximum Pulse Width of Horizontal Fly-back 5.5 us

Fvfy Vertical Fly-back Frequency 50 *200 Hz

5 V

Vvfly Vertical Fly-back Input

0 V

Tvflymin Minimum Pulse Width of Vertical Fly-back 20 us

Tvflymax Maximum Pulse Width of Vertical Fly-back 1 ms

5 V

HFLB

Thwidth

VFLB

Tvwidth

Figure 2. H/V Fly-Back Signal

2.0 V

0 V

5 V

2.0 V

0 V

6

NT68275

7

NT68275

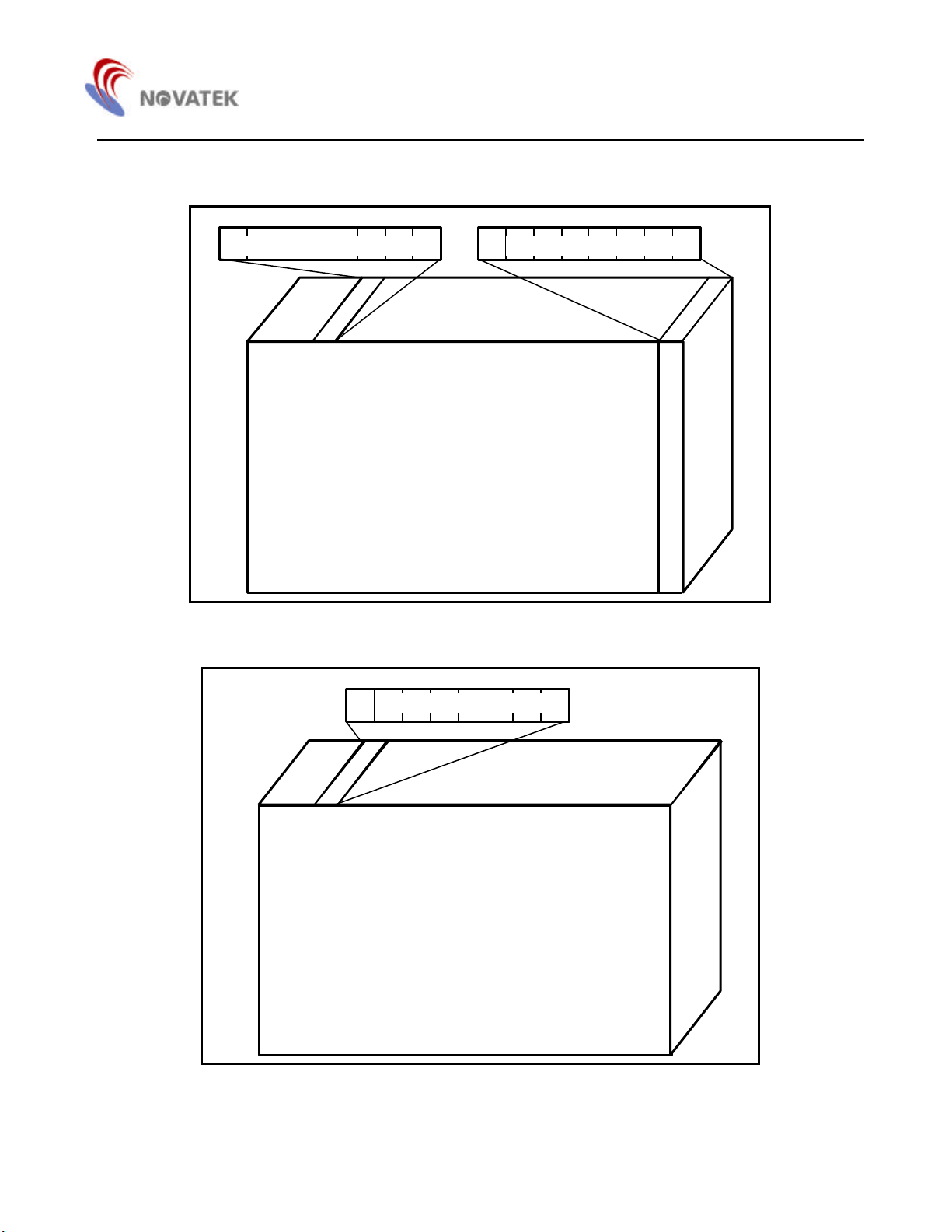

IIC Bus - Slave Transmitter & Receiver (Slave address: $7A & $7B)

Table 1. IIC Bus

Symbol Parameter Min. Typ. Max. Unit Notes

Fmaxcl Maximum SCL Clock Frequency 100 KHz

VIL Input Low Voltage -0.5 1.5 V

VIH Input High Voltage 3.0 5.5 V

Tlow Low Period of SCL Clock 4.7 us

Thigh High Period of SCL Clock 4.0 us

Tsudat Data Setup Time 250 ns

Thddat Data Hold Time 300 ns

Tiicr Rise Time of IIC Bus 1000 ns

Tiicf Fall Time of IIC Bus 300 ns

SCL, SDA

Tsusta

Setup Time for Repeated START

Condition

1.3 us

Thdsta Hold Time for START Condition 4.0 us

Tsusta Setup Time for START Condition 4.7 us

Tsusto Setup Time for STOP Condition 4.0 us

Tiicbuf

Time IIC bus must be free before next

new transmission can start

4.7 us

Iiicl IIC Bus Sink Current 4 5 mA Viicoutl = 0.4 V

Tfilter Input Filter Spike Suppression 100 ns SCL, SDA

See also IIC Table Control and IIC Sub Address Control

SDA Tiicbuf

Tiicr Tiicf

Tlow

Thdsta

SCL

Thdsta Tsudat

STOP START

Thddat

Thigh

Figure 3. IIC Bus Timing

8

Tsusta

START

Tsusto

STOP

NT68275

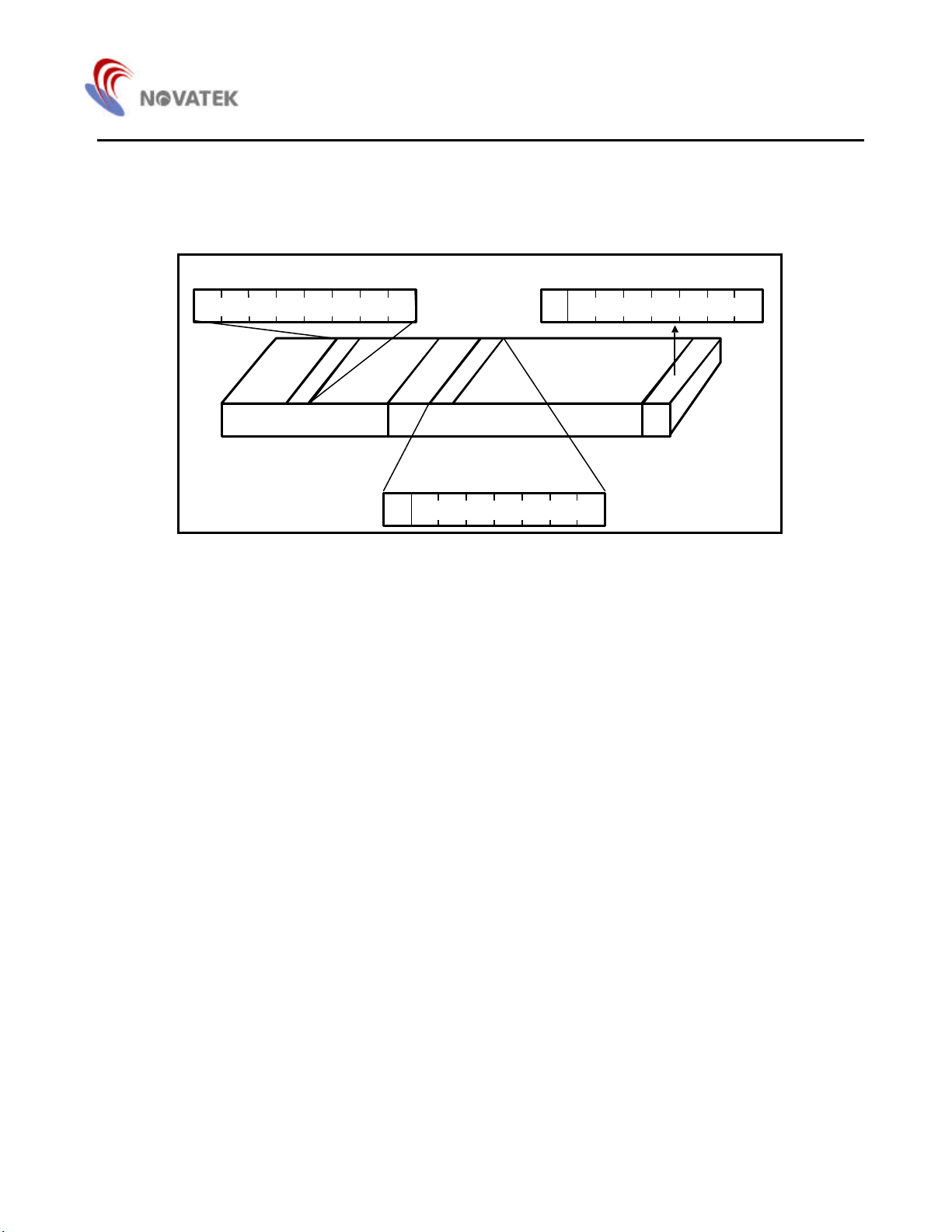

Memory Map

07 07

Fonts Address $00-$FF

0

00

ROW

14

Figure 4-1. Memory Map of Display Register (Row 0 – 14)

7

COLUMN

DISPLAY REGISTER

Character Attribute Register

Row Attribute Register

29

07

7

0

30

ROW ATTRIBUTE REGISTER

7

0

0

0 29

ROW

14

CHARACTER ATTRIBUTE REGISTER

COLUMN

Figure 4-2. Memory Map of Attribute Register (Row 0 – 14)

9

NT68275

Window 1-4 Control Register

ROW

15

WINDOW1 - WINDOW4 OSD SCREEN CONTROL

0

0

COLUMN

07

Reset Flag Control Register

7

11

12 22

OSD Screen Control Register

7

0

07

Figure 4-3. Memory Map of Control Register (Row 15)

07

23

10

NT68275

List of Control Registers:

(1) Display Register: Row 0 – 14 , Column 0 – 29

8 7 6 5 4 3 2 1 0

Row 0-14

Column 0-29

*Page MSB LSB

Font’s Address $00 - $1FF

Bit 8: * Page - This bit will address the page 1 ROM font area by bit 7-0 of this control register. Otherwise, it

will address page 0. This can be set by the bit5 column data at IIC bus transmission. Refer to

Figure 8-1 & 8-3 for ROM font area.

Bit 7-0: These eight bits will address one of the 256 characters/ symbols residing in the character ROM fonts.

Note that if user sets MCFONT bit (row 15, column 22) to ‘1’, the 0 ~ 256 will address standard ROM

fonts, and if cleared to ‘0’, the 0 ~ 239 will address standard ROM fonts & 240 ~ 255, multi-color ROM

fonts.

(2) Character Attribute Register: Row 0 – 14, Column 0 – 29

7 6 5 4 3 2 1 0

Row 0-14

Column 0-29

BKR BKG BKB BLINK R G B

Character Attribute Control

Bit 6-4: BKR/G/B -These three bits define the color attribute of the background for the corresponding

character/symbol. If all three bits are cleared, no background will be displayed. Refer to the

TAB 3 for the color selections.

Bit 3: BLINK - This bit enables the blinking effect of the corresponding character/symbol with this bit set to

‘1’. The blinking frequency is approximately 1Hz with a fifty-fifty duty cycle at 80Hz vertical sync

frequency.

Bit 2-0: R/G/B -These three bits define the color attribute of the corresponding character/symbol. Refer to the

TAB 2 for the color selections.

TAB 2. Character/Window Color Selection

COLOR R G B

Black 0 0 0

Blue 0 0 1

Green 0 1 0

Cyan 0 1 1

Red 1 0 0

Magenta 1 0 1

Yellow 1 1 0

White 1 1 1

TAB 3. Character/Window Background Color Selection

COLOR R G B

No Background 0 0 0

Blue 0 0 1

Green 0 1 0

Cyan 0 1 1

Red 1 0 0

Magenta 1 0 1

Yellow 1 1 0

White 1 1 1

11

NT68275

IIC Bus Controlled On-Screen Display

12 V1.0

Loading...

Loading...