NOVATEK NT3960 Datasheet

NT3960

TFT LCD Source Driver

Features

Output : 300/309 output channels

6-bit resolution /64 gray scale

Dot inversion with polarity control

V1 ~ V10 for adjusting Gamma correction

Power for analog circuit : 6.5 ~ 10V

Output dynamic range : 0.1 ~ AV

DD-0.1V

Power consumption of analog circuit : 2.5mA

Power for interface circuit : 3.0 ~ 3.6V

Operating frequency : 65MHz

Output deviation : 10 ~ 20mV

Data inverting for reducing EMI

Cascade function with bi-direction shift control

CMOS silicon gate ( p-type substrate )

COG

General Description

NT3960 is a data driver IC for a color TFT LCD panel. The channel number of 300 or 309 outputs is selectable for

SVGA and XGA applications. For better performance, dot inversion and a wide range voltage output, 6.5~10V, are designed

in this chip and for reducing EMI, data inversion control is used. This chip also supplies 10 sections of voltage-reference for

Gamma correction.

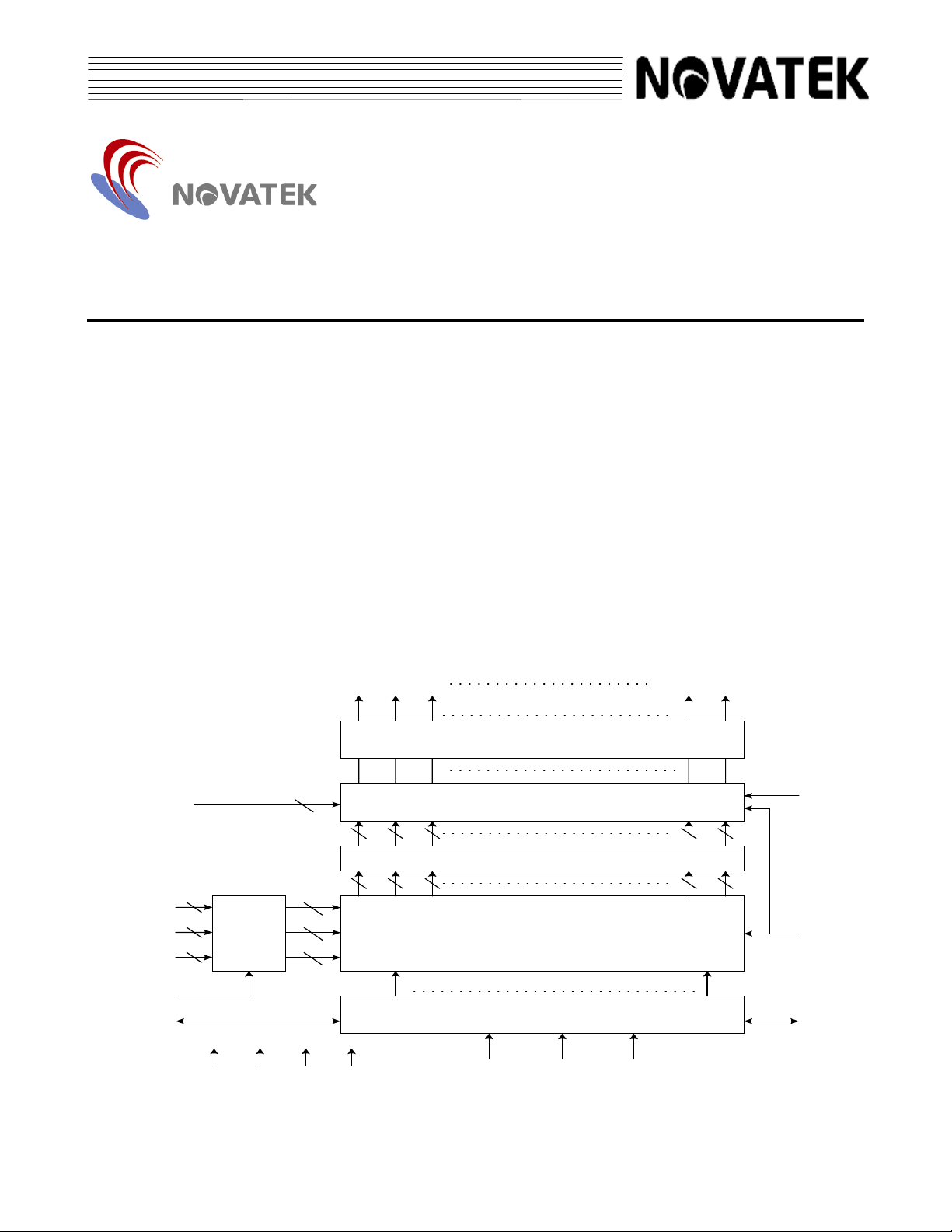

Block Diagram

OUT1

OUT3

OUT2

Out Driver Buffer ( 309 channels )

OUT308

OUT309

V1 ~ V10

D00 ~ D05

D10 ~ D15

D20 ~ D25

REV

DIO1 DIO2

6

6

Decoder

6

GND AVDD AVSS

Vcc

10

6

6

6

6

6

Digital to Analog Converter

6

Level Shift

Line Latch ( 309 X 6 bits X 2 )

1 103

Shift Registers ( 103 or 100 )

CLK SHL

SELT

6

6

6666

6

1 V1.0

POL

LD

NT3960

TFT LCD Source Driver

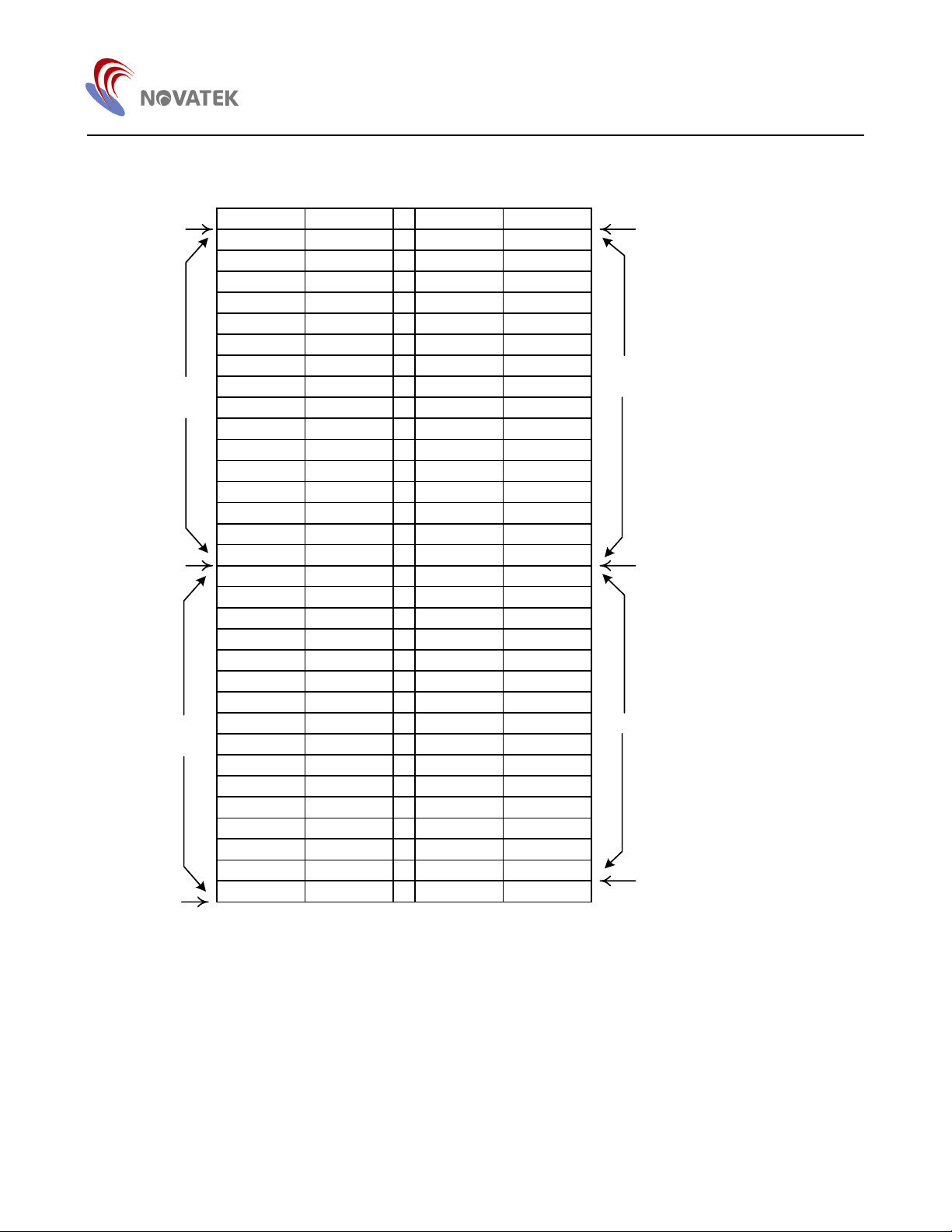

Pin Configuration (IC face view)

PASS1

PASS2

PASS3

DIO2

AVDD

AVSS

GND

Vcc

REV

SHL

GND

POL

LD

D25

D24

D23

NC

D22

D21

D20

Test

SELT

AVSS

V10

V9

V8

V7

V6

V5

V4

V3

V2

V1

AVDD

D15

D14

D13

NC

D12

D11

D10

NC

D05

D04

D03

NC

D02

D01

D00

NC

CLK

Vcc

GND

AVSS

AVDD

DIO1

PASS4

PASS5

PASS6

NT3960

PASS1

PASS2

PASS3

OUT309

OUT308

OUT307

OUT306

OUT305

OUT5

OUT4

OUT3

OUT2

OUT1

PASS4

PASS5

PASS6

2

NT3960

TFT LCD Source Driver

Pad Description

Pad No. Designation I/O

132~140,142~150,

112~120,122~130,

47~55, 57~65

31 ~ 34 REV I Controls whether data is inverted or not.

152 ~ 155 CLK

69 ~ 71 SELT

106 ~ 77 V1 ~ V10 I Gamma correction reference voltage. The voltage of these pins must be AVSS<

189 ~ 497 OUT1 ~

35 ~ 37 SHL I

176 ~ 178

8 ~ 10

44 ~ 46 LD I Latches the polarity of outputs and switches the new data to outputs.

D05 ~ D00

D15 ~ D10

D25 ~ D20

OUT309

DIO1

DIO2

I Data input. For three 6-bit data,1 pixel, of color data (R, G, B)

DX5 : MSB; DX0 : LSB

When “REV”=1 the data will be inverted. EX. “00” “ 3F”, “07” “ 38”, “15” “2A”,

and so on.

I Clock signal; latching data onto the line latches at the rising edge.

I Selects the output channel number; when SELT= “0” : 309 channels; and “1” = 300

channels (OUT151~ OUT159 are in-available ). There is a 100K internal pull-up

resistor with this pin.

V10< V9< V8<V7<V6; V5<V4<V3<V2<V1< AVDD

O Output drive signals;

If 300-channel function is selected, OUT151~ OUT159 are in-available.

Selects left or right shift;

SHL=“1” : DIO1OUT1,2,3OUT4,5,6OUT7,8,9---OUT307,308,309= DIO2

SHL=“0” : DIO1=OUT1,2,3OUT4,5,6OUT7,8,9--- OUT307,308,309DIO2

I/O Start pulse signal input/output

When SHL is applied high (SHL="1"), a start high-pulse on DIO1 is latched at the

rising edge of the CLK. Then the data are latched serially onto internal latches at

the rising edge of the CLK. After all line latches are full with data, 100/103 clocks, a

pulse is shifted out through the DIO2 pin at the rising edge of the CLK. This function

can cascade two or more devices for dot expansion. In normal applications, the

DIO2 signal of the first device is connected to the DIO1 of the second stage, and the

DIO2 of the second one is connected to the DIO1 of the third, and so on like a daisy

chain.

In contrast, when SHL is applied low, a start pulse inputs on DIO2, and outputs

through DIO1.

*Remark : The input pulse-width of DIO1/2 may be over 1 clock-cycle.

1. At the rising edge, latches the “POL” signal to control the polarity of the outputs.

2. The pin also controls the switch of the line registers that switches the new

incoming data

to outputs.

*Remark : The LD may switch the new data to outputs at anytime even if the line

data are not completely full.

SHL

1 Input Output Right

0 Output Input Left

DIO1

Description

DIO2

SHIFT

3

NT3960

TFT LCD Source Driver

Pad Description (continued)

Pad No. Designation I/O

41 ~ 43 POL I Polarity select for the dot-inversion control. Available at the rising edge of LD

“POL” value is latched at the rising edge of “LD” to control the polarity of the even or

odd outputs. “POL=1” represents that the next-line odd outputs are of positive

polarity with a voltage output range from V1~V5, and even outputs are of negative

polarity with a voltage output range from V6 to V10. On the other hand, if LD gets

low level “POL”, odd outputs are of negative polarity and even outputs are of

positive.

POL=1: Odd outputs range from V1 ~ V5

Even outputs range from V6 ~ V10

POL=0: Odd outputs range from V6 ~ V10

Even outputs range from V1 ~ V5

*Remark: Pay attention to the polarity when selecting the 300-channel function.

The polarity of OUT160 ~OUT309 must be changed. (The polarity needs to

be continuous, +, -, +, -, +, -, etc. If you don’t change the polarity, it will not be

continuous between OUT150 and OUT160 when selecting the 300-channel

function. )

11~15, 107~111,

171~175

16 ~ 20, 72 ~ 76,

166 ~ 170

26 ~ 30, 156 ~ 160 Vcc I Power supply for digital circuits

21 ~ 25, 38 ~ 40,

161 ~ 165

66 ~ 68 Test - For testing

5~7, 500~498

179~181,188~186

501, 502 Align Mark - For COG assembly alignment

1~4, 182 ~ 185,

56, 121, 131, 141,

151

AVDD I Power supply for analog circuits ; 6.5 ~ 10V

AVSS I Ground pins for analog circuits

GND

PASS1~3

PASS4~6

NC - No connected

I Ground pins for digital circuits

- The internal connected paths

Description

4

NT3960

TFT LCD Source Driver

Power on/off sequence:

This IC is a high-voltage LCD driver, so may be damaged by a large current flow when an incorrect power sequence is used.

First connecting the logical power, Vcc & GND and then the drive power, AVDD&AVSS with V1~V10 as the last is the

recommended sequence. When shutting off the power, first shut off the drive power and then the logic system, or turn off all

power simultaneously.

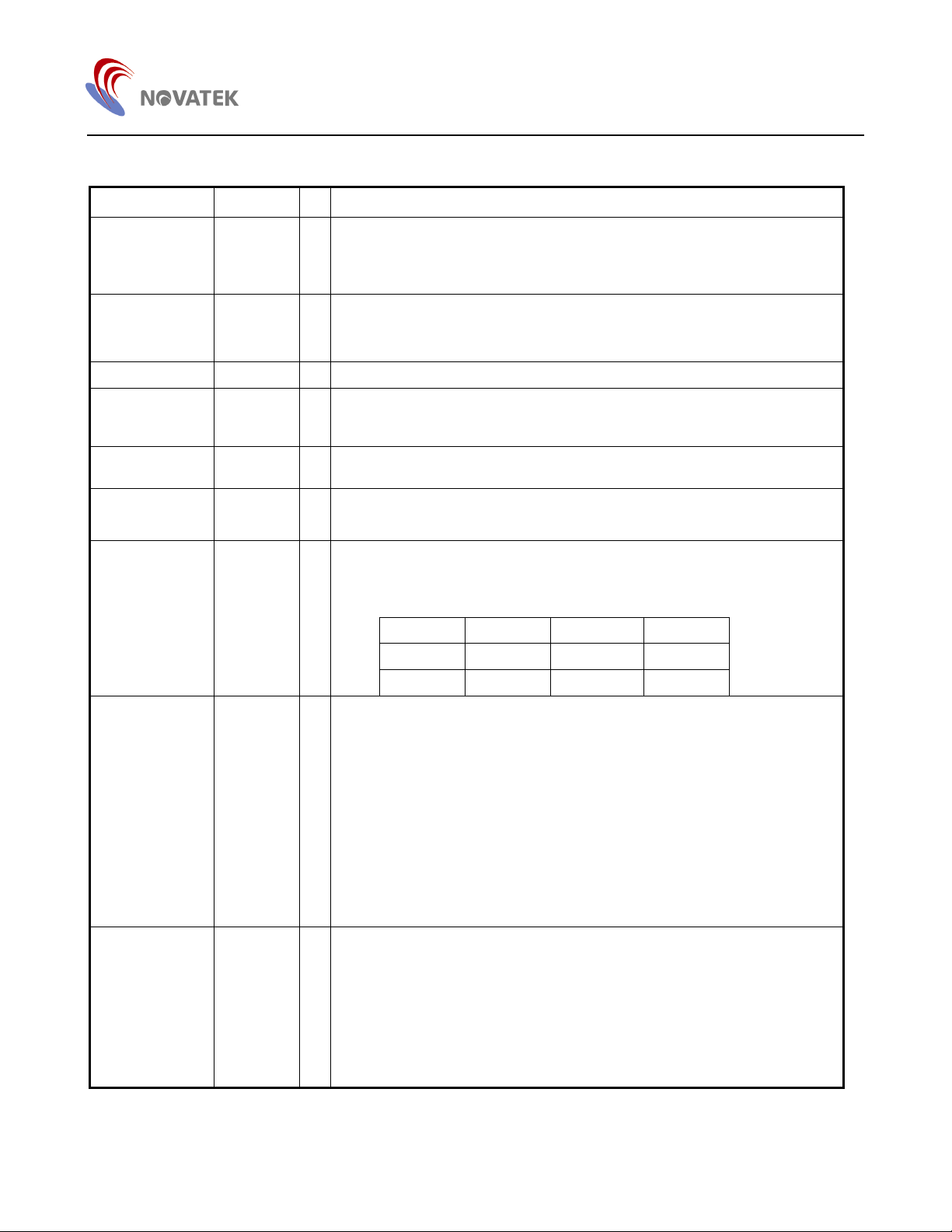

Relationship between input data and output channels

(1) SHL=”1” , shift right, a start pulse from DIO1

Output

Order

Data

(2) SHL=”0”, shift left, a start pulse from DIO2

Output

Order

Data

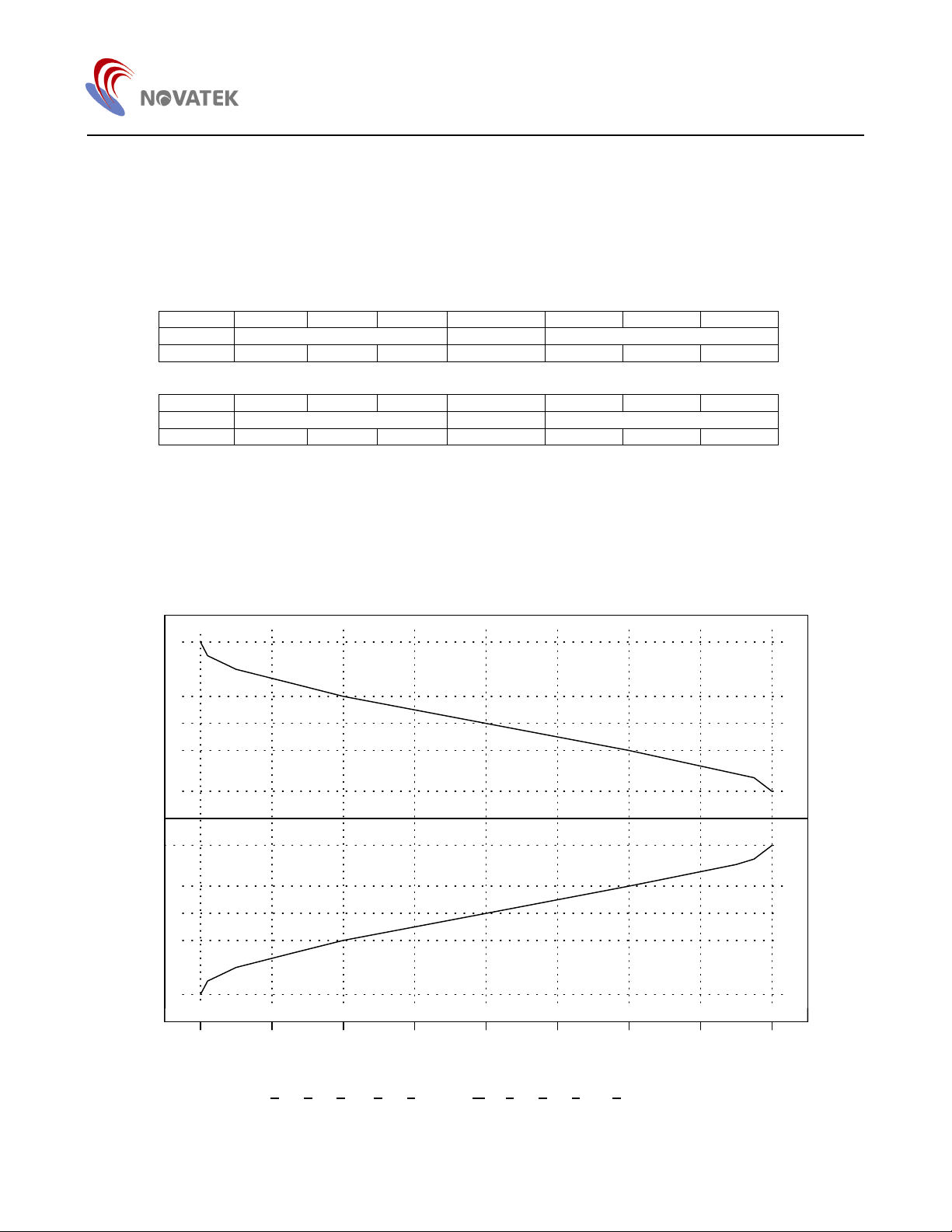

Relationship between input data and output voltage

The figure below shows the relationship between the input data and the output voltage with the polarity. The range of

V1~V5 is for positive polarity, and V6 ~ V10 for negative polarity. Please refer to the following pages to get the relative resistor

value and voltage calculation method.

Gamma correction diagram

Vout

AVDD

OUT1 OUT2 OUT3 - - - OUT307 OUT308 OUT309

First data --- Last data

D05~D00 D15~D10 D25~D20 - - - D05~D00 D15~D10 D25~D20

OUT1 OUT2 OUT3 - - - OUT307 OUT308 OUT309

Last data --- First data

D05~D00 D15~D10 D25~D20 - - - D05~D00 D15~D10 D25~D20

V1

V2

V3

V4

V5

Vcom

V6

V7

V8

V9

V10

AVSS

08H

10H00H 18H 20H 28H 30H 38H 3FH

Positive polarity

Negative polarity

Input Data

Remark : AV

DD-0.1 > V1 > V2 > V3 > V4 > V5 ; V6 > V7 > V8 > V9 > V10 >AVSS+0.1V

Actual application( for reference only): AVDD=8.4V, V1=8.2V, V2=7.16V, V3=6.72V, V4=6.38V,

V5=4.98V, V6=3.44V, V7=2.08V, V8=1.70V, V9=1.28V, V10=0.20V.

5

NT3960

TFT LCD Source Driver

Gamma correction resistor

V1, V10

V2, V9

2.65K

V3, V8

7.5K

Name resistor

R0 2000 R32 150

R1 500 R33

R2 500 R34

R3 500 R35

R4 500 R36

R5 500 R37

R6 500 R38

R7 500 R39

R8 250 R40

R9 250 R41

R10 250 R42

R11 250 R43

R12 250 R44

R13 250 R45

R14 250 R46

R15 250 R47

R16 250 R48

R17 250 R49

R18 200 R50

R19 150 R51

R20 150 R52

R21 150 R53

R24 150 R56

R25 150 R57

R26 150 R58

R27 150 R59 500

R28 150 R60 500

R29 150 R61 1250

R30 150 R62 1750

R31 150

Name resistor

150

150

150

150

150

150

100

100

100

150

150

150

150

150

150

150

150

150

150

150

150

200R22 150 R54

250R23 150 R55

250

250

250

V3, V8

2.25K

V4, V7

6.10K

V5, V6

Total impedance, Rn=R0 ~ R62, equals 18.5K

6

Loading...

Loading...