NOVATEK NT3883H, NT3883F Datasheet

Features

Provides 80-channel LCD driver

Internal serial to parallel conversion circuits:

40-bit bi-direction shift r egister 2

80-bit lat ch 1

80-bit 4-level driver 1

Logic circuit supply voltage range: 4.5V - 5.5V

General Description

The NT3883 is a dot matrix LCD 80-channel driver

fabricated by low power CMOS technology. This IC

consists of two 40-bit bi-directional shift registers, 80-bit

latch and 80-bit 4-l evel LCD driver. The NT3883 converts

serial data that are received from the LCD controller, such

Pin Configuration

NT3883

Dot Matrix LCD 80-Channel Driver

DD

LCD driving voltage range (V

Applicable LCD duty cycle: 1/2 to 1/16

Interfaces with a NT3881B/C/D LCD controller

LCD bias voltage can be supplied externally

Available in 100-pi n Q FP and i n CHIP FO RM

as NT3881B/C/D, to paral lel data and outputs LCD dri ving

waveforms to drive LCD. Expansion of character-type

liquid cryst al display can be easily obtained according to

the number and structure of characters.

- VEE): 3.5V to 11V

S30

S29

S28

S27

S26

S25

S24

S23

S22

S21

S20

S19

S18

S17

S16

S15

S14

S13

S12

S11

S10

S

S

S

S

3

3

3

3

1

4

3

2

100

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

S9

22

S8

23

S7

24

S6

25

S5

26

S4

27

S3

28

S2

29

S1

30

31 3832 39 45 48 50

V

N

C

E

E

D

S

S

S

S

3

3

3

3

8

7

6

5

9399 92 86 83 81

96

NT3883F

35

S

C

G

V

L

L

N

2V3VD

1

1

D

S

S

S

S

7

8

4

3

9

0

0

9

NCNCNCS

L

2

S

S

S

S

7

7

7

7

5

6

7

8

8590 89 8897 9195

87

4641 42 4334 4036

44

D

D

D

C

L

R

L

L

2

1

1

2

S

S

S

S

7

7

7

7

1

2

3

4

8498 8294

S70

80

S69

79

S68

78

S67

77

S66

76

S65

75

S64

74

S63

73

S62

72

S61

71

S60

70

S59

69

S58

68

S57

67

S56

66

S55

65

S54

64

S53

63

S52

62

S51

61

S50

60

S49

59

S48

58

S47

57

S46

56

S45

55

S44

54

S43

53

S42

52

S41

51

4733 4937

NCNCMD

R

2

1 V2.1 November, 1999

Pad Configuration

S31

S30

S29

S28

S27

S26

S25

S24

S23

S22

S21

S20

S19

S18

S17

S16

S15

S14

S13

S12

S11

S10

NT3883

S

S

3

2

100

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

S9

S8

23

S7

24

S6

25

S5

26

S4

27

S3

28

S2

29

S1

31

30

S

S

S

S

3

3

3

5

4

3

95

3

4

3

3

3

9

0

8

7

6

94 93 92 91 90 89 8899 98 97 96 87 86 85 84 83 82

NT3883H

33 34 353637 38 39 43 44 45 464748

G

S

G

V

E

E

V2V3V

N

L

D

D

L

D

1

1

S

S

S

S

S

S

S

7

7

8

8

9

0

D

C

S

L

L

L

1

2

2

S

S

S

7

7

6

7

D

R

1

S

S

7

7

7

7

4

5

2

3

S71

81

S70

80

S69

79

S68

78

S67

77

S66

76

75

S65

74

S64

73

S63

72

S62

S61

71

70

S60

69

S59

68

S58

S57

67

66

S56

65

S55

64

S54

63

S53

62

S52

61

S51

60

S50

59

S49

S48

58

S47

57

S46

56

55

S45

54

S44

S43

53

S42

52

S41

51

D

M

D

R

L

2

2

2

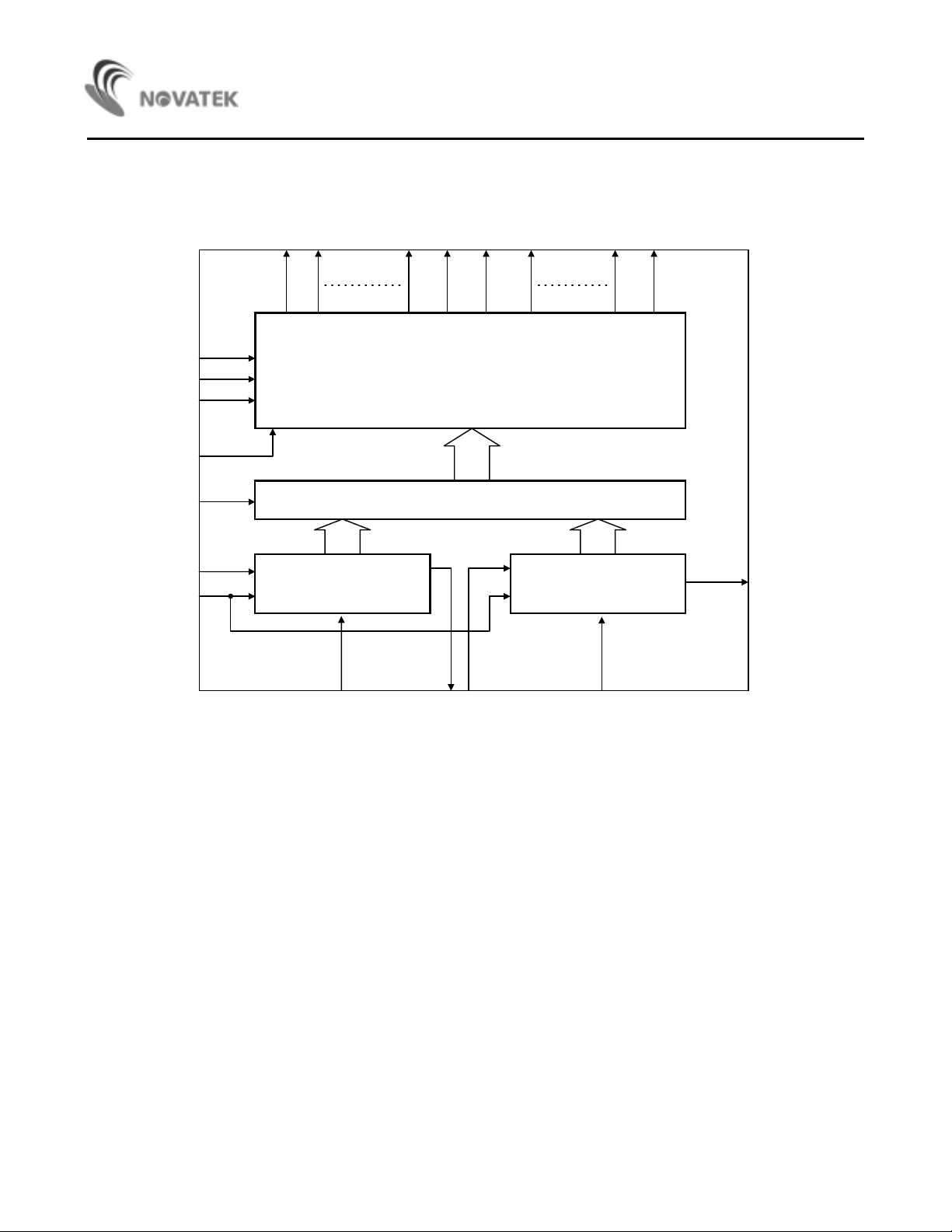

Block Diagram

g

DD

V

2

V

3

V

EE

V

M

NT3883

S1 S2 S39 S40 S41 S42 S79 S80

80-Bit 4-Level LCD Drivers

CL1

DL2

CL2

First

40-Bit Shift Re

ister

SL1 SL2

80-Bit Latch

Second

40-Bit Shift Register

DR2

GNDDL2DR1

3

NT3883

Absolute Maximum Rating s*

Power Su p pl y Volta ge ( VDD-GND) . . . . . . -0.3V to 7.0V

Power Supp l y Vo l ta ge (V

. . . . . . . . . . . . . . . . . . . . . .V

Input Voltage . . . . . . . . . . . . . . -0.3V to V

Operating Temperature . . . . . . . . . . -20

Storage Temperature . . . . . . . . . . . . . -55qC to + 125qC

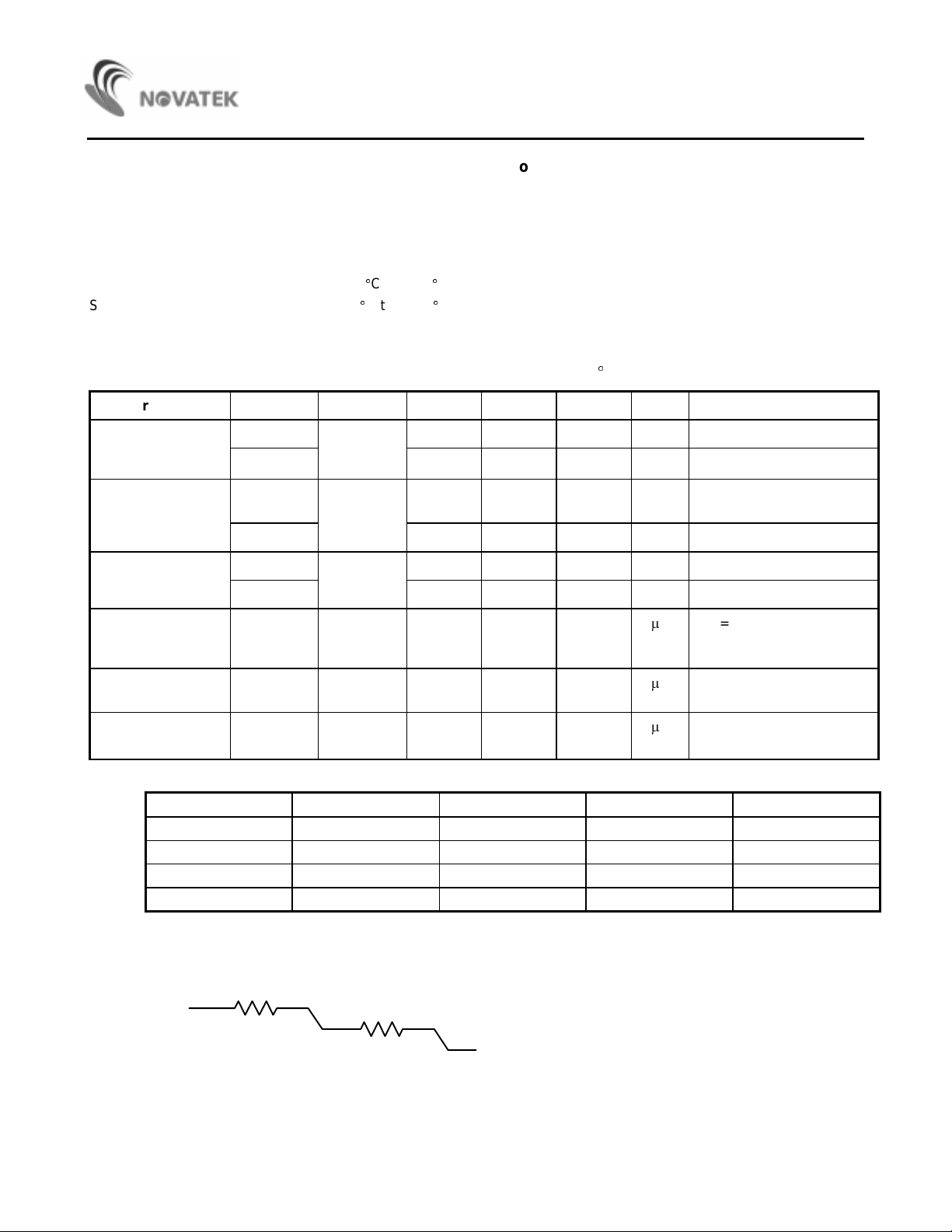

DC Electrical Characteristics

) . . . . . . . . . . . . . . . . . .

DD-VEE

DD

- 13.5V to VDD + 0.3V

(V

= 5.0V, GND = 0V, V

DD

DD

+ 0.3V

q

C to + 75qC

*Comments

Stresses above those listed under "Absolute Maximum

Ratings" may cause permanent damage to this device.

These are stress ratings only. Functional operation of

this device at these or any other conditions above those

indicated in the operational sections of this specification

is not implied and exposure to the absolute maximum

rating conditi ons for extended periods may affect device

reliability.

= 0V, TA = 25

EE

q

C)

Parameter Symbol Terminal Min. Typ. Max. Unit Conditions

Input Voltage

Output Voltage

IH

V

IL

V

OH

V

CL1, CL2,

DL1, DL2

*1

DR1, DR2

DD

0.7 V

0-

DD

- 0.4

V

-

V

0.3 V

DD

DD

--V

V

V

IOH = -0.4mA

*1

--0.4V

--1.1V

--1.5V

OL

= +0.4mA

I

ON

= 0.1mA for one of Sj

I

ON

= 0.05mA for each of Sj

I

Vi - Sj Voltage

Descending

OL

V

D1

V

D2

V

*2

Input Leakage

Current

IL

I

CL1, CL2

DL1,

-5 - 5

P

A

IN

= 0 or V

V

DD

DL2*1

Vi Leakage

VL

I

V2, V3, V

EE

-10 - 10

P

A

S1 to S80 open

Current

Power Supply

Current

DD

I

*3 - - 500

P

A

CL1

= 1KHz

f

CL2

= 1MHz

f

Note *1: SL1 and SL2 determine The Input or Output of DL1, DL2, DR1 and DR2 and the configuration is as follows.

Terminal SL1 = High SL1 = Low SL2 = High SL2 = Low

DL1 Output Input - -

DR1 Input Output - -

DL2 - - Output Input

DR2 - - Input Output

*2: Vi – Sj (Vi = VDD, V2, V3, VEE; j = 1 to 80) equivalent cir c ui t (for reference)

*3: Input/out put cur r ent is excluded. W hen the input is at the intermediate level with CMOS, some excessive

1Kmax.

V

i

Power

Switch

10Kmax.

Data

Swtich

S

j

Current will flow through the input circuit to power supply. To avoid this, the input l evel must be fixed at high or

low state.

4

Loading...

Loading...