Page 1

Some Thoughts on DC/DC Converters

Jim Williams and Brian Huffman

INTRODUCTION

Application Note 29

October 1988

Many systems require that the primary source of DC power

be converted to other voltages. Battery driven circuitry is

an obvious candidate. The 6V or 12V cell in a laptop computer must be converted to different potentials needed for

memory, disc drives, display and operating logic. In theory,

AC line powered systems should not need DC/DC converters

because the implied power transformer can be equipped

with multiple secondaries. In practice, economics, noise

requirements, supply bus distribution problems and other

constraints often make DC/DC conversion preferable. A

common example is logic dominated, 5V powered systems

utilizing ±15V driven analog components.

The range of applications for DC/DC converters is large,

with many variations. Interest in converters is commensurately quite high. Increased use of single supply powered

systems, stiffening performance requirements and battery

operation have increased converter usage.

Historically, effi ciency and size have received heavy emphasis. In fact, these parameters can be signifi cant, but

often are of secondary importance. A possible reason

behind the continued and overwhelming attention to size

and effi ciency in converters proves surprising. Simply

put, these parameters are (within limits) relatively easy to

achieve! Size and effi ciency advantages have their place,

but other system-oriented problems also need treatment.

Low quiescent current, wide ranges of allowable inputs,

substantial reductions in wideband output noise and cost

effectiveness are important issues. One very important

converter class, the 5V to ±15V type, stresses size and

effi ciency with little emphasis towards parameters such

as output noise. This is particularly signifi cant because

wideband output noise is a frequently encountered problem

with this type of converter. In the best case, the output noise

mandates careful board layout and grounding schemes.

In the worst case, the noise precludes analog circuitry

from achieving desired performance levels (for further

discussion see Appendix A, “The 5V to ±15V Converter

— A Special Case”). The 5V to ±15V DC/DC conversion

requirement is ubiquitous, and presents a good starting

point for a study of DC/DC converters.

5V TO ±15V CONVERTER CIRCUITS

Low Noise 5V to ±15V Converter

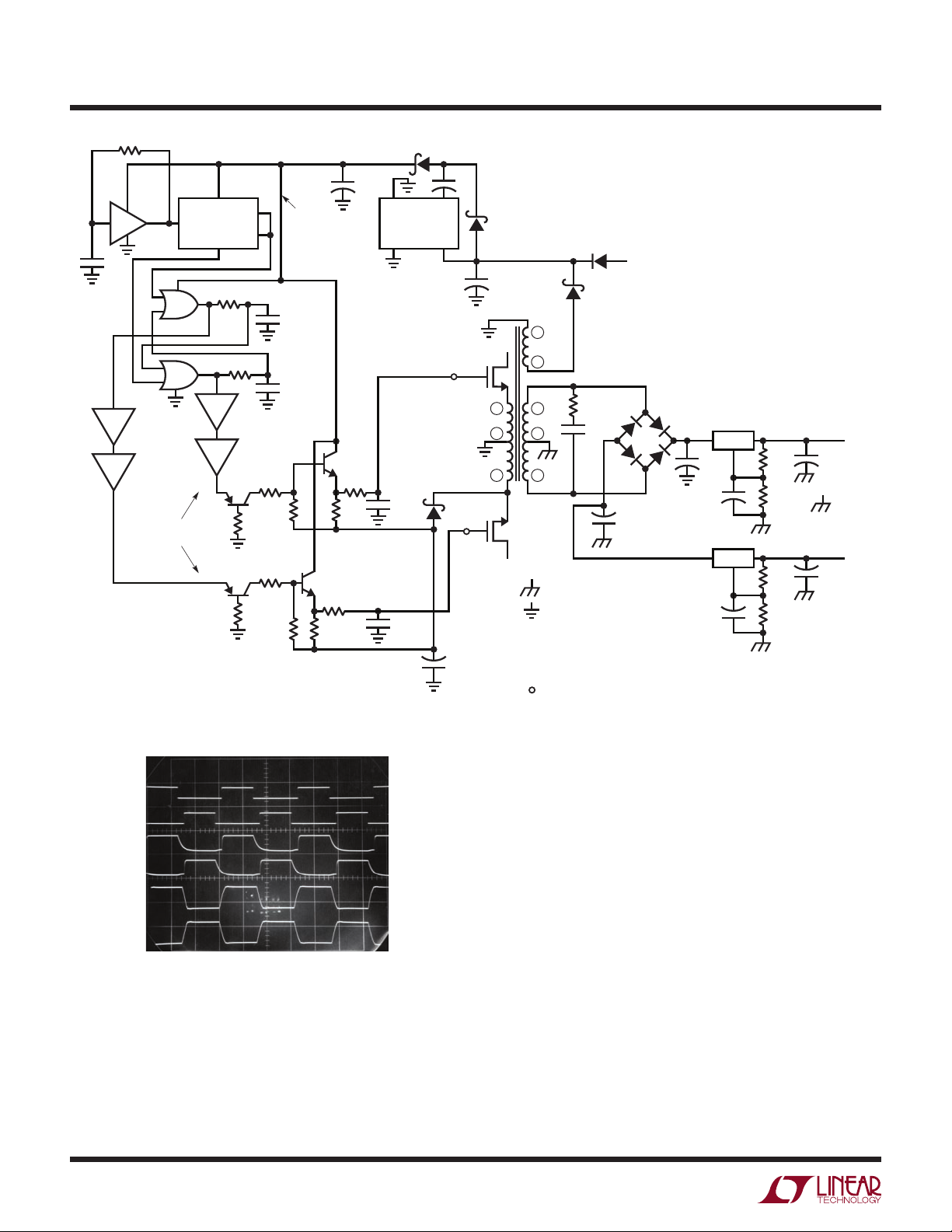

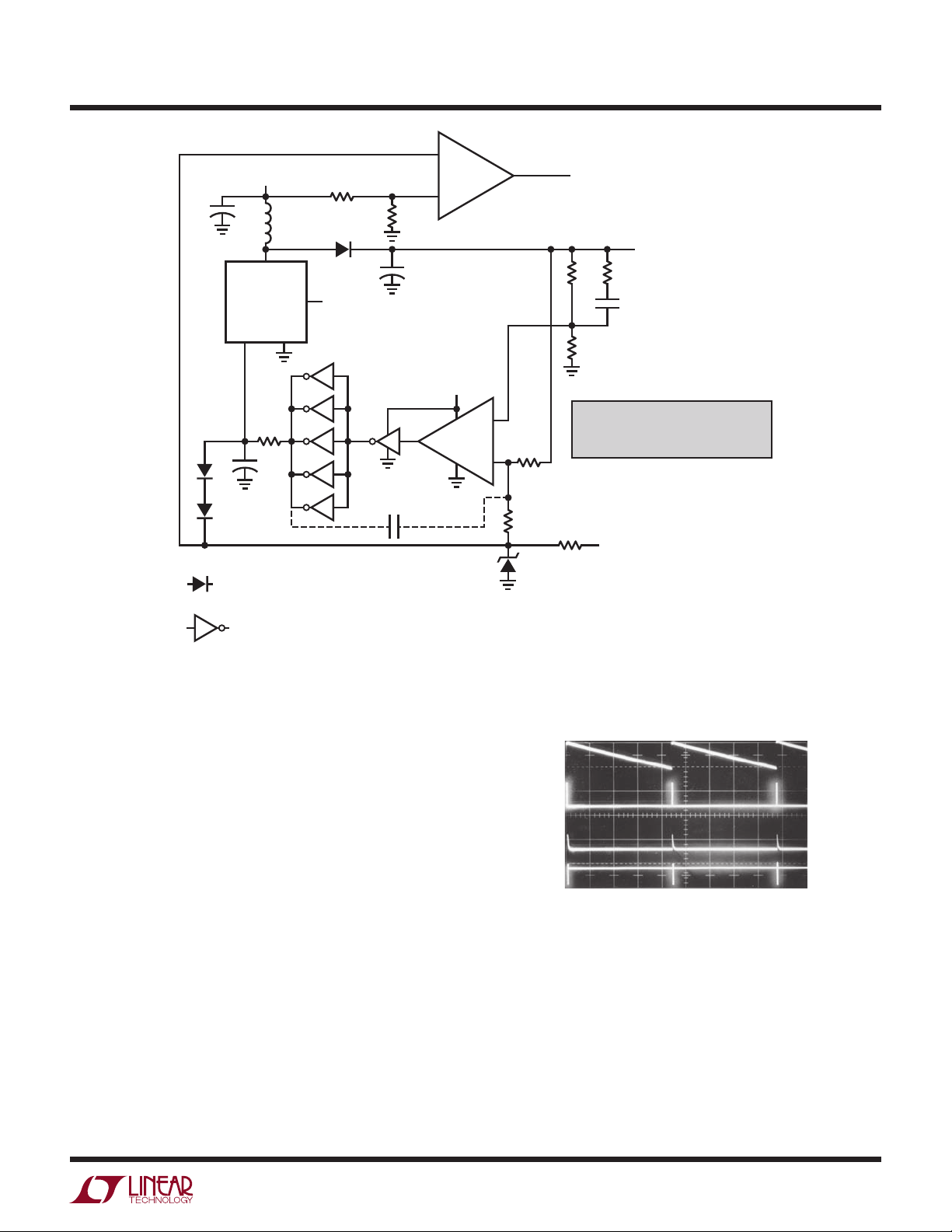

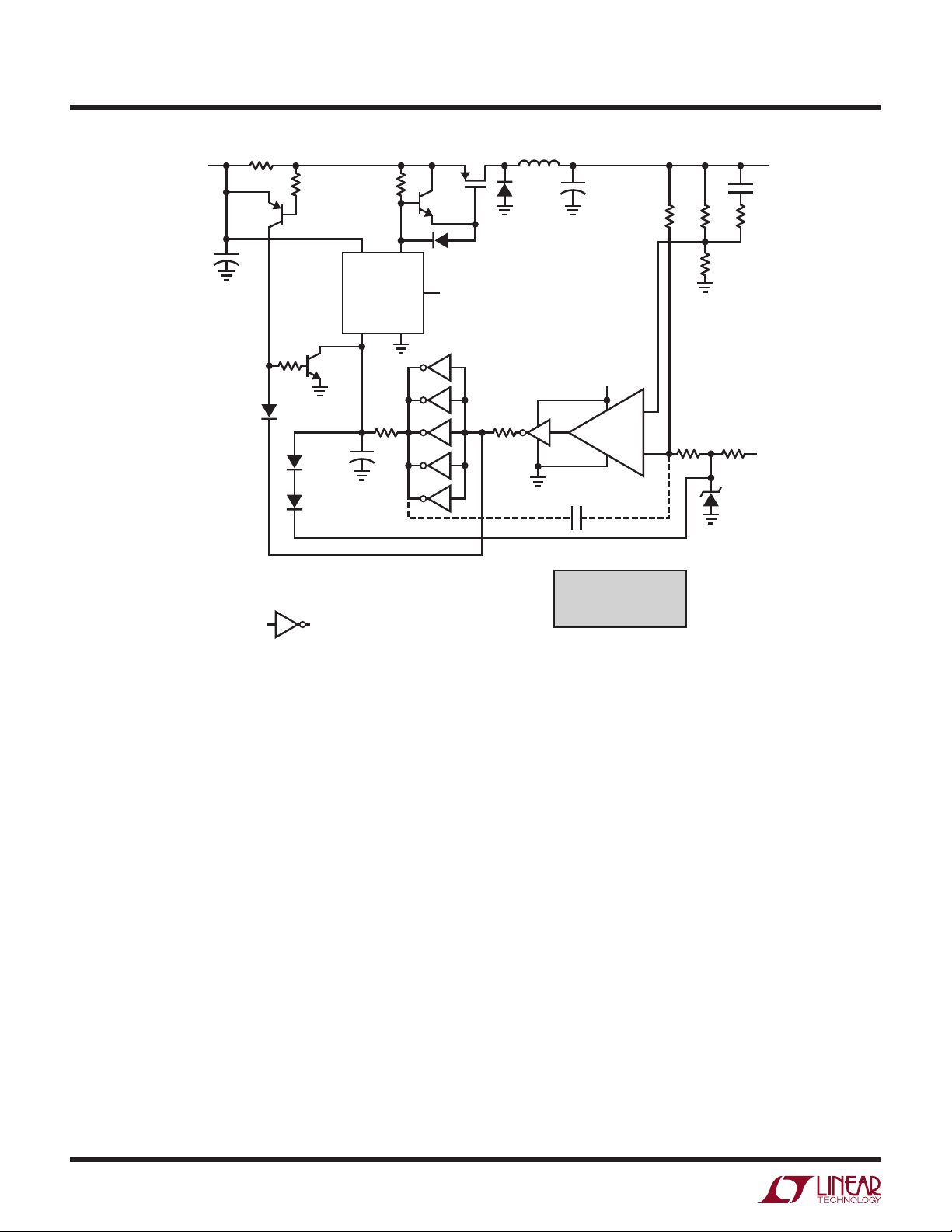

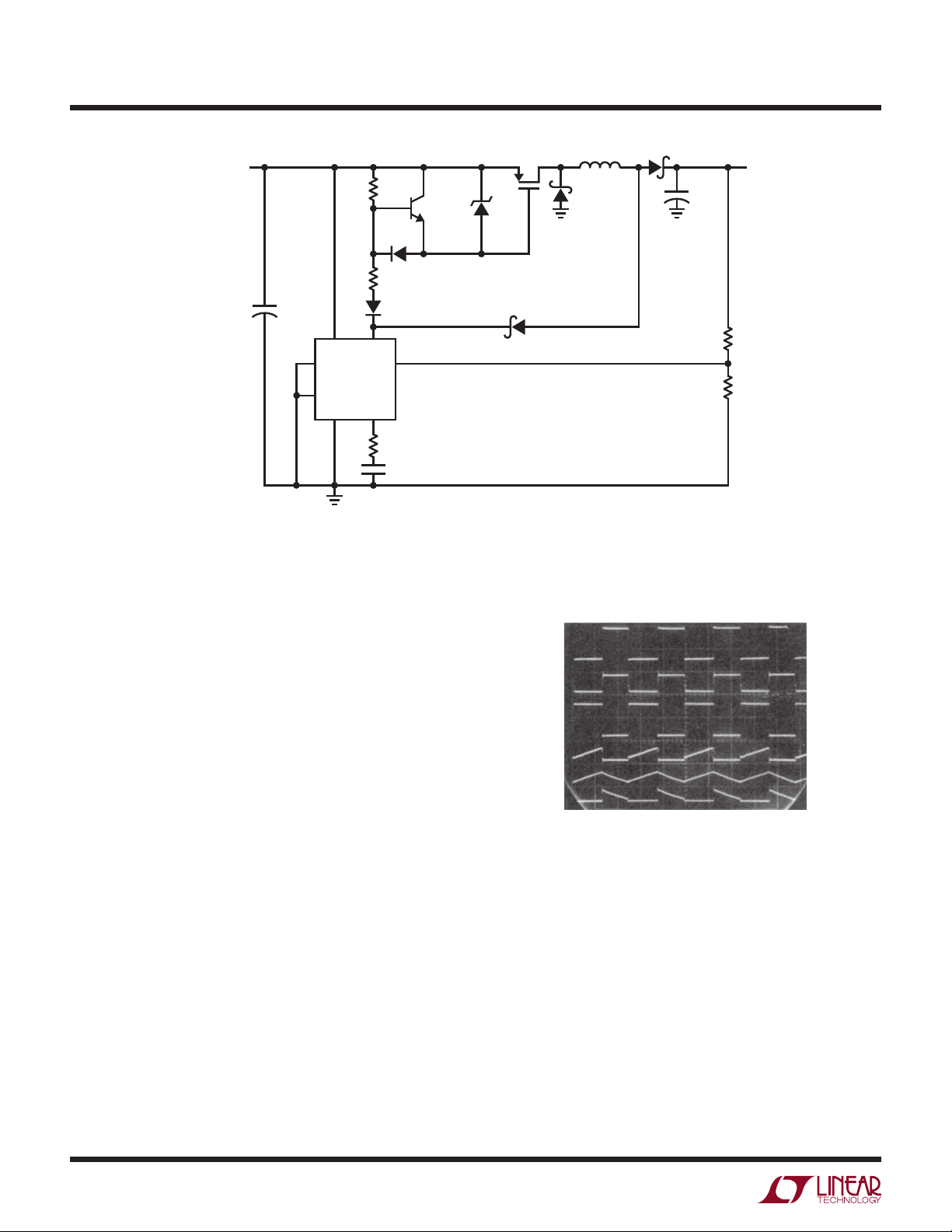

Figure 1’s design supplies a ±15V output from a 5V input.

Wideband output noise measures 200 microvolts peakto-peak, a 100× reduction over typical designs. Effi ciency

at 250mA output is 60%, about 5% to 10% lower than

conventional types. The circuit achieves its low noise

performance by minimizing high speed harmonic content

in the power switching stage. This forces the effi ciency

trade-off noted, but the penalty is small compared to the

benefi t.

The 74C14 based 30kHz oscillator is divided into a 15kHz

2-phase clock by the 74C74 fl ip-fl op. The 74C02 gates and

10k-0.001μF delays condition this 2-phase clock into nonoverlapping, 2-phase drive at the emitters of Q1 and Q2

(Figure 2, Traces A and B, respectively). These transistors

provide level shifting to drive emitter followers Q3-Q4. The

Q3-Q4 emitters see 100Ω-0.003μF fi lters, slowing drive

to output MOSFETs Q5-Q6. The fi lter’s effects appear at

the gates of Q5 and Q6 (Traces C and D, respectively). Q5

and Q6 are source followers, instead of the conventional

common source connection. This limits transformer rise

time to the gate terminals fi ltered slew rate, resulting in

L, LT, LTC, LTM, Linear Technology and the Linear logo are registered

trademarks of Linear Technology Corporation. All other trademarks are the

property of their respective owners.

an32f

AN29-1

Page 2

Application Note 29

0.001

CLK-NON

OVERLAP

GENERATOR

22k

74C14

74C02

74C14

74C14

CK

74C02

15kHz, 5μs

NON-OVERLAP

+V

74C74

Q

10k

10k

74C14

74C14

K1

Q1

LEVEL SHIFTS

K2

Q2

Q

D

0.001

0.001

100Ω

150k 1k

10k

100Ω

10k

+

POINT

“A”

(SEE TEXT)

BOOST

OUTPUT

≈17V

DC

DIRVERS-

EDGE

SHAPING

Q4

100

1k150k

1N5817

+

2

8

–4V

+

10

+

D1

1N5817

DC

22μF

Q5

1N5817

47

4

5V

D

6

S

1

7

2

8

3 9

L1

OUTPUT

S

Q6

D

5V

= ±15 COMMON

= +5 GROUND

* = 1% FILM RESISTOR

FET = MTP3055E-MOTOROLA

PNP = 2N3906

NPN = 2N3904

L1 = PULSE ENGINEERING, INC. #PE-61592

= FERRITE BEAD, FERRONICS #21-110J

D3

1N5817

D2

1N5817

TURBO BURST

470

0.001

100μF

+

5V

IN

(4.5V TO 5.5V)

MUR 120

(ALL)

10μF

1μF

+

+15

OUT

OUT

COMMON

–15

OUT

LT1086

+

100μF

+

10μF

LT337A

10μF

+

124*

1.37k*

249*

2.74k*

AN29 F01

+

100

3

LT1054

5

BOOST

Q3

100

0.003

0.003

Figure 1. Low Noise 5V to ±15V Converter

A = 20V/DIV

B = 20V/DIV

C = 20V/DIV

D = 20V/DIV

E = 10V/DIV

F = 10V/DIV

HORIZ = 20μs/DIV

AN29 F02

Figure 2. 5V to ±15V Low Noise Converter Waveforms

well controlled waveforms at the sources of Q5 and Q6

(Traces E and F, respectively). L1 sees complimentary,

slew limited drive, eliminating the high speed harmonics

normally associated with this type converter. L1’s output

is rectifi ed, fi ltered and regulated to obtain the fi nal out-

put. The 470Ω-0.001μF damper in L1’s output maintains

loading during switching, aiding low noise performance.

The ferrite beads in the gate leads eliminate parasitic RF

oscillations associated with follower confi gurations.

The source follower confi guration eases controlling L1’s

edge rise times, but complicates gate biasing. Special

provisions are required to get the MOSFETs fully turned

on and off. Source follower connected Q5 and Q6 require

voltage overdrive at the gates to saturate. The 5V primary

supply cannot provide the specifi ed 10V gate — channel

bias required for saturation. Similarly, the gates must be

pulled well below ground to turn the MOSFETs off. This

is so because L1’s behavior pulls the sources negative

when the devices turn off. Turn-off bias is bootstrapped

from the negative side of Q6’s source waveform. D1 and

the 22μF capacitor produce a –4V potential for Q3 and Q4

to pull down to. Turn-on bias is generated by a 2-stage

an32f

AN29-2

Page 3

Application Note 29

boost loop. The 5V supply is fed via D3 to the LT®1054

switched capacitor voltage converter (switched capacitor

voltage converters are discussed in Appendix B, “Switched

Capacitor Voltage Converters — How They Work”). The

LT1054 confi guration, set up as a voltage doubler, initially

provides about 9V boost to point “A” at turn-on. When

the converter starts running L1 produces output (“Turbo

Boost” on schematic) at windings 4-6 which is rectifi ed by

D2, raising the LT1054’s input voltage. This further raises

point “A” to the 17V potential noted on the schematic.

These internally generated voltages allow Q5 and Q6 to

receive proper drive, minimizing losses despite their source

follower connection. Figure 3, an AC-coupled trace of the

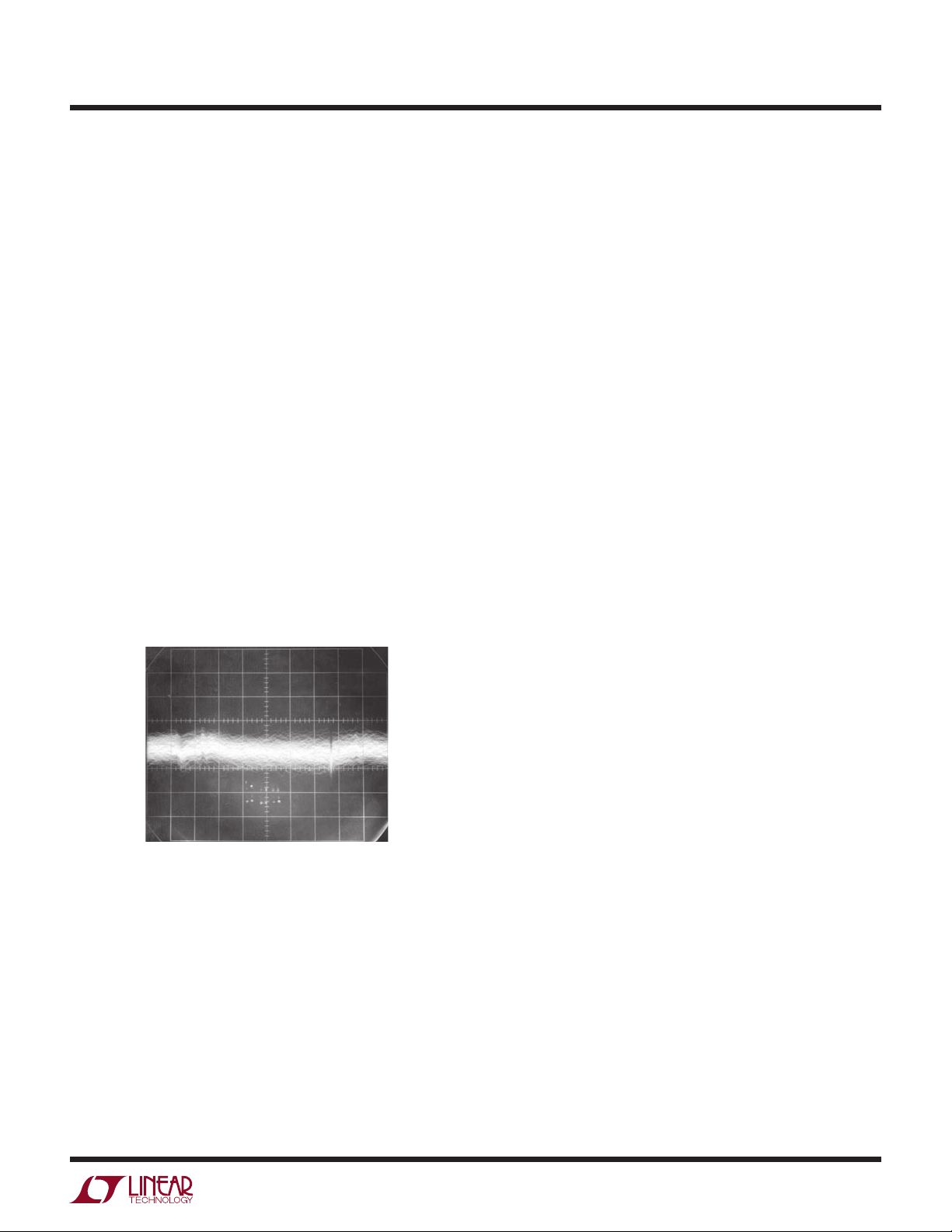

15V converter output, shows 200μV

noise at full power

P-P

(250mA output). The –15V output shows nearly identical characteristics. Switching artifacts are comparable in

amplitude to the linear regulators noise. Further reduction

in switching based noise is possible by slowing Q5 and

Q6 rise times. This, however, necessitates reducing clock

rate and increasing non-overlap time to maintain available

output power and effi ciency. The arrangement shown

represents a favorable compromise between output noise,

available output power, and effi ciency.

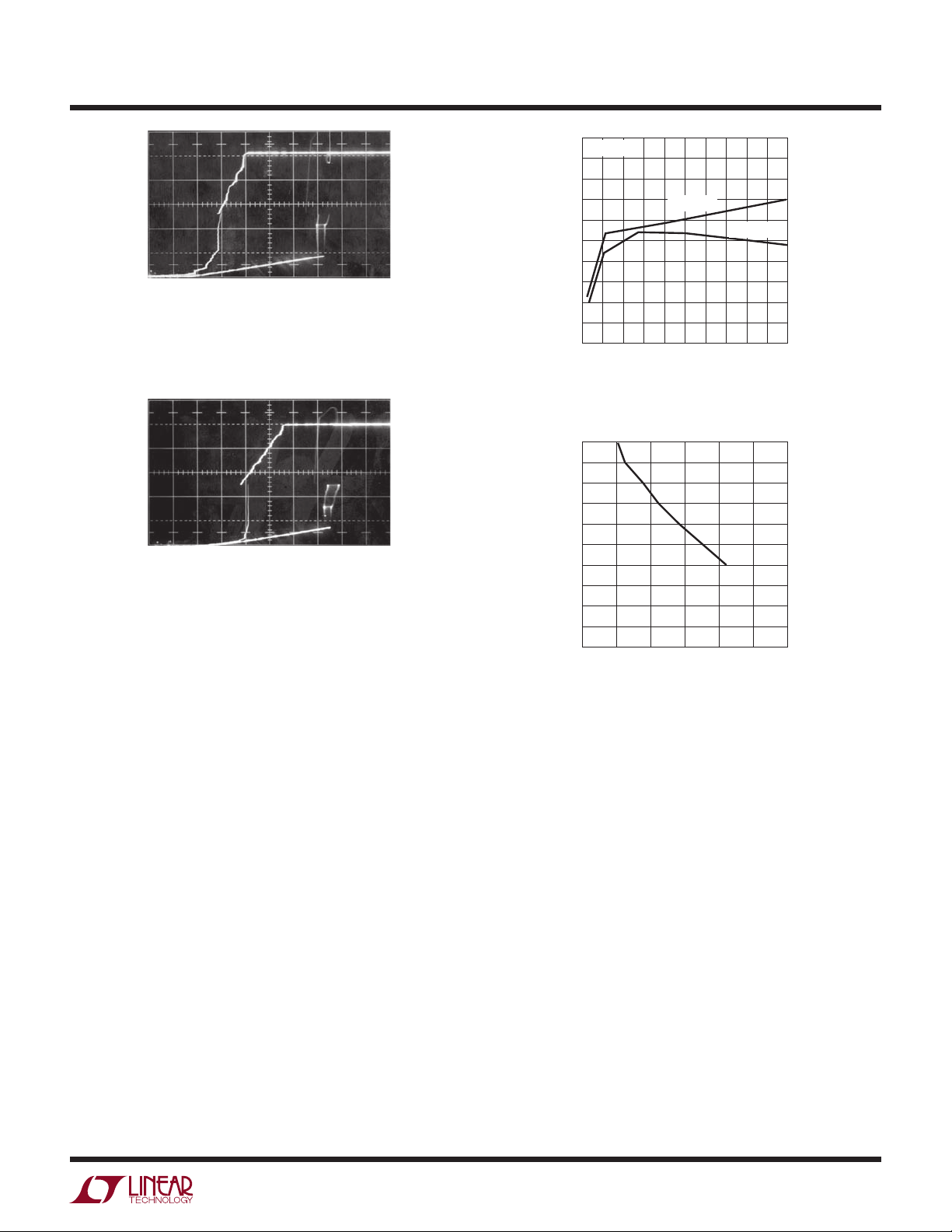

A = 100μV/DIV

(AC-COUPLED)

less than 30μV of output noise. This is almost 7× lower

than the previous circuit and approaches a 1000× improvement over conventional designs. The trade off is effi ciency

and complexity.

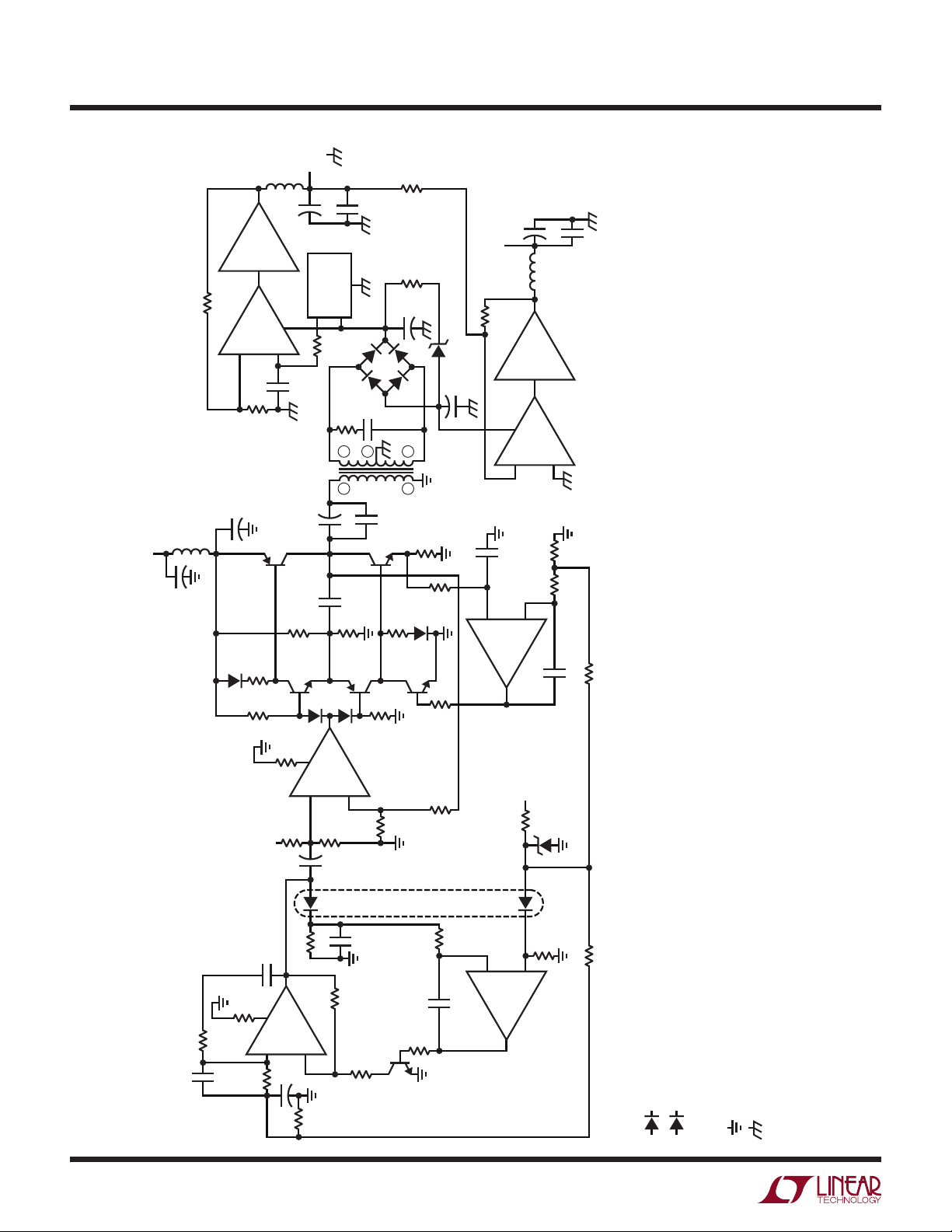

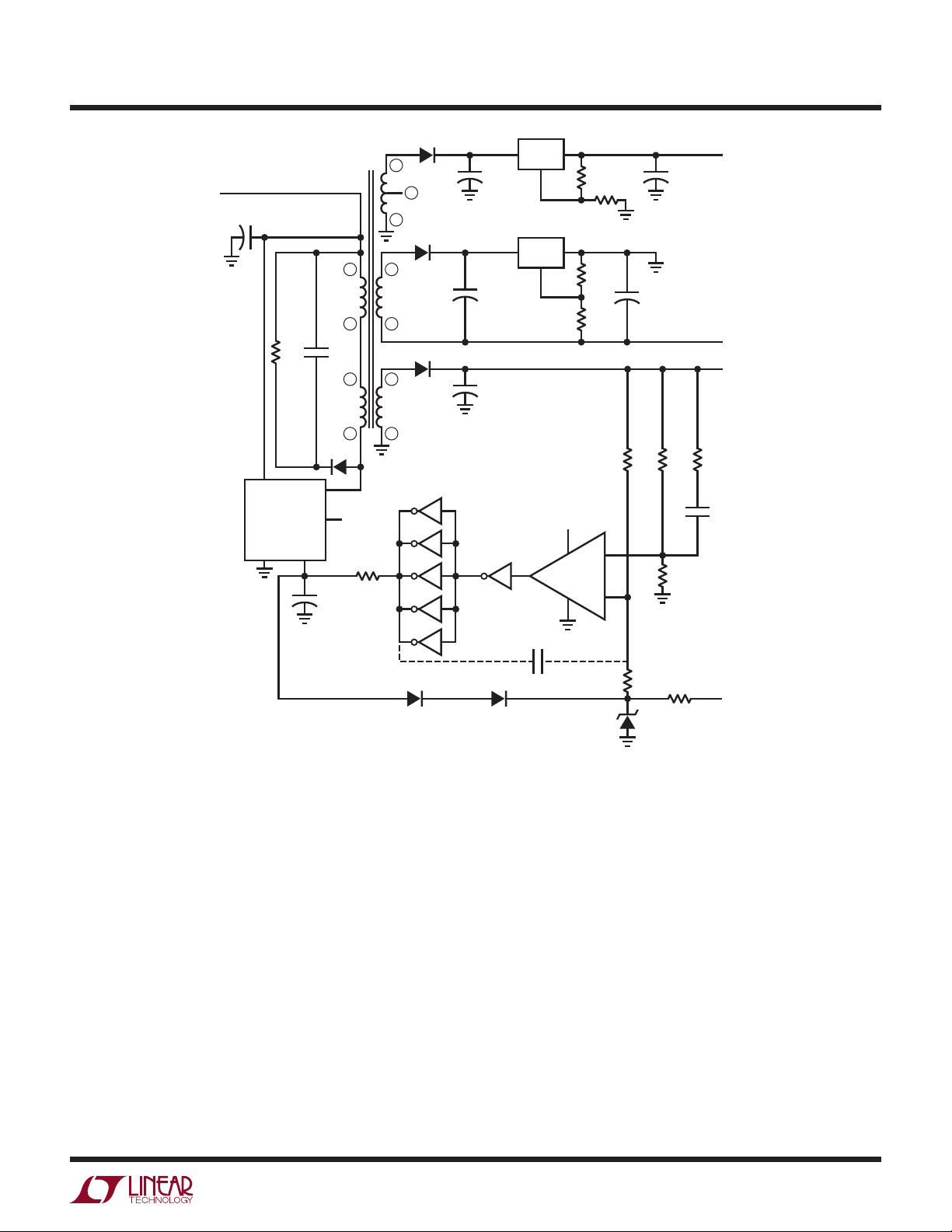

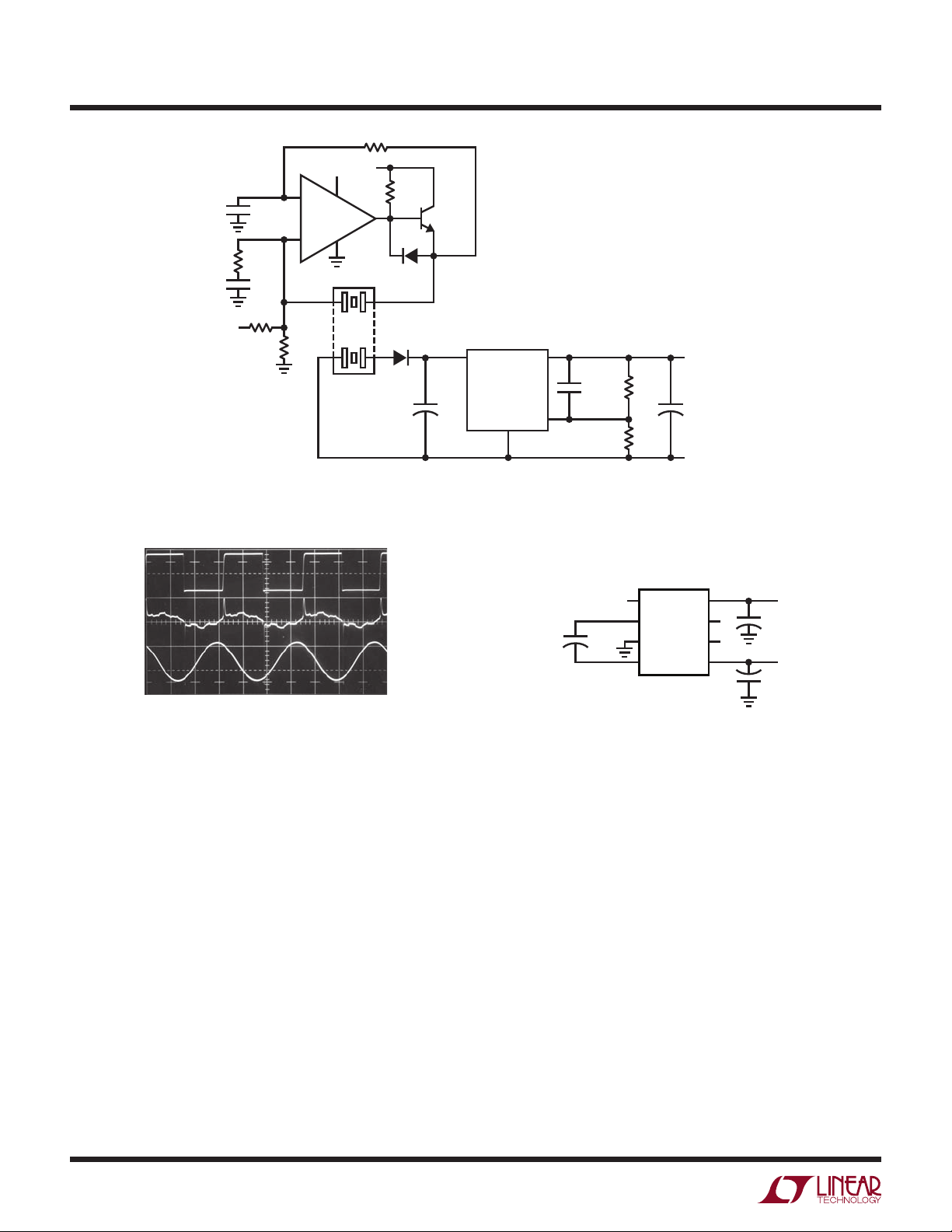

A1 is set up as a 16kHz Wein bridge oscillator. The single

power supply requires biasing to prevent A1’s output from

saturating at the ground rail. This bias is established by

returning the undriven end of the Wein network to a DC

potential derived from the LT1009 reference. A1’s output

is a pure sine wave (Figure 5, Trace A) biased off ground.

A1’s gain must be controlled to maintain sine wave output.

A2 does this by comparing A1’s rectifi ed and fi ltered positive output peaks with an LT1009 derived DC reference.

A2’s output, biasing Q1, servo controls A1’s gain. The

0.22μF capacitor frequency compensates the loop, and the

thermally mated diodes minimize errors due to rectifi er

temperature drift. These provisions fi x A1’s AC and DC

output terms against supply and temperature changes.

A1’s output is AC coupled to A3. The 2k –820Ω divider

re-biases the sine wave, centering it inside A3’s input

common mode range even with supply shifts. A3 drives a

power stage, Q2-Q5. The stages common emitter outputs

and biasing permit 1V

at V

= 4.5V. At full converter output loading the

SUPPLY

RMS

(3V

) transformer drive, even

P-P

stage delivers 3 ampere peaks but the waveform is clean

(Trace B), with low distortion (Trace C). The 330μF coupling

capacitor strips DC and L3 sees pure AC. Feedback to A3 is

taken at the Q4-Q5 collectors. The 0.1μF unit at this point

suppresses local oscillations. L3’s secondary RC network

adds additional high frequency damping.

HORIZ = 5μs/DIV

Figure 3. Output Noise of the Low Noise 5V to ±15V Converter.

Appendix H Shows a Modern IC Low Noise Regulator

AN29 F03

Ultralow Noise 5V to ±15V Converter

Residual switching components and regulator noise set

Figure 1’s performance limits. Analog circuitry operating

at the very highest levels of resolution and sensitivity may

require the lowest possible converter noise. Figure 4’s

converter uses sine wave transformer drive to reduce

harmonics to negligible levels. The sine wave transformer

drive combines with special output regulators to produce

Without control of quiescent current the power stage

will encounter thermal runaway and destroy itself. A4

measures DC output current across Q5’s emitter resistor

and servo controls Q6 to fi x quiescent current. A divided

portion of the LT1009 reference sets the servo point at

A4’s negative input and the 0.33μF feedback capacitor

stabilizes the loop.

L3’s rectifi ed and fi ltered outputs are applied to regulators

designed for low noise. A5 and A7 amplify the LT1021’s

fi ltered 10V output up to 15V. A6 and A8 provide the –15V

output. The LT1021 and amplifi ers give better noise performance than three terminal regulators. The Zener-resistor

network clips overvoltages due to start-up transients.

an32f

AN29-3

Page 4

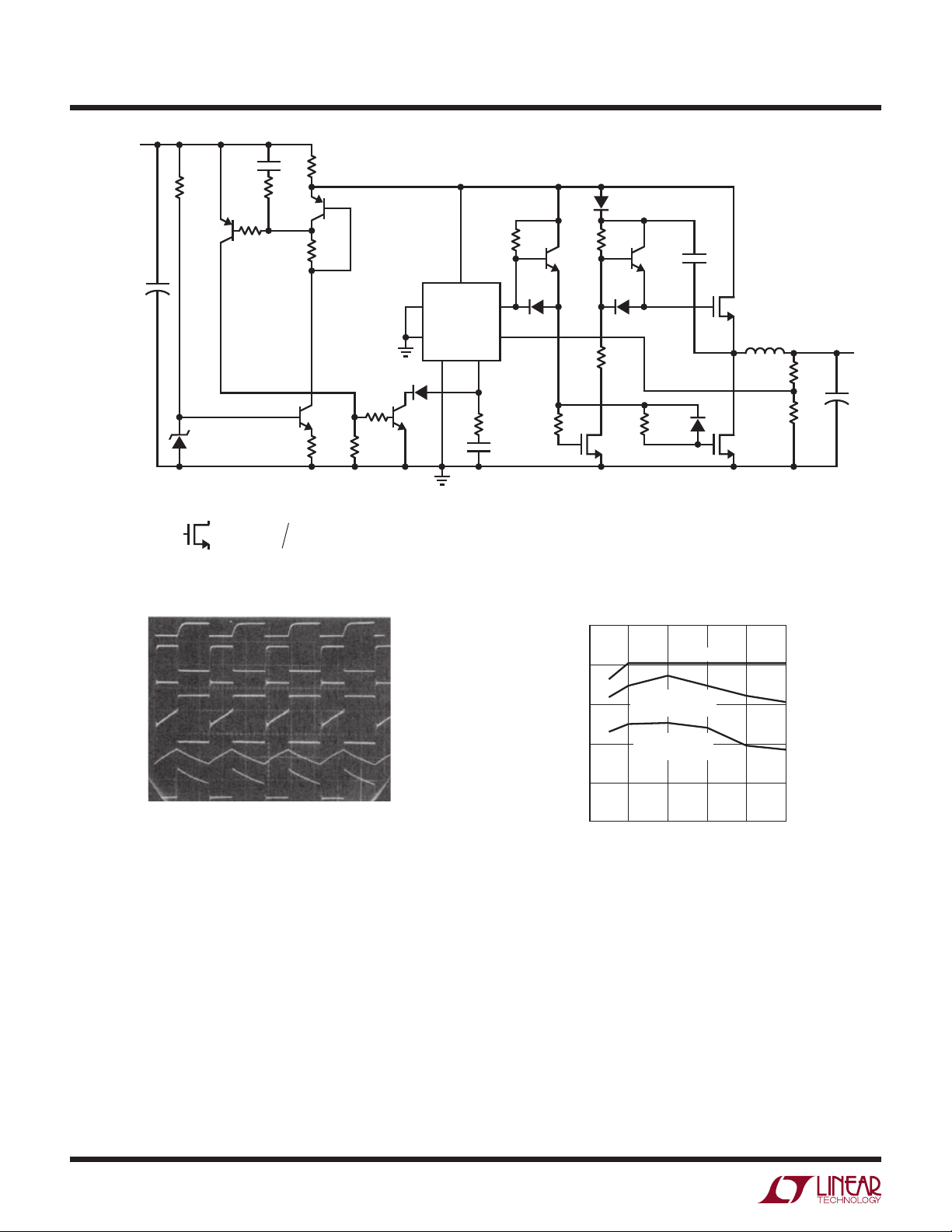

Application Note 29

OUT

15V

L1

25μH

+

47μF

A7

LT1010

IN

5V

(4.5V TO 5.5V)

4.99k*

A5

–

1/2 LT1013

10k*

22μF

+

L4

100μH

Q4

+

22μF

1N4001

68Ω

AMP

POWER

430Ω

8

+

1μF

MJE2955

50Ω

Q2

OUT

5k

†

330μF

0.1

2N2219

0.1

LT1021

L3

+

OUT

10V

IN

330Ω

534

8

0.1

50Ω

Q3

COMMON

19V

UNREG

*

*

0.005

Q5

MJE3055

2N2905

220μF

+

*

*

1

100Ω

330Ω 10k*

1N4001

Q6

0.1Ω

220μF

10k

1k750Ω*

10k*

1N5260B

+

–19V

UNREG

0.22

+

47μF

OUT

–15V

L2

25μH

A8

LT1010

4

A6

–

1/2 LT1013

620Ω

Q

I

LOOP

CONTROL

10k

–

+

A4

1/2 LT1013

0.33

AN29 F04

0.1

+

20k

0.01

LT1006

270Ω

–

1k*

(SELECTED

VALUE—

SEE TEXT)

430Ω

5V

1k

LT1009

2.5

MATED

THERMALLY

200k

–

0.22

2k

Q1

1/2 LT1013

A2

+

OSCILLATOR

10k

STAB. LOOP

3.1k

= 1N4148

= 1N4934

L1, L2 = PULSE ENGINEERING, INC. #PE-92100

L3 = PULSE ENGINEERING, INC. #PE-65064

*

L4 = PULSE ENGINEERING, INC. #PE-92108

= THF337K006P1G

UNMARKED NPN = 2N3904

* = 1% METAL FILM RESISTOR

†

= +5 GROUND

= ±15 COMMON

Figure 4. Ultralow Noise Sine Wave Drive 5V to ±15V Converter

an32f

220Ω

8

A3

+

820Ω

2k

5V

1μF

+

10k

A1

LT1006

47μF

0.22

680Ω

–

220Ω

0.01

8

+

1k

16kHz

OSCILLATOR

1k

+

1k

AN29-4

Page 5

A = 2V/DIV

B = 2V/DIV

C = 1% DISTORTION

D = 20μV/DIV

HORIZ = 50μs/DIV

Figure 5. Waveforms for the Sine Wave Driven Converter.

Note that Output Noise (Trace D) is Only 30μV

AN29 F05

P-P

L1 and L2 combine with their respective output capacitors to aid low noise characteristics. These inductors are

outside the feedback loop, but their low copper resistance

does not signifi cantly degrade regulation. Trace D, the 15V

output at full load, shows less than 30μV (2ppm) of noise.

The most signifi cant trade-off in this design is effi ciency.

The sine wave transformer drive forces substantial power

loss. At full output (75mA), effi ciency is only 30%.

Before use, the circuit should be trimmed for lowest

distortion (typically 1%) in the sine wave delivered to

L3. This trim is made by selecting the indicated value at

A1’s negative input. The 270Ω value shown is nominal,

with a typical variance of ±25%. The sine wave’s 16kHz

frequency is a compromise between the op amps available gain bandwidth, magnetics size, audible noise, and

minimization of wideband harmonics.

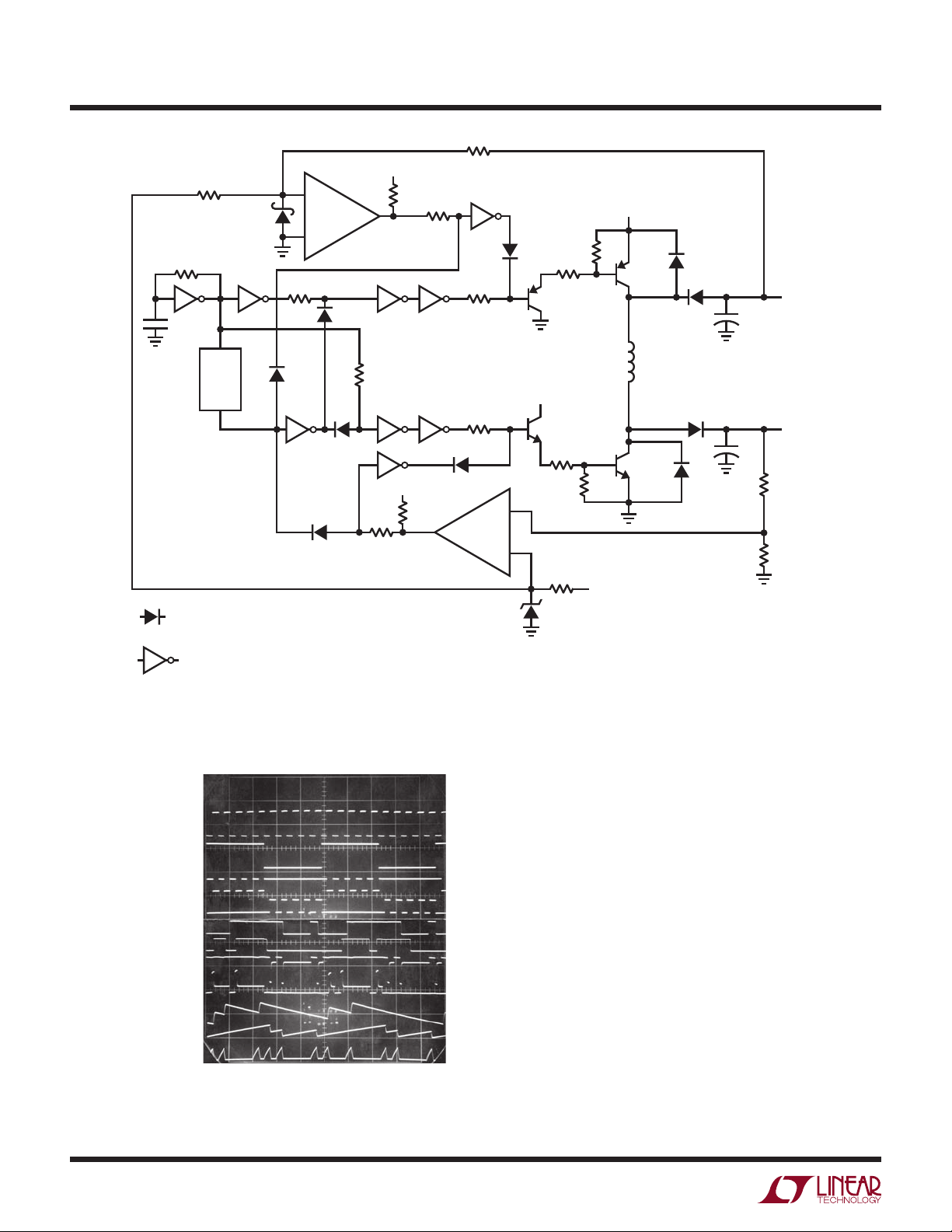

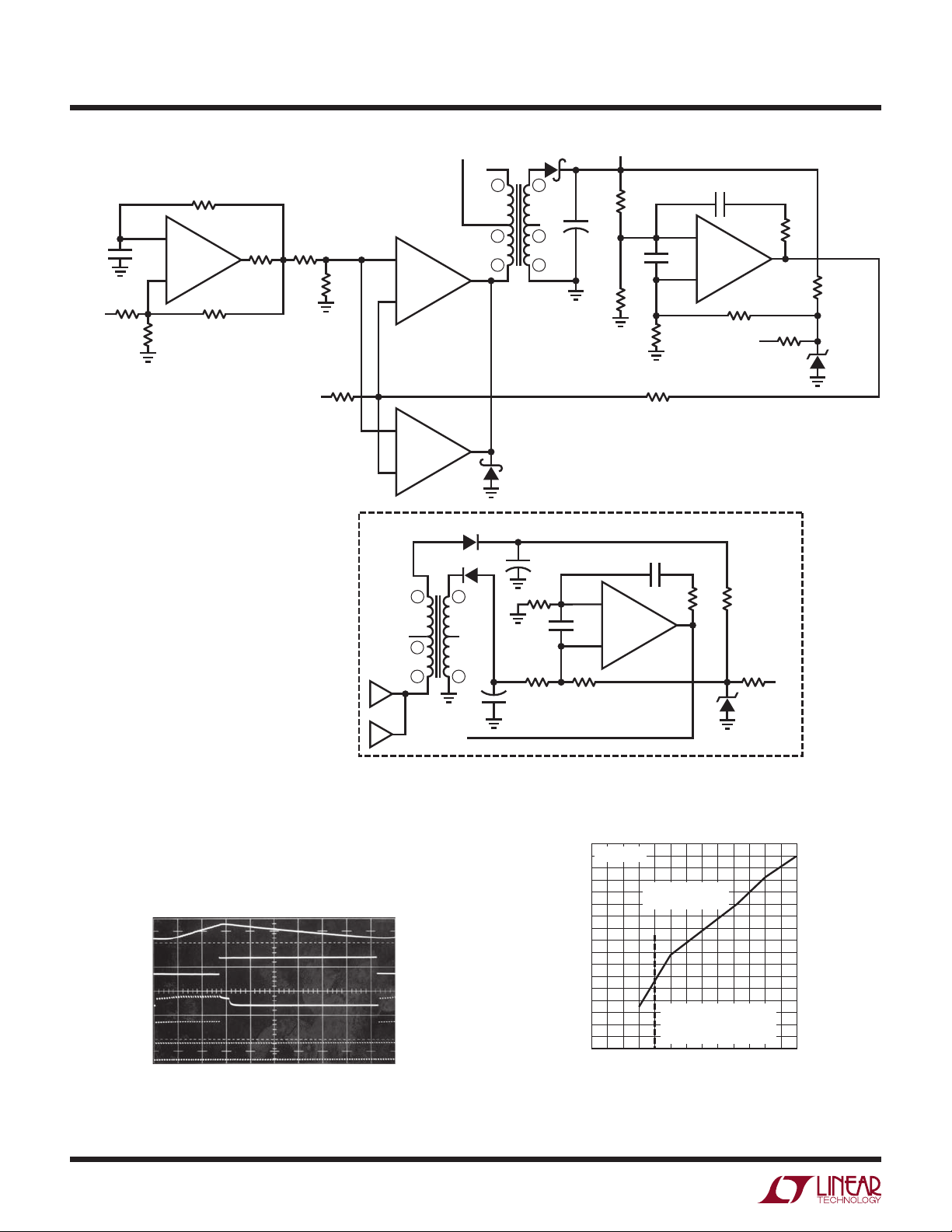

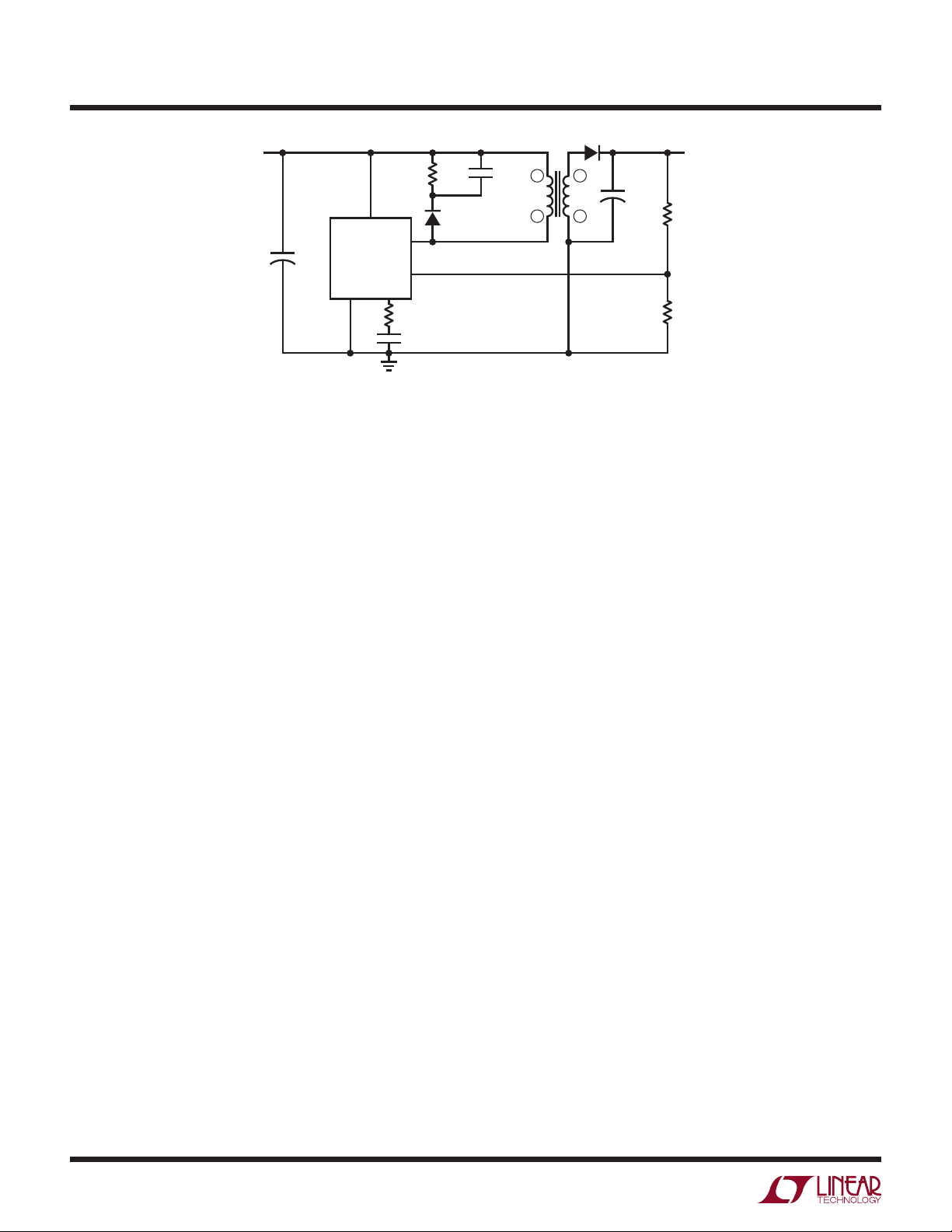

Single Inductor 5V to ±15V Converter

Simplicity and economy are another dimension in 5V to

±15V conversion. The transformer in these converters is

usually the most expensive component. Figure 6’s unusual

drive scheme allows a single, 2-terminal inductor to replace

the usual transformer at signifi cant cost savings. Tradeoffs include loss of galvanic isolation between input and

output and lower power output. Additionally, the regulation

technique employed causes about 50mV of clock related

output ripple.

The circuit functions by periodically and alternately allowing

each end of the inductor to fl yback. The resultant positive

and negative peaks are rectifi ed and fi ltered. Regulation

is obtained by controlling the number of fl yback events

during the respective output’s fl yback interval.

Application Note 29

The leftmost logic inverter produces a 20kHz clock (Trace A,

Figure 7) which feeds a logic network composed of additional inverters, diodes and the 74C90 decade counter. The

counter output (Trace B) combines with the logic network

to present alternately phased clock bursts (Traces C andD)

to the base resistors of Q1 and Q2. When φ1 (Trace B)

is unclocked it resides in its high state, biasing Q2 and

Q4 on. Q4’s collector effectively grounds the “bottom” of

L1 (TraceH). During this interval φ2 (Trace A) puts clock

bursts into Q1’s base resistor. If the –15V output is too

low servo comparator C1A’s output (Trace E) is high, and

Q1’s base can receive pulsed bias. If the converse is true

the comparator will be low, and the bias gated away via

Q1’s base diode. When Q1 is able to bias, Q3 switches,

resulting in negative going fl yback events at the “top” of

L1 (Trace G). These events are rectifi ed and fi ltered to

produce the –15V output. C1A regulates by controlling

the number of clock pulses that switch the Q1-Q3 pair.

The LT1004 serves as a reference. Trace J, the AC-coupled

–15V output, shows the effect of C1A’s regulating action.

The output stays within a small error window set by C1A’s

switched control loop. As input voltage and loading conditions change C1A adjusts the number of clock pulses

allowed to bias Q1-Q3, maintaining loop control.

When the φ1 and φ2 signals reverse state the operating

sequence reverses. Q3’s collector (Trace G) is pulled high

with Q2-Q4 switching controlled by C1B’s servo action.

Operating waveforms are similar to the previous case.

Trace F is C1B’s output, Trace H is Q4’s collector (L1’s “bottom”) and Trace I is the AC-coupled 15V output. Although

the two regulating loops share the same inductor they

operate independently, and asymmetrical output loading is

not deleterious. The inductor sees irregularly spaced shots

of current (Trace K), but is unaffected by its multiplexed

operation. Clamp diodes prevent reverse biasing of Q3

and Q4 during transient conditions. The circuit provides

±25mA of regulated power at 60% effi ciency.

Low Quiescent Current 5V to ±15V Converter

A fi nal area in 5V to ±15V converter design is reduction

of quiescent current. Typical units pull 100mA to 150mA

of quiescent current, unacceptable in many low power

systems.

an32f

AN29-5

Page 6

Application Note 29

150k*

12.4k*

HP5082-2810

32k

1000pF

5

74C90

÷10

12

= 1N4148

* = 1% METAL FILM RESISTOR

= 74C14

+

1/2 LT1018

–

10k

C1A

10k

10k

5V

300Ω

10k

100Ω

K2

4.7k

K1

4.7k

5V

300Ω

C1B

1/2 LT1018

Q1

2N3906

5V

Q2

2N3904

100Ω

+

–

1k

LT1004

1.2V

5V

2k

Q3

2N5023

–15V

15V

137k*

12.4k*

AN29 F06

OUT

OUT

+

100

L1

145μH

+

Q4

2N3507

2k

5V

100

L1 = PULSE ENGINEERING, INC. # PE-92105

Figure 6. Single Inductor 5V to ±15V Regulated Converter

A = 5V/DIV

B = 5V/DIV

C = 10V/DIV

D = 10V/DIV

E = 10V/DIV

F = 10V/DIV

G = 20V/DIV

H = 20V/DIV

I = 0.05V/DIV (AC-COUPLED)

J = 0.05V/DIV (AC-COUPLED)

K = 1A/DIV

HORIZ = 100μs/DIV

Figure 7. Waveforms for the Single Inductor, Dual-Output,

Regulated Converter

AN29 F07

Figure 8’s design supplies ±15V outputs at 100mA while

consuming only 10mA quiescent current. The LT1070

switching regulator (for a complete description of this

device, see Appendix C, “Physiology of the LT1070”) drives

L1 in fl yback mode. A damper network clamps excessive

fl yback voltages. Flyback events at L1’s secondary are

half-wave rectifi ed and fi ltered, producing positive and

negative outputs across the 47μF capacitors. The positive

16V output is regulated by a simple loop. Comparator

C1A balances a sample of the positive output with a 2.5V

reference obtained from the LT1020. When the 16V output (Trace A, Figure 9) is too low, C1A switches (TraceB)

high, turning off the 4N46 opto-isolator. Q1 goes off, and

the LT1070’s control pin (V

causes full duty cycle 40kHz switching at the V

) pulls high (Trace C). This

C

pin

SW

(Trace D). The resultant energy into L1 forces the 16V

output to ramp quickly positive, turning off C1A’s output.

an32f

AN29-6

Page 7

5V

IN

(4.5V TO 5.5V)

Application Note 29

16V PRE-REG

0.47

V

GND

10k

1 9

3 7

SW

1.2k

2W

MUR120

V

IN

NC

2N3906

LT1070FB

V

C

Q1

L1 = PULSE ENGINEERING, INC. # PE-61592

* = 1% FILM RESISTOR

= +5 GROUND

= ±15 COMMON

1N4148

L1

+

8

+

1N4148

5V

4N46

390k

47μF

47μF

1.2M*

82k

216k*

–

C1A

1/2 LT1017

+

20M

10k

–16V UNREG

10k

0.002

UPDATE

Burst Mode regulators

can achieve lower I

Figure 8. Low I

, Isolated 5V to ±15V Converter

Q

Q

9

3

V

GND

–1N

5

COMP

PNP

0.001μF

3M* 500k* 100k

470k

IN

LT1070

2.5V

+IN

REF OUT

74 6

Q2

VN2222

OPTIONAL

(SEE TEXT)

28

OUT

11

FB

COMP

NPN

–16V UNREG

–15V

15V

OUT

2.5M*

0.001μF

100mA

+

500k*

10μF

+

10μF

–15V

OUT

100mA

TO

REF OUT

470k

3.2M

1.5M

–

1/2 LT1017

+

47k

C1B

TO

TO

TO 16V

PRE-REG

1.5k

5.6M

AN29 F08

A = 100mV/DIV

(AC-COUPLED ON

LEVEL)

16V

DC

B = 20V/DIV

C = 2V/DIV

D = 20V/DIV

HORIZ = 5ms/DIV

AN29 F09

Figure 9. Waveforms for the Low IQ 5V to ±15V Converter

The 20M value combined with the 4N46’s slow response

(note the delay between C1A going high and the V

pin

C

rise) gives about 40mV of hysteresis. The LT1070’s onoff duty cycle is load dependent, saving signifi cant power

when the converter is lightly loaded. This characteristic

is largely responsible for the 10mA quiescent current.

The opto-isolator preserves the converters input-output

isolation. The LT1020, a low quiescent current regulator

with low dropout, further regulates the 16V line, giving

the 15V output. The linear regulation eliminates the 40mV

ripple and improves transient response. The –16V output

tends to follow the regulated –16V line, but regulation

is poor. The LT1020’s auxiliary onboard comparator is

compensated to function as an op amp by the RC damper

at Pin 5. This amplifi er linearly regulates the –16V line.

MOSFET Q2 provides low dropout current boost, sourcing

the –15V output. The –15V output is stabilized with the

op amp by comparing it with the 2.5V reference via the

500k-3M current summing resistors. 1000pF capacitors

frequency compensate each regulating loop. This converter

functions well, providing ±15V outputs at 100mA with

only 10mA quiescent current. Figure 10 plots effi ciency

versus a conventional design over a range of loads. For

high loads results are comparable, but the low quiescent

circuit is superior at lower current.

A possible problem with this circuit is related to the poor

regulation of the –16V line. If the positive output is lightly

loaded L1’s magnetic fl ux is low. Heavy negative output

loading under this condition results in the –16V line falling

below its output regulators dropout value. Specifi cally, with

no load on the 15V output only 20mA is available from

the –15V output. The full 100mA is only available from

an32f

AN29-7

Page 8

Application Note 29

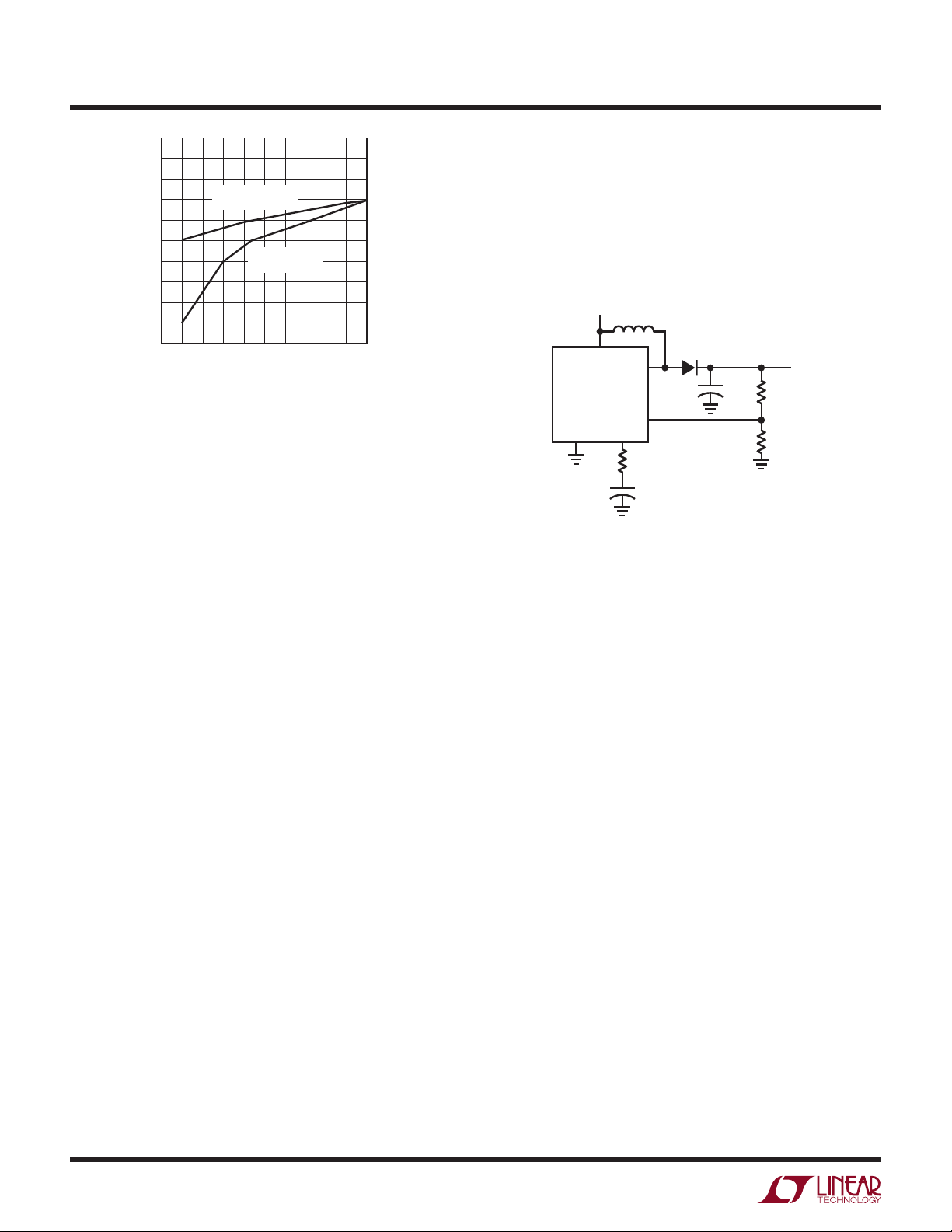

100

90

80

70

60

50

40

EFFICIENCY (%)

30

20

10

0

0

LOW QUIESCENT

CURRENT DESIGN

CONVENTIONAL

DESIGN

2010

4030

50

OUTPUT CURRENT (mA)

60 70 90

80

100

AN29 F10

Figure 10. Effi ciency vs Load for the Low IQ Converter

the –15V output when the 15V output is supplying more

than 8mA. This restriction is often acceptable, but some

situations may not tolerate it. The optional connection in

Figure 8 (shown in dashed lines) corrects the diffi culty.

C1B detects the onset of –16V line decay. When this occurs its output pulls low, loading the 16V line to correct

the problem. The biasing values given permit correction

before the negative linear regulator drops out.

MICROPOWER QUIESCENT CURRENT CONVERTERS

Many battery-powered applications require very wide

ranges of power supply output current. Normal conditions

require currents in the ampere range, while standby or

“sleep” modes draw only microamperes. A typical laptop

computer may draw 1 to 2 amperes running while needing only a few hundred microamps for memory when

turned off. In theory, any DC/DC converter designed

for loop stability under no-load conditions will work. In

practice, a converter’s relatively large quiescent current

may cause unacceptable battery drain during low output

current intervals.

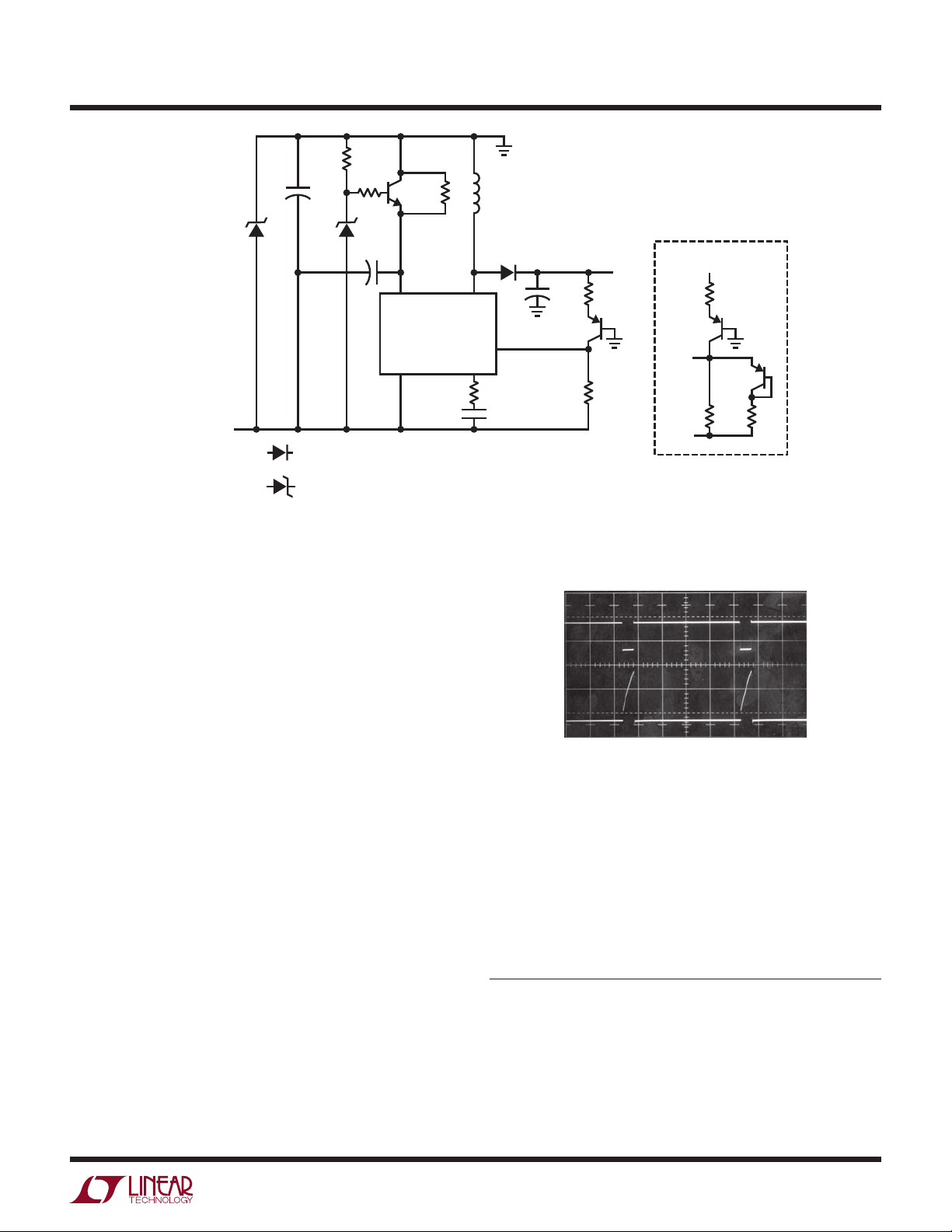

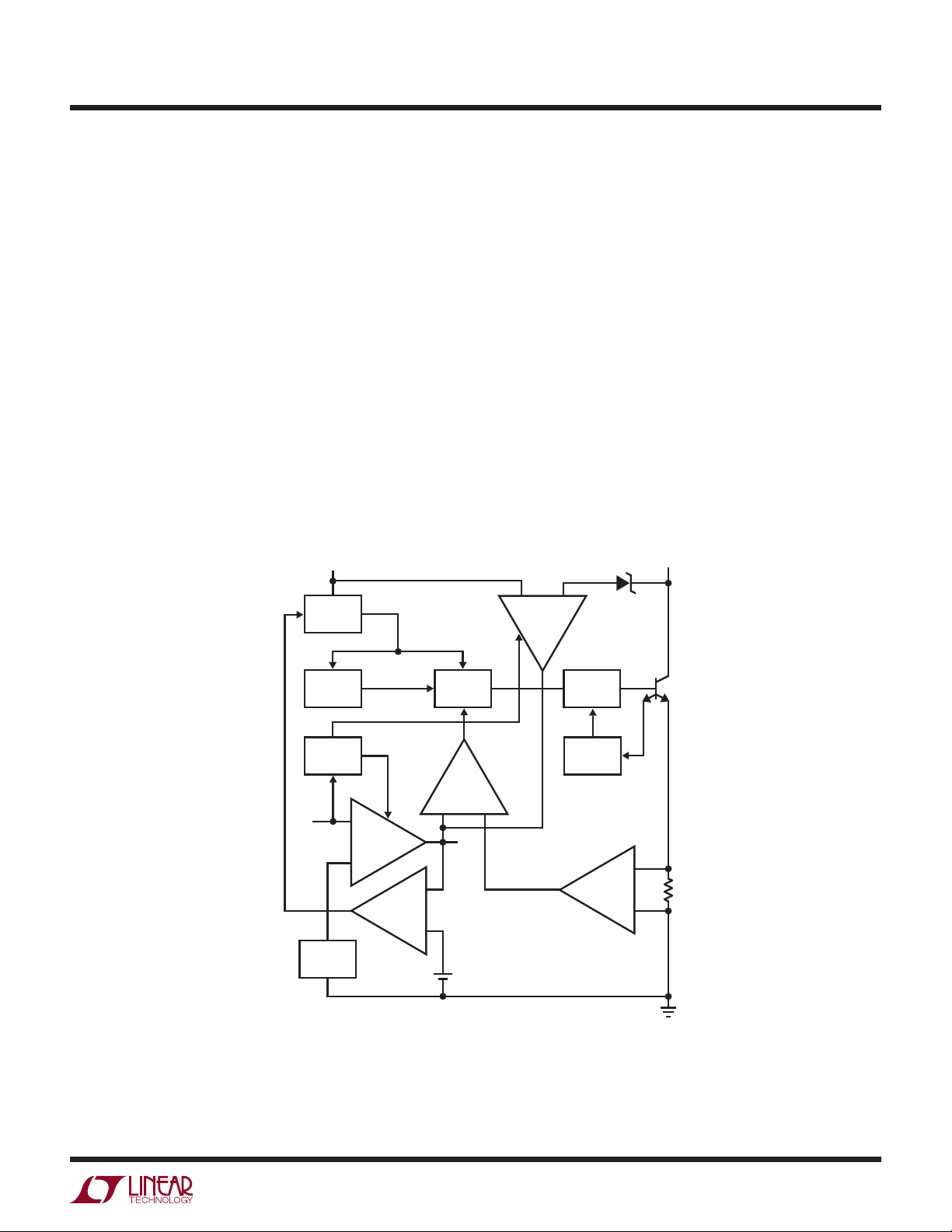

Figure 11 shows a typical fl yback based converter. In this

case the 6V battery is converted to a 12V output by the

inductive fl yback voltage produced each time the LT1070’s

pin is internally switched to ground (for commentary

V

SW

on inductor selection in fl yback converters see Appendix D,

“Inductor Selection for Flyback Converters”). An internal

40kHz clock produces a fl yback event every 25μs. The

energy in this event is controlled by the IC’s internal error amplifi er, which acts to force the feedback (FB) pin to

a 1.23V reference. The error amplifi ers high impedance

output (the VC pin) uses an RC damper for stable loop

compensation.

This circuit works well but pulls 9mA of quiescent current.

If battery capacity is limited by size or weight this may be

too high. How can this fi gure be reduced while retaining

high current performance?

V

IN

L1*

6V

50μH

V

IN

LT1070

GND V

+

MUR8100

V

SW

FB

C

1k

1μF

+

470μF

*PULSE ENGINEERING, INC

#PE-51515

10.7k

1.24k

AN29 F11

V

12V

OUT

Figure 11. 6V to 12V, 2 Amp Converter with 9mA Quiescent Current

A solution is suggested by considering an auxiliary V

function. If the V

pin is pulled within 150mV of ground the

C

pin

C

IC shuts down, pulling only 50 microamperes. Figure 12’s

special loop exploits this feature, reducing quiescent current to only 150 microamperes. The technique shown is

particularly signifi cant, with broad implication in battery

powered systems. It is easily applied to a wide variety of

DC/DC converters, meeting an acknowledged need across

a wide spectrum of applications.

Figure 12’s signal fl ow is similar to Figure 11, but additional

circuitry appears between the feedback divider and the V

C

pin. The LT1070’s internal feedback amplifi er and reference

are not used. Figure 13 shows operating waveforms under

no-load conditions. The 12V output (Trace A) ramps down

over a period of seconds. During this time comparator

A1’s output (Trace B) is low, as are the 74C04 paralleled

inverters. This pulls the V

IC in its 50μA shutdown mode. The V

pin (Trace C) low, putting the

C

pin (Trace D) is

SW

high, and no inductor current fl ows. When the 12V output

drops about 20mV, A1 triggers and the inverters go high,

pulling the V

pin pulses the inductor at the 40kHz clock rate, caus-

V

SW

pin up and turning on the regulator. The

C

ing the output to abruptly rise. This action trips A1 low,

forcing the V

pin back into shutdown. This “bang-bang”

C

control loop keeps the 12V output within the 20mV ramp

an32f

AN29-8

Page 9

+

6V

IN

(4.5V TO 8V)

47μF

L1

50μH

V

SW

LT1070

V

GND

C

R6

200Ω

+

C2

47μF

MUR405

FB NC

3.6M*

Application Note 29

–

A2

1/2 LT1017

+

1.2M*

+

C1

2700μF

6V

A1

1/2 LT1017

–

+

“LOW BATT”

R3

2M

12V

R1

1M*R7100k

R2

120k*

OUT

C3

1500pF

UPDATE

Micropower regulators using

Burst Mode operation are available

10pF**

** = OPTIONAL. SEE TEXT

= 1N4148

* = 1% METAL FILM RESISTOR

= 74C04

L1 = PULSE ENGINEERING, INC. # PE-51515

Figure 12. 6V to 12V, 2 Amp Converter with 150μA Quiescent Current

hysteresis window set by R3-R4. Diode clamps prevent

pin overdrive. Note that the loop oscillation period of

V

C

4 to 5 seconds means the R6-C2 time constant at V

C

is

not a signifi cant term. Because the LT1070 spends almost

all of the time in shutdown, very little quiescent current

(150μA) is drawn.

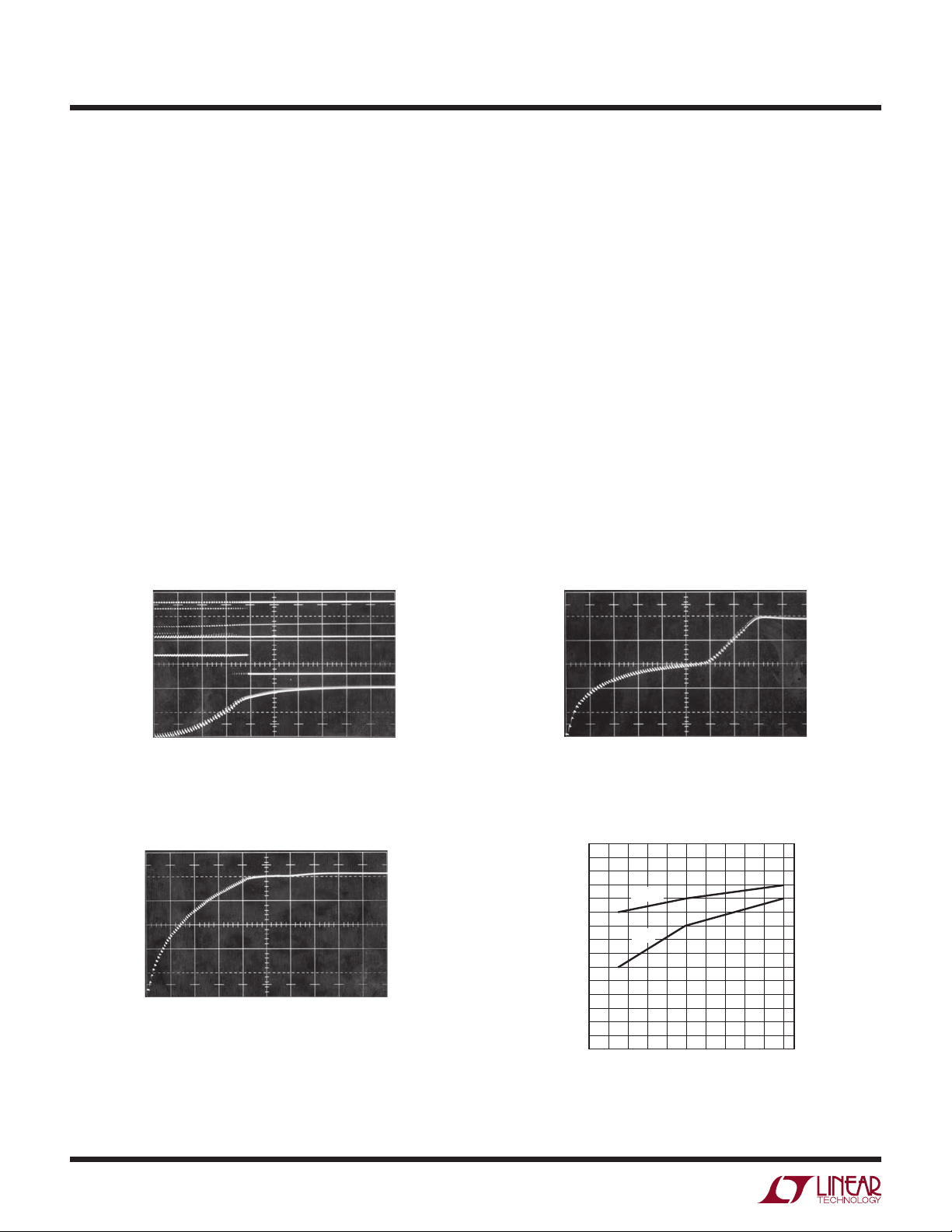

Figure 14 shows the same waveforms with the load increased to 3mA. Loop oscillation frequency increases to

keep up with the loads sink current demand. Now, the V

C

pin waveform (Trace C) begins to take on a fi ltered appearance. This is due to R6-C2’s 10ms time constant. If

R4

10k

AN29 F12

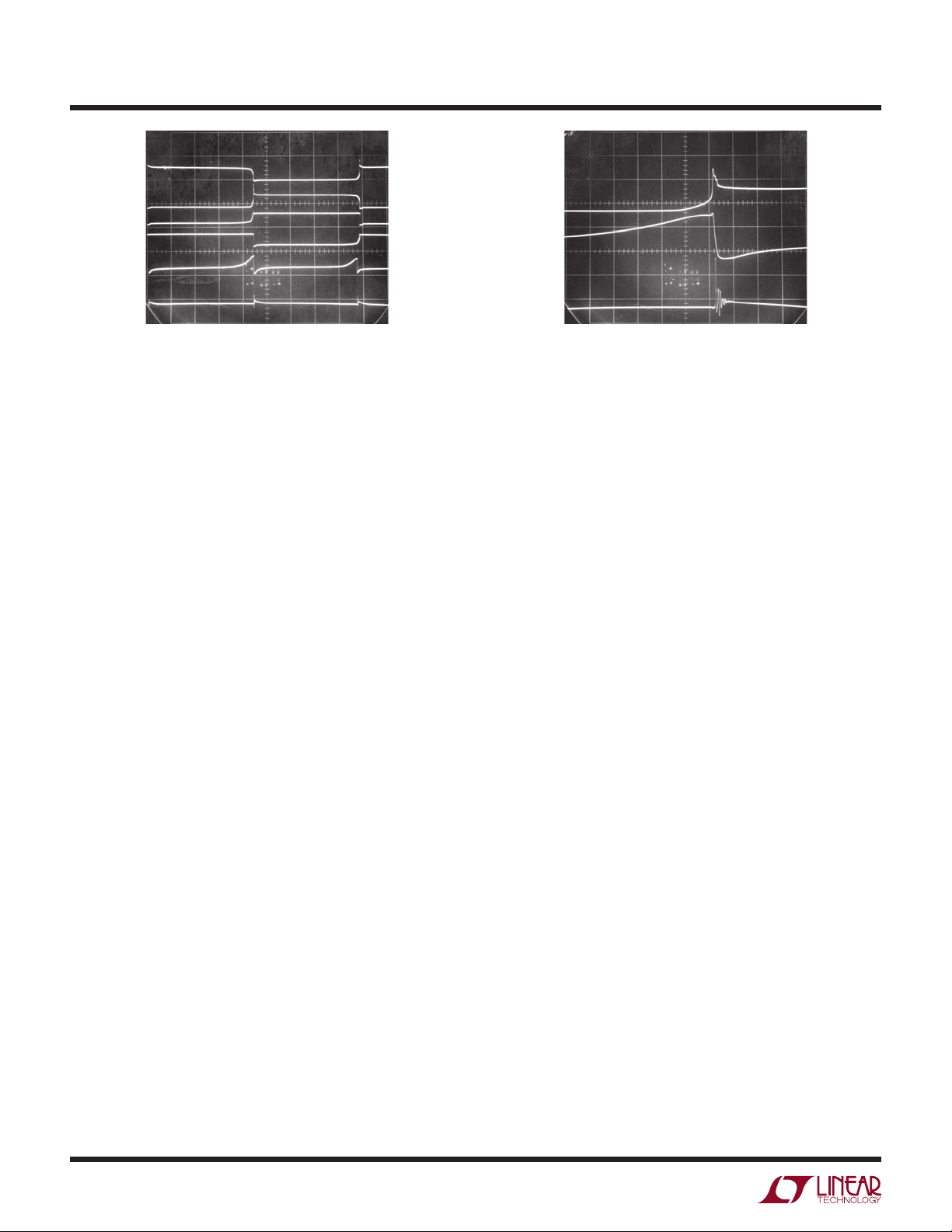

A = 0.02V/DIV

(AC-COUPLED)

B = 5V/DIV

C = 2V/DIV

D = 10V/DIV

R5

180k

LT1004

1.2V

6V

Figure 13. Low I

HORIZ = 1s/DIV

Converter Waveforms with No Load

Q

(Traces B and D Retouched for Clarity)

AN29 F13

an32f

AN29-9

Page 10

Application Note 29

the load continues to increase, loop oscillation frequency

will also increase. The R6-C2 time constant, however,

is fi xed. Beyond some frequency, R6-C2 must average

loop oscillations to DC. Figure 15 shows the same circuit

points at 1 ampere loading. Note that the VC pin is at DC,

and repetition rate has increased to the LT1070’s 40kHz

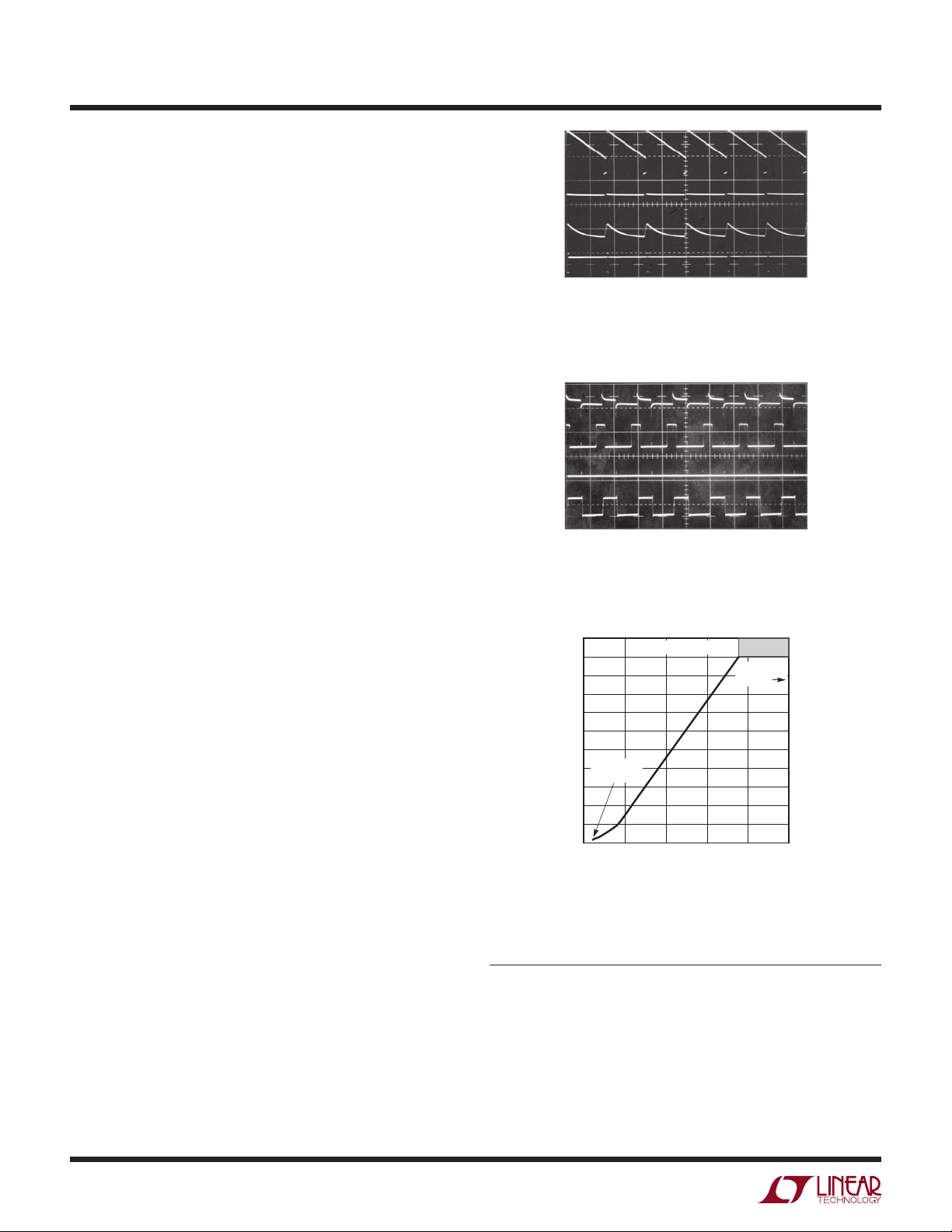

clock frequency. Figure 16 plots what is occurring, with

a pleasant surprise. As output current rises, loop oscillation frequency also rises until about 500Hz. At this point

the R6-C2 time constant fi lters the V

LT1070 transitions into “normal” operation. With the V

pin to DC and the

C

C

pin at DC it is convenient to think of A1 and the inverters as a linear error amplifi er with a closed-loop gain set

by the R1-R2 feedback divider. In fact, A1 is still duty

cycle modulating, but at a rate far above R6-C2’s break

frequency. The phase error contributed by C1 (which was

selected for low loop frequency at low output currents) is

dominated by the R6-C2 roll off and the R7-C3 lead into

A1. The loop is stable and responds linearly for all loads

beyond 80mA. In this high current region the LT1070 is

desirably “fooled” into behaving like Figure 11’s circuit.

A formal stability analysis for this circuit is quite complex,

but some simplifi cations lend insight into loop operation.

At 100μA loading (120kΩ) C1 and the load form a decay

time constant exceeding 300 seconds. This is orders of

magnitude larger than R7-C3, R6-C2, or the LT1070’s

40kHz commutation rate. As a result, C1 dominates the

loop. Wideband A1 sees phase shifted feedback, and very

1

low frequency oscillations similar to Figure 13’s occur

.

Although C1’s decay time constant is long, its charge

time constant is short because the circuit has low sourcing impedance. This accounts for the ramp nature of the

oscillations.

Increased loading reduces the C1 load decay time constant. Figure 16’s plot refl ects this. As loading increases,

the loop oscillates at a higher frequency due to C1’s decreased decay time. When the load impedance becomes

low enough C1’s decay time constant ceases to dominate

the loop. This point is almost entirely determined by R6

and C2. Once R6 and C2 “take over” as the dominant time

constant the loop begins to behave like a linear system.

In this region (e.g. above about 75mA, per Figure 16) the

LT1070 runs continuously at its 40kHz rate. Now, the R7C3 time constant becomes signifi cant, performing as a

2

simple feedback lead

to smooth output response. There is

A = 0.02V/DIV

(AC-COUPLED)

B = 5V/DIV

C = 2V/DIV

D = 10V/DIV

HORIZ = 20ms/DIV

AN29 F14

Figure 14. Low IQ Converter Waveforms at Light Loading

A = 0.02V/DIV

B = 5V/DIV

C = 2V/DIV

D = 10V/DIV

AN29 F15

2.5A

80

100

AN29 F16

Figure 15. Low I

550

500

450

400

350

300

250

IQ = 150μA

200

150

LOOP FREQUENCY (Hz)

100

50

0

0

HORIZ = 20μs/DIV

Converter Waveforms at 1 Amp Loading

Q

LINEAR REGION

EXTENDS TO

0.2Hz

20

OUTPUT (mA)

60

40

Figure 16. Figure 12’s Loop Frequency vs Output Current.

Note Linear Loop Operation Above 80mA

1

Some layouts may require substantial trace area to A1’s inputs. In such

cases the optional 10pF capacitor shown ensures clean transitions at A1’s

output.

2

“Zero Compensation” for all you technosnobs out there.

AN29-10

an32f

Page 11

A = 10V/DIV

B = 0.1V/DIV

(AC-COUPLED)

HORIZ = 5ms/DIV

Figure 17. Load Transient Response for Figure 12’s

Low IQ Regulator

AN29 F17

Application Note 29

3

constant decay

is visible as Trace B approaches steady state between the

4th and 5th vertical divisions.

A2 functions as a simple low-battery detector, pulling low

when V

drops below 4.8V.

IN

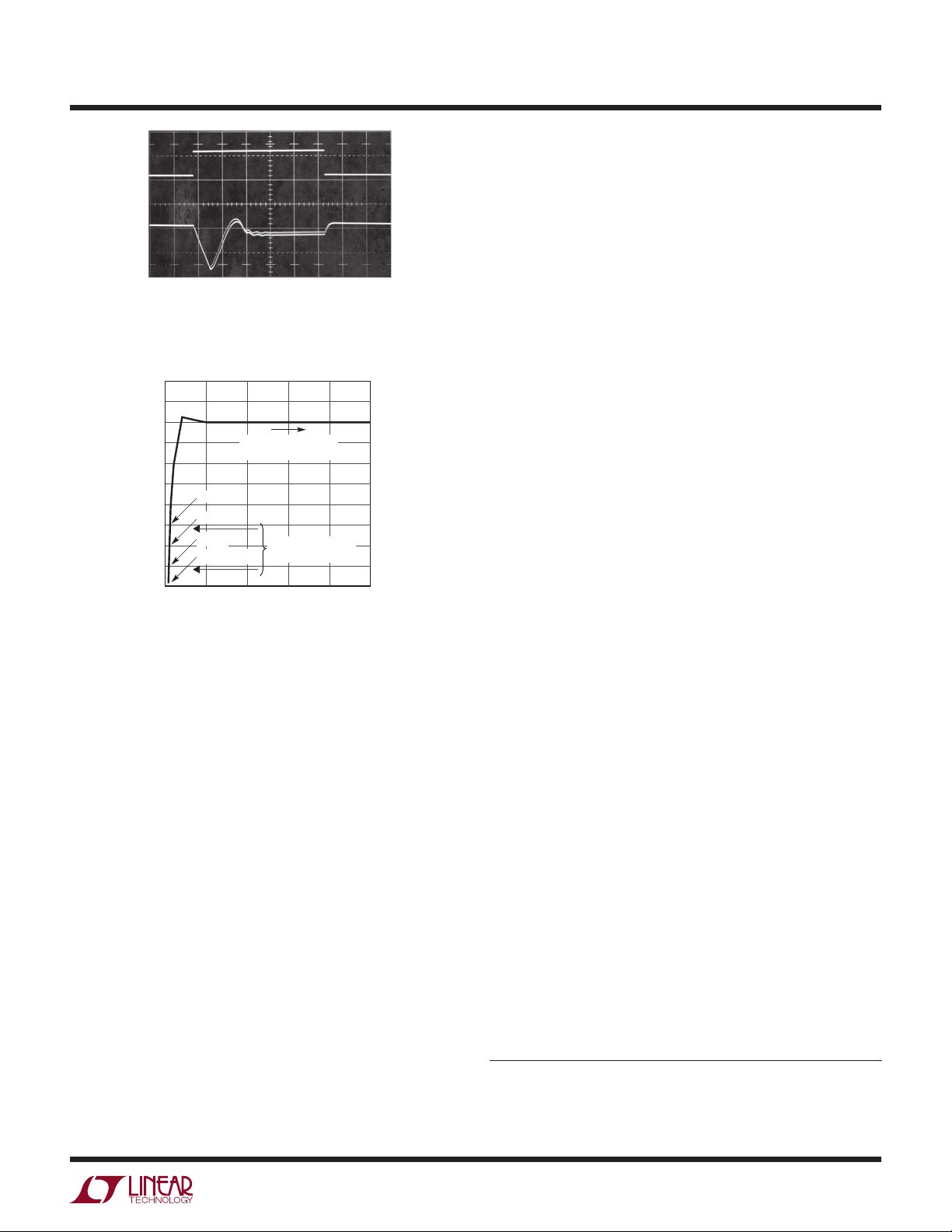

Figure 18 plots effi ciency versus output current. High

power effi ciency is similar to standard converters. Low

power effi ciency is somewhat better, although poor in

the lowest ranges. This is not particularly bothersome,

as power loss is very small.

(“rattling” is perhaps more appropriate)

100

90

80

70

60

50

40

EFFICIENCY (%)

30

20

10

0

0

Figure 18. Effi ciency vs Output Current for Figure 12.

Standby Effi ciency is Poor, But Power Loss Approaches

Battery Self Discharge

TYPICAL OPERATING

15mA

3mA

650μA

IQ = 150μA

0.5

1

OUTPUT CURRENT (A)

REGION

TYPICAL STANDBY

REGION

1.5

2

2.5

AN29 F18

a fundamental trade-off in the selection of the R7-C3 lead

network values. When the converter is running in its linear

region they must dominate the DC hysteresis deliberately

generated by R3-R4. As such, they have been chosen for

the best compromise between output ripple at high load

and loop transient response.

This loop provides a controlled, conditional instability

instead of the more usually desirable (and often elusive)

unconditional stability. This deliberately introduced characteristic lowers converter quiescent current by a factor of

60 without sacrifi cing high power performance. Although

demonstrated in a boost converter, it is readily exportable

to other confi gurations. Figure 19a’s step-down (buck

mode) confi guration uses the same basic loop with almost

no component changes. P-channel MOSFET Q1 is driven

from the LT1072 (a low power version of the LT1070) to

convert 12V to a 5V output. Q2 and Q3 provide current

limiting, while Q4 supplies turn off drive to Q1. the lower

output voltage mandates slightly different hysteresis biasing than Figure 12, accounting for the 1MΩ value at the

comparators positive input. In other respects the loop and

its performance are identical. Figure 19b uses the loop in

a transformer based multi-output converter. Note that the

fl oating secondaries allow a –12V output to be obtained

with a positive voltage regulator.

Low Quiescent Current Micropower 1.5V to 5V

Converter

Despite the complex dynamics transient response is quite

good. Figure 17 shows performance for a step from no

load to 1 ampere. When Trace A goes high a 1 ampere load

appears across the output (Trace B). Initially, the output

sags almost 150mV due to slow loop response time (the

R6-C2 pair delay V

pin response). When the LT1070 comes

C

on (signaled by the 40kHz “fuzz” at the bottom extreme

of Trace B) response is reasonably quick and surprisingly

well behaved considering circuit dynamics. The multi-time

Figure 20 extends our study of low quiescent current converters into the low voltage, micropower domain. In some

circumstances, due to space or reliability considerations, it

is preferable to operate circuitry from a single 1.5V cell. This

eliminates almost all ICs as design candidates. Although

it is possible to design circuitry which runs directly from

®

a single cell (see LTC

Application Note 15, “Circuitry For

Single Cell Operation”) a DC/DC converter permits using

higher voltage ICs. Figure 20’s design converts a single

3

Once again, “multi-pole settling” for those who adore jargon.

an32f

AN29-11

Page 12

Application Note 29

12V

(8V TO 16V)

IN

0.4Ω

1k100Ω

Q2

2N3906

Q1

IRF-9531

Q4

2N3904

L1

100μH

MUR405

5V

+

2700μF

1M

1M*

OUT

1500pF

100k

+

10μF

2k

1N4148

1N4148

1N4148

L1 = PULSE ENGINEERING, INC. # PE-92108

** = OPTIONAL. SEE TEXT

* = 1% FILM RESISTOR

Q3

2N3904

= 74C04

+

V

IN

V

LT1072

C

200Ω

47μF

V

GND

SW

FB NC

10k

12V

IN

–

1/2 LT1017

+

10pF**

UPDATE

Burst Mode regulators

can achieve lower I

Q

340k*

10k 470k

LT1004

1.2V

AN29 F19a

12V

IN

Figure 19a. The Low Quiescent Current Loop Applied to a Buck Converter

1.5V cell to a 5V output with only 125μA quiescent current.

Oscillator C1A’s output is a 2kHz square wave (Trace D,

Figure 21). The confi guration is conventional, except that

the biasing accommodates the narrow common mode

range dictated by the 1.5V supply. To maintain low power,

C1A’s integrating capacitor is small, with only 50mV of

swing. The parallel connected sides of C2 drive L1. When

the 5V output (Trace A) coasts down far enough C1B

goes low (Trace B), pulling both C2 positive inputs close

to ground. C1A’s clock now appears at the paralleled C2

outputs (Trace C), forcing energy into L1. The paralleled

outputs minimize saturation losses. L1’s fl yback pulses,

rectifi ed and stored in the 47μF capacitor, form the circuits

DC output. C1B on-off modulates C2 at whatever duty

cycle is required to maintain the circuits 5V output. The

LT1004 is the reference, with the resistor divider at C1B’s

positive input setting the output voltage. Schottky clamping

of C2’s outputs prevents negative going overdrives due to

parasitic L1 behavior.

AN29-12

an32f

Page 13

Application Note 29

12V

MUR120

L1

7

+

t

IN

22μF

+

4

t

2

2k

2W

0.2μF

3

8

9

MUR120

10

t

11

MBR360

5

+

+

t

L1

t

1

6

MUR120

V

GND

IN

LT1071

V

SW

V

C

+

FB NC

200Ω

C2

47μF

74C04 (5)

R6

470μF

470μF

C1

2700μF

LT1086

LT1086

1.2k

1.2k

11k

12V

IN

A1

1/2 LT1017

11k

–

+

+

10μF

12V

+

10μF

–12V

V

OUT

5V

1A

R3

R1

1M

1M*R710k

C3

0.005

R2

453k*

1N4148

L1 = PULSE ENGINEERING, INC. # PE-65108

* = 1% FILM RESISTOR

** = OPTIONAL. SEE TEXT

Figure 19b. Multi-Output, Transformer Coupled Low Quiescent Current Converter

The 1.2V LT1004 reference biasing is bootstrapped to the

5V output, permitting circuit operation down to 1.1V. A

10M bleed to supply ensures start-up. The 1M resistors

divide down the 1.2V reference, keeping C1B inside common mode limits. C1B’s positive feedback RC pair sets

about 100mV hysteresis and the 22pF unit suppresses

high frequency oscillation.

The micropower comparators and very low duty cycles at

light load minimize quiescent current. The 125μA fi gure

noted is quite close to the LT1017’s steady-state currents.

As load increases the duty cycle rises to meet the demand,

10pF**

R4

1N4148

10k

LT1004

1.2

AN29 F19b

R5

180k

12V

IN

requiring more battery power. Decrease in battery voltage

produces similar behavior. Figure 22 plots available output

current versus battery voltage. Predictably, the highest

power is available with a fresh cell (e.g., 1.5V to 1.6V),

although regulation is maintained down to 1.15V for 250μA

loading. The plot shows that the test circuit continued to

regulate below this point, but this cannot be relied on in

practice (LT1017 V

= 1.15V). The low supply voltage

MIN

makes saturation and other losses in this circuit diffi cult

to control. As such, effi ciency is about 50%.

an32f

AN29-13

Page 14

Application Note 29

3.9M

–

1.5M

150pF

3.9M

1.5V

470k

* = 1% METAL FILM RESISTOR

PNP = 2N3906

NPN = 2N3904

L1 = TRIAD # SP-29

C1A

1/2 LT1017

+

2M

240k

1.5V

150k

10M

–

C2B

1/2 LT1017

+

–

C2A

1/2 LT1017

+

V

IN

(1.1V TO 2V)

NC

1N4148

HP5082-2810

HP5082-2810

L1

5

6

HP-5082-2810

+

2.2μF

5V

OUT

22pF

1M*

0.001

+

C1B

1/2 LT1017

–

1M*

10M

360k

10M

V

IN

LT1004

1.2V

34

+

NC

2

1

4.3M*

47μF

619k*

390k

0.001

OPTIONAL FOR

NEGATIVE

OUTPUT

(SEE TEXT)

1.5V

C2B

C2A

Figure 20. 800μA Output 1.5V to 5V Converter

A = 100mV/DIV

(AC-COUPLED ON

LEVEL)

5V

DC

B = 2V/DIV

C = 2V/DIV

D = 2V/DIV

HORIZ = 5ms/DIV

AN29 F21

Figure 21. Waveforms for Low Power 1.5V to 5V Converter

5

6

TO 390kΩ

OF C2B

47μF

+

620k

14

3

850

800

750

= 5V

700

650

OUT

600

550

500

450

400

350

300

250

200

150

100

OUTPUT (μA) AVAILABLE AT V

22pF

1.2M* 10k5.1M

50

0

+

–

IQ = 125μA

0

1.05 1.15

C1B

V

OUT

EFFICIENCY ≈ 50%

GUARANTEED MINIMUM

OPERATING VOLTAGE

1.25

INPUT VOLTAGE (V)

10M 47k

= 5V

LT1017

1.35

LT1004

1.2V

1.45

V

1.55

AN29 F22

IN

Figure 22. Output Current Capability vs Input Voltage for Figure 20

AN29 F20

AN29-14

an32f

Page 15

Application Note 29

The optional connection in Figure 20 (shown in dashed

lines) takes advantage of the transformers fl oating secondary to furnish a –5V output. Drive circuitry is identical, but

C1B is rearranged as a current summing comparator. The

LT1004’s bootstrapped positive bias is supplied by L1’s

primary fl yback spikes.

200mA Output 1.5V to 5V Converter

Although useful, the preceding circuit is limited to low

power operation. Some 1.5V powered systems (survival

2-way radios, remote, transducer fed data acquisition

systems, etc.) require much more power. Figure 23’s

design supplies a 5V output with 200mA capacity. Some

sacrifi ce in quiescent current is made in this circuit. This is

predicated on the assumption that it operates continuously

22

+

1.5V

IN

L1

10k

–

1/2 LT1018

+

39k

47k

C1A

220μF

+

1N4148

1.5V

200k

1.5V

IN

10k

100Ω

HP5082-2810

1.5V

IN

Q1

2N2907

1k

2Ω

1/2 LT1018

1.5V

IN

V

+

IN

LT1070

V

C

1k

25μH

V

SW

FB

GND

6.8μF

0.01

68k

L1 = PULSE ENGINEERING, INC. # PE-92100

* = 1% METAL FILM RESISTOR

at high power. If lowest quiescent current is necessary the

technique detailed back in Figure 12 is applicable.

The circuit is essentially a fl yback regulator, similar to

Figure 11. The LT1070’s low saturation losses and ease

of use permit high power operation and design simplicity. Unfortunately, this device has a 3V minimum supply

requirement. Bootstrapping its supply pin from the 5V

output is possible, but requires some form of start-up

mechanism. Dual comparator C1 and the transistors form

a start-up loop. When power is applied C1A oscillates

(Trace A, Figure 24) at 5kHz. Q1 biases, driving Q2’s base

hard. Q2’s collector (Trace B) pumps L1, causing voltage

step-up fl yback events. These events are rectifi ed and

stored in the 500μF capacitor, producing the circuit’s DC

output. C1B is set up so it (Trace C) goes low when circuit

1N5823

5V

3.74k*

665Ω*

576Ω*

100k

47k

OUT

C1B “+”

1.5V

V

SUPPLY

INPUT

TO

IN

OPTIONAL IF

CAN EXCEED 1.7V

+V

1k

75k

LT1004

1.2V

100k

AN29 F23

UPDATE

LT1172 can be used

in place of LT1070

Q2

2N3507

C1B

+

500μF

–

+

Figure 23. 200mA Output 1.5V to 5V Converter

an32f

AN29-15

Page 16

Application Note 29

output crosses about 4.5V. When this occurs C1A’s integration capacitor is pulled low, stopping it from oscillating.

Under these conditions Q2 can no longer drive L1, but the

LT1070 can. This behavior is observable at the LT1070’s

pin (the junction of L1, Q2’s collector and the LT1070),

V

SW

Trace D. When the start-up circuit goes off, the LT1070 V

IN

pin has adequate supply voltage and it begins operation.

This occurs at the 4th vertical division of the photograph.

There is some overlap between start-up loop turn-off and

LT1070 turn-on, but it has no detrimental effect. Once the

circuit is running it functions similarly to Figure 11.

The start-up loop must be carefully designed to function

over a wide range of loads and battery voltages. Start-up

currents exceed 1 ampere, necessitating attention to Q2’s

saturation and drive characteristics. The worst case is a

nearly depleted battery and heavy output loading. Figure25

shows circuit output starting into a 100mA load at V

BATTERY

= 1.2V. The sequence is clean, and the LT1070 takes over at

the appropriate point. In Figure 26, loading is increased to

200mA. Start-up slope decreases, but starting still occurs.

The abrupt slope increase (6th vertical division) is due to

overlapping operation of the start-up loop and the LT1070.

Figure 27 plots input-output characteristics for the circuit.

Note that the circuit will start into all loads with V

BATTERY

=

1.2V. Start-up is possible down to 1.0V at reduced loads.

Once the circuit has started, the plot shows it will drive full

200mA loads down to V

possible down to V

BATTERY

BATTERY

= 1.0V. Reduced drive is

= 0.6V (a very dead battery)!

Figures 28 and 29, dynamic XY crossplot versions of

Figure 27, are taken at 20 and 200 milliamperes, respectively. Figure 30 graphs effi ciency at two supply voltages

over a range of output currents. Performance is attractive, although at lower currents circuit quiescent power

degrades effi ciency. Fixed junction saturation losses are

responsible for lower overall effi ciency at the lower supply

voltage. Figure 31 shows quiescent current increasing as

supply decays. Longer inductor current charge intervals

are necessary to compensate the decreased supply voltage.

A = 5V/DIV

B = 10V/DIV

C = 2V/DIV

D = 1V/DIV

(AC-COUPLED ON

5VDC LEVEL)

HORIZ = 2ms/DIV

AN29 F24

Figure 24. High Power 1.5V to 5V Converter Start-Up Sequence

VERT = 1V/DIV

HORIZ = 2ms/DIV

AN29 F25

Figure 25. High Power 1.5V to 5V Converter Turn-On Into a

100mA Load at V

BATT

= 1.2V

VERT = 1V/DIV

HORIZ = 2ms/DIV

AN29 F26

Figure 26. High Power 1.5V to 5V Converter Turn-On Into a

200mA Load at V

1.5

= 5V

1.4

OUT

1.3

1.2

1.1

1.0

0.9

0.8

0.7

0.6

0.5

0.4

0.3

0.2

0.1

0

MINIMUM INPUT VOLTAGE TO MAINTAIN V

0

= 1.2V

BATT

START

RUN

80

60 100 200

20 40

OUTPUT CURRENT (mA)

120 140

180160

AN29 F27

AN29-16

Figure 27. Input-Output Data for Figure 23

an32f

Page 17

VERT = OUTPUT

= 1V/DIV

HORIZ = INPUT = 0.15V/DIV

AN29 F28

Figure 28. Input-Output XY Characteristics of the

1.5V to 5V Converter at 20mA Loading

VERT = OUTPUT

= 1V/DIV

HORIZ = INPUT = 0.15V/DIV

AN29 F29

Figure 29. Input-Output XY Characteristics of the

1.5V to 5V Converter at 200mA Loading

HIGH EFFICIENCY CONVERTERS

High Effi ciency 12V to 5V Converter

Effi ciency is sometimes a prime concern in DC/DC converter design (see Appendix E, “Optimizing Converters

for Effi ciency”). In particular, small portable computers

frequently use a 12V primary supply which must be converted down to 5V. A 12V battery is attractive because it

offers long life when all trade-offs and sources of loss are

considered. Figure 32 achieves 90% effi ciency. This circuit

can be recognized as a positive buck converter. Transistor

Q1 serves as the pass element. The catch diode is replaced

with a synchronous rectifi er, Q2, for improved effi ciency.

The input supply is nominally 12V but can vary from 9.5V

to 14.5V. Power losses are minimized by utilizing low

source-to-drain resistance, 0.028Ω, NMOS transistors

for the catch diode and pass element. The inductor, Pulse

Engineering PE-92210K, is made from a low loss core

material which squeezes a little more effi ciency out of the

circuit. Also, keeping the current sense threshold voltage

low minimizes the power lost in the current limit circuit.

Application Note 29

100

V

= 5V

OUT

90

80

70

60

50

40

EFFICIENCY (%)

30

20

10

0

4020

0

Figure 30. Effi ciency vs Operating Point for Figure 23

1.50

1.45

1.40

1.35

1.30

1.25

1.20

1.15

SUPPLY VOLTAGE (V)

1.10

1.05

1.00

55

50

Figure 31. IQ vs Supply Voltage for Figure 23

Figure 33 shows the operating waveforms. Q5 drives the

synchronous rectifi er, Q2, when the V

turned “off”. Q2 is turned off through D1 and D2 when the

pin is “on”. To turn on Q1, the gate (Trace B) must

V

SW

be driven above the input voltage. This is accomplished

by bootstrapping the capacitor, C1, off the drain of Q2

(Trace C). C1 charges up through D1 when Q2 is turned on.

When Q2 is turned off, Q3 is able to conduct, providing a

path for C1 to turn Q1 on. During this time, current fl ows

through Q1 (Trace D) through the inductor (Trace E) and

into the load. To turn Q1 off, the V

Q5 is now able to turn on Q4 and the gate of Q1 is pulled

low through D3 and the 50Ω resistor. This resistor is used

to reduce the voltage noise generated by fast switching

characteristics of Q1. When Q2 is conducting (Trace F),

Q1 must be off. The effi ciency will be decreased if both

transistors are conducting at the same time. The 220Ω

VIN = 1.5V

VIN = 1.2V

120 140 180

8060

100

OUTPUT CURRENT (mA)

65 70

60

QUIESCENT CURRENT (mA)

SW

160

200

AN29 F30

80

75

AN29 F31

pin (Trace A) is

SW

pin must be “off”.

an32f

AN29-17

Page 18

Application Note 29

12V

(9.5V TO 14.5V)

IN

220μF

50k

Q8**

2N3906

100Ω

Q7**

2N3906

1k

+

LT1004-2.5

L1 = PULSE ENGINEERING, INC. # PE-92210K

* = 1% FILM RESISTORS

** = USE MATCHING OF 20mV AT 200μA

= P50N05E

(MOTOROLA)

0.018Ω47pF

R1

619Ω

Q6

2N2222

9k

IRFZ44

(INTERNATIONAL RECTIFIER)

100Ω

3.5k

1N4148

Q9

2N2222

E1

LT1072CN8

E2

GND

1N4148

5k

Q5

2N2222

D1

V

IN

V

1N4148

V

SW

FB

C

1μF

5k

Q3

2N2222C10.1μF

D3

1N4148

50Ω

220Ω1k

220Ω

Q4

VN2222

1N4148

D2

Q1

P50N05E

L1

100μH

Q2

P50N05E

3.01k*

1k*

AN29 F32

V

OUT

5V

5A

+

1000μF

Figure 32. 90% Effi ciency Positive Buck Converter with Synchronous Switch

A = 20V/DIV

B = 20V/DIV

C = 20V/DIV

D = 2A/DIV

E = 2A/DIV

F = 2A/DIV

HORIZ = 10μs/DIV

AN29 F33

Figure 33. Waveforms for 90% Effi ciency Buck Converter

resistors and D2 are used to minimize the overlap of the

switch cycles. Figure 34 shows the effi ciency versus load

plot for the circuit as shown. The other plots are for nonsynchronously switched buck regulators (see indicated

Figures).

Short circuit protection is provided by Q6 through Q9.

A 200μA current source is generated from an LT1004,

Q6 and the 9k resistor. This current fl ows through R1

and generates a threshold voltage of 124mV for the

comparator, Q7 and Q8. When the voltage drop across the

100

90

80

70

EFFICIENCY (%)

60

50

0

SYNC SWITCHES

PMOS AND DIODES

(SEE FIGURE 42)

PNP AND DIODES

(SEE FIGURE 42)

1

2

I

LOAD

(A)

3

4

5

AN29 F34

Figure 34. Effi ciency vs Load for Figure 32. The Synchronous

Switches Give Higher Effi ciency than Simple FET or Bipolar

Transistors and Diodes

0.018Ω sense resistor exceeds 124mV, Q8 is turned on.

The LT1072’s V

pin goes off when the VC pin is pulled

SW

below 0.9V. This occurs when Q8 forces Q9 to saturate.

An RC damper suppresses line transients that might

prematurely turn on Q8.

AN29-18

an32f

Page 19

Application Note 29

MBR1060

12V

IN

680Ω

V

IN

V

+

100μF

GND

L1 = PULSE ENGINEERING, INC. # PE-65066

* = 1% FILM RESISTORS

MBR1060 = MOTOROLA

LT1070

SW

FB

V

C

1k

1μF

MBR360

0.47μF

Figure 35. High Effi ciency Flux Sensed Isolated Converter

High Effi ciency, Flux Sensed Isolated Converter

Figure 35’s 75% effi ciency is not as good as the previous

circuit, but it has a fully fl oating output. This circuit uses

a bifi lar wound fl ux sensing secondary to provide isolated

voltage feedback. In operation the LT1070’s V

pin (Trace

SW

A, Figure 36) pulses L1’s primary, producing identical waveforms at the fl oating power and fl ux sensing secondaries

(Traces B and C). Feedback occurs from the fl ux sense

winding via the diode and capacitive fi lter. The 1k resistor provides a bleed current, while the 3.4k-1.07k divider

sets output voltage. The diode partially compensates the

diode in the power output winding, resulting in an overall

temperature coeffi cient of about 100ppm/°C. The oversize

diode aids effi ciency, although signifi cant improvement

(e.g., 5% to 10%) is possible if synchronous rectifi cation

is employed, as in Figure 32. The primary damper network

is unremarkable, although the 2k-0.1μF network has been

added to suppress excessive ringing at low output current.

2k

0.1μF

A = 10V/DIV

B = 10V/DIV

C = 10V/DIV

4

5

MBR1060

3

6

+

1000μF

+

22μF

HORIZ = 5μs/DIV

L1

t

8

t

t

1

5V

OUT

100mA TO 1A

(SEE TEXT)

3.40k*

1k

1.07k*

AN29 F35

AN29 F36

Figure 36. Waveforms for Flux Sensed Converter

This ringing is not deleterious to circuit operation, and the

network is optional. Below about 10% loading non-ideal

transformer behavior introduces signifi cant regulation error. Regulation stays within ±100mV from 10% to 100%

of output rating, with excursion exceeding 900mV at no

load. Figure 37’s circuit trades away isolation for tight

regulation with no output loading restrictions. Effi ciency

is the same.

an32f

AN29-19

Page 20

Application Note 29

12V

IN

680ΩL10.47μF

V

IN

V

+

100μF

GND

L1 = PULSE ENGINEERING, INC. # PE-65067

* = 1% FILM RESISTORS

Figure 37. Non-Isolated Version of Figure 35

LT1070

SW

V

C

1k

MBR360

FB

1μF

WIDE RANGE INPUT CONVERTERS

Wide Range Input –48V to 5V Converter

Often converters must accommodate a wide range of

inputs. Telephone lines can vary over considerable tolerances. Figure 38’s circuit uses an LT1072 to supply a 5V

output from a telecom input. The raw telecom supply is

nominally –48V but can vary from –40V to –60V. This range

of voltages is acceptable to the V

required for the V

pin (V

IN

MAX

Zener diode serve this purpose, dropping V

pin but protection is

SW

= 60V). Q1 and the 30V

’s voltage to

IN

acceptable levels under all line conditions.

Here the “top” of the inductor is at ground and the LT1072’s

ground pin at –V. The feedback pin senses with respect

to the ground pin, so a level shift is required from the 5V

output. Q2 serves this purpose, introducing only –2mV/°C

drift. This is normally not objectionable in a logic supply.

It can be compensated with the optional appropriately

scaled diode-resistor shown in Figure 38.

Frequency compensation uses an RC damper at the V

C

pin. The 68V Zener is a type designed to clamp and absorb

excessive line transients which might otherwise damage

the LT1072 (V

maximum voltage is 75V)

SW

MBR1060

8

4

t

1

+

1000μF

t

5

Figure 39 shows operating waveforms at the V

AN29 F37

5V

1A

3.01k*

1k*

OUT

SW

pin.

Trace A is the voltage and Trace B the current. Switching

is crisp, with well controlled waveforms. A higher current

version of this circuit appears in LTC Application Note 25,

“Switching Regulators For Poets.”

3.5V to 35V

IN

–5V

Converter

OUT

Figure 40’s approach has an even wider input range. In

this case it produces either a –5V or 5V output (shown in

dashed lines). This circuit is an extension of Figure 11’s

basic fl yback topology. The coupled inductor allows the

option for buck, boost, or buck-boost converters. This

circuit can operate down to 3.5V for battery applications

while accepting 35V inputs.

Figure 41 shows the operating waveforms for this circuit.

During the V

(Trace A) “on” time, current fl ows through

SW

the primary winding (Trace B). No current is transferred

to the secondary because the catch diode, D1, is reverse

biased. The energy is stored in the magnetic fi eld. When

the switch is turned “off” D1 forward biases and the energy

is transferred to the secondary winding. Trace C is the

voltage seen on the secondary and Trace D is the current

AN29-20

an32f

Page 21

INPUT

–48V

(–40V TO –60V)

3k

100μF

1/2W

220Ω

1N5936

30V

2.2μF

Q1

2N5550

+

68V**

+

V

IN

LT1072HV

GND

*

MUR410 (MOTOROLA)

**

1.5KE68A (MOTOROLA)

L1 = PULSE ENGINEERING, INC. # PE-92108

Figure 38. Wide Range Input Converter

Application Note 29

L1

1k

100μH

*

+

V

SW

FB

V

C

2k

0.22

330μF

2N5401

5V

OUT

0.5A

3.9k

1%

Q2

1.1k

1%

OPTIONAL

LOW DRIFT FEEDBACK

CONNECTION (SEE TEXT)

FROM

5V OUTPUT

3.01k

1%

Q2

2N5401

TO

FB PIN

TO

–48V

Q3

2N5401

1k

1%

3.01k

1%

AN29 F38

fl owing through it. This is not an ideal transformer so

not all of the primary windings energy is coupled into the

secondary. The energy left in the primary winding causes

the overvoltage spikes seen on the V

pin (Trace E). This

SW

phenomenon is modeled by a leakage inductance term

which is placed in series with the primary winding. When

the switch is turned “off” current continues to fl ow in the

inductor causing the snubber diode to conduct (Trace F).

The snubber diode current falls to zero as the inductor

loses its energy. The snubber network clamps the voltage

spike. When the snubber diode current reaches zero, the

pin voltage settles to a potential related to the turns

V

SW

ratio, output voltage and input voltage.

4

The feedback pin senses with respect to ground, so Q1

through Q3 provides the level shift from the –5V output.

Q1 introduces a –2mV/°C drift to the circuit. This effect can

be compensated by a circuit similar to the one shown in

Figure 38. Line regulation is degraded due to Q3’s output

impedance. If this is a problem, an op amp must be used

to perform the level shift (see AN19, Figure 29).

A = 50V/DIV

B = 0.5A/DIV

HORIZ = 5μs/DIV

AN29 F39

Figure 39. Waveforms for Wide Range Input Converter

Wide Range Input Positive Buck Converter

Figure 42 is another example of a positive buck converter.

This is a simpler version compared to the synchronous

switch buck, Figure 32. However, effi ciency isn’t as high

(see Figure 34). If the PMOS transistor is replaced with

a Darlington PNP transistor (shown in dashed lines)

effi ciency decreases further.

4

Application Note AN19, “LT1070 Design Manual,” page 25

an32f

AN29-21

Page 22

Application Note 29

VIN = 3.5V TO 35V

5V

V

IN

V

+

100μF

GND

L1 = PULSE ENGINEERING, INC. # PE-65050

* = 1% FILM RESISTORS

A = 20V/DIV

B = 4A/DIV

C = 10V/DIV

D = 4A/DIV

E = 20V/DIV

F = 2A/DIV

SW

LT1070

FB

V

C

1k 1k*

1μF

A, B, C, D HORIZ = 10μs/DIV

E, F HORIZ = 1μs/DIV

Figure 41. Waveforms for Wide Range Input Positive

–5V Output Flyback Converter

Figure 43a shows the operating waveforms for this circuit.

The pass transistor’s (Q1) drive scheme is similar to the one

shown in Figure 32. During the V

the gate of the pass transistor is pulled down through D1.

This forces Q1 to saturate. Trace B is the voltage seen on

the drain of Q1 and Trace C is the current passing through

Q1. The supply current fl ows through the inductor (Trace D)

and into the load. During this time energy is being stored

in the inductor. When voltage is applied to the inductor,

0.68μF

510Ω

1W

MBR360

(MOTOROLA)

n = 1

3

•

L1

4

2N3906

L1

Q3

1k*

1%

2

n = 1

•

1

MBR360

D1

Figure 40. Wide Range Input Positive-to-Negative Flyback Converter

AN29 F41

(Trace A) “on” time,

SW

1k*

1%

Q2

2N3906

Q1

1000μF

2N2222

3.32k*

1%

+

–5V

1A

OUT

V

IN

3

n = 1

4

V

SW

FB

MBR360

L1

2

+

•

1

OPTIONAL (SEE TEXT)

1000μF

5V

1A

3.01k*

1k*

OUT

AN29 F40

current does not instantly rise. As the magnetic fi eld builds

up, the current builds. This is seen in the inductor current

waveform (Trace D). When the V

pin is “off,” Q2 is able

SW

to conduct and turns Q1 off. Current can no longer fl ow

through Q1, instead D2 is conducting (Trace E). During

this period some of the energy stored in the inductor will

be transferred to the load. Current will be generated from

the inductor as long as there is any energy in it. This can

be seen in Figure 43a. This is known as continuous mode

operation. If the inductor is completely discharged, no

current will be generated (see Figure 43b). When this

happens neither switch, Q1 or D2, is conducting. The

inductor looks like a short and the voltage on the cathode

of D2 will settle to the output voltage. These “boingies”

can be seen in Trace B of Figure 43b. This is known as

discontinuous mode operation. Higher input voltages

can be handled with the gate-source Zener clamped by

D2. The 400 milliwatt Zener’s current must be rescaled

by adjusting the 50Ω value. Maximum gate-source voltage is 20V. The circuit will function up to 35V

. At inputs

IN

beyond 35V all semiconductor breakdown voltages must

be considered.

AN29-22

an32f

Page 23

Application Note 29

V

12V TO 35V

100μF

2N3906

5.1k

0.1Ω

1k

1k

V

IN

E1

E2

GND

100pF

IN

+

L1 = PULSE ENGINEERING, INC # PE-92113

* = 1% FILM RESISTORS

LT1072CN8

1N4148

2N2222

V

SW

V

1k

1N4148

51Ω

1W

FB

C

1k

1μF

Q2

2N2222A

D1

OPTIONAL

(SEE TEXT)

1k

IRF9Z30

(HEAT SINK)

D2

12V

1N759

(OPT)

(HEAT SINK)

2N2222

Q1

2N6667

L1

170μH

D2

MBR735

(MOTOROLA)

100μF

+

AN29 F42

5V

5A

3.01k*

1k*

OUT

Figure 42. Positive Buck Converter

A = 10V/DIV

B = 10V/DIV

C = 2A/DIV

D = 2A/DIV

E = 2A/DIV

HORIZ = 10μs/DIV

AN29 F43a

Figure 43a. Waveforms for Wide Range Input Positive Buck

Converter (Continuous Mode)

1N4148

100Ω

1W

A = 10V/DIV

B = 10V/DIV

C = 0.5A/DIV

D = 0.5A/DIV

E = 0.5A/DIV

HORIZ = 10μs/DIV

AN29 F43b

Figure 43b. Waveforms for Wide Range Input Positive Buck

Converter (Discontinuous Mode)

an32f

AN29-23

Page 24

Application Note 29

28V NOMINAL

(15V TO 35V)

100μF

1k

Q2

2N2222A

1N4148

220Ω

+

V

IN

E1

LT1072CN8

E2

GND

L1 = PULSE ENGINEERING, INC # PE-52627

* = 1% FILM RESISTORS

1W

D1

1N4148

V

SW

FB

V

C

1k

1μF

Figure 44. Positive Buck-Boost Converter

IRF9Z30

7.5V

1N755

D2

MBR360

Q1

L1

330μH

D3

MBR360

(MOTOROLA)

D4

MBR360

28V

+

1000μF

250mA

26.1k

1.21k*

AN29 F44

Buck-Boost Converter

The buck boost topology is useful when the input voltage can either be higher or lower than the output. In this

example, Figure 44, this is accomplished with a single

inductor instead of a transformer, as in Figure 40 (optional).

However, the input voltage range only extends down to

15V and can reach to 35V. If the maximum 1.25A switch

current rating of the LT1072 is exceeded an LT1071 or

LT1070 can be used instead. At high power levels package

thermal characteristics should be considered.

The operation of the circuit is similar to the positive buck

converter, Figure 42. The gate drive to the pass transistor

is derived the same way except the gate-source voltage is

clamped. Remember, the gate-source maximum voltage

rating is specifi ed at ±20V. Figure 45 shows the operating

waveforms. When the V

pin is “on” (Trace A), the pass

SW

transistor, Q1, is saturated. The gate voltage (Trace B) is

clamped by the Zener diode. Trace C is the voltage on the

drain of Q1 and Trace D is the current through it. This

is where the similarities between the two circuits end.

Notice the inductor is pulled to within a diode drop, D2

above ground, instead of being tied to the output (see

A = 20V/DIV

B = 10V/DIV

C = 20V/DIV

D = 2A/DIV

E = 2A/DIV

F = 2A/DIV

HORIZ = 10μs/DIV

AN29 F45

Figure 45. Waveforms for Positive Buck-Boost Converter

Figure 42). In this case, the inductor has the input voltage

applied across it, except for a Vbe and saturation losses.

D4 is reverse biased and blocks the output capacitor from

discharging into the V

pin. When the VSW pin is “off” Q1

SW

and D2 cease to conduct. Since the current in the inductor

(Trace E) continues to fl ow, D3 and D4 are forward biased

and the energy in the inductor is transferred into the load.

Trace F is the current through D3. Also, D2 keeps Q1 from

staying on if the circuit is operating in buck mode. D1, on

the other hand, blocks current from fl owing into the gate

drive circuit when operating in boost mode.

AN29-24

an32f

Page 25

INPUT

10k

Q1

2N6667

335μH

MR1122

Application Note 29

V

≈ 1.8V

L1

+

10,000μF

470

REF

LT1083

IN OUT

ADJ

240*

OUTPUT

+

10μF

1k

0.001

1M

LT1011

4

1

28V

4N28

+

10k

10k

–

1N914

Figure 46. High Power Linear Regulator with Switching Pre-Regulator

A = 200mV/DIV

(AC-COUPLED)

B = 50V/DIV

C = 20V/DIV

D = 5A/DIV

HORIZ = 500μs/DIV

AN29 F47

Figure 47. Switching Pre-Regulated Linear Regulators Waveforms

Wide Range Switching Pre-Regulated Linear

Regulator

In a sense, linear regulators can be considered extraordinarily wide range DC/DC converters. They do not face

the dynamic problems switching regulators encounter

under varying ranges of input and output. Excess energy

is simply dissipated at heat. This elegantly simplistic

energy management mechanism pays dearly in terms of

effi ciency and temperature rise. Figure 46 shows a way a

linear regulator can more effi ciently control high power

under widely varying input and output conditions.

The regulator is placed within a switched-mode loop that

servo-controls the voltage across the regulator. In this

arrangement the regulator functions normally while the

switched-mode control loop maintains the voltage across it

1N914

28V

V

≈ 1.8V

REF

L1 = PULSE ENGINEERING, INC. # PE-51518

* = 1% FILM RESISTOR

2k

AN29 F46

at a minimal value, regardless of line, load or output setting

changes. Although this approach is not quite as effi cient as

a classical switching regulator, it offers lower noise and the

fast transient response of the linear regulator. The LT1083

functions in the conventional fashion, supplying a regulated

output at 7.5A capacity. The remaining components form

the switched-mode dissipation limiting control. This loop

forces the potential across the LT1083 to equal the 1.8V

value of V

. The opto-isolator furnishes a convenient

REF

way to single end the differentially sensed voltage across

the LT1083. When the input of the regulator (Trace A,

Figure 47) decays far enough, the LT1011 output (Trace B)

switches low, turning on Q1 (Q1 collector is Trace C). This

allows current fl ow (Trace D) from the circuit input into the

10,000μF capacitor, raising the regulator’s input voltage.

When the regulator input rises far enough, the comparator

goes high, Q1 cuts off and the capacitor ceases charging. The MR1122 damps the fl yback spike of the current

limiting inductor. The 0.001μF-1M combination sets loop

hysteresis at about 100mV

. This free-running oscil-

P-P

lation control mode substantially reduces dissipation in

the regulator, while preserving its performance. Despite

changes in the input voltage, different regulated outputs or

load shifts, the loop always ensures minimum dissipation

in the regulator.

an32f

AN29-25

Page 26

Application Note 29

100

90

P

= 12W

OUT

80

70

P

= 15W

OUT

P

= 5W

60

OUT

50

40

P

= 5W

OUT

EFFICIENCY (%)

30

20

10

0

0

V

= 5V VIN = 15V

OUT

V

= 5V VIN = 28V

OUT

1

V

OUT

V

OUT

VIN = 15V

= 12V

VIN = 28V

= 15V

LT1083 WITH NO PRE-REGULATOR. THEORETICAL LIMITS ONLY.

DISSIPATION LIMITED

LT1083 WITH NO PRE-REGULATOR. THEORETICAL LIMITS ONLY.

DISSIPATION LIMITED

2

3

OUTPUT (A)

Figure 48. Effi ciency vs Output Current for Figure 46 at Various Operating Points