Page 1

Application Note 143

N

R

December 2013

A Simple Method to Accurately Predict PLL Reference

Spur Levels Due to Leakage Current

Michel Azarian and Will Ezell

Presented is a simple model that can be used to accurately

predict the level of reference spurs due to charge pump

and/or op amp leakage current in a PLL system. Knowing

how to predict these levels helps pick loop parameters

wisely during the early stages of a PLL system design.

Quick Review of PLLs

The phase locked loop (PLL) is a negative feedback system

that locks the phase and frequency of a higher frequency

device (usually a voltage controlled oscillator, VCO) whose

phase and frequency are not very stable over temperature

and time to a more stable and lower frequency device

(usually a temperature compensated or oven controlled

crystal oscillator, TCXO or OCXO). As a black box, the PLL

can be viewed as a frequency multiplier.

A PLL is employed when there is the need for a high

frequency local oscillator (LO) source. Example applica

tions are numerous and include wireless communications,

medical devices and instrumentation.

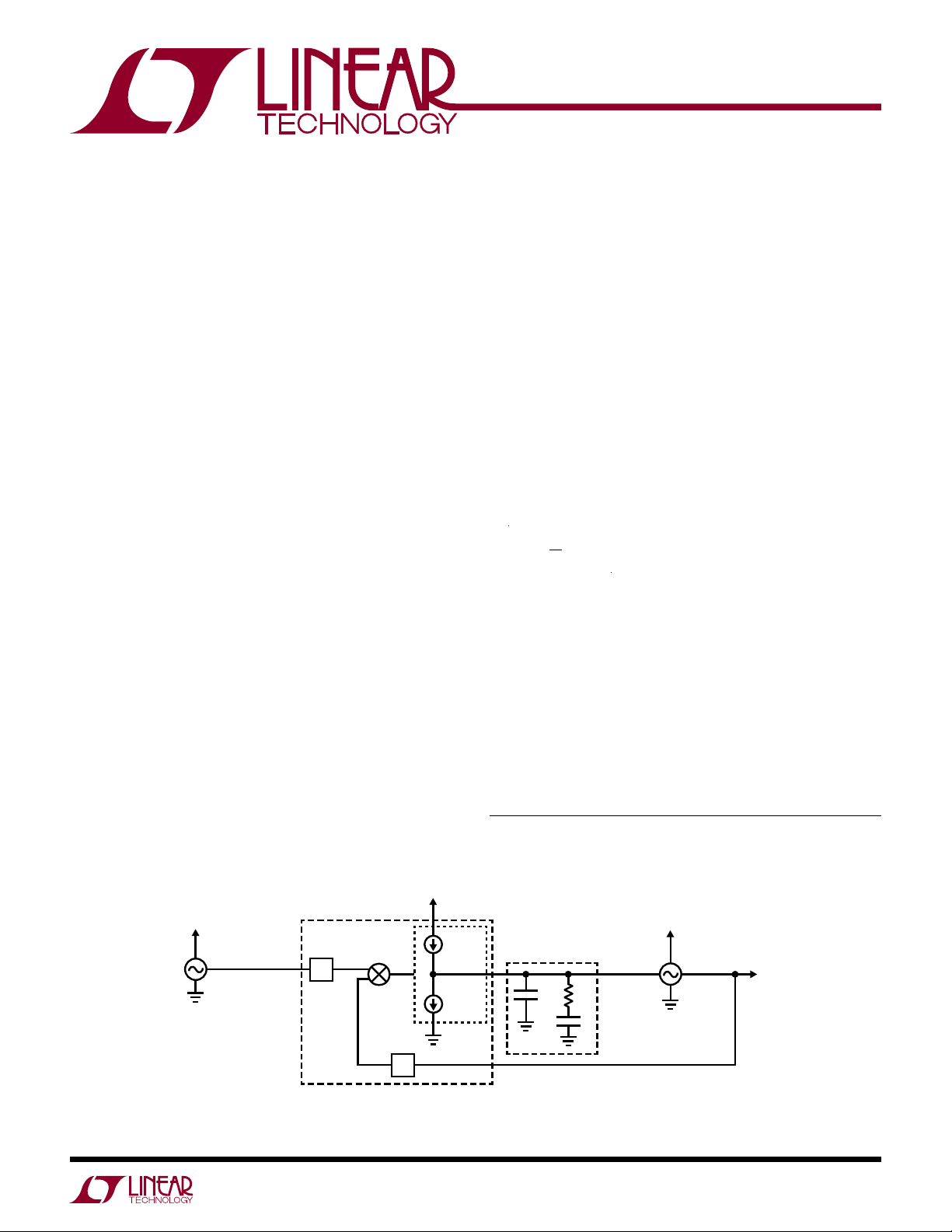

Figure 1 shows the building blocks of a PLL system used

for generating an LO signal. The PLL integrated cir

(IC)

usually contains all clock dividers (R and N), phase/

cuit

frequency detector (PFD) and the charge pump, represented

by the two current sources, ICP_UP and ICP_DN.

The VCO output is compared to the reference clock (the

OCXO output here) after both signals are divided down in

frequency by their respective integer dividers (N and R,

respectively). The PFD block controls the charge pump to

sink or source current pulses at the f

rate into the loop

PFD

filter to adjust the voltage on the tuning port of the VCO

(V_TUNE) until the outputs of the clock dividers are equal

in frequency and are in phase. When these are equal, it is

said that the PLL is locked. The LO frequency is related to

the reference frequency, f

fLO=

• f

REF

, by the following equation:

REF

The PLL shown in Figure 1 is called an integer-N PLL because the feedback divider (the N-divider) can only assume

integer values. When this divider can assume both integer

and noninteger values, the loop is called a fractional-N

PLL. The focus here will be only on integer-N PLLs, as

different mechanisms are at work in fractional-N PLLs.

Integer

-N PLL Nonidealities

The PLL IC contributes its own nonidealities to the system,

principally phase noise and spurious.

L, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks and

PLLWizard is a trademark of Linear Technology Corporation. All other trademarks are the

property of their respective owners.

V_CP

= f

OCXO

PLL IC

÷R

f

PFD

PFD

÷N

Figure 1. Basic Building Blocks of a PLL

ICP_UP

ICP_DN

LOOP FILTER

CPR

V_VCO

VCO

V_TUNE

Z

C

I

f

LO

FEEDBACK

AN143 F01

LO

an143f

AN143-1

V_OCXO

OCXO

f

REF

Page 2

Application Note 143

Phase Noise

The PLL system of Figure 1 acts as a low pass filter on the

reference clock phase noise and as a high pass filter on

that of the VCO. The low pass and high pass filter cutoff

frequency is defined by the loop bandwidth (LBW) of the

PLL. Ideally, the LO phase noise follows that of the reference

clock converted to the LO frequency (that is, multiplied by

N/R) up to the LBW and subsequently follows the phase

noise of the VCO. The PLL IC’s noise contribution elevates

the phase noise in the transition area.

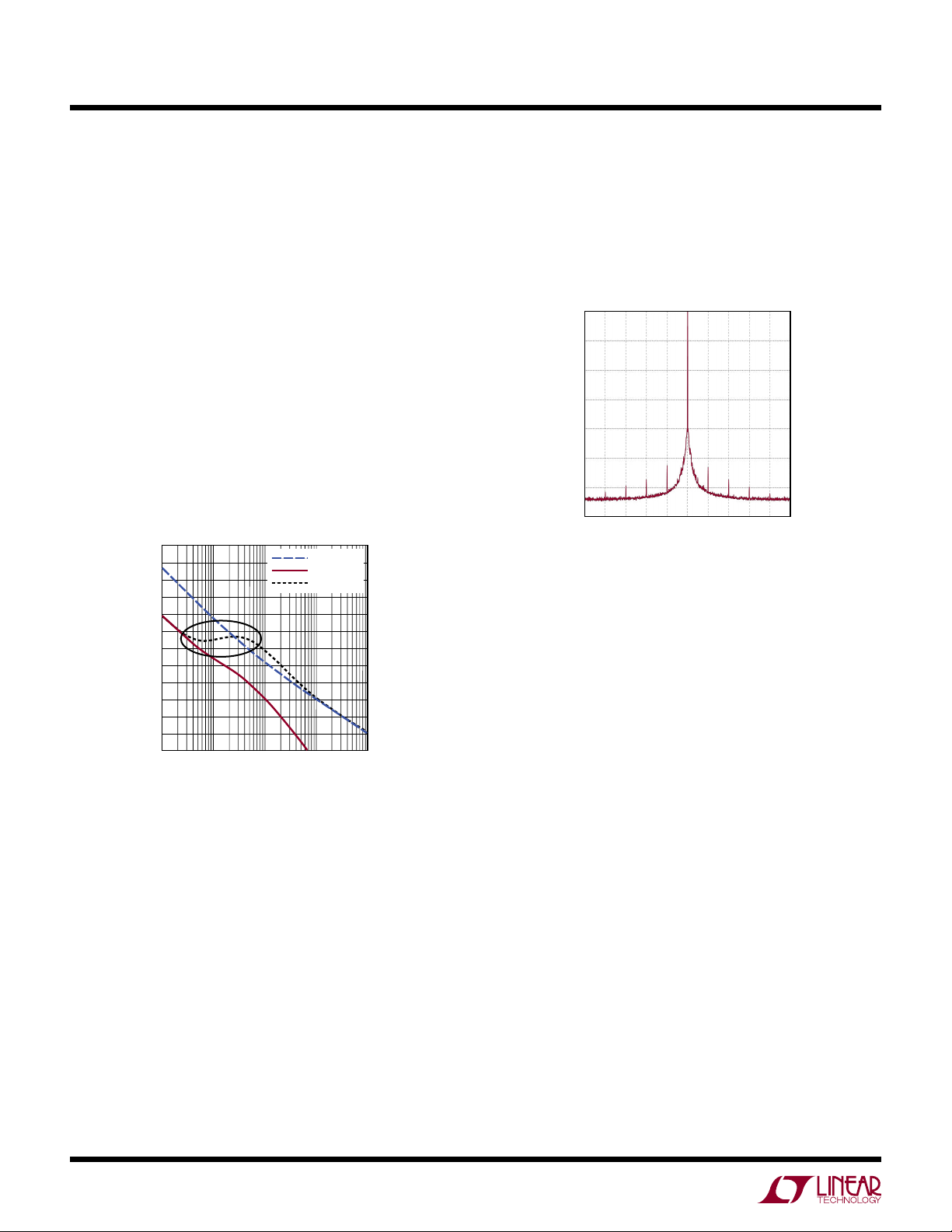

Figure 2 is a phase noise plot generated by PLLWiz

ard™, a free PLL design and simulation tool from Linear

Technology. The figure shows both the total output phase

(TOTAL), and the individual noises at the output

noise

due to the reference (REF at RF) and the VCO (VCO at

RF). The IC’s noise contribution can easily be seen in the

highlighted area.

–40

–50

–60

–70

–80

–90

–100

–110

–120

PHASE NOISE (dBc/Hz)

–130

–140

–150

–160

100

Figure 2. PLL IC Phase Noise Contribution Region as Highlighted

by the Drawn Ellipse

1k

OFFSET FREQUENCY (Hz)

10k

VCO AT RF

REF AT RF

TOTAL

100k 1M

AN143 F02

Spurious

Any unwanted signals on the power supplies shown in

Figure 1 (V_OCXO, V_CP and V_VCO) can translate into

spurious (spurs) on the LO signal. Careful design of these

supplies greatly reduces or even eliminates these spurs.

Charge pump related spurs, however, are inevitable. But,

they can be reduced with careful PLL system design.

These spurs are commonly referred to as reference spurs,

though reference here does not mean the reference clock

frequency. Rather, it refers to f

by an integer-N PLL has dual sideband spurs at f

. An LO signal produced

PFD

PFD

and

its harmonics.

For example, Figure 3 shows the spectrum of a 2.1GHz LO

signal. f

is 1MHz (N = 2100) and the reference clock

PFD

is 10MHz (R = 10). The loop bandwidth is 40kHz. As a

side note, it is worth mentioning that the spurious level

achieved in this measurement is world class due to the

high performance of the LTC6945, an ultralow noise and

spurious PLL IC from Linear Technology.

0

–20

–40

–60

–80

AMPLITUDE (dBc)

–100

–120

–140

2096

Figure 3. Reference Spurs of a 2100 MHz LO Signal with an

f

of 1MHz Generated Using the LTC6945 PLL IC from Linear

PFD

Technology Along with the UMX-586-D16-G VCO from RFMD

2100

2098

FREQUENCY (MHz)

2102 2104

AN143 F03

Causes of Reference Spurs

In steady-state operation, the PLL is locked, and, theoretically, there is no more need to engage the ICP_UP and

ICP_DN current sour

ces of Figure 1 during ever

y PFD

cycle. However, doing so would create a dead zone in the

loop response as there is a significant drop in the smallsignal loop gain (practically, an open loop). This dead zone

is eliminated by forcing ICP_UP and ICP_DN to produce

extremely narrow pulses during every PFD cycle. These

are commonly referred to as anti-backlash pulses. This

produces energy content on the VCO tune line at f

PFD

and

its harmonics. The negative feedback cannot counteract

these pulses since these frequencies are outside the loop

bandwidth of a properly designed PLL. The VCO, then, is

frequency modulated (FM) by this energy content, and

related spurs appear at f

and its harmonics, all centered

PFD

around LO.

Between anti-backlash pulses, the charge pump current

sources are off (tri-stated). Inherently, the charge pump

has some leakage current when tri-stated. Using an op amp

in an active loop filter (such as in Figure 7) introduces yet

an143f

AN143-2

Page 3

Application Note 143

another leakage current source due to the op amp’s input

bias and offset currents. The aggregate of these unwanted

currents, whether sourcing or sinking, causes a drift in

the voltage across the loop filter and, consequently, in

the tune voltage of the VCO. The negative feedback of the

loop will correct for this anomaly by introducing a unipolar

current pulse from the charge pump once every PFD cycle

so that the average tune line voltage produces the correct

frequency out of the VCO. The pulses produce energy at

, which also causes spurs to appear centered around LO

f

PFD

and offset by f

In integer-N PLLs, f

and its harmonics as previously noted.

PFD

is often chosen to be relatively small

PFD

because of the system’s frequency step size requirements.

This means that the anti-backlash pulse width, especially

with the present high speed IC technologies, is extremely

small compared to the PFD period. As such, a large leak

age current causes the total charge pump pulses to be

unipolar and tends to be the dominant cause of reference

spurs.

This phenomenon will

be examined in more depth.

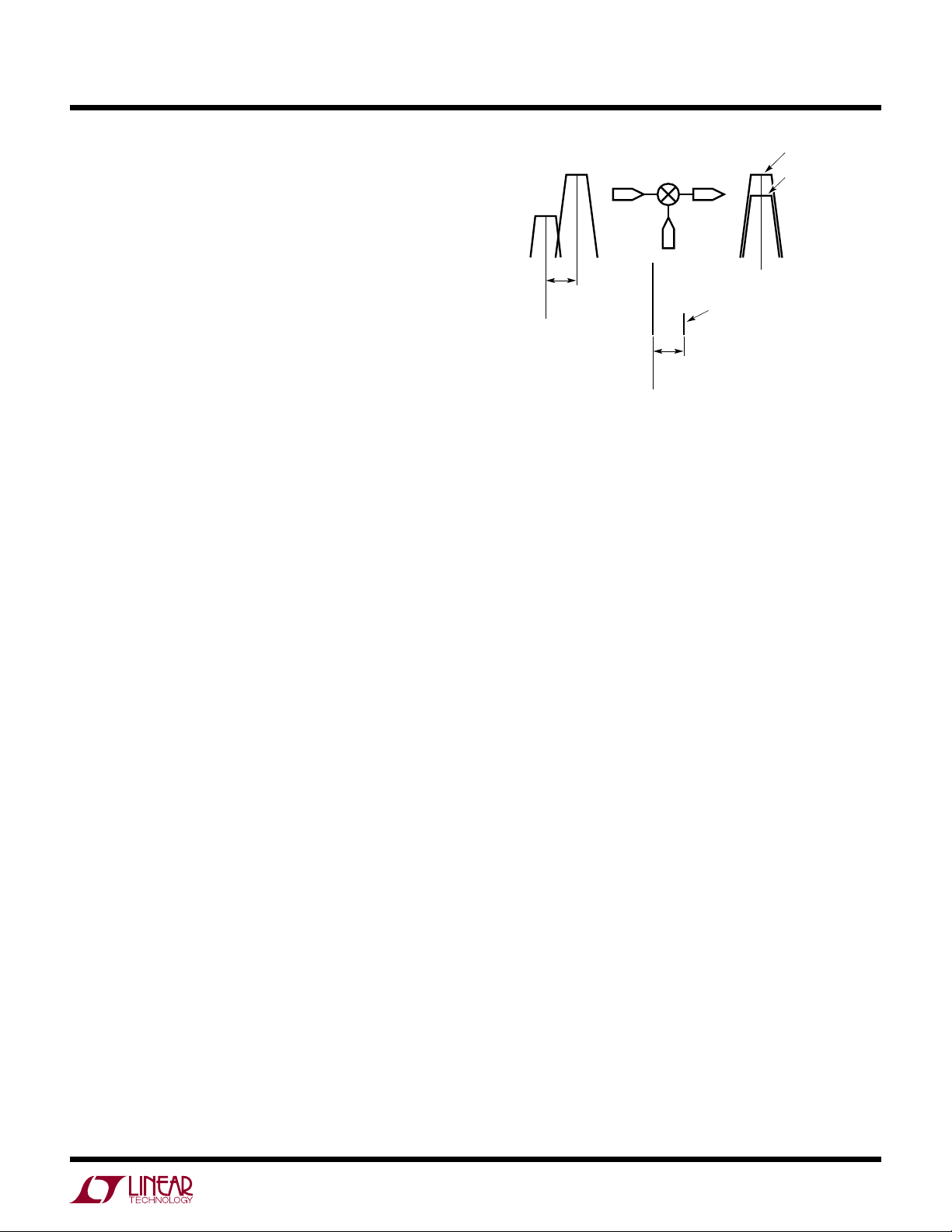

Reference Spurs’ Effect on System Performance

In a particular communications frequency band there are

multiple channels that occupy equal bandwidths. The

center-to-center frequency distance between two adjacent

channels is equal among all channels and is denoted by

channel spacing. Due to several factors, it is common to

find large variations in signal strength between any two

adjacent channels.

DESIRED

f

IF

CHANNEL AT IF

ADJACENT

CHANNEL AT IF

AN143 F04

ADJACENT

CHANNEL

DESIRED

CHANNEL

CHANNEL

SPACING

f

RF

Figure 4. Illustration of Adjacent Channel Interference Due to

Reference Spurs

MIXER

RF IF

LO

CHANNEL

SPACING

f

LO

REFERENCE

SPUR

Relationship Between Leakage Current and Reference

Spur Levels

The mathematical prediction of a PLL IC’s phase noise

contribution is relatively straightforward and can be ac

curately determined by calculations. However, the prediction of reference spur levels is traditionally believed to

be complex. This section derives a method to accurately

predict reference spur levels due to leakage current using

simple calculations. T

wo examples using different loop

filters will be examined.

Passive Loop Filter Example

A typical scenario in a multi-channel wireless communi

cations system where a stronger channel exists adjacent

to the desired but weaker channel is shown in Figure 4.

Only one of the LO reference spurs of concern is shown.

In an integer-N PLL, f

is usually chosen to be equal

PFD

to the channel spacing, which means that the reference

spurs are positioned at the channel spacing from the LO.

These spurs translate all adjacent and nearby channels to

the center of the intermediate frequency (f

) along with

IF

the LO mixing the desired channel to the same frequency.

These undesired channels, being uncorrelated to the signal

in the desired channel, appear as an elevated noise floor

to the desired signal and limit the signal-to-noise ratio.

A PLL system with a typical passive loop filter is shown in

Figure 5 along with a current sour

to represent the leakage current of the charge pump. As

ce denoted I_LEAKAGE

suming the PLL is locked, I_LEAKAGE reduces the charge

held by C

during the time when the charge pump is off.

P

When the charge pump turns on once every PFD cycle,

ICP_UP replenishes the charge lost from C

by applying

P

a short pulse of current. Feedback forces the average

voltage seen at V_TUNE (V_TUNE_AVG) to be constant,

maintaining the correct LO frequency. Figure 6 depicts

this visually.

The derivation of the resultant spurs involves some knowl

edge of loop stability requirements, the first being LBW

an143f

AN143-3

Page 4

Application Note 143

f

10

1

PFD

1

PFD

LBW

1

3

z=Rz•CI

3

z

1

PFD

2π

ΔT

C

AN143 F06

restrictions. The LBW of the PLL system is designed to

be at least 10 times smaller than f

LBW≤

PFD

PFD

,

This means that the period of the PFD is:

T

=

PFD

and,hence,LBW ≤

f

10 • T

To create a stable loop with plenty of phase margin, a zero,

consisting of R

and CI in Figure 5, is inserted in the loop

Z

at about 1/3rd the LBW. That is,

ZeroLocation ≈

where τ

=

3

2πτ

⇒LBW ≈

z

2πτ

,

z

Replacing LBW in the last equation with its equivalent in

terms of T

2πτ

PFD

≤

10 • T

results in:

, or T

PFD

≤

τ

z

30

This means that the PFD period is almost five times shorter

than the time constant of the zero, τ

ripple produced at a period of T

unseen by C

. The closed-loop bandwidth LBW is approxi-

I

. This implies that the

Z

across CP is mostly

PFD

mately equal to the unity crossing of the open-loop gain.

Since the zero is located within the loop bandwidth (it is

located at 1/3rd the unity crossing of the open-loop gain),

the voltage

across C

is dictated by the negative feedback

I

and is mostly a DC value.

Practically speaking, only C

is discharged and charged

P

during the PFD cycles shown in Figure 6.

If a capacitor, C, is charged or discharged with a constant

current source, I, over a period of time given by ΔT, the

voltage delta across this capacitor is given by:

ΔV =I

To maintain a fixed output frequency at LO, the voltage

droop that occurs during the discharge period is equal to

V_CP

V_OCXO

PLL IC

OCXO

÷R

Figure 5. A PLL System with a Passive Loop Filter and I_Leakage Representing the

Charge Pump Leakage Current

I_CP

P-P

T

CHARGE

PFD

÷N

ICP_UP

ICP_DN

T

DISCHARGE

I_LEAKAGE

LOOP FILTER

CPR

T

PFD

V_TUNE

Z

C

I

V_VCO

VCO

LO

FEEDBACK

AN143 F05

V_TUNE_AVGV

TIME

Figure 6. CP Discharging Through I_Leakage and Charging Back Through

ICP_UP Every PFD Cycle

an143f

AN143-4

Page 5

Application Note 143

I_LEAKAGE •T

P

I_CP• T

P

T

T

and T

≈ T

∞

I_LEAKAGE •T

P

I_LEAKAGE

PFD

I_LEAKAGE

P

PFD

I_LEAKAGE

P

PFD

c

R

c

the voltage buildup during the charging period of Figure 6.

That is:

V

P-P

where, T

=

CHARGE

DISCHARGE

=

C

is the amount of time the charge pump

CHARGE

C

current is active during every PFD cycle.

The charge pump current, I_CP, is usually in the mA range

and I_LEAKAGE is usually in the nA range, which means

that:

CHARGE

PFD

DISCHARGE

PFD

This implies that the ripple voltage seen across CP can be

represented by a sawtooth waveform.

To study the effect of this sawtooth waveform on the

spectrum of the LO signal, and since the waveform is a

periodic function, it can be broken down into its frequency

components using Fourier Series analysis.

SAWTOOTHFOURIER SERIES= DC VALUE –

V

P-P

π

sin(2πnft)

∑

n=1

n

where:

The DC value, which is equal to V_TUNE_AVG in Figure 6,

is set by the negative feedback per the requested LO frequency. The AC components, however, frequency modulate

the VCO through its tune pin with a tuning sensitivity of

K

to produce dual sideband spurs with a fundamental

VCO

of f

. The Appendix derives the following equation that

PFD

is going to be used next.

SIDEBAND

CARRIER

= 2 , dB0log

10

K

• E

VCO

2f

m

m

The effect of the negative feedback on these AC components

is negligible because f

, being the fundamental and the

PFD

lowest frequency component, is at least 10 times higher

in frequency than the zero dB crossing of the open-loop

gain by design.

To find the fundamental reference spur-to-carrier power

ratio, f

REF_SPUR_FUND

For the 2nd harmonic reference spur, fm = 2 f

V

P-2ndHAR

= f

m

PFD

CARRIER

and:

, Em = V

= 20log

P-FUND

10

and:

K

VCO

2πC

• I_LEAKAGE

2

• f

P

PFD

PFD

, dB

, Em =

V

=

P-P

C

PFD

=

CP• f

When n = 1, the fundamental peak is:

EF_SPUR_2ndHAR

CARRIER

= 20log

10

K

• I_LEAKAGE

VCO

8πC

2

• f

P

PFD

Ratios for higher order harmonics are found using a

similar approach.

V

P-FUND

the 2nd harmonic peak is:

=

πC

• f

Active Loop Filter Example

Figure 7 shows an example implementation of an active

loop filter built around an op amp. I_LEAKAGE represents

V

P- 2ndHAR

=

2πC

• f

the combined leakage currents of the charge pump and the

and so on.

V_CP

OCXO

PLL IC

÷R

ICP_UP

PFD

I_LEAKAGE

ICP_DN

÷N

V_OCXO

Figure 7. A PLL System with an Active Loop Filter and I_Leakage Representing the Charge Pump and Op Amp Leakage Currents

LOOP FILTER

V_CP_BIAS

C

P

V_OPAMP

+

–

C

I

R

V_VCO

R

V_FILT

Z

P2

V_TUNE

C

P2

VCO

LO

FEEDBACK

AN143 F07

, dB

an143f

AN143-5

Page 6

Application Note 143

|

V_TUNE

|=|

1

P2

|

AN143 F08

op amp. The same methodology used in the passive filter

example applies here since the loop filters have a similar

structure. The addition of the pole composed of R

at the output of the op amp to limit the device’s con-

C

P2

P2

and

tribution of noise beyond 15 or 20 times the LBW reduces

the amplitude

node of the VCO. It should be noted that C

of the sawtooth signal seen at the tuning

includes the

P2

input capacitance of the VCO tune port.

The sawtooth signal undergoes low pass filtering whose

equation can be found using basic voltage division equa

-

tions in the Laplace Transform domain and can be written as:

| | | |

V_FILT

| | | |

1+j2πf•RP2•C

,

where f represents frequency in Hz.

Naturally, the sawtooth signal Fourier Series components

get affected differently according to their frequency. The

reference spur-to-carrier ratios become:

| |

V_TUNE

| |

V_FILT

2

PFD

|

1

,

REF_SPUR_FUND

CARRIER

= 20log

K

• I_LEAKAGE •|

VCO

10

2πCP• f

dBc, where

| | | |

V_TUNE

|

| | | |

V_FILT

|

1

= |

1+j2π •f

REF_SPUR_2ndHAR

CARRIER

1

• •RP2C

PFD

= 20log

|

,

P2

| |

K

• I_LEAKAGE •|

VCO

10

8πCP• f

V_TUNE

| |

V_FILT

2

PFD

|

2

,

dBc, where

| | | |

V_TUNE

|

| | | |

V_FILT

|

2

= |

1+j4π •f

1

PFD•RP2•CP2

|

, and soon.

Lab Verification of the Theory

The PLL systems shown in Figures 5 and 7 were reproduced

in the lab. External current was introduced at the charge

pump node using a precision source meter to null the

intrinsic fundamental reference spur caused by inherent

leakages in the system. Then, specific additional current

values were injected into the loop while measuring the

fundamental reference spur levels. Figure 8 compares

the measured and calculated values for both filter types.

The measured and calculated numbers agree to within the

instrument accuracies and component tolerances.

–40

–50

–60

–70

–80

–90

FUNDAMENTAL REFERENCE SPUR LEVEL (dBc)

–100

Figure 8. Comparison of Measured and Calculated Fundamental

Reference Spur Levels Using Active and Passive Loop Filters

Table 1. Details About the PLL Systems Used to Generate the

Measurements of Figure 8.

PLL IC LTC6945, 6GHz

Op Amp N/A LT1678, Low Noise, Rail-to-

VCO CVCO55CL-0902-0928,

C

(nF) 8.2 22

P

(kHz) 250 250

f

PFD

(MHz/V) 18 63

K

VCO

LBW (kHz) 7 7.6

(Ω) N/A 100

R

P2

(nF) N/A 13.3

C

P2

PASSIVE FILTER, MEASURED

PASSIVE FILTER, CALCULATED

ACTIVE FILTER, MEASURED

ACTIVE FILTER, CALCULATED

5

PASSIVE LOOP FILTER ACTIVE LOOP FILTER

Integer-N Synthesizer

from Linear

Technology

902 to 928 MHz VCO

from Crystek

25 100

10

INJECTED CURRENT (nA)

50 1000

LTC6945, 6GHz Integer-N

Synthesizer from Linear

Technology

Rail Precision Op Amp from

Linear Technology

UMS-1400-A16-G, 700-1400

MHz VCO from RFMD

AN143-6

an143f

Page 7

Application Note 143

REF_SPUR_FUND

CARRIER

PFD

|

V_TUNE

| |

|

1

REF_SPUR_2ndHAR

CARRIER

V_TUNE

| |

PFD

REF_SPUR_3rdHAR

CARRIER

| |

PFD

d

dt

∫

∫

∫

Summary of Results

Table 2 summarizes the equations derived in this application note.

Conclusion

Integer

-N PLL operation and nonidealities are important

topics in the design of RF systems. Reference spurs can

have a

significantly negative impact on overall system

performance. The simple model shown here accurately

predicts reference spur levels due to leakage current in

PLLs and can be a useful design tool, significantly reduc

ing the number of board revisions required to reach a

desired solution.

Appendix: Derivation of Spur

-to-Carrier Ratio Using

Narrowband FM Equations

Consider an FM signal centered at an LO of frequency f

c

in Hz. This signal can be written as:

e(t) = E

cos(2pfct + q(t)),

c

where E

is the peak amplitude of e(t) in V.

c

The instantaneous frequency of e(t) is:

ω

=

inst

2πfct+θ(t)

(

=2πfc+θ´(t),rad/sec

)

Since e(t) is an FM signal, the modulating signal em(t)

modulates the instantaneous frequency of e(t) as follows:

q´(t) = Ke

(t), rad/sec

m

where K is the deviation sensitivity of frequency in rad/

(sec • V):

θ(t)=

t

θ´(t)dt =

o

t

Kem(t)dt=K

o

t

em(t)dt

o

As far as this paper is concerned, the modulating signal

is a tone—one of the Fourier Series components of the

sawtooth waveform—which is given by:

(t) = Em cos(2pfmt),

e

m

where E

is the peak amplitude of em(t) in V and fm is its

m

frequency in Hz.

Table 2. Summary of Formulas to Predict Reference Spur Levels Up to the 3rd Harmonic

Loop Filter Type Passive Active

Reference to Figure 5 Figure 7

|

1

1

PFD•RP2•CP2

|

2

1

PFD•RP2•CP2

|

3

1

PFD•RP2•CP2

V_FILT

| |

V_TUNE

|

| |

V_FILT

| |

V_TUNE

|

| |

V_FILT

K

• • I_LEAKAGE |

VCO

dBc

(

)

|

|

dBc

(

)

|

2

dBc

(

)

|

3

20log

20log

20log

10

1

K

VCO

10

1

K

VCO

10

1

2πCP• f

• • I_LEAKAGE |

8πCP• f

• • I_LEAKAGE |

18πCP• f

| |

V_TUNE

| |

V_FILT

2

| |

|

1+j2π • f

| |

| |

V_FILT

2

| |

|

1+j4π • f

| |

V_TUNE

| |

V_FILT

2

| |

|

1+j6π • f

| |

|

|

|

Information furnished by Linear Technology Corporation is believed to be accurate and reliable.

However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

an143f

AN143-7

Page 8

Application Note 143

K •E

m

K

m

1

c

)

This means that the time varying component of e(t)’s

phase is:

θ(t)=K

2πK

=

where K

t

E

cos(2πf

m

∫

o

VCO•Em

sin(2πf

2πf

, in Hz/V, is the tuning sensitivity of the VCO

VCO

t)dt=

m

m

t),

2πf

m

sin(2πf

m

t)

m

used to generate e(t).

Define m as the modulation index, such as:

θ(t)=

wherem=

VCO•Em

f

m

K

VCO•Em

sin(2πfmt)=m•sin(2πfmt),

f

e(t), then, can be written as:

e(t) = E

cos(2pfct + m • sin(2pfmt)).

c

Expanding using some basic trigonometric identities gives:

e(t) = E

cos(2pfct) • cos(m • sin(2pfmt)) – Ec sin(2pfCt)

c

• sin(m • sin(2pfmt)),

m is much smaller than 1 as far as the reference spur

generation is concerned. This implies that:

cos(m • sin(2pf

and sin(m • sin(2pf

t)) ≈ 1,

m

t)) ≈ m • sin(2pfmt)

m

Then

e(t) ≈ E

cos(2pfct) – m • E

c

sin(2pfct) • sin(2pfmt),

c

or

e(t)=Eccos(2πfCt)+

–cos 2π(f

– fm)t)

(

m•Ec(cos(2π(f

2

,

+fm)t)

C

which is a narrow band FM signal composed of a carrier

and two sidebands located at ±fm centered around

at f

c

the carrier.

Based on the last representation of e(t), sideband-to-carrier

power ratio in dBc is given by:

SIDEBAND

CARRIER

=20log

10

m

2

= 20log

10

K

VCO•Em

2f

m

Bibliography

1. B. P. Lathi, “Modern Digital and Analog Communication Systems”, Third Edition, Oxford University Press,

1998, ISBN 0195110099

F. M. Gardner, “Phaselock Techniques”, Third Edition,

2.

John Wiley and Sons, 2005, ISBN 0471430633

3. Linear Technology, LTC6945 data sheet, 1630 McCarthy

Blvd., Milpitas, CA, 95035, www.linear.com

4. R. E. Best, “Phase-Locked Loops, Theory, Design, and

Applications”, Second Edition, McGraw-Hill, 1993, ISBN

0079113869

5. W. F. Egan, “Frequency Synthesis by Phase Lock”,

Second Edition, John Wiley and Sons, 2000, ISBN

0471321044

6. Z. Tranter, “Principles of Communications, Systems,

Modulation, and Noise”, Fourth Edition, John Wiley

and Sons, 1995, ISBN 0471124966

AN143-8

Linear Technology Corporation

1630 McCarthy Blvd., Milpitas, CA 95035-7417

(408) 432-1900 ● FAX: (408) 434-0507

●

www.linear.com

an143f

LT 1213 • PRINTED IN USA

LINEAR TECHNOLOGY CORPORATION 2013

Loading...

Loading...