Page 1

SERVICE MANUAL

6M83B-24E391

Page 2

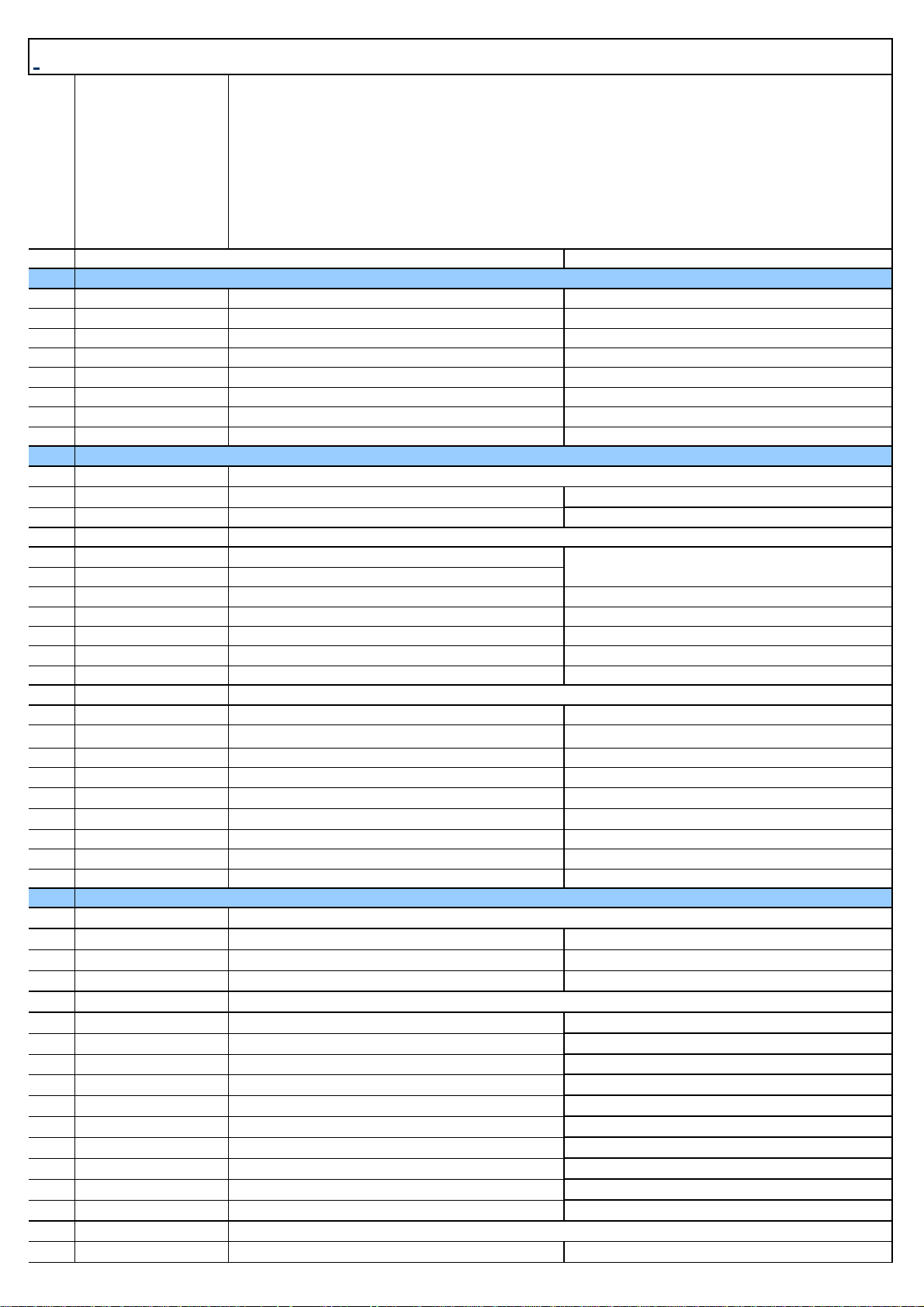

Content:

1. 6M83B SPECIFICATION

2. LIST OF KEY PARTS

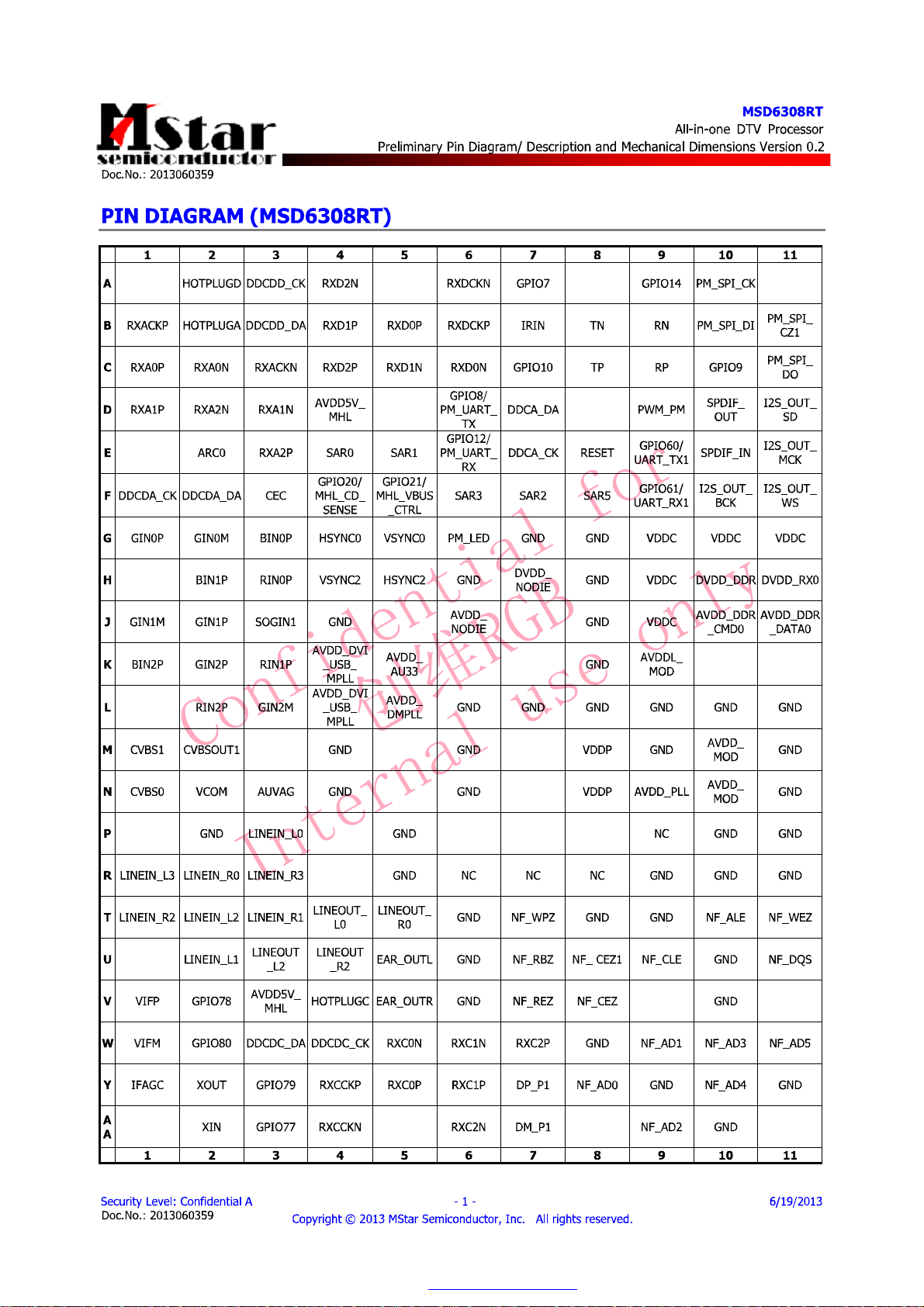

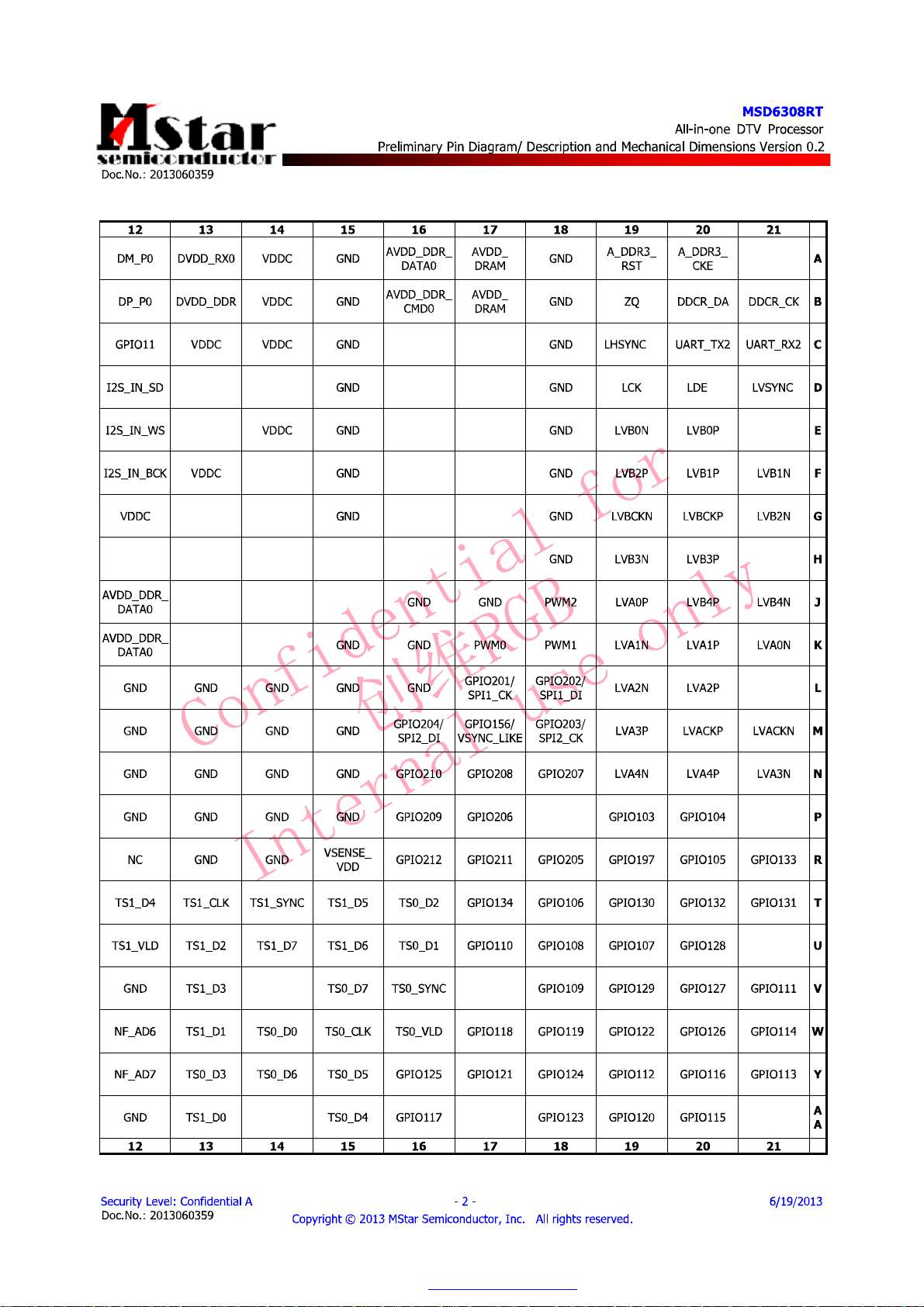

3. IC SPECIFICATION

4. BLOCK DIAGRAM

5. CIRCUIT DIAGRAM

6. MAIN PCB DRAWING

7. INSTRUCTION MANUAL

Page 3

1 Outlook

Please refer to the picture

2 Brief Information

2.1 Product Name 24E391

2.2 Chassis Name 6M83B

2.3 Solution MSD6308RTC

2.4 Key functions ISDB-T/PAL M,N

2.5 Target Market Argentina

2.6 Product Category

2.7 Product Positioning LOW END DTV

2.8 Product size \

3 Panel Specification

3.1 Model Number Model Number

3.1.1 Panel Manufacturer SKYWORTH

3.1.2 Model Number SEL240HY(QD0-210)

3.2 Mechanical Mechanical

3.2.1 Panel Size 24"

3.2.2 Dimension TBD

3.2.3 Visible Area (mm) : H x V TBD

3.2.4 Pixel Format (H × V) TBD

3.2.5 Backlight Type LED

3.2.6 Diagonal Screen Size \

3.2.7 Pixel Pitch (mm) TBD

3.3 Electronic Parameter Electronic Parameter

3.3.1 Power consuption \

3.3.2

3.3.3 Contrast Ratio \

3.3.4 Dynamic Contrast Ratio \

3.3.5 Veiwing Angle \

3.3.6 Response Time (ms) \

3.3.7 Back light Time (Hours) \

3.3.8 120Hz(100Hz)/240Hz(200Hz) \

3.3.9 3D No/PR/SG \

4 Signal Receiving System

4.1 ATV Receiving System ATV Receiving System

4.1.1 PAL BG/I/DK/NTSC-M No

4..1.2 PAL/SECAM BG/DK/I SECAM L/L" No

4.1.3 PAL M/N NTSC-M Yes

4.2 DTV Receiving System DTV Receiving System

4.2.1 ATSC No

4.2.2 DVB-T No

4.2.3 DVB-T with CI No

4.2.4 DVB-T2 No

4.2.5 DVB-T2 with CI+ No

4.2.6 ISDB-T/SBTVD-T Yes

4.2.7 DTMB No

4.2.8 DVB-C with CA No

4.2.9 DVB-S No

4.2.10 DVB-S2 No

4.3 Antenna input Antenna input

4.3.1 Antenna Input port: 1 (1 for analogue) No

Brightness (cd/m2)

\

Page 4

4.3.2

Antenna Input port: 1 (1 for both analogue and digital)

4.3.3 Antenna Input port: 2 (1 air + 1 Cable) Yes

4.3.4 Type of Antenna Input Port IEC169-2 Female

4.3.5 Receiving Frequency range (ATV)

4.3.6 Receiving Frequency range (DTV) VHF 177-213 MHZ, UHF 473-803 MHZ

4.4 External Signal Receiving System

4.4.1 Composite Input PAL 50Hz/60Hz Yes

4.4.2 SECAM Yes

4.4.3 NTSC 3.58 Yes

4.4.4 NTSC4.43 Yes

4.4.5 Component Input 480i /480p/720p/1080i (60Hz) Yes

4.4.6 576i /576p/720p/1080i (50Hz) Yes

4.4.7 1080P 24Hz/25Hz/30Hz/50Hz/60Hz Yes

4.4.8 PC Input VGA (640 x 480) Yes

4.4.9 S-VGA (800 x 600) Yes

4.4.10 XGA (1024 x 768) Yes

4.4.11 W-XGA (1280 x 768) Yes

4.4.12

4.4.13 S-XGA (1280 x 1024) Yes

4.4.14 HDMI Input 480i /480p/720p/1080i (60Hz) (Video Format) Yes/Yes/Yes/Yes

4.4.15 576i /576p/720p/1080i (50Hz) (Video Format) Yes/Yes/Yes/Yes

4.4.16 1080P 24Hz/25Hz/30Hz/50Hz/60Hz (Video Format) Yes/Yes/Yes/Yes/Yes

4.4.17 VGA (640 x 480) (PC Format) Yes

4.4.18 S-VGA (800 x 600) (PC Format) Yes

4.4.19 XGA (1024 x 768) (PC Format) Yes

4.4.20 W-XGA (1280 x 768) (PC Format) Yes

4.4.21

4.4.22 S-XGA (1280 x 1024) (PC Format) Yes

4.4.23 USB Media player formats

5 Features

5.1 Picture Picture

5.1.1 Picture Mode Normal/ Movie / Sports / User

5.1.2 Picture Display Size 4:3/16:9/Panorama/Subtitle/Movie/Native

5.1.3 Picture Freeze Yes

5.1.4 Backlight Adjust No

5.1.5 Auto Format No

5.1.6 3:2 Pull Down No

5.1.7 4:3 Stretch No

5.1.8 Comfilter 3D

5.1.9 PIP(Single tuner) No

5.1.10 Noise Reduction Off/Low/Middle/High

5.1.11 MPEG Reduction Off/Low/Middle/High

5.1.12 3D No

5.1.13 Color temperature

5.2 Sound Sound

5.2.1 Sound Mode Standard / Music / Film /News/ User

5.2.2 For personal mode:Treble/Bass/Balance No

5.2.3 Surround Yes

5.2.4 Sound Mode Standard / Music / Film / News/ User

5.2.5 Equalizer Yes

5.2.6 Audio Output Power 2 X 3W

5.2.7 NICAM No

5.2.8 A2 No

5.2.9 BTSC(MTS) Yes

5.3 Teletext Teletext

5.3.1 FLOF/TOP No

5.3.2 Memory Page No

5.3.3 Character Language No

5.3.4 Teletext Level No

5.4 Program Management Program Management

5.4.1 V-Chip No

W-XGA(1360×768)

W-XGA(1360×768)(PC Format)

54MHz~864MHz

Please see attached

Cool/ Normal/Warm/ User

No

Yes

Yes

Page 5

5.4.2 Parent Control(Child Lock) Yes

5.4.3 Closed Caption Yes

5.4.4 Subtitle Yes

5.4.5 EPG Yes

5.4.6 Channel list Yes

5.4.7 Faivorate Channel List Yes

5.4.8 Channel Editor Yes

5.4.9 On/Off timer Yes

5.4.10 Sleep timer Yes

5.4.11 Channel Swap timer No

5.4.12 Blue Screen Yes

5.5 AC Input AC Input

5.5.1 AC Input Range \

5.5.2 AC Plug Type \

5.5.3 AC Cable Length \

5.5.4 Power Consumption \

5.5.5 Standby Power Consumption <1W

5.6 HDMI HDMI

5.6.1 CEC Yes

5.6.2 ARC No

5.6.3 3D No

5.6.4 MHL Yes

5.7 Software Update Software Update

5.7.1 By USB Yes

5.7.2 By Internet Yes

5.7.3 Internet Auto search No

5.7.4 By Over-Air No

5.7.5 By other Service Port No

5.8 PVR PVR

5.8.1 By External USB or HDD Yes

5.8.2 Built in HDD No

5.8.3 Time Shift Yes

5.9 OSD Lauguage OSD Lauguage

5.9.1 OSD Lauguage English/Spanish/Portuguese

5.1O USB File System USB File System

5.10.1 FAT16 Yes

5.10.2 FAT32 Yes

5.10.3 NTFS Yes

5.11 Middleware Middleware

5.11.1 MHEG5 No

5.11.2 Ginga Yes

5.11.3 MHP No

5.12 Wifi Wifi

5.12.1 Wifi Dongle Optional

5.12.2 Wifl Built in No

6 Terminals Configuration

6.1 Teminal Direction (Side and Bottom & Side and Rear)

6.2 Wifi Wifi

6.2.1 Tuner BackX2

6.2.2 Composite Side X1

6.2.3 S-Video No

6.2.4 Full Scart No

6.2.5 Half Scart No

6.2.6 Component Side X1

6.2.7 PC input with 3.5mm mini jack audio input Side X1(same AV audio)

6.2.8 HDMI Side X1 BackX1

6.2.9 USB Side X1

6.2.10 LAN Back X1

6.2.11 CI Slot No

6.2.12 CA Slot No

Page 6

6.3 Output Output

Power on / Standby / Recording(Green / Red / Orange)

\

6.3.1 Video Output No

6.3.2 Audio Output (Fixed & Variable) Share with earphone

6.3.3 Digital Audio Output (Coaxial & Optical) No

6.3.4 Earphone Back X1

6.4 Diagram of Teminal Configuration

7 Mechanical Spec

7.1 Cabinet Cabinet

7.1.1 Cabinet color For front back stand \

7.1.2 Operation Keys / Touch sensor

7.1.3 AC Power Switch Mechanical power switch \

7.1.4

LED Indicator

7.1.5 Power on / Standby (Green / Red ) \

7.1.6

7.1.7 Program Timer / Recoding (Green / Red) \

7.1.8 On Timer or Program Timer(Green) \

7.1.9 Logo Style Silk Printing / SUS Badge (inlet type) \

7.1.10 Stand Tilt / Swivel

7.2 Dimension & Stuffing Dimension & Stuffing

7.2.1 Size (with stand)( mm ) \

7.2.2 Size (without stand) ( mm ) \

7.2.3 Package Size (with stand)(mm) \

7.2.4 Net Weight(Kg) \

7.2.5 Gross Weight \

7.2.6 Loading quantity (20GP/40GP/40GP) with pallet \

7.2.7 Loading quantity (20GP/40GP/40GP) without pallet \

7.2.8 Stand build in Packing Box (together or separately ) \

8 Accessories

8.1 Remote Controller Remote Controller

8.1.1 Type No. TBD

8.1.2 Battery TBD

8.2 Instruction Manual Instruction Manual

8.2.1 Paper size \

8.2.2 Printing Color \

8.2.3 Languages (Refer to Sales Country Sheet) \

8.2.4 Total Pages \

8.2 Others Others

8.2.1 3D Glasses \

8.2.2 Camera \

8.2.3 etc \

9 Requested Certification

9.1 CB Yes

9.2 UL \

9.3 EMC TBD

9.4 FCC \

9.5 HDMI Yes

9.6 USB No

9.7 CI+ No

9.8 Dolby No

9.9 DOLBY + No

9.10 Dvix Hometheatre \

9.11 DviX HD \

9.12 DviX+HD \

9.13 MHL No

9.14 DLNA \

9.15 CTS \

9.16 Wifi \

9.17 MPES \

9.18 Energy Star \

Power on (Green) \

Please see attached

\

Page 7

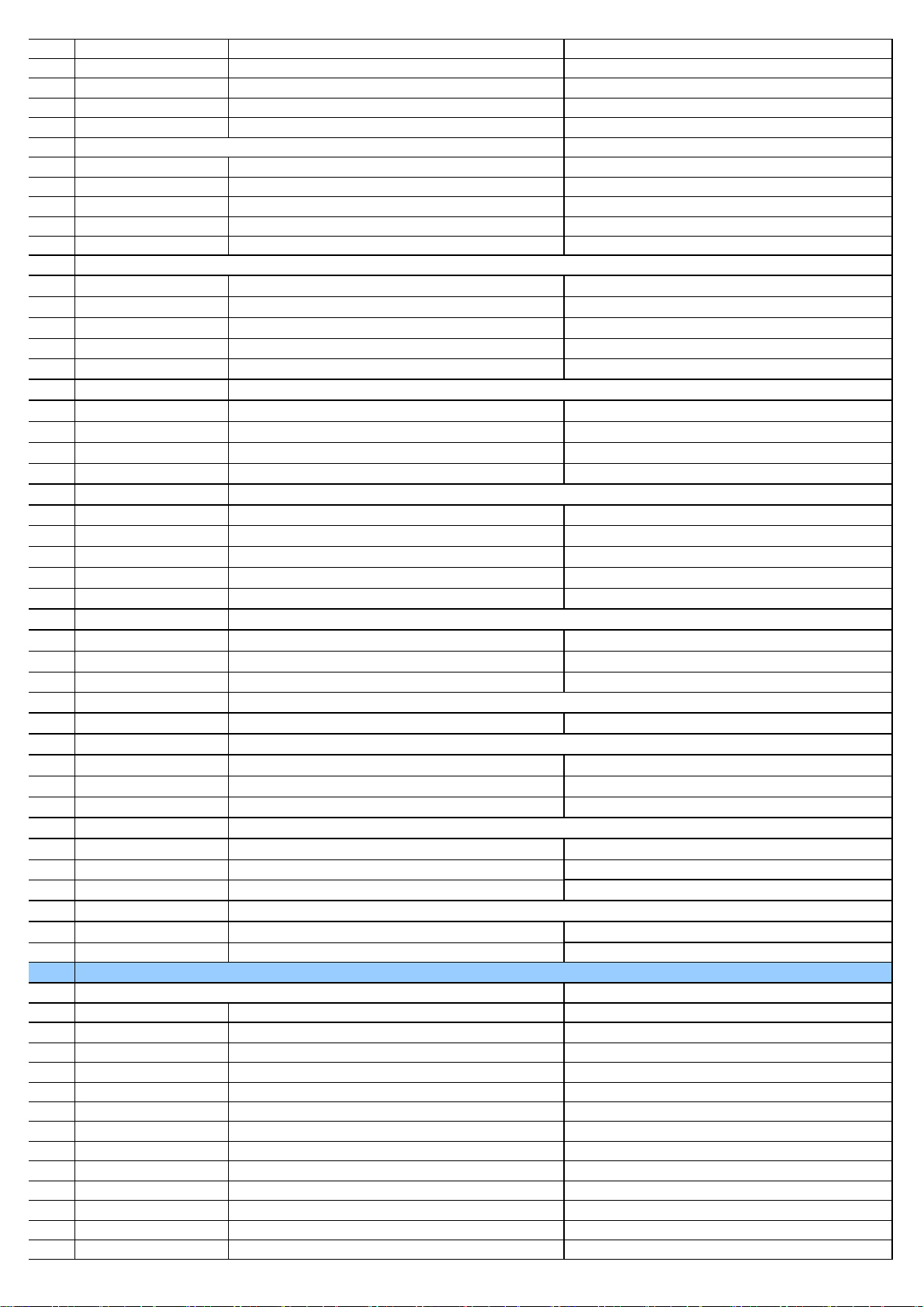

6M83B关键件清单

长周期\关键件分类 物料编号 单机用量 位号

TUNER 5219-06033D-7V00 1 T1

MAIN CHIP 475C-M63085-3690 1 U9

Nand-FLASH 4701-T581G1-0480 1 U23

AMP 4722-T31130-0280 1 U15

DC/DC 5V 476A-M14950-0080 1 U5

DC/DC 1.15V 476A-M14950-0080 1 U4

DC/DC 3.3V 476A-M14940-0080 1 U2

LDO 3.3V 47DG-L11171-0030 1 U6

LDO 1.5V 47B6-A11174-0300 1 U3

P-MOS 47D9-M94350-0080 1 U11

Page 8

Page 9

Page 10

Page 11

Page 12

Page 13

Page 14

Page 15

Page 16

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.cn

Page 17

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.cn

Page 18

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.cn

Page 19

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.cn

Page 20

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.cn

Page 21

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.cn

Page 22

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.cn

Page 23

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.cn

Page 24

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.cn

Page 25

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.cn

Page 26

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.cn

Page 27

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.cn

Page 28

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.cn

Page 29

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.cn

Page 30

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.cn

Page 31

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.cn

Page 32

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.cn

Page 33

www.ti.com

...........................................................................................................................................SLOS650B–AUGUST2009–REVISEDSEPTEMBER2009

6-WFILTER-FREESTEREOCLASS-DAUDIOPOWERAMPLIFIERWITH

1

FEATURES

2

•6-W/chintoan8-ΩLoadsat10%THD+NFrom

a10-VSupply

•12-Wintoa4-ΩMonoLoadat10%THD+N

Froma10-VSupply

•87%EfficientClass-DOperationEliminates

NeedforHeatSinks

•WideSupplyVoltageRangeAllowsOperation

from8Vto26V

•Filter-FreeOperation

•SpeakerGuard™SpeakerProtectionIncludes

AdjustablePowerLimiterplusDCProtection

•FlowThroughPinOutFacilitatesEasyBoard

Layout

•RobustPin-to-PinShortCircuitProtectionand

ThermalProtectionwithAutoRecoveryOption

•ExcellentTHD+N/Pop-FreePerformance

•FourSelectable,FixedGainSettings

•DifferentialInputs

APPLICATIONS

•Televisions

•ConsumerAudioEquipment

•Monitors

TPA3113D2

SPEAKERGUARD™

DESCRIPTION

TheTPA3113D2isa6-W(perchannel)efficient,

Class-Daudiopoweramplifierfordrivingbridged-tied

stereospeakers.AdvancedEMISuppression

Technologyenablestheuseofinexpensiveferrite

beadfiltersattheoutputswhilemeetingEMC

requirements.SpeakerGuard™speakerprotection

circuitryincludesanadjustablepowerlimiteranda

DCdetectioncircuit.Theadjustablepowerlimiter

allowstheusertoseta"virtual"voltageraillower

thanthechipsupplytolimittheamountofcurrent

throughthespeaker.TheDCdetectcircuitmeasures

thefrequencyandamplitudeofthePWMsignaland

shutsofftheoutputstageiftheinputcapacitorsare

damagedorshortsexistontheinputs.

TheTPA3113D2candrivestereospeakersaslowas

4Ω.ThehighefficiencyoftheTPA3113D2,87%,

eliminatestheneedforanexternalheatsinkwhen

playingmusic.

Theoutputsarealsofullyprotectedagainstshortsto

GND,VCC,andoutput-to-output.Theshort-circuit

protectionandthermalprotectionincludesan

auto-recoveryfeature.

OUTL+

Audio

Source

OUTL-

OUTR+

OUTR-

Figure1.TPA3113D2SimplifiedApplicationSchematic

1

Pleasebeawarethatanimportantnoticeconcerningavailability,standardwarranty,anduseincriticalapplicationsofTexas

Instrumentssemiconductorproductsanddisclaimerstheretoappearsattheendofthisdatasheet.

2SpeakerGuard,PowerPadaretrademarksofTexasInstruments.

PRODUCTIONDATAinformationiscurrentasofpublicationdate.

ProductsconformtospecificationsperthetermsoftheTexas

Instrumentsstandardwarranty.Productionprocessingdoesnot

necessarilyincludetestingofallparameters.

1 Fm

LINP

LINN

RINP

RINN

GAIN0

GAIN1

PLIMIT

PBTL

FaultFault

SDSD

TPA3113D2

OUTPL

OUTNL

OUTPR

OUTNR

PVCC

FERRITE

FERRITE

FERRITE

BEAD

BEAD

BEAD

FILTER

FILTER

FILTER

FERRITE

FERRITE

FERRITE

BEAD

BEAD

BEAD

FILTER

FILTER

FILTER

8to26V

Copyright©2009,TexasInstrumentsIncorporated

6W

6W

8W

8W

Page 34

TPA3113D2

SLOS650B–AUGUST2009–REVISEDSEPTEMBER2009...........................................................................................................................................

Thesedeviceshavelimitedbuilt-inESDprotection.Theleadsshouldbeshortedtogetherorthedeviceplacedinconductivefoam

duringstorageorhandlingtopreventelectrostaticdamagetotheMOSgates.

www.ti.com

ABSOLUTEMAXIMUMRATINGS

overoperatingfree-airtemperaturerange(unlessotherwisenoted)

V

V

T

T

T

R

ESDElectrostaticdischarge

(1)Stressesbeyondthoselistedunderabsolutemaximumratingsmaycausepermanentdamagetothedevice.Thesearestressratings

(2)TheTPA3113D2incorporatesanexposedthermalpadontheundersideofthechip.Thisactsasaheatsink,anditmustbeconnected

(3)InaccordancewithJEDECStandard22,TestMethodA114-B.

(4)InaccordancewithJEDECStandard22,TestMethodC101-A

SupplyvoltageAVCC,PVCC–0.3Vto30V

CC

SD,GAIN0,GAIN1,PBTL,FAULT

InterfacepinvoltagePLIMIT–0.3VtoGVDD+0.3V

I

RINN,RINP,LINN,LINP–0.3Vto6.3V

ContinuoustotalpowerdissipationSeeDissipationRatingTable

Operatingfree-airtemperaturerange–40°Cto85°C

A

Operatingjunctiontemperaturerange

J

Storagetemperaturerange–65°Cto150°C

stg

(2)

BTL:PVCC>15V4.8

MinimumLoadResistanceBTL:PVCC≤15V3.2

L

PBTL3.2

Humanbodymodel

Charged-devicemodel

(3)

(allpins)±2kV

(4)

only,andfunctionaloperationsofthedeviceattheseoranyotherconditionsbeyondthoseindicatedunderrecommendedoperating

conditionsisnotimplied.Exposuretoabsolute-maximum-ratedconditionsforextendedperiodsmayaffectdevicereliability.

toathermallydissipatingplaneforproperpowerdissipation.Failuretodosomayresultinthedevicegoingintothermalprotection

shutdown.SeeTITechnicalBriefsSLMA002formoreinformationaboutusingtheTSSOPthermalpad.

(1)

UNIT

–0.3VtoV

–40°Cto150°C

(allpins)±500V

+0.3V

CC

DISSIPATIONRATINGS

PACKAGE

28pinTSSOP(PWP)4.48W27.87°C/W2.33W0.72°C/W0.45°C/W

(1)Forthemostcurrentpackageandorderinginformation,seethePackageOptionAddendumattheendofthisdocument,orseetheTI

websiteatwww.ti.com.

(1)

TA≤25°CDERATINGFACTOR(θJA)TA=85°Cθ

JP

Ψ

JT

RECOMMENDEDOPERATINGCONDITIONS

overoperatingfree-airtemperaturerange(unlessotherwisenoted)

PARAMETERTESTCONDITIONSMINMAXUNIT

V

V

V

V

I

I

T

SupplyvoltagePVCC,AVCC826V

CC

High-levelinputvoltageSD,GAIN0,GAIN1,PBTL2V

IH

Low-levelinputvoltageSD,GAIN0,GAIN1,PBTL0.8V

IL

Low-leveloutputvoltageFAULT,R

OL

High-levelinputcurrentSD,GAIN0,GAIN1,PBTL,VI=2V,V

IH

Low-levelinputcurrentSD,GAIN0,GAIN1,PBTL,VI=0.8V,V

IL

Operatingfree-airtemperature–4085°C

A

=100k,VCC=26V0.8V

PULL-UP

=18V50µA

CC

=18V5µA

CC

2SubmitDocumentationFeedbackCopyright©2009,TexasInstrumentsIncorporated

ProductFolderLink(s):TPA3113D2

Page 35

www.ti.com

...........................................................................................................................................SLOS650B–AUGUST2009–REVISEDSEPTEMBER2009

DCCHARACTERISTICS

TA=25°C,V

|V

|VI=0V,Gain=36dB1.515mV

OS

I

CC

I

CC(SD)

r

DS(on)

GGain

t

on

t

OFF

GVDDGateDriveSupplyI

t

DCDET

=24V,RL=8Ω(unlessotherwisenoted)

CC

PARAMETERTESTCONDITIONSMINTYPMAXUNIT

Class-Doutputoffsetvoltage(measured

differentially)

QuiescentsupplycurrentSD=2V,noload,PV

QuiescentsupplycurrentinshutdownmodeSD=0.8V,noload,PV

V

=12V,IO=500mA,

Drain-sourceon-stateresistancemΩ

CC

TJ=25°C

GAIN1=0.8VdB

GAIN1=2VdB

=24V3250mA

CC

=24V250400µA

CC

HighSide400

Lowside400

GAIN0=0.8V192021

GAIN0=2V252627

GAIN0=0.8V313233

GAIN0=2V353637

Turn-ontimeSD=2V

Turn-offtimeSD=0.8V2µs

=100µA6.46.97.4V

GVDD

DCDetecttimeV

=6V,VRINP=0V420ms

(RINN)

DCCHARACTERISTICS

TA=25°C,V

|V

|VI=0V,Gain=36dB1.515mV

OS

I

CC

I

CC(SD)

r

DS(on)

GGain

t

ON

t

OFF

GVDDGateDriveSupplyI

V

O

=12V,RL=8Ω(unlessotherwisenoted)

CC

PARAMETERTESTCONDITIONSMINTYPMAXUNIT

Class-Doutputoffsetvoltage(measured

differentially)

QuiescentsupplycurrentSD=2V,noload,PV

QuiescentsupplycurrentinshutdownmodeSD=0.8V,noload,PV

V

=12V,IO=500mA,

Drain-sourceon-stateresistancemΩ

CC

TJ=25°C

GAIN1=0.8VdB

GAIN1=2VdB

=12V2035mA

CC

=12V200µA

CC

HighSide400

Lowside400

GAIN0=0.8V192021

GAIN0=2V252627

GAIN0=0.8V313233

GAIN0=2V353637

Turn-ontimeSD=2V

Turn-offtimeSD=0.8V2µs

=2mA6.46.97.4V

GVDD

OutputVoltagemaximumunderPLIMIT

control

V

=2V;VI=1Vrms6.757.908.75V

(PLIMIT)

TPA3113D2

14ms

14ms

Copyright©2009,TexasInstrumentsIncorporatedSubmitDocumentationFeedback3

ProductFolderLink(s):TPA3113D2

Page 36

TPA3113D2

SLOS650B–AUGUST2009–REVISEDSEPTEMBER2009...........................................................................................................................................

ACCHARACTERISTICS

TA=25°C,V

K

SVR

P

O

THD+NTotalharmonicdistortion+noiseV

V

n

SNRSignal-to-noiseratio102dB

f

OSC

=24V,RL=8Ω(unlessotherwisenoted)

CC

PARAMETERTESTCONDITIONSMINTYPMAXUNIT

PowerSupplyripplerejection–70dB

200mV

Gain=20dB,Inputsac-coupledtoAGND

ContinuousoutputpowerTHD+N=10%,f=1kHz,V

CC

Outputintegratednoise20Hzto22kHz,A-weightedfilter,Gain=20dB

rippleat1kHz,

PP

=10V6W

CC

=16V,f=1kHz,PO=3W(half-power)0.07%

65µV

–80dBV

CrosstalkVO=1Vrms,Gain=20dB,f=1kHz–100dB

MaximumoutputatTHD+N<1%,f=1kHz,

Gain=20dB,A-weighted

Oscillatorfrequency250310350kHz

Thermaltrippoint150°C

Thermalhysteresis15°C

ACCHARACTERISTICS

TA=25°C,V

K

SVR

THD+NTotalharmonicdistortion+noiseRL=8Ω,f=1kHz,PO=3W(half-power)0.06%

V

n

SNRSignal-to-noiseratio102dB

f

OSC

=12V,RL=8Ω(unlessotherwisenoted)

CC

PARAMETERTESTCONDITIONSMINTYPMAXUNIT

Supplyripplerejection–70dB

200mV

Gain=20dB,Inputsac-coupledtoAGND

Outputintegratednoise20Hzto22kHz,A-weightedfilter,Gain=20dB

ripplefrom20Hz–1kHz,

PP

65µV

–80dBV

CrosstalkPo=1W,Gain=20dB,f=1kHz–100dB

MaximumoutputatTHD+N<1%,f=1kHz,

Gain=20dB,A-weighted

Oscillatorfrequency250310350kHz

Thermaltrippoint150°C

Thermalhysteresis15°C

www.ti.com

PWP(TSSOP)PACKAGE

(TOPVIEW)

SD

FAULT

LINP

LINN

GAIN0

GAIN1

AVCC

AGND

GVDD

PLIMIT

RINN

RINP

NC

PBTL

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

PVCCL

PVCCL

BSPL

OUTPL

PGND

OUTNL

BSNL

BSNR

OUTNR

PGND

OUTPR

BSPR

PVCCR

PVCCR

4SubmitDocumentationFeedbackCopyright©2009,TexasInstrumentsIncorporated

ProductFolderLink(s):TPA3113D2

Page 37

www.ti.com

...........................................................................................................................................SLOS650B–AUGUST2009–REVISEDSEPTEMBER2009

PINFUNCTIONS

PIN

NAME

SD

FAULT2O

LINP3IPositiveaudioinputforleftchannel.Biasedat3V.

LINN4INegativeaudioinputforleftchannel.Biasedat3V.

GAIN05IGainselectleastsignificantbit.TTLlogiclevelswithcompliancetoAVCC.

GAIN16IGainselectmostsignificantbit.TTLlogiclevelswithcompliancetoAVCC.

AVCC7PAnalogsupply

AGND8Analogsignalground.Connecttothethermalpad.

GVDD9O

PLIMIT10I

RINN11INegativeaudioinputforrightchannel.Biasedat3V.

RINP12IPositiveaudioinputforrightchannel.Biasedat3V.

NC13Notconnected

PBTL14IParallelBTLmodeswitch

PVCCR15P

PVCCR16P

BSPR17IBootstrapI/Oforrightchannel,positivehigh-sideFET.

OUTPR18OClass-DH-bridgepositiveoutputforrightchannel.

PGND19PowergroundfortheH-bridges.

OUTNR20OClass-DH-bridgenegativeoutputforrightchannel.

BSNR21IBootstrapI/Oforrightchannel,negativehigh-sideFET.

BSNL22IBootstrapI/Oforleftchannel,negativehigh-sideFET.

OUTNL23OClass-DH-bridgenegativeoutputforleftchannel.

PGND24PowergroundfortheH-bridges.

OUTPL25OClass-DH-bridgepositiveoutputforleftchannel.

BSPL26IBootstrapI/Oforleftchannel,positivehigh-sideFET.

PVCCL27P

PVCCL28P

Pin

Number

1I

I/O/PDESCRIPTION

Shutdownlogicinputforaudioamp(LOW=outputsHi-Z,HIGH=outputs

enabled).TTLlogiclevelswithcompliancetoAVCC.

Opendrainoutputusedtodisplayshortcircuitordcdetectfaultstatus.Voltage

complianttoAVCC.Shortcircuitfaultscanbesettoauto-recoverybyconnecting

FAULTpintoSDpin.Otherwise,bothshortcircuitfaultsanddcdetectfaultsmust

beresetbycyclingPVCC.

High-sideFETgatedrivesupply.Nominalvoltageis7V.Alsoshouldbeusedas

supplyforPLIMITfunction

Powerlimitleveladjust.ConnectaresistordividerfromGVDDtoGNDtoset

powerlimit.ConnectdirectlytoGVDDfornopowerlimit.

PowersupplyforrightchannelH-bridge.Rightchannelandleftchannelpower

supplyinputsareconnectinternally.

PowersupplyforrightchannelH-bridge.Rightchannelandleftchannelpower

supplyinputsareconnectinternally.

PowersupplyforleftchannelH-bridge.Rightchannelandleftchannelpower

supplyinputsareconnectinternally.

PowersupplyforleftchannelH-bridge.Rightchannelandleftchannelpower

supplyinputsareconnectinternally.

TPA3113D2

Copyright©2009,TexasInstrumentsIncorporatedSubmitDocumentationFeedback5

ProductFolderLink(s):TPA3113D2

Page 38

TPA3113D2

SLOS650B–AUGUST2009–REVISEDSEPTEMBER2009...........................................................................................................................................

FUNCTIONALBLOCKDIAGRAM

www.ti.com

LINP

LINN

FAULT

GAIN0

GAIN1

PLIMIT

AVCC

GVDD

RINN

RINP

GVDD

PVCCL

PBTL Select

Gate

Drive

OUTPL FB

Logic

PWM

Logic

PWM

Logic

SC Detect

DC Detect

Thermal

Detect

UVLO/OVLO

PVCCL

PVCCL

PVCCL

Gate

Drive

Gate

Drive

GVDD

GVDD

GVDD

Gain

Control

OUTNL FB

SD

TTL

Buffer

LDO

Regulator

OUTNN FB

Gain

Control

OUTNP FB

Gain

Control

AVDD

GVDD

PLIMIT

Reference

Ramp

Generator

PLIMIT

PLIMIT

Biases and

References

Startup Protection

PVCCL

PVCCL

PVCCL

PVCCL

BSPL

OUTPL FB

OUTPL

PGND

BSNL

OUTNL FB

OUTNL

PGND

BSNR

OUTNR

OUTNR FB

PGND

BSPR

AGND

PBTL

TTL

Buffer

PBTL

Select

PBTL Select

Gate

Drive

OUTPR

OUTPR FB

PGND

6SubmitDocumentationFeedbackCopyright©2009,TexasInstrumentsIncorporated

ProductFolderLink(s):TPA3113D2

Page 39

TPA3113D2

www.ti.com

(AllMeasurementstakenat1kHz,unlessotherwisenoted.MeasurementsweremadeusingtheTPA3113D2EVMwhichis

...........................................................................................................................................SLOS650B–AUGUST2009–REVISEDSEPTEMBER2009

TYPICALCHARACTERISTICS

availableatti.com.)

TOTALHARMONICDISTORTIONTOTALHARMONICDISTORTION

vsvs

FREQUENCY(BTL)FREQUENCY(BTL)

10

Gain = 20 dB

VCC = 12 V

ZL = 8 Ω + 66 µH

1

0.1

PO = 5 W

0.01

PO = 0.5 W

THD − Total Harmonic Distortion − %

PO = 2.5 W

0.001

20 100 1k 10k

f − Frequency − Hz

Figure2.Figure3.

TOTALHARMONICDISTORTIONTOTALHARMONICDISTORTION

vsvs

FREQUENCY(BTL)FREQUENCY(BTL)

10

Gain=20dB

VCC=24V

=8 W +66 Hm

Z

− %

L

1

20k

10

− %

0.1

otalHarmonicDistortion

0.01

THD − T

0.001

G001

10

Gain=20dB

VCC=18V

Z

=8 W +66 Hm

L

1

PO=1W

PO=5W

20 100 1k 10k

f − Frequency − Hz

Gain = 20 dB

VCC = 12 V

ZL = 6 Ω + 47 µH

1

20k

G002

0.1

otalHarmonicDistortion

0.01

THD − T

PO=1W

0.1

PO = 5 W

0.01

THD − Total Harmonic Distortion − %

PO = 0.5 W

PO = 2.5 W

PO=5W

0.001

20 100 1k 10k

f − Frequency − Hz

20k

G003

0.001

20 100 1k 10k

f − Frequency − Hz

20k

Figure4.Figure5.

Copyright©2009,TexasInstrumentsIncorporatedSubmitDocumentationFeedback7

ProductFolderLink(s):TPA3113D2

G004

Page 40

TPA3113D2

SLOS650B–AUGUST2009–REVISEDSEPTEMBER2009...........................................................................................................................................

TYPICALCHARACTERISTICS(continued)

(AllMeasurementstakenat1kHz,unlessotherwisenoted.MeasurementsweremadeusingtheTPA3113D2EVMwhichis

availableatti.com.)

www.ti.com

TOTALHARMONICDISTORTIONTOTALHARMONICDISTORTION

vsvs

FREQUENCY(BTL)FREQUENCY(BTL)

10

Gain=20dB

VCC=18V

Z

=6 W +47 Hm

L

1

0.1

0.01

THD − TotalHarmonicDistortion − %

PO=1W

PO=5W

0.001

20 100 1k 10k

f − Frequency − Hz

Figure6.Figure7.

TOTALHARMONICDISTORTION+NOISETOTALHARMONICDISTORTION+NOISE

vsvs

OUTPUTPOWER(BTL)OUTPUTPOWER(BTL)

10

Gain = 20 dB

VCC = 12 V

ZL = 8 Ω + 66 µH

1

20k

10

− %

0.1

0.01

THD − TotalHarmonicDistortion

0.001

G005

10

Gain=20dB

VCC=12V

Z

=4 W +33 Hm

L

1

PO=1W

PO=5W

20 100 1k 10k

f − Frequency − Hz

Gain = 20 dB

VCC = 18 V

ZL = 8 Ω + 66 µH

1

20k

G006

0.1

f = 1 kHz

0.01

THD+N − Total Harmonic Distortion + Noise − %

0.001

0.01 0.1 1

PO − Output Power − W

f = 20 Hz

f = 10 kHz

10

0.1

0.01

THD+N − Total Harmonic Distortion + Noise − %

0.001

0.01 0.1 1 10

G007

f = 1 kHz

f = 10 kHz

PO − Output Power − W

f = 20 Hz

Figure8.Figure9.

8SubmitDocumentationFeedbackCopyright©2009,TexasInstrumentsIncorporated

ProductFolderLink(s):TPA3113D2

G008

Page 41

TPA3113D2

www.ti.com

(AllMeasurementstakenat1kHz,unlessotherwisenoted.MeasurementsweremadeusingtheTPA3113D2EVMwhichis

availableatti.com.)

...........................................................................................................................................SLOS650B–AUGUST2009–REVISEDSEPTEMBER2009

TYPICALCHARACTERISTICS(continued)

TOTALHARMONICDISTORTION+NOISETOTALHARMONICDISTORTION+NOISE

vsvs

OUTPUTPOWER(BTL)OUTPUTPOWER(BTL)

10

Gain = 20 dB

VCC = 24 V

ZL = 8 Ω + 66 µH

1

f = 1 kHz

0.1

0.01

f = 20 Hz

THD+N − Total Harmonic Distortion + Noise − %

f = 10 kHz

0.001

0.01 0.1 1 10

PO − Output Power − W

Figure10.Figure11.

TOTALHARMONICDISTORTION+NOISETOTALHARMONICDISTORTION+NOISE

vsvs

OUTPUTPOWER(BTL)OUTPUTPOWER(BTL)

10

Gain = 20 dB

VCC = 18 V

ZL = 6 Ω + 47 µH

1

10

Gain = 20 dB

VCC = 12 V

ZL = 6 Ω + 47 µH

1

0.1

0.01

THD+N − Total Harmonic Distortion + Noise − %

f = 10 kHz

0.001

0.01 0.1 1 10

G009

10

Gain = 20 dB

VCC = 12 V

ZL = 4 Ω + 33 µH

1

f = 1 kHz

f = 20 Hz

PO − Output Power − W

G010

f = 1 kHz

0.1

f = 20 Hz

0.01

THD+N − Total Harmonic Distortion + Noise − %

f = 10 kHz

0.001

0.01 0.1 1 10

PO − Output Power − W

0.1

0.01

THD+N − Total Harmonic Distortion + Noise − %

0.001

0.01 0.1 1 10

G011

f = 20 Hz

PO − Output Power − W

f = 1 kHz

f = 10 kHz

Figure12.Figure13.

Copyright©2009,TexasInstrumentsIncorporatedSubmitDocumentationFeedback9

ProductFolderLink(s):TPA3113D2

G012

Page 42

TPA3113D2

SLOS650B–AUGUST2009–REVISEDSEPTEMBER2009...........................................................................................................................................

TYPICALCHARACTERISTICS(continued)

(AllMeasurementstakenat1kHz,unlessotherwisenoted.MeasurementsweremadeusingtheTPA3113D2EVMwhichis

availableatti.com.)

www.ti.com

MAXIMUMOUTPUTPOWEROUTPUTPOWER

vsvs

PLIMITVOLTAGE(BTL)PLIMITVOLTAGE(BTL)

16

Gain = 20 dB

VCC = 24 V

14

ZL = 8 Ω + 66 µH

12

35

Gain = 20 dB

VCC = 12 V

30

ZL = 4 Ω + 33 µH

25

10

20

8

15

6

− Maximum Output Power − W

4

O(Max)

P

2

0

0.0 0.5 1.0 1.5 2.0 2.5 3.0

V

− PLIMIT Voltage − V

PLIMIT

− Output Power − W

O

P

G013

10

5

0

0 1 2 3 4 5 6

V

− PLIMIT Voltage − V

PLIMIT

Note:DashedlinerepresentsthermallylimitedNote:Dashedlinerepresentsthermallylimited

region.region.

Figure14.Figure15.

G014

GAIN/PHASEEFFICIENCY

vsvs

FREQUENCY(BTL)OUTPUTPOWER(BTL)

40

35

30

25

20

Gain − dB

15

CI = 1 µF

Gain = 20 dB

10

Filter = Audio Precision AUX-0025

VCC = 12 V

5

VI = 0.1 Vrms

ZL = 8 Ω + 66 µH

0

20 100 10k 100k

Phase

Gain

1k

f − Frequency − Hz

Figure16.

100

50

0

−50

−100

−150

−200

−250

−300

100

90

80

70

60

50

Phase − °

40

η − Efficiency − %

30

20

10

0

G015

0 1 2 3 4 5 6 7 8 9 10

PO − Output Power − W

Note:Dashedlinesrepresentthermallylimited

region.

VCC = 12 V

VCC = 18 V

VCC = 24 V

Gain = 20 dB

ZL = 8 Ω + 66 µH

G018

Figure17.

10SubmitDocumentationFeedbackCopyright©2009,TexasInstrumentsIncorporated

ProductFolderLink(s):TPA3113D2

Page 43

TPA3113D2

www.ti.com

(AllMeasurementstakenat1kHz,unlessotherwisenoted.MeasurementsweremadeusingtheTPA3113D2EVMwhichis

availableatti.com.)

...........................................................................................................................................SLOS650B–AUGUST2009–REVISEDSEPTEMBER2009

TYPICALCHARACTERISTICS(continued)

EFFICIENCYEFFICIENCY

OUTPUTPOWER(BTLwithLCFILTER)OUTPUTPOWER(BTL)

100

vsvs

100

90

80

70

60

50

40

η − Efficiency − %

30

20

10

0

0 1 2 3 4 5 6 7 8 9 10

VCC = 12 V

VCC = 24 V

Gain = 20 dB

LC Filter = 22 µH + 0.68 µF

RL = 8 Ω

PO − Output Power − W

VCC = 18 V

G032

90

VCC = 12 V

80

70

60

50

40

η − Efficiency − %

30

20

10

0

0 1 2 3 4 5 6 7 8 9 10

PO − Output Power − W

Note:DashedlinesrepresentthermallylimitedNote:Dashedlinesrepresentthermallylimited

region.region.

Figure18.Figure19.

EFFICIENCYEFFICIENCY

vsvs

OUTPUTPOWER(BTLwithLCFILTER)OUTPUTPOWER(BTL)

100

90

80

70

VCC = 12 V

VCC = 18 V

100

90

80

70

Gain = 20 dB

VCC = 12 V

ZL = 4 Ω + 33 µH

VCC = 18 V

Gain = 20 dB

ZL = 6 Ω + 47 µH

G019

60

50

40

η − Efficiency − %

30

20

10

Gain = 20 dB

LC Filter = 22 µH + 0.68 µF

RL = 6 Ω

0

0 1 2 3 4 5 6 7 8 9 10

PO − Output Power − W

G033

60

50

40

η − Efficiency − %

30

20

10

0

0 1 2 3 4 5 6 7 8 9 10

PO − Output Power − W

Note:DashedlinesrepresentthermallylimitedNote:Dashedlinerepresentsthermallylimited

region.region.

Figure20.Figure21.

Copyright©2009,TexasInstrumentsIncorporatedSubmitDocumentationFeedback11

ProductFolderLink(s):TPA3113D2

G020

Page 44

TPA3113D2

SLOS650B–AUGUST2009–REVISEDSEPTEMBER2009...........................................................................................................................................

TYPICALCHARACTERISTICS(continued)

(AllMeasurementstakenat1kHz,unlessotherwisenoted.MeasurementsweremadeusingtheTPA3113D2EVMwhichis

availableatti.com.)

EFFICIENCYSUPPLYCURRENT

OUTPUTPOWER(BTLwithLCFILTER)TOTALOUTPUTPOWER(BTL)

100

90

80

vsvs

1.2

Gain = 20 dB

ZL = 8 Ω + 66 µH

1.0

www.ti.com

70

0.8

VCC = 12 V

60

50

0.6

VCC = 18 V

40

η − Efficiency − %

30

20

10

Gain = 20 dB

LC Filter = 22 µH + 0.68 µF

RL = 4 Ω

0

0 1 2 3 4 5 6 7 8 9 10

PO − Output Power − W

− Supply Current − A

CC

I

G034

0.4

0.2

0.0

0 1 2 3 4 5 6 7 8 9 10

P

− Total Output Power − W

O(Tot)

Note:DashedlinerepresentsthermallylimitedNote:Dashedlinesrepresentthermallylimited

region.region.

Figure22.Figure23.

CROSSTALKSUPPLYRIPPLEREJECTIONRATIO

vsvs

FREQUENCY(BTL)FREQUENCY(BTL)

−20

−30

−40

Gain = 20 dB

VCC = 12 V

VO = 1 Vrms

ZL = 8 Ω + 66 µH

0

−20

Gain = 20 dB

V

= 200 mV

ripple

ZL = 8 Ω + 66 µH

pp

−50

−60

−40

VCC = 24 V

G021

−70

−80

Crosstalk − dB

−90

−60

Right to Left

−80

VCC = 12 V

−100

−110

Left to Right

−120

−130

20 100 1k 10k 20k

f − Frequency − Hz

− Supply Ripple Rejection Ratio − dB

−100

SVR

K

−120

20 100 1k 10k 20k

G023

f − Frequency − Hz

Figure24.Figure25.

12SubmitDocumentationFeedbackCopyright©2009,TexasInstrumentsIncorporated

ProductFolderLink(s):TPA3113D2

G024

Page 45

TPA3113D2

www.ti.com

(AllMeasurementstakenat1kHz,unlessotherwisenoted.MeasurementsweremadeusingtheTPA3113D2EVMwhichis

availableatti.com.)

...........................................................................................................................................SLOS650B–AUGUST2009–REVISEDSEPTEMBER2009

TYPICALCHARACTERISTICS(continued)

TOTALHARMONICDISTORTIONTOTALHARMONICDISTORTION+NOISE

vsvs

FREQUENCY(PBTL)OUTPUTPOWER(PBTL)

10

Gain=20dB

VCC=12V

Z

=4 W +33 Hm

L

1

PO=5W

0.1

0.01

THD − TotalHarmonicDistortion − %

PO=2.5W

0.001

20 100 1k 10k

f − Frequency − Hz

Figure26.Figure27.

GAIN/PHASEEFFICIENCY

vsvs

FREQUENCY(PBTL)OUTPUTPOWER(PBTL)

40

35

30

25

20

Gain − dB

15

CI = 1 µF

Gain = 20 dB

10

Filter = Audio Precision AUX-0025

VCC = 24 V

5

VI = 0.1 Vrms

ZL = 8 Ω + 66 µH

0

20 100 10k 100k1k

Phase

Gain

f − Frequency − Hz

Figure28.Figure29.

PO=0.5W

20k

100

50

0

−50

−100

−150

−200

−250

−300

G025

G027

TotalHarmonicDistortion+Noise − %

THD+N −

0.001

Phase − °

η − Efficiency − %

10

Gain=20dB

VCC=12V

Z

=4 W +33 Hm

L

1

f=1kHz

0.1

0.01

f=20Hz

f=10kHz

0.01 0.1 1 10

PO− OutputPower − W

100

90

80

VCC = 12 V

VCC = 18 V

70

60

50

40

30

20

10

Gain = 20 dB

ZL = 4 Ω + 33 µH

0

0 1 2 3 4 5 6 7 8 9 10

PO − Output Power − W

50

G026

G029

Copyright©2009,TexasInstrumentsIncorporatedSubmitDocumentationFeedback13

ProductFolderLink(s):TPA3113D2

Page 46

TPA3113D2

SLOS650B–AUGUST2009–REVISEDSEPTEMBER2009...........................................................................................................................................

TYPICALCHARACTERISTICS(continued)

(AllMeasurementstakenat1kHz,unlessotherwisenoted.MeasurementsweremadeusingtheTPA3113D2EVMwhichis

availableatti.com.)

www.ti.com

SUPPLYCURRENTSUPPLYRIPPLEREJECTIONRATIO

vsvs

OUTPUTPOWER(PBTL)FREQUENCY(PBTL)

1.0

Gain = 20 dB

0.9

ZL = 4 Ω + 33 µH

0.8

0.7

0.6

VCC = 12 V

0.5

0.4

− Supply Current − A

0.3

CC

I

VCC = 18 V

0.2

0.1

0.0

0 1 2 3 4 5 6 7 8 9 10

PO − Output Power − W

Figure30.Figure31.

0

Gain = 20 dB

V

= 200 mV

ripple

ZL = 8 Ω + 66 µH

−20

−40

−60

−80

− Supply Ripple Rejection Ratio − dB

−100

SVR

K

−120

20 100 1k 10k 20k

G030

pp

VCC = 12 V

f − Frequency − Hz

G031

14SubmitDocumentationFeedbackCopyright©2009,TexasInstrumentsIncorporated

ProductFolderLink(s):TPA3113D2

Page 47

TPA3113D2

www.ti.com

GainSettingViaGAIN0andGAIN1Inputs

ThegainoftheTPA3113D2issetbytwoinputterminals,GAIN0andGAIN1.

ThegainslistedinTable1arerealizedbychangingthetapsontheinputresistorsandfeedbackresistorsinside

theamplifier.Thiscausestheinputimpedance(Z

arecontrolledbyratiosofresistors,sothegainvariationfrompart-to-partissmall.However,theinputimpedance

frompart-to-partatthesamegainmayshiftby±20%duetoshiftsintheactualresistanceoftheinputresistors.

Fordesignpurposes,theinputnetwork(discussedinthenextsection)shouldbedesignedassuminganinput

impedanceof7.2kΩ,whichistheabsoluteminimuminputimpedanceoftheTPA3113D2.Atthelowergain

settings,theinputimpedancecouldincreaseashighas72kΩ

...........................................................................................................................................SLOS650B–AUGUST2009–REVISEDSEPTEMBER2009

DEVICEINFORMATION

)tobedependentonthegainsetting.Theactualgainsettings

I

Table1.GainSetting

GAIN1GAIN0

002060

012630

103215

11369

AMPLIFIERGAIN(dB)

TYPTYP

INPUTIMPEDANCE

(kΩ)

SDOperation

TheTPA3113D2employsashutdownmodeofoperationdesignedtoreducesupplycurrent(I

minimumlevelduringperiodsofnonuseforpowerconservation.TheSDinputterminalshouldbeheldhigh(see

specificationtablefortrippoint)duringnormaloperationwhentheamplifierisinuse.PullingSDlowcausesthe

outputstomuteandtheamplifiertoenteralow-currentstate.NeverleaveSDunconnected,becauseamplifier

operationwouldbeunpredictable.

Forthebestpower-offpopperformance,placetheamplifierintheshutdownmodepriortoremovingthepower

supplyvoltage.

)totheabsolute

CC

PLIMIT

Thevoltageatpin10canusedtolimitthepowertolevelsbelowthatwhichispossiblebasedonthesupplyrail.

AddaresistordividerfromGVDDtogroundtosetthevoltageatthePLIMITpin.Anexternalreferencemayalso

beusediftightertoleranceisrequired.Alsoadda1µFcapacitorfrompin10toground.

Vinput

PLIMIT =6.96VPout=11.8W

PLIMIT =3VPout=10W

PLIMIT =1.8VPout=5W

TPA3110D1PowerLimitFunction

Vin=1.13 Freq=1kHzRLoad=8WV

PP

Figure32.PLIMITCircuitOperation

Copyright©2009,TexasInstrumentsIncorporatedSubmitDocumentationFeedback15

ProductFolderLink(s):TPA3113D2

Page 48

TPA3113D2

SLOS650B–AUGUST2009–REVISEDSEPTEMBER2009...........................................................................................................................................

ThePLIMITcircuitsetsalimitontheoutputpeak-to-peakvoltage.Thelimitingisdonebylimitingthedutycycle

tofixedmaximumvalue.Thislimitcanbethoughtofasa"virtual"voltagerailwhichislowerthanthesupply

connectedtoPVCC.This"virtual"railis4timesthevoltageatthePLIMITpin.Thisoutputvoltagecanbeusedto

calculatethemaximumoutputpowerforagivenmaximuminputvoltageandspeakerimpedance.

æ ö

æ ö

R

ç ÷

ç ÷

ç ÷

è ø

P = for unclipped power

OUT

è ø

L

R + 2 x R

L S

2 x R

L

x V

2

P

Where:

R

isthetotalseriesresistanceincludingR

S

R

istheloadresistance.

L

V

isthepeakamplitudeoftheoutputpossiblewithinthesupplyrail.

P

V

=4×PLIMITvoltageifPLIMIT<4×V

P

P

(10%THD)=1.25×P

OUT

(unclipped)

OUT

,andanyresistanceintheoutputfilter.

DS(on)

P

Table2.PLIMITTypicalOperation

TESTCONDITIONS()PLIMITVOLTAGE

PVCC=24V,Vin=1Vrms,1.62514

RL=8Ω,Gain=26dB

PVCC=24V,Vin=1Vrms,1.86514.8

RL=8Ω,Gain=20dB

PVCC=12V,Vin=1Vrms,1.76515

RL=8Ω,Gain=20dB

OUTPUTPOWEROUTPUTVOLTAGEAMPLITUDE

(W)(V

)

P-P

www.ti.com

(1)

GVDDSupply

TheGVDDSupplyisusedtopowerthegatesoftheoutputfullbridgetransistors.Itcanalsobeusedtosupply

thePLIMITvoltagedividercircuit.Adda1µFcapacitortogroundatthispin.

DCDetect

TPA3113D2hascircuitrywhichwillprotectthespeakersfromDCcurrentwhichmightoccurduetodefective

capacitorsontheinputorshortsontheprintedcircuitboardattheinputs.ADCdetectfaultwillbereportedon

theFAULTpinasalowstate.TheDCDetectfaultwillalsocausetheamplifiertoshutdownbychangingthe

stateoftheoutputstoHi-Z.TocleartheDCDetectitisnecessarytocyclethePVCCsupply.CyclingSDwill

NOTclearaDCdetectfault.

ADCDetectFaultisissuedwhentheoutputdifferentialduty-cycleofeitherchannelexceeds14%(forexample,

+57%,-43%)formorethan420msecatthesamepolarity.ThisfeatureprotectsthespeakerfromlargeDC

currentsorACcurrentslessthan2Hz.ToavoidnuisancefaultsduetotheDCdetectcircuit,holdtheSDpinlow

atpower-upuntilthesignalsattheinputsarestable.Also,takecaretomatchtheimpedanceseenatthepositive

andnegativeinputstoavoidnuisanceDCdetectfaults.

TheminimumdifferentialinputvoltagesrequiredtotriggertheDCdetectareshowintable2.Theinputsmust

remainatorabovethevoltagelistedinthetableformorethan420msectotriggertheDCdetect.

16SubmitDocumentationFeedbackCopyright©2009,TexasInstrumentsIncorporated

ProductFolderLink(s):TPA3113D2

Page 49

TPA3113D2

www.ti.com

PBTLSelect

TPA3113D2offersthefeatureofparallelBTLoperationwithtwooutputsofeachchannelconnecteddirectly.If

thePBTLpin(pin14)istiedhigh,thepositiveandnegativeoutputsofeachchannel(leftandright)are

synchronizedandinphase.TooperateinthisPBTL(mono)mode,applytheinputsignaltotheRIGHTinputand

placethespeakerbetweentheLEFTandRIGHToutputs.Connectthepositiveandnegativeoutputtogetherfor

bestefficiency.ForanexampleofthePBTLconnection,seetheschematicintheAPPLICATIONINFORMATION

section.

FornormalBTLoperation,connectthePBTLpintolocalground.

Short-CircuitProtectionandAutomaticRecoveryFeature

TPA3113D2hasprotectionfromovercurrentconditionscausedbyashortcircuitontheoutputstage.Theshort

circuitprotectionfaultisreportedontheFAULTpinasalowstate.TheamplifieroutputsareswitchedtoaHi-Z

statewhentheshortcircuitprotectionlatchisengaged.ThelatchcanbeclearedbycyclingtheSDpinthrough

thelowstate.

Ifautomaticrecoveryfromtheshortcircuitprotectionlatchisdesired,connecttheFAULTpindirectlytotheSD

pin.ThisallowstheFAULTpinfunctiontoautomaticallydrivetheSDpinlowwhichclearstheshort-circuit

protectionlatch.

...........................................................................................................................................SLOS650B–AUGUST2009–REVISEDSEPTEMBER2009

Table3.DCDetectThreshold

AV(dB)Vin(mV,differential)

20112

2656

3228

3617

ThermalProtection

ThermalprotectionontheTPA3113D2preventsdamagetothedevicewhentheinternaldietemperature

exceeds150°C.Thereisa±15°Ctoleranceonthistrippointfromdevicetodevice.Oncethedietemperature

exceedsthethermalsetpoint,thedeviceentersintotheshutdownstateandtheoutputsaredisabled.Thisisnot

alatchedfault.Thethermalfaultisclearedoncethetemperatureofthedieisreducedby15°C.Thedevice

beginsnormaloperationatthispointwithnoexternalsysteminteraction.

ThermalprotectionfaultsareNOTreportedontheFAULTterminal.

Copyright©2009,TexasInstrumentsIncorporatedSubmitDocumentationFeedback17

ProductFolderLink(s):TPA3113D2

Page 50

TPA3113D2

SLOS650B–AUGUST2009–REVISEDSEPTEMBER2009...........................................................................................................................................

APPLICATIONINFORMATION

PVCC

www.ti.com

Control

System

Audio

Source

PVCC

1 Fm

10 kΩ

1 kΩ

10 Ω

1 Fm

100 μF 0.1 μF

100 kΩ

1 Fm

1 Fm

1 Fm

1 Fm

1 Fm

10 kΩ

10

11

12

13

14

1

2

3

4

5

6

7

8

9

SD

FAULT

LINP

LINN

GAIN0

GAIN1

AVCC

AGND

GVDD

PLIMIT

RINN

RINP

NC

PBTL

TPA3113D2

GND

29

PowerPAD

OUTNR

OUTPR

PVCCR

PVCCR

PVCCL

PVCCL

BSPL

OUTPL

PGND

OUTNL

BSNL

BSNR

PGND

BSPR

28

27

26

25

24

23

22

21

20

19

18

17

16

15

0.22 μF

0.22 μF

0.22 μF

0.22 μF

100 μF

FB

FB

FB

FB

1000 pF

1000 pF

1000 pF

1000 pF

1000 pF

0.1 μF

1000 pF

PVCC

Figure33.StereoClass-DAmplifierwithBTLOutputandSingle-EndedInputs

18SubmitDocumentationFeedbackCopyright©2009,TexasInstrumentsIncorporated

ProductFolderLink(s):TPA3113D2

Page 51

TPA3113D2

www.ti.com

...........................................................................................................................................SLOS650B–AUGUST2009–REVISEDSEPTEMBER2009

PVCC

Control

System

Audio

Source

PVCC

10 Ω

1 kΩ

1 Fm

1 Fm

1 Fm

1 Fm

AVCC

100 kΩ

1 28

2

3

4

5

6

7

8

9

10

11

12

13

14

SD

FAULT

LINP

LINN

GAIN0

GAIN1

AVCC

AGND

GVDD

PLIMIT

RINN

RINP

NC

PBTL

TPA3113 D

GND

29

PowerPAD

PVCCL

PVCCL

BSPL

OUTPL

PGND

OUTNL

BSNL

BSNR

OUTNR

PGND

OUTPR

BSPR

PVCCR

PVCCR

27

26

25

24

23

22

21

20

19

18

17

16

15

100 μF 0. 1 μF

0.47 μF

0.47 μF

100 μF

FB

FB

0.1 μF

1000 pF

1000 pF

1000 pF

1000 pF

PVCC

Figure34.StereoClass-DAmplifierwithPBTLOutputandSingle-EndedInput

Copyright©2009,TexasInstrumentsIncorporatedSubmitDocumentationFeedback19

ProductFolderLink(s):TPA3113D2

Page 52

TPA3113D2

SLOS650B–AUGUST2009–REVISEDSEPTEMBER2009...........................................................................................................................................

TPA3113D2ModulationScheme

TheTPA3113D2usesamodulationschemethatallowsoperationwithouttheclassicLCreconstructionfilter

whentheampisdrivinganinductiveload.Eachoutputisswitchingfrom0voltstothesupplyvoltage.TheOUTP

andOUTNareinphasewitheachotherwithnoinputsothatthereislittleornocurrentinthespeaker.Theduty

cycleofOUTPisgreaterthan50%andOUTNislessthan50%forpositiveoutputvoltages.Thedutycycleof

OUTPislessthan50%andOUTNisgreaterthan50%fornegativeoutputvoltages.Thevoltageacrosstheload

sitsat0Vthroughoutmostoftheswitchingperiod,reducingtheswitchingcurrent,whichreducesanyI2Rlosses

intheload.

OUTP

www.ti.com

OUTP

OUTP-OUTN

Speaker

Current

OUTP-OUTN

Speaker

Current

OUTP-OUTN

Speaker

Current

OUTN

OUTP

OUTN

PVCC

OUTP

OUTN

-PVCC

NoOutput

0V

PositiveOutput

0V

0A

NegativeOutput

0V

0A

Figure35.TheTPA3113D2OutputVoltageandCurrentWaveformsIntoanInductiveLoad

FerriteBeadFilterConsiderations

UsingtheAdvancedEmissionsSuppressionTechnologyintheTPA3113D2amplifieritispossibletodesigna

highefficiencyClass-Daudioamplifierwhileminimizinginterferencetosurroundingcircuits.Itisalsopossibleto

accomplishthiswithonlyalow-costferritebeadfilter.Inthiscaseitisnecessarytocarefullyselecttheferrite

beadusedinthefilter.

Oneimportantaspectoftheferritebeadselectionisthetypeofmaterialusedintheferritebead.Notallferrite

materialisalike,soitisimportanttoselectamaterialthatiseffectiveinthe10to100MHzrangewhichiskeyto

theoperationoftheClassDamplifier.Manyofthespecificationsregulatingconsumerelectronicshave

emissionslimitsaslowas30MHz.Itisimportanttousetheferritebeadfiltertoblockradiationinthe30MHz

andaboverangefromappearingonthespeakerwiresandthepowersupplylineswhicharegoodantennasfor

thesesignals.Theimpedanceoftheferritebeadcanbeusedalongwithasmallcapacitorwithavalueinthe

rangeof1000pFtoreducethefrequencyspectrumofthesignaltoanacceptablelevel.Forbestperformance,

theresonantfrequencyoftheferritebead/capacitorfiltershouldbelessthan10MHz.

20SubmitDocumentationFeedbackCopyright©2009,TexasInstrumentsIncorporated

ProductFolderLink(s):TPA3113D2

Page 53

TPA3113D2

www.ti.com

Also,itisimportantthattheferritebeadislargeenoughtomaintainitsimpedanceatthepeakcurrentsexpected

fortheamplifier.Someferritebeadmanufacturersspecifythebeadimpedanceatavarietyofcurrentlevels.In

thiscase,itispossibletomakesuretheferritebeadmaintainsanadequateamountofimpedanceatthepeak

currentoftheamplifier.Ifthesespecificationsarenotavailable,itisalsopossibletoestimatethebeadcurrent

handlingcapabilitybymeasuringtheresonantfrequencyofthefilteroutputatlowpowerandatmaximumpower.

Achangeofresonantfrequencyoflessthanfiftypercentunderthisconditionisdesirable.Examplesofferrite

beadswhichhavebeentestedandworkwellwiththeTPA3113D2include28L0138-80R-10and

HI1812V101R-10fromStewardandthe742792510fromWurthElectronics.

Ahighqualityceramiccapacitorisalsoneededfortheferritebeadfilter.AlowESRcapacitorwithgood

temperatureandvoltagecharacteristicswillworkbest.

AdditionalEMCimprovementsmaybeobtainedbyaddingsnubbernetworksfromeachoftheclassDoutputsto

ground.SuggestedvaluesforasimpleRCseriessnubbernetworkwouldbe10Ωinserieswitha330pF

capacitoralthoughdesignofthesnubbernetworkisspecifictoeveryapplicationandmustbedesignedtaking

intoaccounttheparasiticreactanceoftheprintedcircuitboardaswellastheaudioamp.Takecaretoevaluate

thestressonthecomponentinthesnubbernetworkespeciallyiftheampisrunningathighPVCC.Also,make

surethelayoutofthesnubbernetworkistightandreturnsdirectlytothePGNDorthePowerPad™beneaththe

chip.

...........................................................................................................................................SLOS650B–AUGUST2009–REVISEDSEPTEMBER2009

m

LimitLevel-dB V/m

70

60

50

40

30

20

10

0

30M

230M 430M 630M

FCCClassB(3m)

830M

f-Frequency-Hz

Figure36.TPA3113D2EMCspectrumwithFCCClassBLimits

Efficiency:LCFilterRequiredWiththeTraditionalClass-DModulationScheme

Themainreasonthatthetraditionalclass-Damplifierneedsanoutputfilteristhattheswitchingwaveformresults

inmaximumcurrentflow.Thiscausesmorelossintheload,whichcauseslowerefficiency.Theripplecurrentis

largeforthetraditionalmodulationscheme,becausetheripplecurrentisproportionaltovoltagemultipliedbythe

timeatthatvoltage.Thedifferentialvoltageswingis2×V

thetraditionalmodulationscheme.AnidealLCfilterisneededtostoretheripplecurrentfromeachhalfcyclefor

thenexthalfcycle,whileanyresistancecausespowerdissipation.Thespeakerisbothresistiveandreactive,

whereasanLCfilterisalmostpurelyreactive.

TheTPA3113D2modulationschemehaslittlelossintheloadwithoutafilterbecausethepulsesareshortand

thechangeinvoltageisV

insteadof2×V

CC

.Astheoutputpowerincreases,thepulseswiden,makingthe

CC

ripplecurrentlarger.RipplecurrentcouldbefilteredwithanLCfilterforincreasedefficiency,butformost

applicationsthefilterisnotneeded.

AnLCfilterwithacutofffrequencylessthantheclass-Dswitchingfrequencyallowstheswitchingcurrenttoflow

throughthefilterinsteadoftheload.Thefilterhaslessresistancebuthigherimpedanceattheswitching

frequencythanthespeaker,whichresultsinlesspowerdissipation,thereforeincreasingefficiency.

,andthetimeateachvoltageishalftheperiodfor

CC

Copyright©2009,TexasInstrumentsIncorporatedSubmitDocumentationFeedback21

ProductFolderLink(s):TPA3113D2

Page 54

TPA3113D2

SLOS650B–AUGUST2009–REVISEDSEPTEMBER2009...........................................................................................................................................

WhentoUseanOutputFilterforEMISuppression

TheTPA3113D2hasbeentestedwithasimpleferritebeadfilterforavarietyofapplicationsincludinglong

speakerwiresupto125cmandhighpower.TheTPA3113D2EVMpassesFCCClassBspecificationsunder

theseconditionsusingtwistedspeakerwires.Thesizeandtypeofferritebeadcanbeselectedtomeet

applicationrequirements.Also,thefiltercapacitorcanbeincreasedifnecessarywithsomeimpactonefficiency.

TheremaybeafewcircuitinstanceswhereitisnecessarytoaddacompleteLCreconstructionfilter.These

circumstancesmightoccuriftherearenearbycircuitswhicharesensitivetonoise.Inthesecases,aclassic

secondorderButterworthfiltersimilartothoseshowninthefiguresbelowcanbeused.

SomesystemshavelittlepowersupplydecouplingfromtheAClinebutarealsosubjecttolineconducted

interference(LCI)regulations.Theseincludesystemspoweredby"wallwarts"and"powerbricks."Inthese

cases,itLCreconstructionfilterscanbethelowestcostmeanstopassLCItests.Commonmodechokesusing

lowfrequencyferritematerialcanalsobeeffectiveatpreventinglineconductedinterference.

33 Hm

OUTP

L1

33 mH

OUTN

L2

C2

1 mF

C3

1 mF

www.ti.com

Figure37.TypicalLCOutputFilter,CutoffFrequencyof27kHz,SpeakerImpedance=8Ω

15 Hm

OUTP

OUTN

L1

15 mH

L2

C2

2.2 mF

C3

2.2 mF

Figure38.TypicalLCOutputFilter,CutoffFrequencyof27kHz,SpeakerImpedance=4Ω

Ferrite

ChipBead

OUTP

Ferrite

ChipBead

OUTN

1nF

1nF

Figure39.TypicalFerriteChipBeadFilter(ChipBeadExample)

22SubmitDocumentationFeedbackCopyright©2009,TexasInstrumentsIncorporated

ProductFolderLink(s):TPA3113D2

Page 55

TPA3113D2

www.ti.com

InputResistance

Changingthegainsettingcanvarytheinputresistanceoftheamplifierfromitssmallestvalue,9kΩ±20%,tothe

largestvalue,60kΩ±20%.Asaresult,ifasinglecapacitorisusedintheinputhigh-passfilter,the-3dBor

cutofffrequencymaychangewhenchanginggainsteps.

The-3-dBfrequencycanbecalculatedusingEquation2.UsetheZIvaluesgiveninTable1.

...........................................................................................................................................SLOS650B–AUGUST2009–REVISEDSEPTEMBER2009

Z

f

C

f=

2 Z Cp

i

Input

Signal

IN

1

i i

Z

i

(2)

InputCapacitor,C

I

Inthetypicalapplication,aninputcapacitorCI)isrequiredtoallowtheamplifiertobiastheinputsignaltothe

properdclevelforoptimumoperation.Inthiscase,C

andtheinputimpedanceoftheamplifier(ZI)forma

I

high-passfilterwiththecornerfrequencydeterminedinEquation3.

-3dB

2 Z Cp

1

i i

f

c

f =

c

ThevalueofCIisimportant,asitdirectlyaffectsthebass(low-frequency)performanceofthecircuit.Consider

theexamplewhereZIis60kΩandthespecificationcallsforaflatbassresponsedownto20Hz.Equation3is

reconfiguredasEquation4.

C =

1

i

2 Z fp

i c

Inthisexample,CIis0.13µF;so,onewouldlikelychooseavalueof0.15µFasthisvalueiscommonlyused.If

thegainisknownandisconstant,useZIfromTable1tocalculateCI.Afurtherconsiderationforthiscapacitoris

theleakagepathfromtheinputsourcethroughtheinputnetworkCI)andthefeedbacknetworktotheload.This

leakagecurrentcreatesadcoffsetvoltageattheinputtotheamplifierthatreducesusefulheadroom,especially

inhighgainapplications.Forthisreason,alow-leakagetantalumorceramiccapacitoristhebestchoice.When

polarizedcapacitorsareused,thepositivesideofthecapacitorshouldfacetheamplifierinputinmost

applicationsasthedclevelthereisheldat3V,whichislikelyhigherthanthesourcedclevel.Notethatitis

importanttoconfirmthecapacitorpolarityintheapplication.Additionally,lead-freesoldercancreatedcoffset

voltagesanditisimportanttoensurethatboardsarecleanedproperly.

(3)

(4)

Copyright©2009,TexasInstrumentsIncorporatedSubmitDocumentationFeedback23

ProductFolderLink(s):TPA3113D2

Page 56

TPA3113D2

SLOS650B–AUGUST2009–REVISEDSEPTEMBER2009...........................................................................................................................................

www.ti.com

PowerSupplyDecoupling,C

S

TheTPA3113D2isahigh-performanceCMOSaudioamplifierthatrequiresadequatepowersupplydecoupling

toensurethattheoutputtotalharmonicdistortion(THD)isaslowaspossible.Powersupplydecouplingalso

preventsoscillationsforlongleadlengthsbetweentheamplifierandthespeaker.Optimumdecouplingis

achievedbyusinganetworkofcapacitorsofdifferenttypesthattargetspecifictypesofnoiseonthepower

supplyleads.Forhigherfrequencytransientsduetoparasiticcircuitelementssuchasbondwireandcopper

traceinductancesaswellasleadframecapacitance,agoodqualitylowequivalent-series-resistance(ESR)

ceramiccapacitorofvaluebetween220pFand1000pFworkswell.Thiscapacitorshouldbeplacedascloseto

thedevicePVCCpinsandsystemground(eitherPGNDpinsorPowerPad)aspossible.Formid-frequencynoise

duetofilterresonancesorPWMswitchingtransientsaswellasdigitalhashontheline,anothergoodquality

capacitortypically0.1µFto1µFplacedascloseaspossibletothedevicePVCCleadsworksbestForfiltering

lowerfrequencynoisesignals,alargeraluminumelectrolyticcapacitorof220µForgreaterplacednearthe

audiopoweramplifierisrecommended.The220µFcapacitoralsoservesasalocalstoragecapacitorfor

supplyingcurrentduringlargesignaltransientsontheamplifieroutputs.ThePVCCterminalsprovidethepower

totheoutputtransistors,soa220µForlargercapacitorshouldbeplacedoneachPVCCterminal.A10µF

capacitorontheAVCCterminalisadequate.Also,asmalldecouplingresistorbetweenAVCCandPVCCcanbe

usedtokeephighfrequencyclassDnoisefromenteringthelinearinputamplifiers.

BSNandBSPCapacitors

ThefullH-bridgeoutputstagesuseonlyNMOStransistors.Therefore,theyrequirebootstrapcapacitorsforthe

highsideofeachoutputtoturnoncorrectly.A0.22µFceramiccapacitor,ratedforatleast25V,mustbe

connectedfromeachoutputtoitscorrespondingbootstrapinput.Specifically,one0.22µFcapacitormustbe

connectedfromOUTPxtoBSPx,andone0.22µFcapacitormustbeconnectedfromOUTNxtoBSNx.(Seethe

applicationcircuitdiagraminFigure1.)

ThebootstrapcapacitorsconnectedbetweentheBSxxpinsandcorrespondingoutputfunctionasafloating

powersupplyforthehigh-sideN-channelpowerMOSFETgatedrivecircuitry.Duringeachhigh-sideswitching

cycle,thebootstrapcapacitorsholdthegate-to-sourcevoltagehighenoughtokeepthehigh-sideMOSFETs

turnedon.

DifferentialInputs

Thedifferentialinputstageoftheamplifiercancelsanynoisethatappearsonbothinputlinesofthechannel.To

usetheTPA3113D2withadifferentialsource,connectthepositiveleadoftheaudiosourcetotheINPinputand

thenegativeleadfromtheaudiosourcetotheINNinput.TousetheTPA3113D2withasingle-endedsource,ac

groundtheINPorINNinputthroughacapacitorequalinvaluetotheinputcapacitoronINNorINPandapply

theaudiosourcetoeitherinput.Inasingle-endedinputapplication,theunusedinputshouldbeacgroundedat

theaudiosourceinsteadofatthedeviceinputforbestnoiseperformance.Forgoodtransientperformance,the

impedanceseenateachofthetwodifferentialinputsshouldbethesame.

TheimpedanceseenattheinputsshouldbelimitedtoanRCtimeconstantof1msorlessifpossible.Thisisto

allowtheinputdcblockingcapacitorstobecomecompletelychargedduringthe14mspower-uptime.Iftheinput

capacitorsarenotallowedtocompletelycharge,therewillbesomeadditionalsensitivitytocomponentmatching

whichcanresultinpopiftheinputcomponentsarenotwellmatched.

UsingLOW-ESRCapacitors

Low-ESRcapacitorsarerecommendedthroughoutthisapplicationsection.Areal(asopposedtoideal)capacitor

canbemodeledsimplyasaresistorinserieswithanidealcapacitor.Thevoltagedropacrossthisresistor

minimizesthebeneficialeffectsofthecapacitorinthecircuit.Thelowertheequivalentvalueofthisresistance,

themoretherealcapacitorbehaveslikeanidealcapacitor.

24SubmitDocumentationFeedbackCopyright©2009,TexasInstrumentsIncorporated

ProductFolderLink(s):TPA3113D2

Page 57

TPA3113D2

www.ti.com

Printed-CircuitBoard(PCB)Layout

TheTPA3113D2canbeusedwithasmall,inexpensiveferritebeadoutputfilterformostapplications.However,

sincetheClass-Dswitchingedgesarefast,itisnecessarytotakecarewhenplanningthelayoutoftheprinted

circuitboard.ThefollowingsuggestionswillhelptomeetEMCrequirements.

•Decouplingcapacitors—Thehigh-frequencydecouplingcapacitorsshouldbeplacedasclosetothePVCC

•Keepthecurrentloopfromeachoftheoutputsthroughtheferritebeadandthesmallfiltercapandbackto

•Grounding—TheAVCC(pin7)decouplingcapacitorshouldbegroundedtoanalogground(AGND).The

•Outputfilter—TheferriteEMIfilter(Figure39)shouldbeplacedasclosetotheoutputterminalsaspossible

•ThermalPad—ThethermalpadmustbesolderedtothePCBforproperthermalperformanceandoptimal

Foranexamplelayout,seetheTPA3113D2EvaluationModule(TPA3113D2EVM)UserManual.BoththeEVM

usermanualandthethermalpadapplicationreportareavailableontheTIWebsiteathttp://www.ti.com.

...........................................................................................................................................SLOS650B–AUGUST2009–REVISEDSEPTEMBER2009

andAVCCterminalsaspossible.Large(220µForgreater)bulkpowersupplydecouplingcapacitorsshould

beplacedneartheTPA3113D2onthePVCCLandPVCCRsupplies.Local,high-frequencybypass

capacitorsshouldbeplacedasclosetothePVCCpinsaspossible.Thesecapscanbeconnectedtothe

thermalpaddirectlyforanexcellentgroundconnection.Consideraddingasmall,goodqualitylowESR

ceramiccapacitorbetween220pFand1000pFandalargermid-frequencycapofvaluebetween0.1µFand

1µFalsoofgoodqualitytothePVCCconnectionsateachendofthechip.

PGNDassmallandtightaspossible.Thesizeofthiscurrentloopdeterminesitseffectivenessasan

antenna.

PVCCdecouplingcapacitorsshouldconnecttoPGND.Analoggroundandpowergroundshouldbe

connectedatthethermalpad,whichshouldbeusedasacentralgroundconnectionorstargroundforthe

TPA3113D2.

forthebestEMIperformance.TheLCfilter(Figure37andFigure38)shouldbeplacedclosetotheoutputs.

ThecapacitorsusedinboththeferriteandLCfiltersshouldbegroundedtopowerground.

reliability.Thedimensionsofthethermalpadandthermallandshouldbe6.46mmby2.35mm.Sevenrowsof

solidvias(threeviasperrow,0,3302mmor13milsdiameter)shouldbeequallyspacedunderneaththe

thermalland.Theviasshouldconnecttoasolidcopperplane,eitheronaninternallayeroronthebottom

layerofthePCB.Theviasmustbesolidvias,notthermalrelieforwebbedvias.SeetheTIApplication

ReportSLMA002formoreinformationaboutusingtheTSSOPthermalpad.ForrecommendedPCB

footprints,seefiguresattheendofthisdatasheet.

RevisionHistory

ChangesfromOriginal(August2009)toRevisionA.....................................................................................................Page

•ChangedFeatureFrom:90%EfficientClass-DOperationEliminatesNeedforHeatSinksTo:87%EfficientClass-D

OperationEliminatesNeedforHeatSinks............................................................................................................................1

•ChangedtheDrainSourceTYPvalueFrom:240to400mΩ...............................................................................................3

•ChangedtheDrainSourceTYPvalueFrom:240to400mΩ...............................................................................................3

•ChangedACChar24V-POFrom:THD+N=10%,f=1kHz,V

kHz,V

•ChangedACChar24V-THD+NFrom:V

PO=3W(half-power)TYPFrom:0.1To:0.07.....................................................................................................................4

•DeletedACChar12V-,PO-Continuousoutputpower......................................................................................................4

•ChangedACChar12V-THD+NFrom:V

=3W(half-power).................................................................................................................................................................4

•ChangedmultiplegraphsintheTYPICALCHARACTERISTICS...........................................................................................7

ChangesfromRevisionA(August2009)toRevisionB................................................................................................Page

•AddedthePinoutillustration.................................................................................................................................................4

•ChangedtheStereoClass-DAmplifierwithBTLOutputandSingle-EndedInputillustrationFigure33-Corrected

thepinnames......................................................................................................................................................................18

•ChangedtheStereoClass-DAmplifierwithPBTLOutputandSingle-EndedInputFigure34-Correctedthepin

names..................................................................................................................................................................................19

Copyright©2009,TexasInstrumentsIncorporatedSubmitDocumentationFeedback25

=10V(TYP=6W).................................................................................................................................................4

CC

=16V,f=1kHz,PO=7.5W(half-power)To:V

CC

=16V,f=1kHz,PO=5W(half-power)To:V

CC

ProductFolderLink(s):TPA3113D2

=16V(TYP=15W)To:THD+N=10%,f=1

CC

=16V,f=1kHz,

CC

=16V,f=1kHz,P

CC

O

Page 58

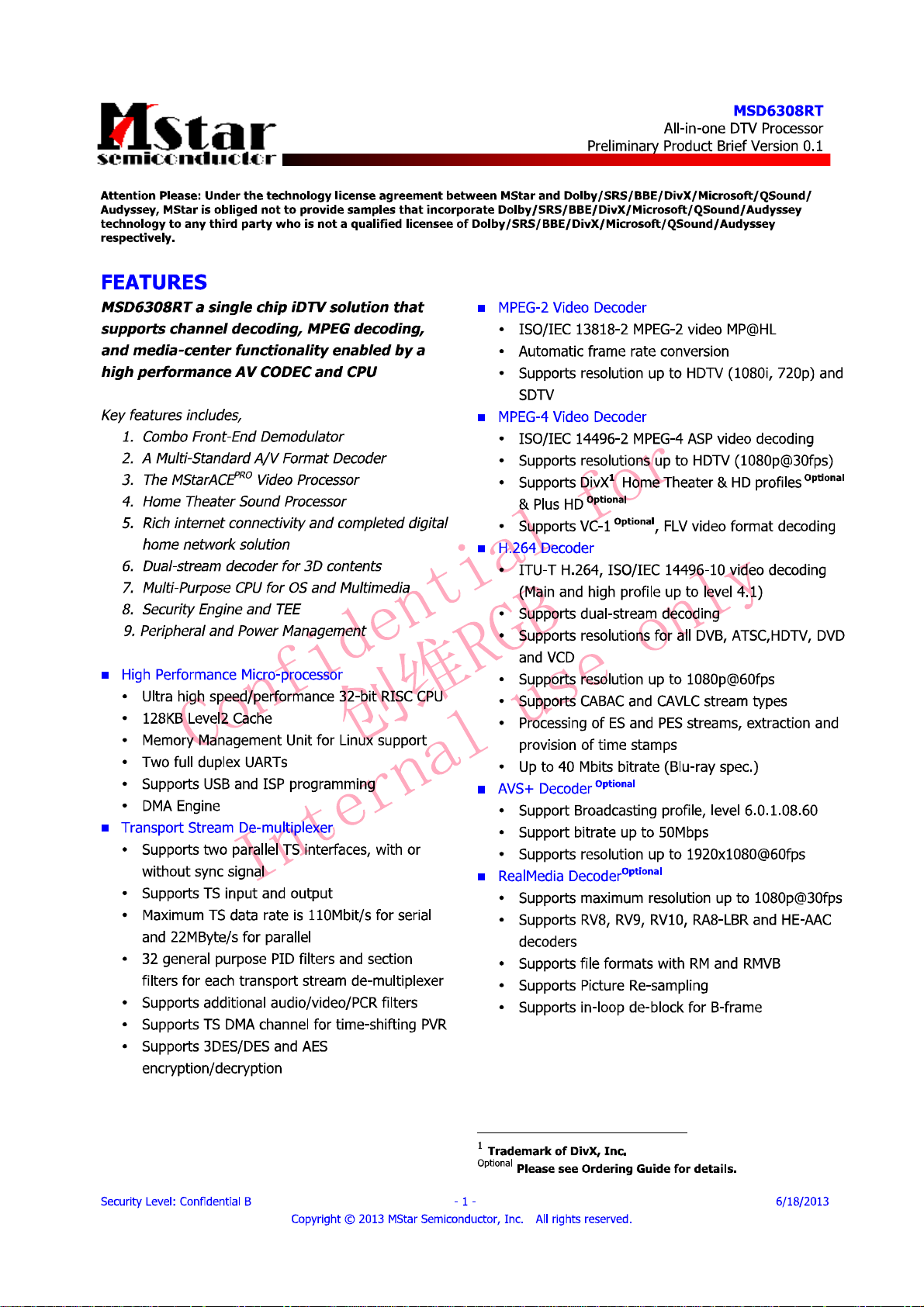

Headphone Amplifiers

Standard

Headphone Amplifiers

BH3541F H3544F,BH3547F,BH3548F

Description

BH3541F, BH3544F, BH3547F, BH3548F is headphone amplifiers suitable for portable products.

BH3541F has a fixed gain of 0 dB and BH3544F, BH3547F, BH3548F has a fixed gain of 6 dB.

External resistors for gain setting are not needed. Package of BH3541F, BH3544F, BH3547F, BH3548F is pin-to-pin

compatible (SOP8), enable to replace each other easily.

BH3541F, BH3544F, BH3547F, BH3548F also has mute functions that make it easy to prevent pop noise when power

supply turns on/off. Moreover, thermal shutdown function is built-in.

BH3541F, BH3544F, BH3547F can drive 16/32 load, BH3548F can drive 8/16/32 . So, BH3548F is suitable for 8

receiver.

Features

1) Built-in mute function for preventing pop noise when power supply turns on/off

2) Built-in thermal shutdown function

3) BH3541F, BH3544F, BH3547F, BH3548F are pin-to-pin compatible

4) SOP8 small package

Applications

TV, Desktop PC, Notebook PC, Camcorder and other equipment having headphone output

Line up

Supply voltage +2.8 +6.5 +4.5 +5.5 +4.0 +5.5 V

Quiescent current 7.0 3.7 6.5 mA

Amplifier gain 0 6 dB

Output [RL=16 ] 62 77 62 mW

load impedance 16 / 32 8/16/32

Operating temperature range -25 +75 -40 +85

,B

Part No. BH3541F BH3544F BH3547F BH3548F Unit

No.10102EAT02

Absolute maximum ratings(Ta=25°C)

Parameter Symbol

Applied voltage

Power dissipation

Storage temperature

*1 Derating is done at 5.5mW/°C above Ta=25°C. (When mounted on a 70mm×70mm×1.6mm PCB board, FR4)

Operating conditions (Ta=25°C)

Parameter Symbol

Supply voltage VCC

Temperature Range Topr -25 +75 -40 +85

* These product are not designed for protection against radioactive rays.

VCC

Pd 550 *1 mW

Tstg -55

BH3541F,BH3544FBH3547F BH3548F

+2.8 +6.5 +4.5 +6.5 +4.0 +5.5 V

BH3541F,BH3544F,BH3547F,BH3548F

Ratings

7.0 V

+125 °C

Limits

Unit

Unit

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

1/8

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.com.cn

2010.05 - Rev.A

Page 59

BH3541F,BH3544F,BH3547F,BH3548F

Electrical characteristics (Unless otherwise noted, Ta=25°C,VCC=5V,RL=32 ,f=1kHz,BW=400 30kHz

BH3541F : VIN=0dBV, BH3544F, BH3547F, BH3548F : VIN =-6dBV)

Parameter Symbol

BH3541F BH3544FBH3547FBH3548F

Limits(TYP.)

UnitConditions

Technical Note

Quiescent current IQ

Mute pin control voltage H VTMH 1.6< V Mute OFF

Mute pin control voltage L VTML <0.3 V Mute ON

Gain GVC 0 6 dB -

Gain difference between

channels

Total harmonic distortion THD 0.02 0.05 0.02 % BW=20 20kHz

Rated output 1 PO1

Rated output 2 PO2 62 77 62 mW

Rated output 3 PO3 - 120 mW

Output noise voltage VNO -93 dBVBW=20 20kHz,Rg=0

Channel separation CS -90 -87 -90 dB Rg=0

Mute attenuation ATT -80 dB Rg=0

GVC 0 dB -

7 3.7 6.5 mA VIN=0Vrms

RL=32 ,THD<0.1%

31 46 31 mW

(BH3541F,BH3544F,BH3548F)

RL=32 ,THD 0.3%

(BH3547F)

RL=16 ,THD<0.1%

(BH3541F,BH3544F,BH3548F)

RL=16 ,THD 0.5%

(BH3547F)

RL=8 ,THD 0.25%

(BH3548F)

Ripple rejection RR -57 dB fRR=100Hz,VRR=-20dBV

Input resistance Rin 180 90 k -

Reference data

BH3541F/BH3544F BH3541F/BH3544F BH3541F/BH3544F

Fig. 1 Quiescent current vs.

power supply voltage

Fig. 2 in DC current vs.

power supply voltage

Fig. 3 Output voltage vs.

Mute control voltage

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

2/8

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.com.cn

2010.05 - Rev.A

Page 60

BH3541F,BH3544F,BH3547F,BH3548F

Reference data (Continued)

BH3541F/BH3544F BH3541F/BH3544F BH3541F/BH3544F

10

1

0.1

Ta 25 C

RL

32

VCC 5V

f 10kHZ

f 1kHZ

10

1

0.1

Ta 25 C

RL

32

VCC 3V

Technical Note

f 10kHZ

f 1kHZ

0.01

f 100HZ

0.001

40

30 20 1010

OUTPUT VOLTAGE : VO (dBV)

0

Fig. 4 Voltage gain vs. frequency Fig. 5 Total harmonic distortion vs.

output voltage (1)

0.01

0.001

40

30

OUTPUT VOLTAGE: VO (dBV)

f 100HZ

20 1010

0

Fig. 6 Total harmonic distortion vs.

output voltage (2)

BH3541F/BH3544F BH3541F/BH3544F BH3541F/BH3544F

Fig. 7 Total harmonic distortion vs.

output voltage (3)

Fig. 8 Total harmonic distortion vs.

output voltage (4)

Fig. 9 Channel separation vs.

frequency

BH3541F/BH3544F BH3541F/BH3544F BH3541F/BH3544F

Fig. 10 MUTE attenuation vs. frequency Fig. 11 Ripple rejection vs. frequencyFig. 12 Ripple rejection vs.

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

3/8

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.com.cn

power supply voltage

2010.05 - Rev.A

Page 61

BH3541F,BH3544F,BH3547F,BH3548F

5

Block diagram

VCC

OUT2BIASIN2

TSD

OUT1 MUTEIN1GND

MUTE

2 1

Measurement circuit

0dB

(6dB)

0dB

(6dB)

3 4

Fig. 13

Fig. 14

678

BIAS

180k

(90k)

180k

(90k)

( ) are BH3544F, BH3547F, BH3548F values.

( ) are BH3544F, BH3547F, BH3548F values.

Technical Note

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

4/8

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.com.cn

2010.05 - Rev.A

Page 62

BH3541F,BH3544F,BH3547F,BH3548F

Terminal Equivalent Circuit / Description

Pin

No.

Pin

Name

I /O Pin voltage

BH3544F,BH3547F,BH3548FBH3547F

1

OUT1

O

7

OUT2

2.1V

(VCC=5V)

1

7 1 7

10k

VCC

Equivalent circuit

1

7 1 7

10k

Technical Note

Function

VCC

Output pin

2 MUTE I

3

IN1

5

IN2

I

6 BIAS I/O

0.1V

(When open)

2.1V

(VCC=5V)

2.1V

(VCC=5V)

200k

VCC

2

190k

VCC

2

3

5

VCC

180k

BIAS

3

5

VCC

90k

BIAS

VCC

70k

64k

BIAS

6

VCC

60k

BIAS

60k

6

Mute control pin

Mute on:Hi

Mute off:Lo (open)

Input pin

Bias pin

(Since the 47 µF

externally attached

capacitor also serves

as the time constant for

pop noise

countermeasures,

evaluate adequately

when changing it.)

4 GND I - - - GND pin

8 VCC I - - - Power supply pin

The figure in the pin explanation and input/output equivalent circuit is reference value, it doesn$t guarantee the value.

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

5/8

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.com.cn