NEC UPC3211GR-E1, UPC3211GR Datasheet

DATA SHEET

BIPOLAR ANALOG INTEGRATED CI RCUIT

µµµµ

PC3211GR

AGC AMPLIFIER FOR DIGITAL CATV RETURN PASS

DESCRIPTION

The µPC3211GR is a silicon monolithic integrated circuit designed as AGC amplifier for digital CATV systems. This

IC is the AGC amplifier with 55 dB gain control range which is packaged in 20-pin SSOP. The device is able to use

for digital QPSK system, therefore it contributes to make design of transmission system simplicity.

FEATURES

• Wide gain control range 55 dB TYP.

• Low distortion IM3 = 57 dBc TYP. @P

IM2 = 44 dBc TYP. @P

• Supply Voltage 9 V

• Packaged in 20-pin SSOP suitable for high-density surface mount.

out

= −10 dBm

out

= −10 dBm

ORDERING INFORMATION

Part Number Package Supplying Form

µ

PC3211GR-E1 20-pin plastic SSOP (225 m i l ) Embossed tape 12 mm wide.

Pin 1 indicates pull-out di rection of tape.

Qty 2.5 kp/reel

To order evaluation samples, please contact your local NEC office. (Part number for sample order: µPC3211GR)

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for

availability and additional information.

Document No. P13564EJ3V0DS00 (3rd edition)

Date Published October 1999 N CP(K)

Printed in Japan

Caution electro-static sensitive device

The mark shows major revised points.

©

1998, 1999

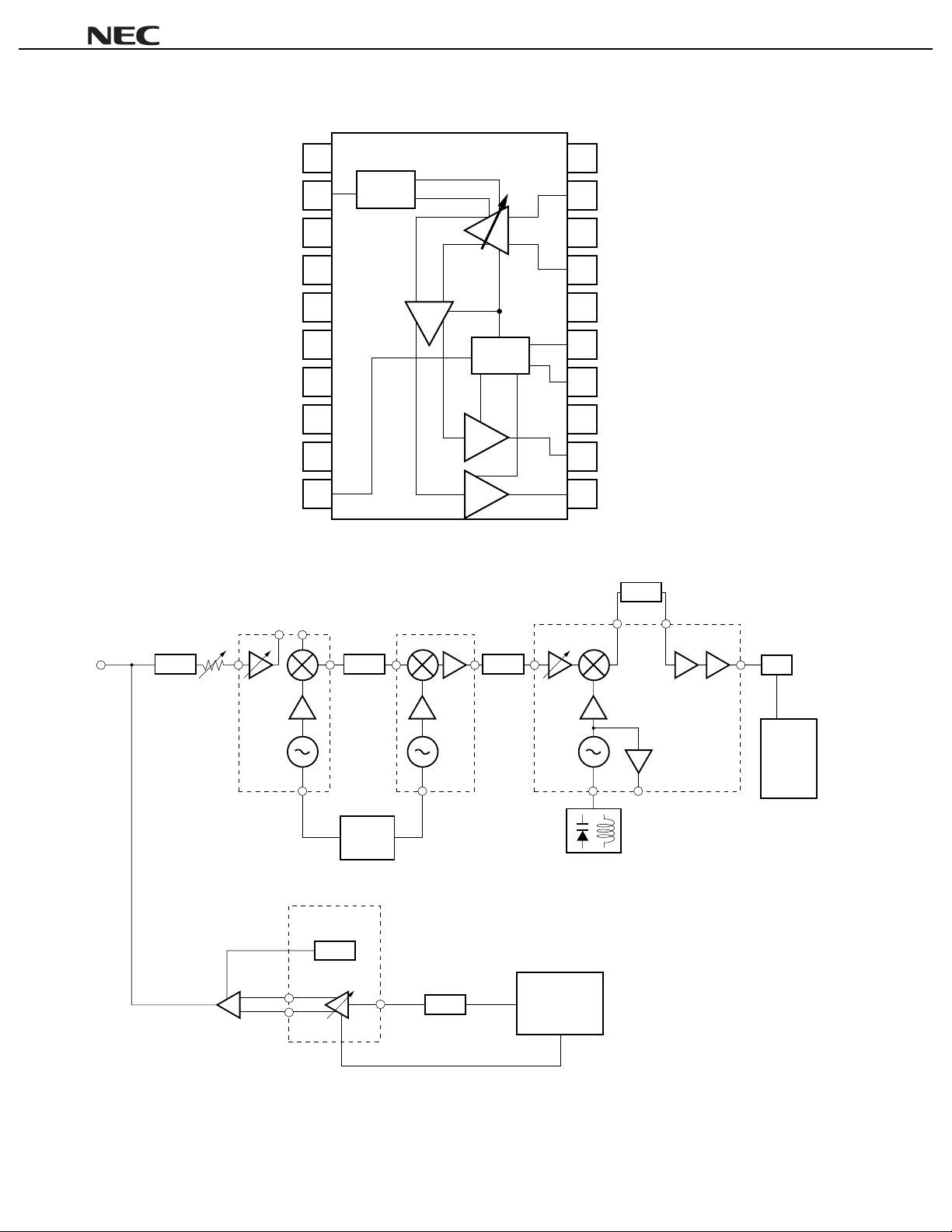

INTERNAL BLOCK DIAGRAM AND PIN CONFIGURATION (TOP VIEW)

BY1

BY2

1

20

µµµµ

PC3211GR

TYPICAL APPLICATION

RF IN

50-750 MHz

RF Return

5-42 MHz

HPF SAW SAW

VAGC

GND2A

GND2B

CC1

V

CC2

V

GND2C

GND2D

GND2E

BY3

PC2799GR

µ

10

2

Cont.

3

4

5

6

REG

7

8

9

PC2798GR

µ

1st IF

PC1686GV

µ

2nd IF

19

18

17

16

15

14

13

12

11

AGC IN1

GND1A

AGC IN2

GND1B

PSAVE

PA_BIAS

GND3

OUT1

OUT2

LPF

DC-10 MHz

A/D

Video Amplifier

QAM

Demo.

&FEC

DUAL

PLL

PC3211GR

µ

Bias

Digital

LPF

2

Data Sheet P13564EJ3V0DS00

QPSK

Modulator

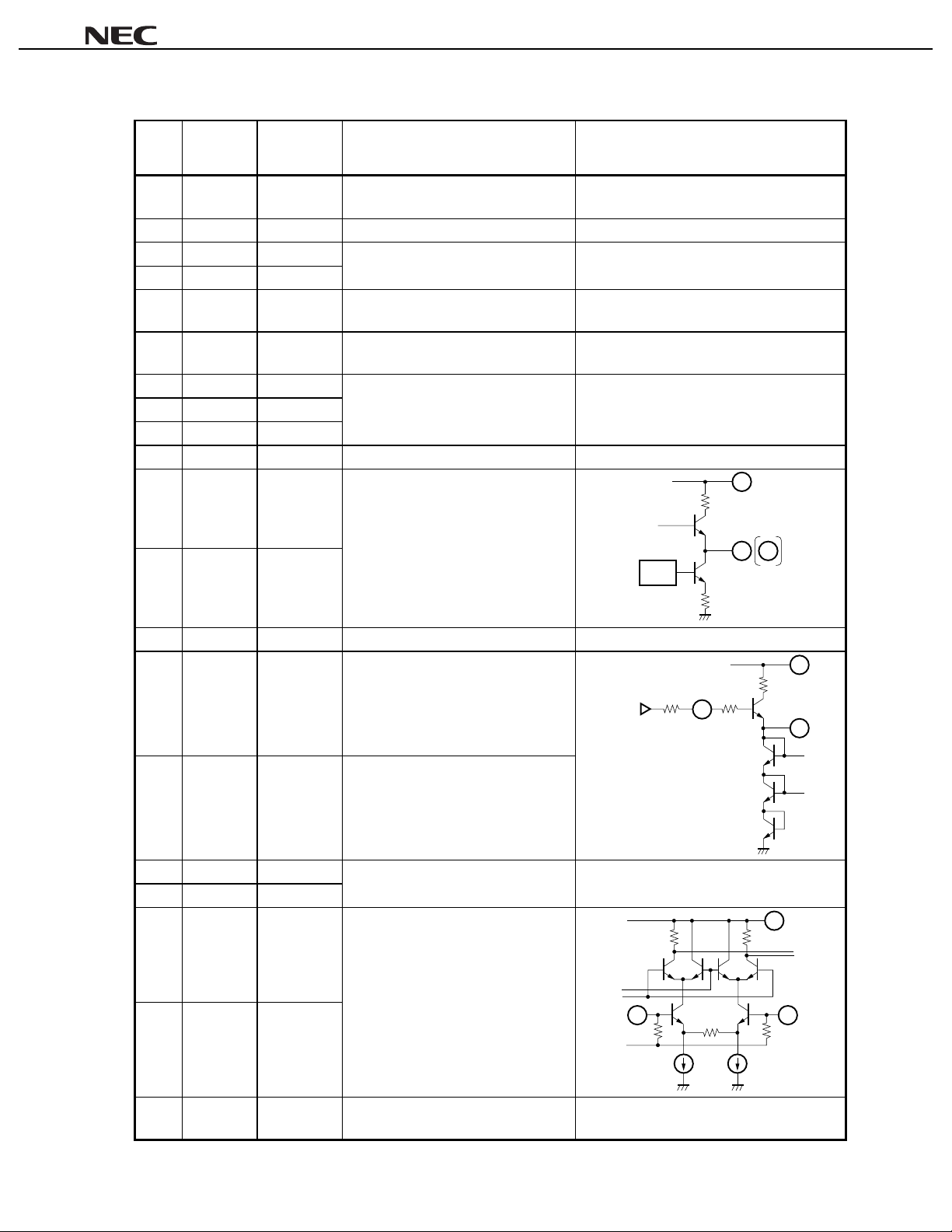

PIN FUNCTIONS

µµµµ

PC3211GR

Pin

No.

Pin

Name

Pin

Voltage

TYP. (V)

Function and Explanation Equivalent Circuit

1 BY2 – Non Connection pin.

This pin should be opened.

2 VAGC 0 to 3 Automatic gain control pi n.

3 GND2A 0.0

Ground pins of differential ampl i fier.

4 GND2B 0.0

5V

cc

1 9.0 Power supply pin of AGC ampli f i er

block.

6V

cc

2 9.0 Power supply pin of differential

amplifier and output block .

7 GND2C 0.0

Ground pins of differential ampl i fier.

8 GND2D 0.0

9 GND2E 0.0

10 BY3 1.64 Bypass pi n of regulator block.

11 OUT2 6.9

Signal output pins.

This pins feature low-impedanc e

because of its emitter-follower output

port.

12 OUT1 6.9

The pin that is not used should be

grounded through 50 ohm resistor.

6

11 12

REG

13 GND3 0.0 Ground pin of output block.

14 PA_BIAS 2.45 This is the pin to feed base bias i n

case of connection to transistor as

power amplifier.

15 Psave 9.0

(+5 kΩ)

Power-save pin.

cc

:ON

V

GND : SLEEP

The 5 kΩ resistor should be

connected between 15 pin and V

16 GND1B 0.0

Ground pin of AGC amplifier block.

18 GND1A 0.0

17 AGC IN2 2.43

Signal input pin.

In the case of single input, 17 or 19

pin should be grounded through

capacitor.

19 AGC IN1 2.43

5

V

CC

(9 V)

cc

.

5 kΩ

15

14

5

1719

20 BY1 – Non Connection pin.

This pin should be opened.

Data Sheet P13564EJ3V0DS00

3

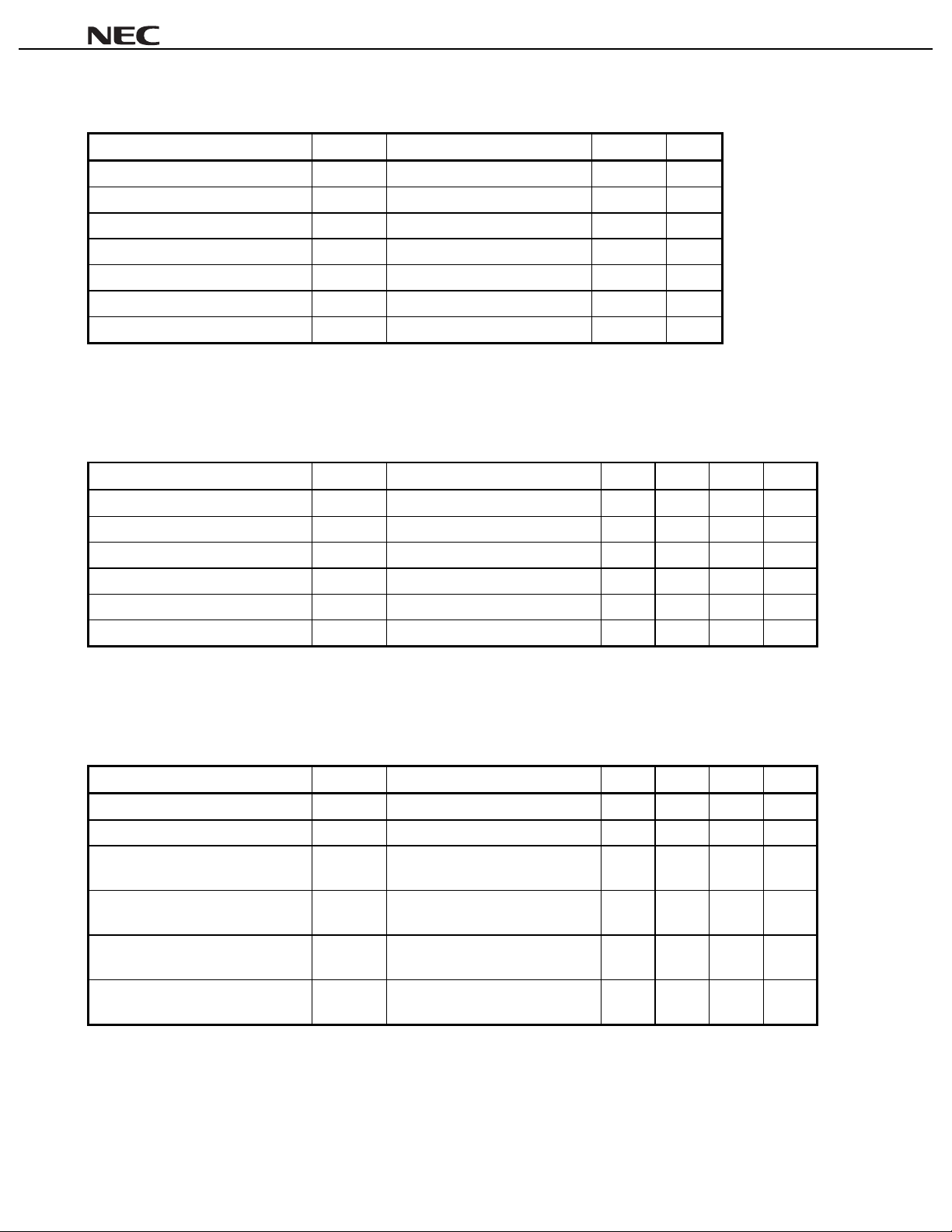

ABSOLUTE MAXIMUM RATINGS (TA = +25°C unless otherwise specified)

Parameter Symbol Test Condition Rating Unit

µµµµ

PC3211GR

Supply Voltage V

Power-save Voltage V (Psave)

AGC Voltage V

Power Dissipation P

Operating Ambient Temperature T

Storage Temperature T

CC

AGC

stg

D

A

TA = +75°C

Note 1

Note 2

11.0 V

11.0 V

3.6 V

500 mW

40 to +75 °C

−

55 to +150 °C

−

Maximum Input Level Pin (MAX) +5 dBm

Notes 1.

Bias to 15 pin through 5 kΩ resistor.

Mounted on 50 mm × 50 mm × 1.6 mm double epoxy glass board.

2.

RECOMMENDED OPERATING RANGE

Parameter Symbol Test Condition MIN. TYP. MAX. Unit

Supply Voltage V

Power-save Voltage V (Psave)

AGC Control Voltage V

Operating Ambient Temperature T

Input Frequency f

Maximum Input Level Pin (MAX) – – 0 dBm

CC

AGC

in

8.0 9.0 10.0 V

Note

0 – 10.0 V

0–3.3V

A

40 +25 +75 °C

−

5 – 100 MHz

Bias to 15 pin through 5 kΩ resistor.

Note

ELECTRICAL CHARACTERISTICS (TA = +25°C, VCC = 9 V, V

AGC

= 0 V, V (Psave) = 9 V (+5 k

specified)

Parameter Symbol Test Conditions MIN. TYP. MAX. Unit

Circuit Current 1 ICC1

Maximum Gain G

MAX

Gain Control Range GCR fin = 65 MHz, Pin = −20 dBm,

Isolation at sleep mode Isol fin = 65 MHz, Pin = −20 dBm,

2nd

order intermodulation distorti on IM

3rd order intermodulation distorti on IM

Notes 1.

By measurement circuit 1

By measurement circuit 2

2.

No input signal

fin = 65 MHz, Pin = −20 dBm

AGC

= 0 to 3 V

V

V (Psave) = 0 V (+5 kΩ)

2

fin1 = 65 MHz, fin2 = 66.8 MHz,

out

= −10 dBm

P

3

fin1 = 65 MHz, fin2 = 66.8 MHz,

out

= −10 dBm

P

Note 1

Note 2

Note 2

Note 2

Note 2

Note 2

), unless otherwise

ΩΩΩΩ

29 38 51 mA

14 16 18 dB

47 55 – dB

60 65 – dB

– –44 –40 dBc

– –57 –50 dBc

4

Data Sheet P13564EJ3V0DS00

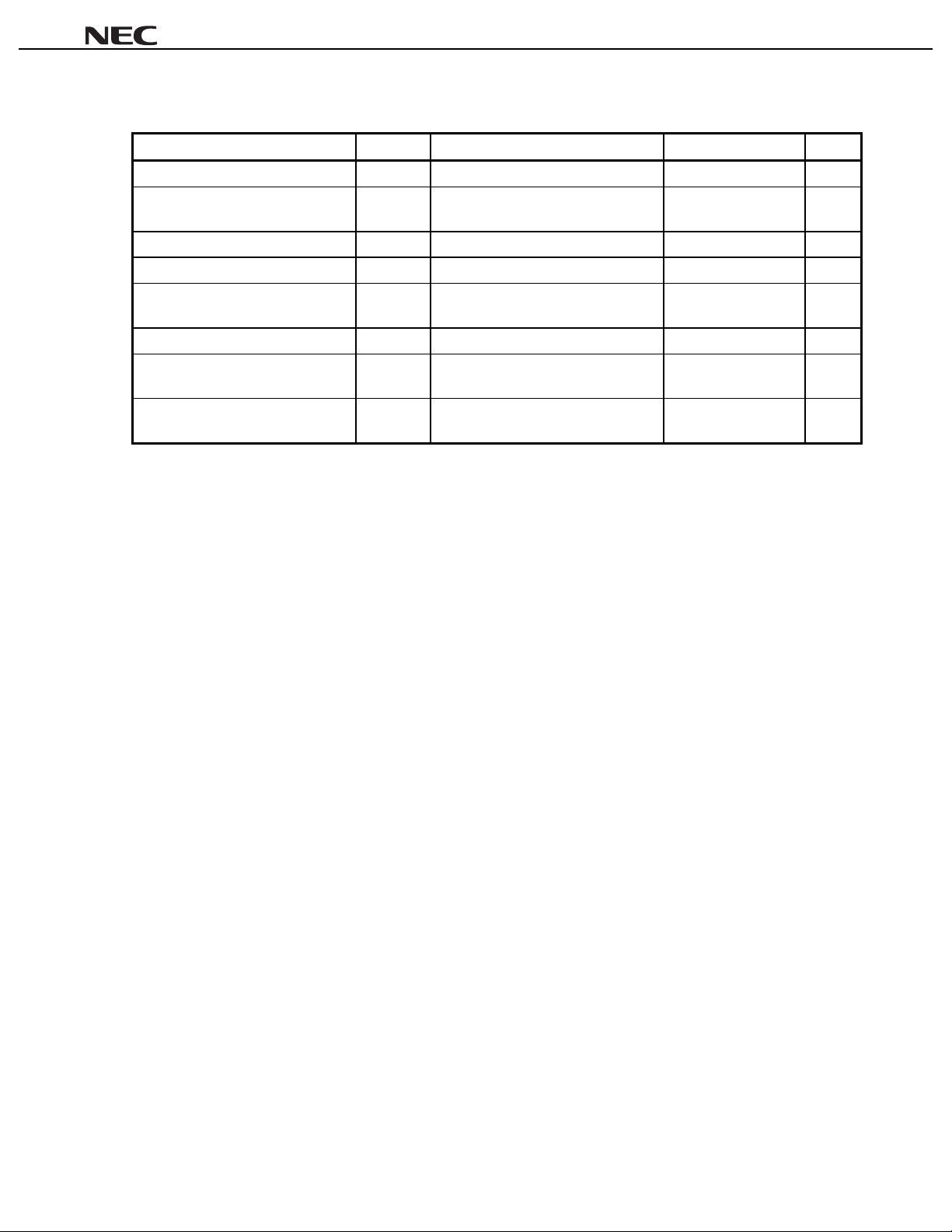

µµµµ

PC3211GR

in

= 65 MHz

in

= −20 dBm

AGC

= 0 V, V (Psave) = 9 V (+5 k

AGC

= 3 V

STANDARD CHARACTERISTICS (TA = +25°C, VCC = 9 V, V

Parameter Symbol Test Conditions Reference Value Unit

Maximum Output Power P

Circuit Current at Power-save mode ICC (P/S) No input signal, V (Psave) = 0 V (+5 kΩ)

Noise Figure NF

Output Intercept Point OIP

Gain Flatness G

Circuit Current 2 ICC2

ON Time t

OFF Time t

Notes 1.

By measurement circuit 2

By measurement circuit 1

2.

By measurement circuit 3

3.

By measurement circuit 4

4.

O (sat)

ON

OFF

fin = 65 MHz, Pin = −5 dBm

f

fin1 = 65 MHz, fin2 = 66.8 MHz

3

flat

fin = 5 to 100 MHz, 6 MHz Band width

P

No input signal, V

fin = 65 MHz,

V (Psave) = 0 → 9 V (+5 kΩ)

fin = 65 MHz,

V (Psave) = 9 → 0 V (+5 kΩ)

Note 1

Note 2

Note 3

Note 1

Note 1

Note 2

Note 4

Note 4

), unless otherwise specified)

ΩΩΩΩ

+5 dBm

3mA

10 dB

+16 dBm

±0.1 dB

43 mA

200

1.7 msec

µ

sec

Data Sheet P13564EJ3V0DS00

5

Loading...

Loading...