Page 1

TFT MONOCHROME LCD MODULE

NL256204AM15-01

NL256204AM15-01A

51cm (20.1 Type)

QSXGA

LVDS Interface (4 ports)

DATA SHEET

DOD-PP-0209 (8th edition)

This DATA SHEET is updated document from

DOD-PP-0113(7).

All information is subject to change without notice.

Please confirm the sales representative before

starting to design your system.

Document Number: DOD-PP-0209 (8th edition)

Published date: March 2007 CP(N)

1

© NEC LCD Technologies, Ltd.

2003- 2007 All rights reserved.

Page 2

NL256204AM15-01/01A

INTRODUCTION

The Copyright to this document belongs to NEC LCD Technologies, Ltd. (hereinafter called "NEC").

No part of this document will be used, reproduced or copied without prior written consent of NEC.

NEC does and will not assume any liability for infringement of patents, copyrights or other intellectual

property rights of any third party arising out of or in connection with application of the products

described herein except for that directly attributable to mechanisms and workmanship thereof. No license,

express or implied, is granted under any patent, copyright or other intellectual property right of NEC.

Some electronic parts/components would fail or malfunction at a certain rate. In spite of every effort to

enhance reliability of products by NEC, the possibility of failures and malfunction might not be avoided

entirely. To prevent the risks of damage to death, human bodily injury or other property arising out

thereof or in connection therewith, each customer is required to take sufficient measures in its safety

designs and plans including, but not limited to, redundant system, fire-containment and anti-failure.

The products are classified into three quality grades: "Standard", "Special", and "Specific" of the

highest grade of a quality assurance program at the choice of a customer. Each quality grade is designed

for applications described below. Any customer who intends to use a product for application other than

that of Standard quality grade is required to contact an NEC sales representative in advance.

The Standard quality grade applies to the products developed, designed and manufactured in

accordance with the NEC standard quality assurance program, which are designed for such application as

any failure or malfunction of the products (sets) or parts/components incorporated therein a customer uses

are, directly or indirectly, free of any damage to death, human bodily injury or other property, like general

electronic devices.

Examples: Computers, office automation equipment, communications equipment, test and measurement

equipment, audio and visual equipment, home electronic appliances, machine tools, personal

electronic equipment, industrial robots, etc.

The Special quality grade applies to the products developed, designed and manufactured in accordance

with an NEC quality assurance program stricter than the standard one, which are designed for such

application as any failure or malfunction of the products (sets) or parts/components incorporated therein a

customer uses might directly cause any damage to death, human bodily injury or other property, or such

application under more severe condition than that defined in the Standard quality grade without such

direct damage.

Examples: Control systems for transportation equipment (automobiles, trains, ships, etc.), traffic control

systems, anti-disaster systems, anti-crime systems, medical equipment not specifically

designed for life support, safety equipment, etc.

The Specific quality grade applies to the products developed, designed and manufactured in accordance

with the standards or quality assurance program designated by a customer who requires an extremely

higher level of reliability and quality for such products.

Examples: Military systems, aircraft control equipment, aerospace equipment, nuclear reactor control

systems, medical equipment/devices/systems for life support, etc.

The quality grade of this product is the "Standard" unless otherwise specified in this document.

DATA SHEET DOD-PP-0209 (8th edition)

2

Page 3

NL256204AM15-01/01A

CONTENTS

INTRODUCTION ..........................................................................................................................................2

1. OUTLINE....................................................................................................................................................4

1.1 STRUCTURE AND PRINCIPLE...........................................................................................................4

1.2 APPLICA TION.......................................................................................................................................4

1.3 FEATURES.............................................................................................................................................4

2. GENERAL SPECIFICATIONS ................................................................................................................5

3. BLOCK DIAGRAM...................................................................................................................................6

4. DETAILED SPECIFICATIONS...............................................................................................................7

4.1 MECHANICAL SPECIFICATIONS......................................................................................................7

4.2 ABSOLUTE MAXIMUM RATINGS....................................................................................................7

4.3 ELECTRICAL CHARACTERISTICS...................................................................................................8

4.3.1 LCD panel signal processing board...............................................................................................8

4.3.2 Inverter...........................................................................................................................................9

4.3.3 Inverter current wave.....................................................................................................................9

4.3.4 Power supply voltage ripple.........................................................................................................10

4.3.5 Fuse..............................................................................................................................................10

4.4 POWER SUPPLY VOLTAGE SEQUENCE........................................................................................11

4.4.1 LCD panel signal processing board.............................................................................................11

4.4.2 Inverter.........................................................................................................................................11

4.5 CONNECTIONS AND FUNCTIONS FOR INTERFACE PINS.........................................................12

4.5.1 LCD panel signal processing board.............................................................................................12

4.5.2 Inverter.........................................................................................................................................14

4.5.3 Positions of socket.......................................................................................................................14

4.6 LUMINANCE CONTROL...................................................................................................................15

4.6.1 Luminance control methods.........................................................................................................15

4.6.2 Detail of BRTP timing .................................................................................................................16

4.7 METHOD OF CONNECTION FOR LVDS TRANSMITTER............................................................17

4.8 DISPLAY GRAY SCALE AND INPUT DATA SIGNALS..................................................................19

4.9 INPUT SIGNAL TIMINGS..................................................................................................................20

4.9.1 Timing characteristics..................................................................................................................20

4.9.2 Input signal timing chart..............................................................................................................20

4.10 LVDS DATA TRANSMISSION MODE............................................................................................21

4.11 DISPLAY POSITIONS.......................................................................................................................22

4.12 PIXEL ARRANGNMENT .................................................................................................................23

4.13 TEN-bit LOOK UP TABLE FOR GAMMA ADJUSTMENT............................................................24

4.14 LUT SERIAL COMMUNICATION TIMINGS.................................................................................27

4.15 OPTICS...............................................................................................................................................29

4.15.1 Optical characteristics................................................................................................................29

4.15.2 Definition of contrast ratio.........................................................................................................31

4.15.3 Definition of luminance uniformity...........................................................................................31

4.15.4 Definition of response times......................................................................................................31

4.15.5 Definition of viewing angles......................................................................................................31

5. RELIABILITY TESTS.............................................................................................................................32

6. PRECAUTIONS .......................................................................................................................................33

6.1 MEANING OF CAUTION SIGNS......................................................................................................33

6.2 CAUTIONS..........................................................................................................................................33

6.3 A TTENTI ONS......................................................................................................................................33

6.3.1 Handling of the product...............................................................................................................33

6.3.2 Environment.................................................................................................................................34

6.3.3 Characteristics..............................................................................................................................35

6.3.4 Other............................................................................................................................................35

7. OUTLINE DRAWINGS...........................................................................................................................36

DATA SHEET DOD-PP-0209 (8th edition)

3

Page 4

1. OUTLINE

1.1 STRUCTURE AND PRINCIPLE

Monochrome LCD module NL256204AM15-01 and NL256204AM15-01A are composed of the

amorphous silicon thin film transistor liquid crystal display (a-Si TFT LCD) panel structure with driver

LSIs for driving the TFT (Thin Film Transistor) array and a backlight.

The a-Si TFT LCD panel structure is injected liquid crystal material into a narrow gap between the TFT

array glass substrate and a monochrome-filter glass substrate.

Grayscale data signals from a host system (e.g. signal generator, etc.) are modulated into best form for

active matrix system by a signal processing board, and sent to the driver LSIs which drive the individual

TFT arrays.

The TFT array as an electro-optical switch regulates the amount of transmitted light from the backlight

assembly, when it is controlled by data signals. Monochrome images are created by regulating the

amount of transmitted light through the TFT array.

1.2 APPLICATION

• Monochrome monitor system

1.3 FEATURES

• Ultra-wide viewing angle (Adopti on of Super- Advanced Super Fine TFT (SA-SFT))

• High luminance

• High contrast

• Low reflection

• High resolution

• 256 gray scales per 1 sub-pixel

• L VDS interface

• Adjustable gamma characteristics by using built-in 10-bit LUT (look up table)

• Selectable LVDS data input map

• Selectable LVDS data transmission mode

• Small foot print

• Incorporated direct type backlight

• Replaceable backlight unit and inverter

• Compliance with the European RoHS directive (2002/95/EC)

(From product which was produced after April. 1, 2006)

• Differences between NL256204AM15-01 and NL256204AM15-01A

NL256204AM15-01/01A

Item NL256204AM15-01 NL256204AM15-01A

White chromaticity Wx, Wy = (0.255, 0.310) (typ.) Wx, Wy = (0.280, 0.304) (typ.)

Backlight unit

(Replaceable part)

201LHS07 201LHS08

DATA SHEET DOD-PP-0209 (8th edition)

4

Page 5

2. GENERAL SPECIFICATIONS

Display area

Diagonal size of display

NL256204AM15-01/01A

399.36 (H) × 319.488 (V) mm

51 cm (20.1 inches)

Drive system

Display gray scale

Pixel

Pixel arrangement

Sub-pixel pitch

Pixel pitch

Module size

Weight

Contrast ratio

Viewing angle

Designed viewing direction

Polarizer surface

Polarizer pencil-hardness

Response time

Luminance

White chromaticity

a-Si TFT active matrix

256 gray scales per 1 sub-pixel (8-bit) (766 gray scales per 1 pixel)

2,560 (H) × 2,048 (V) pixels (1 pixel consists of 3 sub pixels (LCR))

LCR Vertical stripe

0.052 (H) × 0.156 (V) mm

0.156 (H) × 0.156 (V) mm

423.4 (W) × 343.5 (H) × 43.5 (D) mm (typ.)

2,440 g (typ.)

600:1 (typ.)

≥

At the contrast ratio

10:1

• Horizontal: Right side 85° (typ.), Left side 85° (typ.)

• Vertical: Up side 85° (typ.), Down side 85° (typ.)

Viewing angle with optimum grayscale (γ=DICOM): normal axis (perpendicular)

Note1

Antiglare

2H (min.) [by JIS K5400]

Ton + Toff (10%

←→

90%)

30 ms (typ.)

At the maximum luminance control

850 cd/m

2

(typ.)

NL256204AM15-01 Wx, Wy = (0.255, 0.310) (typ.)

NL256204AM15-01A Wx, Wy = (0.280, 0.304) (typ.)

Signal system

Power supply voltage

4 ports LVDS interface

[LCR 8-bit signals, Data enable signal (DE), Dot clock (CLK)]

LCD panel signal processing board: 12.0V

Inverter: 12.0V

Direct light type: 12 cold cathode fluorescent lamps with an inverter

Backlight

Power consumption

At checkered flag pattern, the maximum luminance control

49.2 W (typ.)

Note1: When the product luminance is 850cd/m

DATA SHEET DOD-PP-0209 (8th edition)

NL256204AM15-01

NL256204AM15-01A

2

, the gamma characteristic is designed to γ=DICOM.

Replaceable parts

• Backlight unit: Type No.: 201LHS07

• Inverter: Type No.: 201PW121

Replaceable parts

• Backlight unit: Type No.: 201LHS08

• Inverter: Type No.: 201PW121

5

Page 6

NL256204AM15-01/01A

N

N

N

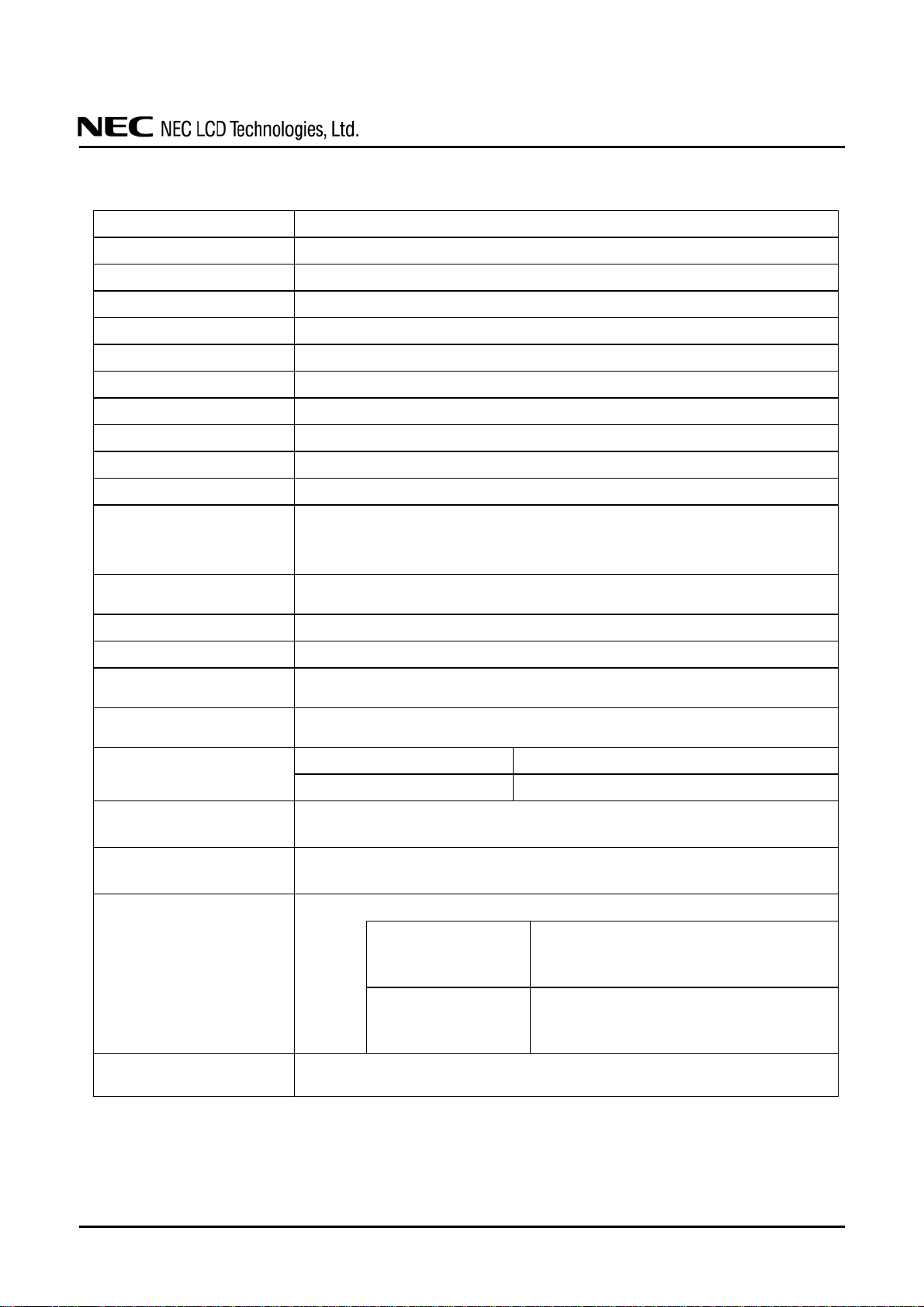

3. BLOCK DIAGRAM

Note1: Relations between GND (Signal ground), FG (Frame ground) and GNDB (Inverter ground) in the

Note2: GND, FG and GNDB must be connected to customer equipment’s ground, and it is recommended that

Host LCD module (product)

DA0+/DA1+/DA2+/CKA+/DA3+/-

DB0+/DB1+/DB2+/CKB+/DB3+/-

DC0+/DC1+/DC2+/CKC+/DC3+/-

DD0+/DD1+/DD2+/CKD+/DD3+/-

MOD[0:1]

BSEL[0:1]

CSR, CSL

SCLK

SDAT

VDD

GND

ote1, Note2

FG

ote1, Note2

VDDB

BRTC

BRTH

BRTI

BRTP

PWSEL

GNDB

ote1, Note2

Fuse

LVDS receiver

LVDS receiver

Fuse

Controller

DC/DC

Converter

Inverter

2,048 lines

V-driver

Power

supply for

drivers

LCD module are as follows.

GND - FG Connected

GND - GNDB Not connected

FG - GNDB Not connected

these grounds are connected together in customer equipment.

H-driver

7,680 lines

TFT LCD panel

H: 2,560 × 3 (L, C, R)

V: 2,048

H-driver

Backlight (Direct light type)

V-driver

DATA SHEET DOD-PP-0209 (8th edition)

6

Page 7

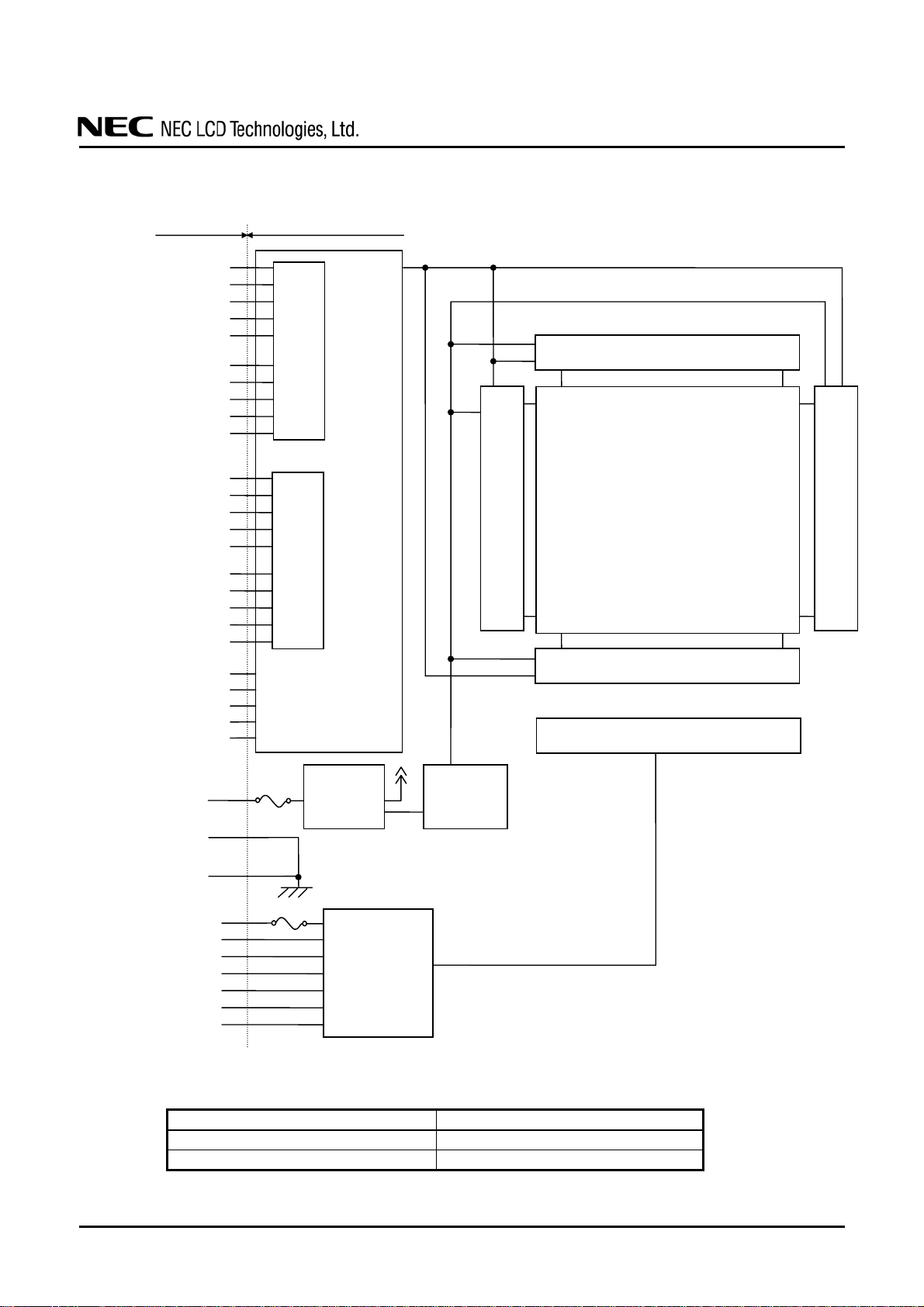

4. DETAILED SPECIFICATIONS

4.1 MECHANICAL SPECIFICATIONS

Parameter Specification Unit

NL256204AM15-01/01A

Module size

Display area

Weight 2,440 (typ.), 2,600 (max.) g

Note1: See "7. OUTLINE DRAWINGS".

4.2 ABSOLUTE MAXIMUM RATINGS

Parameter Symbol Rating Unit Remarks

Power supply voltage

LCD panel signal

processing board

Input voltage

for signals

Inverter

423.4 ± 1.0 (W) × 343.5 ± 1.0 (H) × 43.5 ± 1.0 (D)

399.36 (H) × 319.488 (V)

LCD panel signal

processing board

Inverter VDDB -0.3 to +15.0 V

Display signals

Note1

Function signal 1

Note2

Function signal 2

Note3

BRTI signal VBI -0.3 to +1.5 V

BRTP signal VBP -0.3 to +5.5 V

BRTC signal VBC -0.3 to +5.5 V

PWSEL signal VPSL -0.3 to +5.5 V

VDD -0.3 to +15.0 V

VD -0.3 to +3.6

VF1

-0.3 to +3.9

VF2

Note1 mm

Note1 mm

Ta = 2 5°C

V

Ta = 2 5°C

VDD=12.0V

Ta = 2 5°C

VDDB = 12.0V

Storage temperature Tst -20 to +60

Operating temperature

Relative humidity

Absolute humidity

Note6

Note6

Front surface TopF 0 to +55

Rear surface TopR 0 to +55

≤ 95

RH

AH

≤ 85

≤ 70

≤ 73

Note7

°C

°C

°C

%

%

%

g/m3

-

Note4

Note5

Ta ≤ 40°C

40 < Ta ≤ 50°C

50 < Ta ≤ 55°C

Ta > 5 5°C

Note1: DA0+/-, DA1+/-, DA2+/-, DA3+/-, CKA+/-, DB0+/-, DB1+/-, DB2+/-, DB3+/-, CKB+/-, DC0+/-,

DC1+/-, DC2+/-, DC3+/-, CKC+/-, DD0+/-, DD1+/-, DD2+/-, DD3+/-, CKD+/Note2: MOD0, MOD1, BSEL0, BSEL1

Note3: CSR, CSL, SCLK, SDAT

Note4: Measured at center of LCD panel surface (including self-heat)

Note5: Measured at center of LCD module's rear shield surface (including self-heat)

Note6: No condensation

Note7: Water amount at Ta = 55°C and RH = 70%

DATA SHEET DOD-PP-0209 (8th edition)

7

Page 8

NL256204AM15-01/01A

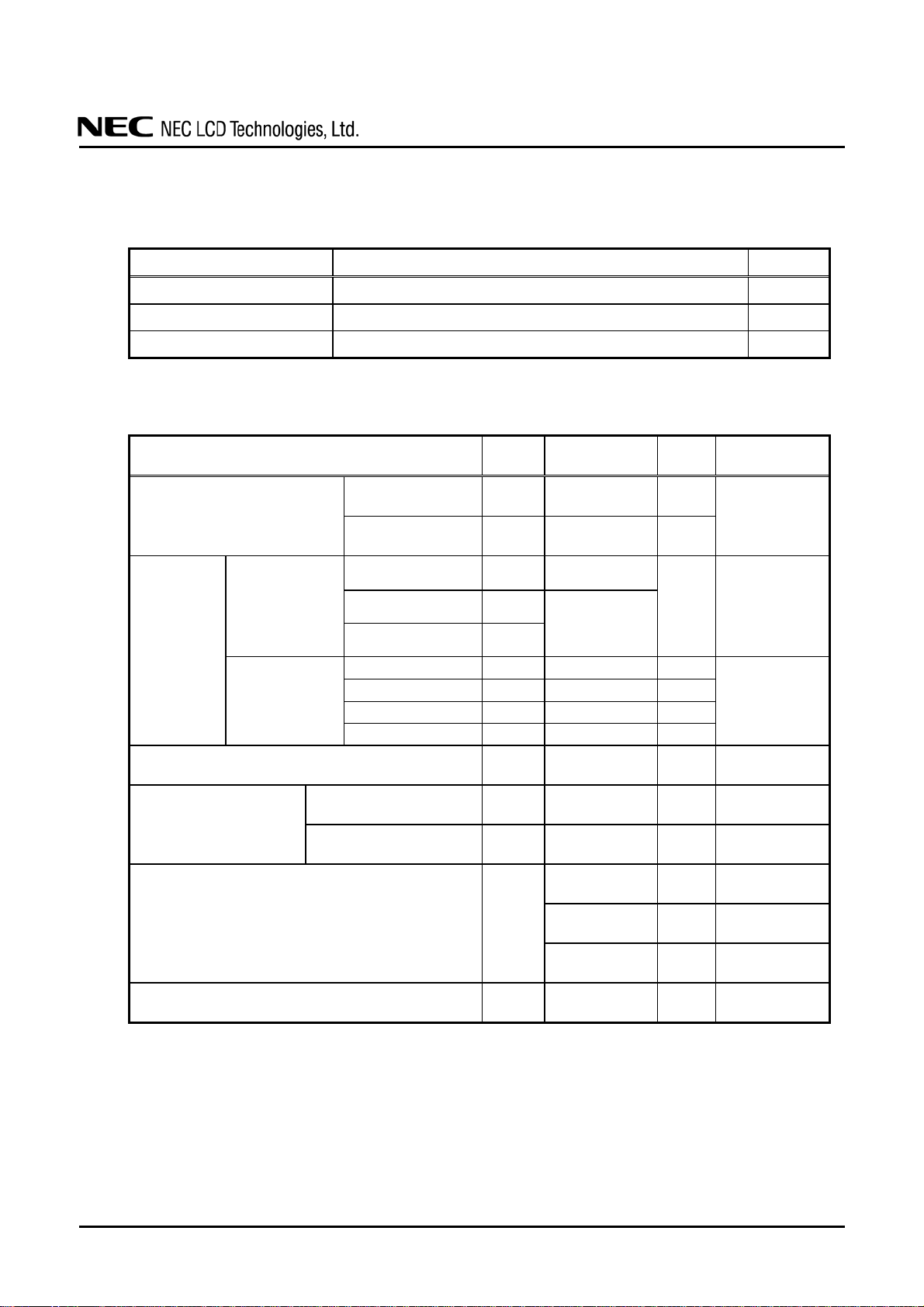

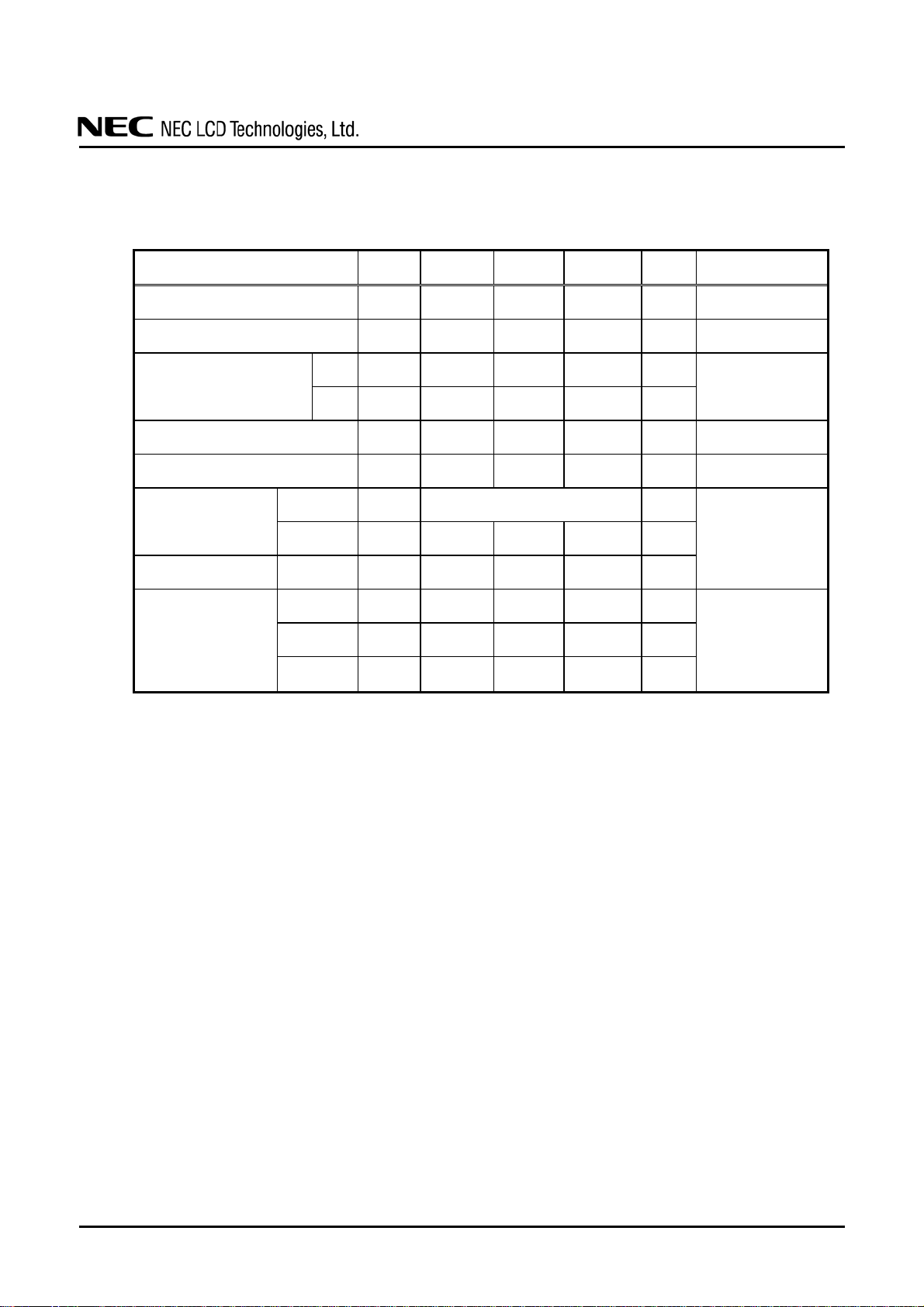

4.3 ELECTRICAL CHARACTERISTICS

4.3.1 LCD panel signal processing board

Parameter Symbol min. typ. max. Unit Remarks

Power supply voltage VDD 10.8 12.0 13.2 V -

Power supply current IDD -

Differential input threshold

voltage for Display signals

Input voltage swing VI 0 - 2.4 V Note4

High VTH - - +100 mV

Low VTL -100 - - mV

900

Note1

1,800

Note2

mA

(Ta = 25°C)

at VDD = 12.0V,

Mode 0 is selected.

at VCM= 1.2V

Note3, Note4

Terminating resistance RT - 100 -

Input voltage for

Function signal 1

Input current for

Function signal 1

Input voltage for

Function signal 2

High VFH1 Keep this pin open. -

Low VFL1 0 - 0.8 V

Low IFL1 -10 - 10

High V+ - - 2.3 V

Low V- 0.5 - - V

Hysteresis VH 0.4 - - V

Ω

Note5

μA

Note6

Note1: Checkered flag pattern [by EIAJ ED-2522]

Note2: Pattern for maximum current

Note3: Common mode voltage for LVDS receiver

Note4: DA0+/-, DA1+/-, DA2+/-, DA3+/-, CKA+/-, DB0+/-, DB1+/-, DB2+/-, DB3+/-, CKB+/-,

DC0+/-, DC1+/-, DC2+/-, DC3+/-, CKC+/-, DD0+/-, DD1+/-, DD2+/-, DD3+/-, CKD+/-.

Note5: MOD0, MOD1, BSEL0, BSEL1

Note6: CSR, CSL, SCLK, SDAT

-

DATA SHEET DOD-PP-0209 (8th edition)

8

Page 9

NL256204AM15-01/01A

4.3.2 Inverter (Ta = 25°C)

Parameter Symbol min. typ. max. Unit Remarks

Power supply voltage VDDB 11.4 12.0 12.6 V -

VDDB = 12.0V,

Power supply current IDDB - 3,200 4,000

BRTI signal VBI 0 - 1.0 V

High VBPH 2.0 - 5.25 V

Low VBPL 0 - 0.8 V

High VBCH 2.0 - 5.25 V

Low VBCL 0 - 0.8 V

High VPSLH 2.0 - 5.25 V

Low VPSLL 0 - 0.8 V

High IBPH - - 3.5 mA

Low IBPL -1.6 - - mA

High IBCH - - 440

Low IBCL -610 - -

High IPSLH - - 440

Low IPSLL -610 - -

Input voltage

for signals

Input current

for signals

BRTP signal

BRTC signal

PWSEL signal

BRTI signal IBI -130 - BRTP signal

BRTC signal

PWSEL signal

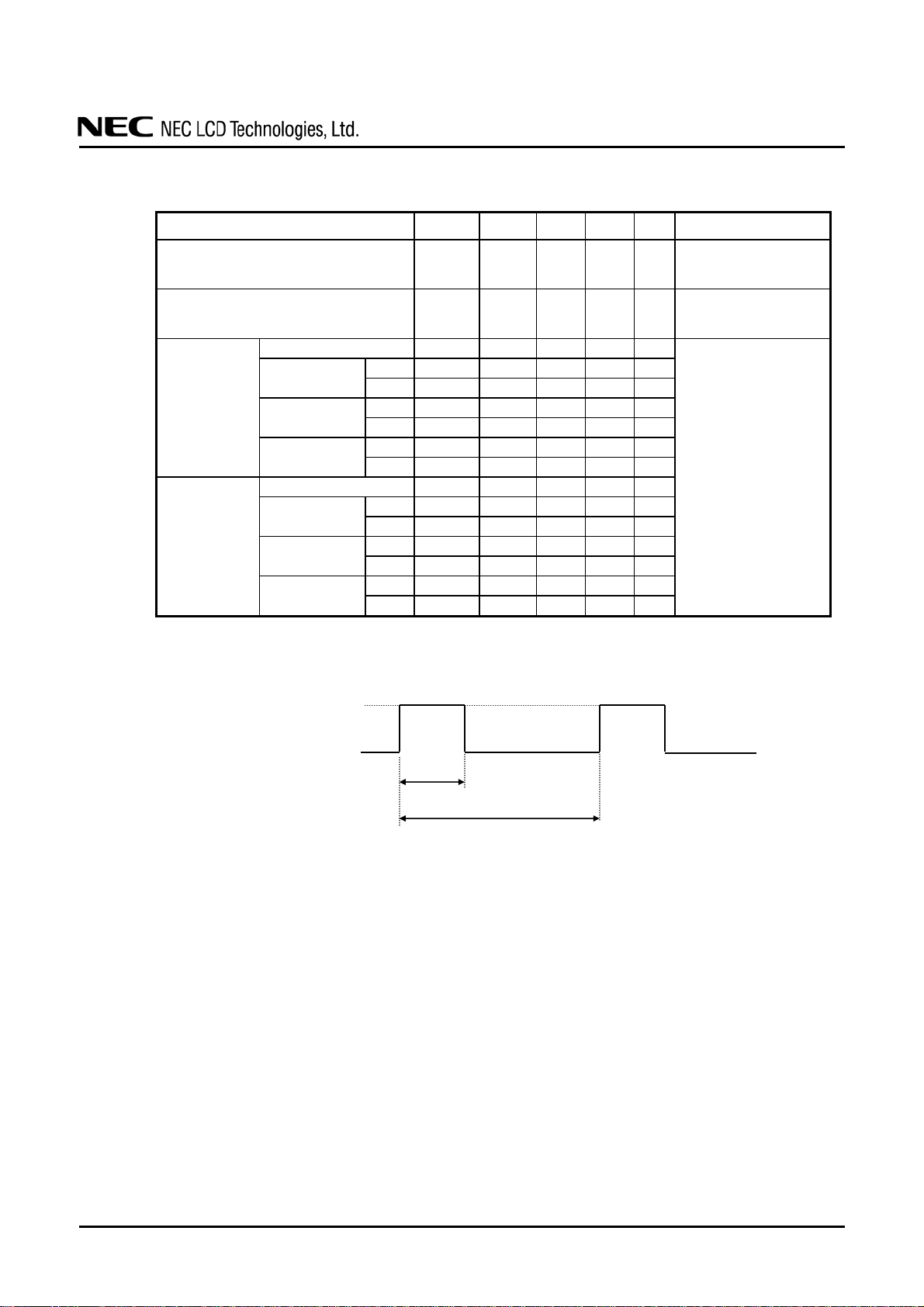

4.3.3 Inverter current wave

3,200 (mA) typ.

0 (A)

Duty

Luminance control frequency

Maximum luminance control: 100%

Minimum luminance control: 20%

Luminance control frequency: 285Hz (typ.)

Note1: Luminance control frequency indicate the input pulse frequency, when select the external pulse

control. See "4.6.2 Detail of BRTP timing".

Note2: The power supply lines (VDDB and GNDB) have large ripple voltage (See "4.3.4 Power

supply voltage ripple".) during luminance control. There is the possibility that the ripple

voltage produces acoustic noise and signal wave noise in audio circuit and so on. Put a

capacitor (5,000 to 6,000μF) between the power supply lines (VDDB and GNDB) to reduce the

noise, if the noise occurred in the circuit.

At the maximum

mΑ

luminance control

μΑ

μΑ

μΑ

μΑ

μΑ

-

DATA SHEET DOD-PP-0209 (8th edition)

9

Page 10

NL256204AM15-01/01A

4.3.4 Power supply voltage ripple

This product works, even if the ripple voltage levels are beyond the permissible values as following

the table, but there might be noise on the display image.

Power supply voltage

(Measure at input terminal of power supply)

Ripple voltage Note1

Unit

VDD 12.0 V

VDDB 12.0 V

Note1: The permissible ripple voltage includes spike noise.

Example of the power supply connection

a) Separate the power supply b) Put in the filter

Power

Power

4.3.5 Fuse

Parameter

VDD

VDDB 0453007 Littelfuse Inc.

Type Supplier

FHC20 502AD

Note1: The power supply capacity should be more than the fusing current. If it is less than the fusing

current, the fuse may not blow in a short time, and then nasty smell, smoke and so on may

occur.

VDD

VDDB

Fuse

KAMAYA ELECTRIC

Co., Ltd.

Power

≤ 100

≤ 200

Filter

Filter

Rating Fusing current Remarks

5A

24V

7A

125V

12.5A,

5s max.

14A,

5s max.

mVp-p

mVp-p

VDD

VDDB

Note1

DATA SHEET DOD-PP-0209 (8th edition)

10

Page 11

NL256204AM15-01/01A

4.4 POWER SUPPLY VOLTAGE SEQUENCE

4.4.1 LCD panel signal processing board

VDD

Note1

0V

VDD ON

10.8V

9.6V

VDD dip < 20ms

5ms < Tr < 80ms

LVDS Signals *1,*2

Note2

0V

CSR, CSL, SCLK, SDAT

Note2

0V

VALID period

t≥20ms Note3

VALID period

10ms < t < 35ms

10ms < t < 35ms

*1: DA0+/-, DA1+/-, DA2+/-, DA3+/-, CKA+/-, DB0+/-, DB1+/-, DB2+/-, DB3+/-, CKB+/-,

DC0+/-, DC1+/-, DC2+/-, DC3+/-, CKC+/-, DD0+/-, DD1+/-, DD2+/-, DD3+/-, CKD+/-

*2: LVDS signals should be measured at the terminal of 100Ω resistance.

Note1: In terms of voltage variation (voltage drop) while VDD rising edg e is below 1 0.8V, a protection

circuit may work, and then this product may not work.

Note2: LVDS signals and CSR, CSL, SCLK, SDAT must be Low or High-impedance, exclude the

VALID period (See above sequence diagram), in order to avoid that internal circuits is

damaged.

If some of signals are cut while this product is working, even if the signal input to it once again,

it might not work normally. VDD should be cut when the display and function signals are

stopped.

Note3: At the beginning of the serial communication mode, take 20ms or more after the LVDS signal

input.

4.4.2 Inverter

Voltage

tr≤800ms

BRTC

12.0V

11.4V

VDDB

0V

0ms<t

Note1: The backlight should be turned on within the valid period of LVDS signals, in order to avoid

unstable data display.

Note2: If tr is more than 800ms, the backlight will be turned off by a protection circuit for inverter.

Note3: When VDDB is 0V or BRTC is Low, PWSEL must be set to Low or Open.

VDD OFF

10.8V

VDD ON

10.8V

Toff > 50ms

0ms < t < 35ms

Time

0ms<t

DATA SHEET DOD-PP-0209 (8th edition)

11

Page 12

4.5 CONNECTIONS AND FUNCTIONS FOR INTERFACE PINS

4.5.1 LCD panel signal processing board

CN1 socket (LCD module side): FI-WE41P-HFE (Japan Aviation Electronics Industry Limited (JAE))

Adaptable plug: FI-W41S (Japan Aviation Electronics Industry Limited (JAE))

Pin No. Symbol Signal Remarks

1 GND Signal ground Note1

2 CSR Chip selection R

3 CSL Chip selection L

4 SCLK Serial Clock

5 SDAT Serial Data

6 MOD0

Selection of LVDS Data Transmission Mode

(Pull-up 25kΩ)

7 MOD1

8 BSEL0

Selection of LVDS data input map

(Pull-up 25kΩ)

9 BSEL1

10 RSVD Reserved Keep this pin Open.

11 GND Signal ground Note1

12 DB3+

13 DB314 GND Signal ground Note1

15 CKB+

16 CKB17 GND Signal ground Note1

18 DB2+

19 DB220 GND Signal ground Note1

21 DB1+

22 DB123 GND Signal ground Note1

24 DB0+

25 DB026 GND Signal ground Note1

27 DA3+

28 DA329 GND Signal ground Note1

30 CKA+

31 CKA32 GND Signal ground Note1

33 DA2+

34 DA235 GND Signal ground Note1

36 DA1+

37 DA138 GND Signal ground Note1

39 DA0+

40 DA041 GND Signal ground Note1

Pixel data B3 LVDS differential data input Note2

Pixel clock B LVDS differential clock input Note2

Pixel data B2 LVDS differential data input Note2

Pixel data B1 LVDS differential data input Note2

Pixel data B0 LVDS differential data input Note2

Pixel data A3 LVDS differential data input Note2

Pixel clock A LVDS differential clock input Note2

Pixel data A2 LVDS differential data input Note2

Pixel data A1 LVDS differential data input Note2

Pixel data A0 LVDS differential data input Note2

NL256204AM15-01/01A

LUT communication control signal

See "4.13 TEN-bit LOOK UP TABLE FOR

GAMMA ADJUSTMENT".

See "4.10 LVDS DATA TRANSMISSION MODE".

MOD0 MOD1 Mode

Open Open 0

Open Low 1

Low Open Reserved

Low Low 0

See "4.7 METHOD OF CONNECTION FOR

LVDS TRANSMITTER".

BSEL0 BSEL1 Mode

Open Open A

Open Low B

Low Open C

Low Low A

DATA SHEET DOD-PP-0209 (8th edition)

12

Page 13

NL256204AM15-01/01A

Note1: All GND terminals should be used without any non-connected lines.

Note2: Twist pair wires with 100Ω (Characteristic impedance) should be used between LCD panel signal

processing board and LVDS transmitter.

CN2 socket (LCD module side): FI-WE31P-HFE (Japan Aviation Electronics Industry Limited (JAE))

Adaptable plug: FI-W31S (Japan Aviation Electronics Industry Limited (JAE))

Pin No. Symbol Signal Remarks

1 GND Signal ground Note1

2 DD3+

3 DD34 GND Signal ground Note1

5 CKD+

6 CKD7 GND Signal ground Note1

8 DD2+

9 DD210 GND Signal ground Note1

11 DD1+

12 DD113 GND Signal ground Note1

14 DD0+

15 DD016 GND Signal ground Note1

17 DC3+

18 DC319 GND Signal ground Note1

20 CKC+

21 CKC22 GND Signal ground Note1

23 DC2+

24 DC225 GND Signal ground Note1

26 DC1+

27 DC128 GND Signal ground Note1

29 DC0+

30 DC031 GND Signal ground Note1

Note1: All GND terminals should be used without any non-connected lines.

Note2: Twist pair wires with 100Ω (Characteristic impedance) should be used between LCD panel signal

processing board and LVDS transmitter.

CN3 socket (LCD module side): IL-Z-8PL-SMTYE (Japan Aviation Electronics Industry Limited (JAE))

Adaptable plug: IL-Z-8S-S125C (Japan Aviation Electronics Industry Limited (JAE))

Pin No. Symbol Function Description

1 VDD

2 VDD

3 VDD

4 VDD

5 GND

6 GND

7 GND

8 GND

Note1: All VDD and GND terminals should be used without any non-connected lines.

Pixel data D3 LVDS differential data input Note2

Pixel clock D LVDS differential clock input Note2

Pixel data D2 LVDS differential data input Note2

Pixel data D1 LVDS differential data input Note2

Pixel data D0 LVDS differential data input Note2

Pixel data C3 LVDS differential data input Note2

Pixel clock C LVDS differential clock input Note2

Pixel data C2 LVDS differential data input Note2

Pixel data C1 LVDS differential data input Note2

Pixel data C0 LVDS differential data input Note2

Power supply Note1

Signal ground Note1

DATA SHEET DOD-PP-0209 (8th edition)

13

Page 14

4.5.2 Inverter

CN201 socket (LCD module side): DF3Z-8P-2H (2∗) (HIROSE ELECTRIC Co,.Ltd.)

Adaptable plug: DF3-8S-2C (HIROSE ELECTRIC Co,.Ltd.)

Pin No. Symbol Function Description

1 GNDB

2 GNDB

3 GNDB

4 GNDB

5 VDDB

6 VDDB

7 VDDB

8 VDDB

Note1: All VDDB and GNDB terminals should be used without any non-connected lines.

CN202 socket (LCD module side): IL-Z-9PL-SMTYE (Japan Aviation Electronics Industry Limited (JAE))

Adaptable plug: IL-Z-9S-S125C3 (Japan Aviation Electronics Industry Limited (JAE))

Pin No. Symbol Function Description

1 GNDB

2 GNDB

3 N.C. - Keep this pin Open.

4 BRTC

5 BRTH

6 BRTI

7 BRTP BRTP signal

8 GNDB Inverter ground Note1

9 PWSEL Selection of luminance control signal method

Note1: All GNDB terminals should be used without any non-connected lines.

Note2: When VDDB is 0V or BRTC is Low, PWSEL must be set to Low or Open.

4.5.3 Positions of socket

Inverter

NL256204AM15-01/01A

Inverter ground Note1

Power supply Note1

Inverter ground Note1

Backlight ON/OFF control signal

Luminance control terminal

Rear side

Insert direction→

1

CN202

9

← Insert direction

10

CN201

1

Insert direction→

41

CN1

1

31

CN2

1

8

CN3

1

High or Open: Backlight ON

Low: Backlight OFF

See "4.6 LUMINANCE CONTROL".

See "4.6 LUMINANCE CONTROL ".

Note2

LCD panel signal processing board

DATA SHEET DOD-PP-0209 (8th edition)

14

Page 15

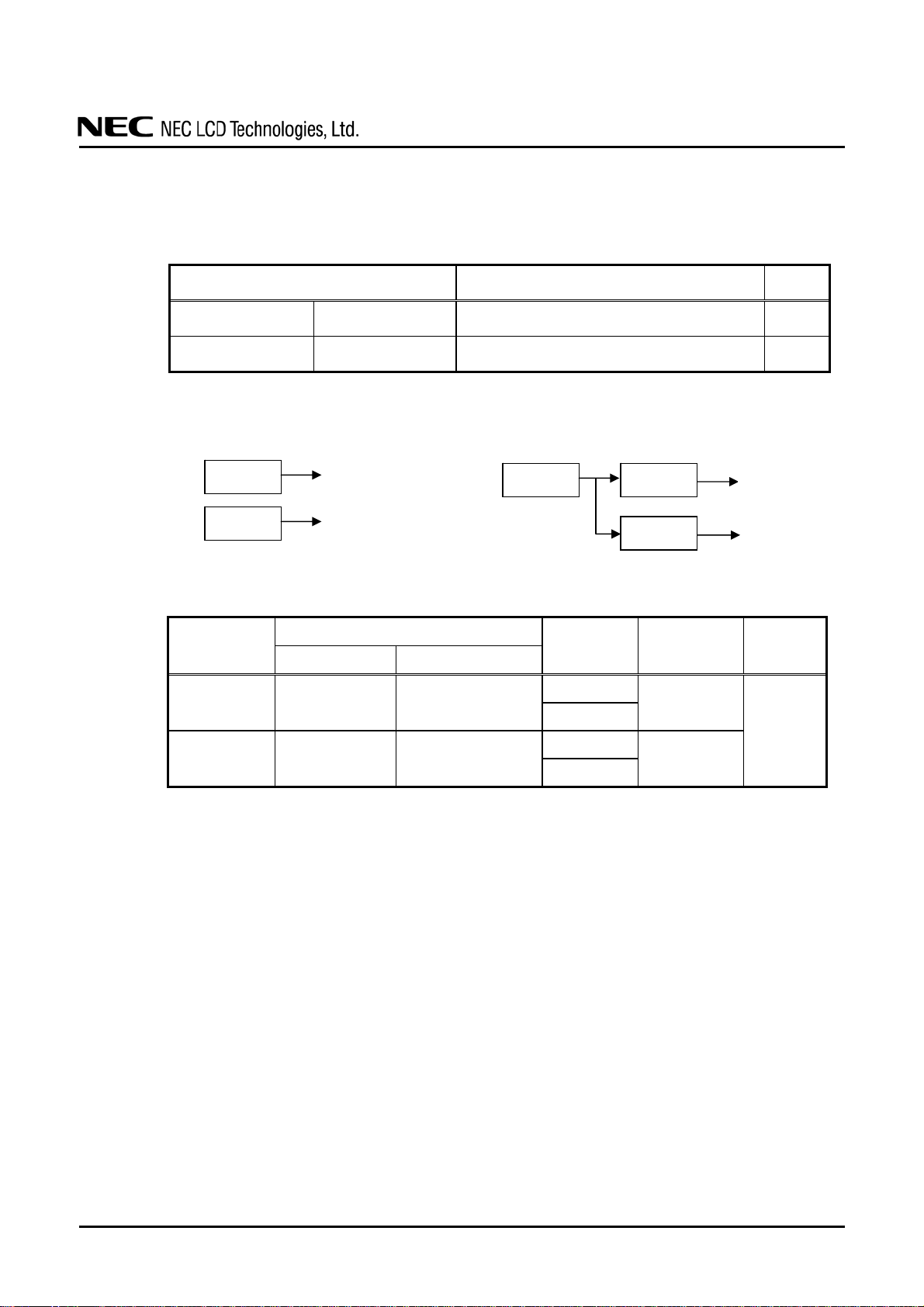

4.6 LUMINANCE CONTROL

4.6.1 Luminance control methods

Method Adjustment and luminance ratio PWSEL terminal BRTP terminal

• Adjustment

The variable resistor (R) for luminance control should be 10kΩ

±5%, 1/10W. Minimum point of the resistance is the mini mum

luminance and maximum point of the resistance is the maximum

luminance.

The resistor (R) must be connected between BRTH-BRTI

Variable resistor

control

Note1

terminals.

• Luminance ratio Note3

• Adjustment

Voltage control method works, when BRTH terminal is 0V and

VBI voltage is input between BRTI-BRTH terminals. This

control method can carry out continuation adjustment of

luminance.

Voltage control

Note1

Luminance is the maximum when BRTI terminal is Open.

• Luminance ratio Note3

• Adjustment

BRTI Voltage (VBI) Luminance ratio

Pulse width modulation (PWM) method works, when PWSEL

terminal is Low and PWM signal (BRTP signal) is input into

Pulse width

modulation

Note1

Note2

BRTP terminal. The luminance is controlled by duty ratio of

BRTP signal.

• Luminance ratio Note3

Duty ratio Note4 Luminance ratio

Note1: In case of the variable resistor control method and the voltage control method, noises may

appear on the display image depending on the input signals timing for LCD panel signal

processing board.

Use PWM method, if interference noises appear on the display image!

Note2: The inverter will stop working, if the Low period of BRTP signal is more than 50ms while

BRTC signal is High or Open. Then the backlight will not turn on anymore, even if BRTP

signal is input again. This is not out of orde r. The inverter will start to wo rk when power is

supplied again.

Note3: These data are the target values.

Note4: See "4.6.2 Detail of BRTP timing".

NL256204AM15-01/01A

BRTH

R

Resistance Luminance ratio

0 Ω

10 kΩ

0V 30% (Min. Luminance)

1.0V 100% (Max. Luminance)

0.2 20% (Min. Luminance)

1.0 100% (Max. Luminance)

BRTI

30% (Min. Luminance)

100% (Max. Luminance)

High or Open Open

Low BRTP signal

DATA SHEET DOD-PP-0209 (8th edition)

15

Page 16

≤

≤

4.6.2 Detail of BRTP timing

(1) Timing diagrams

• Outline chart

BRTC

PWSEL (Low)

BRTP

• Detail of A part

BRTP

(2) Each parameter

NL256204AM15-01/01A

tPWL ≤ 50ms

A

0ms ≤ tPWL ≤ 50ms

VBPH

VBPL

tPWH

tPW

Parameter Symbol min. typ. max. Unit Remarks

0ms

tPWL

0ms ≤ tPWL

50ms

Luminance control frequency FL 185 - 325 Hz Note1, Note2

Duty ratio DL 0.2 - 1.0 - Note1, Note3

Low period tPWL 0 - 50 ms Note4

Note1: Definition of parameters is as follows.

FL =

1

tPW

DL =

tPWH

tPW

Note2: See the following formula for luminance control frequency.

Luminance control frequency = 1/tv × (n+0.25) [or (n + 0.75)]

n = 1, 2, 3 · · · · · ·

tv: Vertical cycle (See "4.9.1 Timing characteristics".)

The interference noise of luminance control frequency and input signal frequency for

LCD panel signal processing board may appear on a display. Set up luminance control

frequency so that the interference noise does not appear!

Note3: See "4.6.1 Luminance control methods".

Note4: If tPWL is more than 50ms, the backlight will be turned off by a protection circuit for

inverter. The inverter will start to work when power is supplied again.

DATA SHEET DOD-PP-0209 (8th edition)

16

Page 17

4.7 METHOD OF CONNECTION FOR LVDS TRANSMITTER

LVDS data input map is selectable by BSEL0 and BSEL1 terminal.

Pixel data

Pixel data

A

B

Bit mapping Transmitter Pin Assignment

BSEL[1:0] Note1, Note2 Dual type LVDS TX CN1

[H:H],

[L:L]

Mode A Mode B Mode C

LA2 LA7 LA0 TA0 R12 R10

LA3 LA6 LA1 TA1 R13 R11 Note3

LA4 LA5 LA2 TA2 R14 R12 ATALA5 LA4 LA3 TA3 R15 R13 ATA+

LA6 LA3 LA4 TA4 R16 R14

LA7 LA2 LA5 TA5 R17 R15

CA2 CA7 CA0 TA6 G12 G10

CA3 CA6 CA1 TB0 G13 G11

CA4 CA5 CA2 TB1 G14 G12

CA5 CA4 CA3 TB2 G15 G13 ATBCA6 CA3 CA4 TB3 G16 G14 ATB+

CA7 CA2 CA5 TB4 G17 G15

RA2 RA7 RA0 TB5 B12 B10

RA3 RA6 RA1 TB6 B13 B11

RA4 RA5 RA2 TC0 B14 B12

RA5 RA4 RA3 TC1 B15 B13

RA6 RA3 RA4 TC2 B16 B14 ATC-

RA7 RA2 RA5 TC3 B17 B15 ATC+

Hsync Hsync Hsync TC4 HSYNC HSYNC

Vsync Vsync Vsync TC5 VSYNC VSYNC

LA0 LA1 LA6 TD0 R10 R16

LA1 LA0 LA7 TD1 R11 R17

CA0 CA1 CA6 TD2 G10 G16 ATD-

CA1 CA0 CA7 TD3 G11 G17 ATD+

RA0 RA1 RA6 TD4 B10 B16

RA1 RA0 RA7 TD5 B11 B17

N.C. N.C. N.C. TD6 - -

CLK CLK CLK CLK CLK CLK

LB2 LB7 LB0 TA0 R22 R20

LB3 LB6 LB1 TA1 R23 R21

LB4 LB5 LB2 TA2 R24 R22 BTA-

LB5 LB4 LB3 TA3 R25 R23 BTA+

LB6 LB3 LB4 TA4 R26 R24

LB7 LB2 LB5 TA5 R27 R25

CB2 CB7 CB0 TA6 G22 G20

CB3 CB6 CB1 TB0 G23 G21

CB4 CB5 CB2 TB1 G24 G22

CB5 CB4 CB3 TB2 G25 G23 BTB-

CB6 CB3 CB4 TB3 G26 G24 BTB+

CB7 CB2 CB5 TB4 G27 G25

RB2 RB7 RB0 TB5 B22 B20

RB3 RB6 RB1 TB6 B23 B21

RB4 RB5 RB2 TC0 B24 B22

RB5 RB4 RB3 TC1 B25 B23

RB6 RB3 RB4 TC2 B26 B24 BTC-

RB7 RB2 RB5 TC3 B27 B25 BTC+

Hsync Hsync Hsync TC4 HSYNC HSYNC

Vsync Vsync Vsync TC5 VSYNC VSYNC

LB0 LB1 LB6 TD0 R20 R26

LB1 LB0 LB7 TD1 R21 R27

CB0 CB1 CB6 TD2 G20 G26 BTD-

CB1 CB0 CB7 TD3 G21 G27 BTD+

RB0 RB1 RB6 TD4 B20 B26

RB1 RB0 RB7 TD5 B21 B27

N.C. N.C. N.C. TD6 - -

CLK CLK CLK CLK CLK CLK

[H:L] [L:H]

DE DE DE TC6 DE DE

DE DE DE TC6 DE DE

Single type

LVDS Tx

THine

THC63LVD823

NS

DS90C387

NL256204AM15-01/01A

Output

Connector

ATC LK-

ATC LK+

BTCLKBTCLK+

Pin No. Signal name

40 DA0-

→

39 DA0+

→

37 DA1-

→

36 DA1+

→

34 DA2-

→

33 DA2+

→

28 DA3-

→

27 DA3+

→

31 CKA-

→

30 CKA+

→

25 DB0-

→

24 DB0+

→

22 DB1-

→

21 DB1+

→

19 DB2-

→

18 DB2+

→

13 DB3-

→

12 DB3+

→

16 CKB-

→

15 CKB+

→

DATA SHEET DOD-PP-0209 (8th edition)

17

Page 18

NL256204AM15-01/01A

BSEL[1:0] Note1, Note2 Dual type LVDS TX CN2

[H:H],

Pixel data

C

Pixel data

D

[L:L]

Mode A Mode B Mode C

LC2 LC7 LC0 TA0 R12 R10

LC3 LC6 LC1 TA1 R13 R11 Note3

LC4 LC5 LC2 TA2 R14 R12 CTA-

LC5 LC4 LC3 TA3 R15 R13 CTA+

LC6 LC3 LC4 TA4 R16 R14

LC7 LC2 LC5 TA5 R17 R15

CC2 CC7 CC0 TA6 G12 G10

CC3 CC6 CC1 TB0 G13 G11

CC4 CC5 CC2 TB1 G14 G12

CC5 CC4 CC3 TB2 G15 G13 CTB-

CC6 CC3 CC4 TB3 G16 G14 CTB+

CC7 CC2 CC5 TB4 G17 G15

RC2 RC7 RC0 TB5 B12 B10

RC3 RC6 RC1 TB6 B13 B11

RC4 RC5 RC2 TC0 B14 B12

RC5 RC4 RC3 TC1 B15 B13

RC6 RC3 RC4 TC2 B16 B14 CTC-

RC7 RC2 RC5 TC3 B17 B15 CTC+

Hsync Hsync Hsync TC4 HSYNC HSYNC

Vsync Vsync Vsync TC5 VSYNC VSYNC

LC0 LC1 LC6 TD0 R10 R16

LC1 LC0 LC7 TD1 R11 R17

CC0 CC1 CC6 TD2 G10 G16 CTD-

CC1 CC0 CC7 TD3 G11 G17 CTD+

RC0 RC1 RC6 TD4 B10 B16

RC1 RC0 RC7 TD5 B11 B17

N.C. N.C. N.C. TD6 - -

CLK CLK CLK CLK CLK CLK

LD2 LD7 LD0 TA0 R22 R20

LD3 LD6 LD1 TA1 R23 R21

LD4 LD5 LD2 TA2 R24 R22 DTA-

LD5 LD4 LD3 TA3 R25 R23 DTA+

LD6 LD3 LD4 TA4 R26 R24

LD7 LD2 LD5 TA5 R27 R25

CD2 CD7 CD0 TA6 G22 G20

CD3 CD6 CD1 TB0 G23 G21

CD4 CD5 CD2 TB1 G24 G22

CD5 CD4 CD3 TB2 G25 G23 DTB-

CD6 CD3 CD4 TB3 G26 G24 DTB+

CD7 CD2 CD5 TB4 G27 G25

RD2 RD7 RD0 TB5 B22 B20

RD3 RD6 RD1 TB6 B23 B21

RD4 RD5 RD2 TC0 B24 B22

RD5 RD4 RD3 TC1 B25 B23

RD6 RD3 RD4 TC2 B26 B24 DTC-

RD7 RD2 RD5 TC3 B27 B25 DTC+

Hsync Hsync Hsync TC4 HSYNC HSYNC

Vsync Vsync Vsync TC5 VSYNC VSYNC

LD0 LD1 LD6 TD0 R20 R26

LD1 LD0 LD7 TD1 R21 R27

CD0 CD1 CD6 TD2 G20 G26 DTD-

CD1 CD0 CD7 TD3 G21 G27 DTD+

RD0 RD1 RD6 TD4 B20 B26

RD1 RD0 RD7 TD5 B21 B27

N.C. N.C. N.C. TD6 - -

CLK CLK CLK CLK CLK CLK

[H:L] [L:H]

DE DE DE TC6 DE DE

DE DE DE TC6 DE DE

Note1: High must be Open.

Note2: Do not change the setting of BSEL0 and BSEL1 during VDD ON period.

Note3: Twist pair wires with 100Ω (Characteristic impedance) should be used between LCD panel

signal processing board and LVDS transmitter.

Single type

LVDS Tx

THine

THC63LVD823

NS

DS90C387

Output

Connector

CTCLKCTCLK+

DTCLK-

DTCLK+

Pin No. Signal name

→

30 DC0-

→

29 DC0+

→

27 DC1-

→

26 DC1+

→

24 DC2-

→

23 DC2+

→

18 DC3-

→

17 DC3+

→

21 CKC-

→

20 CKC+

→

15 DD0-

→

14 DD0+

→

12 DD1-

→

11 DD1+

→

→

→

→

→

→

9 DD28 DD2+

3 DD32 DD3+

6 CKD5 CKD+

DATA SHEET DOD-PP-0209 (8th edition)

18

Page 19

NL256204AM15-01/01A

4.8 DISPLAY GRAY SCALE AND INPUT DATA SIGNALS

This product can display 256 gray scales in each LCR sub-pixel and 766 gray scales per 1 pixel. Also the

relation between display gray scale and input data signals is as the following table.

Data signal (0: Low level, 1: High level)

LA7 LA6 LA5 LA4 LA3 LA2 LA1 LA0 CA7 CA6 CA5 CA4 CA3 CA2 CA1 CA0 RA7 RA6 RA5 RA4 RA3 RA2 RA1 RA0

Display gray scale

Left sub-pixel gray scale

Center sub-pixel gray scale

Right sub-pixel gray scale

LB7 LB6 LB5 LB4 LB3 LB2 LB1 LB0 CB7 CB6 CB5 CB4 CB3 CB2 CB1 CB0 RB7 RB6 RB5 RB4 RB3 RB2 RB1 RB0

LC7 LC6 LC5 LC4 LC3 LC2 LC1 LC0 CC7 CC6 CC5 CC4 CC3 CC2 CC1 CC0 RC7 RC6 RC5 RC4 RC3 RC2 RC1 RC0

LD7 LD6 LD5 LD4 LD3 LD2 LD1 LD0 CD7 CD6 CD5 CD4 CD3 CD2 CD1 CD0 RD7 RD6 RD5 RD4 RD3 RD2 RD1 RD0

Black

dark

bright

White

Black

dark

bright

White

Black

dark

bright

White

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 1

0 0 0 0 0 0 1 0

↑

↓

:

:

1 1 1 1 1 1 0 1

1 1 1 1 1 1 1 0

1 1 1 1 1 1 1 1

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

↑

↓

:

:

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

↑

↓

:

:

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

:

:

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 1

0 0 0 0 0 0 1 0

:

:

1 1 1 1 1 1 0 1

1 1 1 1 1 1 1 0

1 1 1 1 1 1 1 1

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

:

:

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 1

0 0 0 0 0 0 1 0

1 1 1 1 1 1 0 1

1 1 1 1 1 1 1 0

1 1 1 1 1 1 1 1

:

:

:

:

:

:

DATA SHEET DOD-PP-0209 (8th edition)

19

Page 20

4.9 INPUT SIGNAL TIMINGS

4.9.1 Timing characteristics

CLK

DATA

DE

CLK-DATA

Horizontal

Vertical

(One frame)

CLK-DE

Note1: Definition of parameters is as follows.

tc = 1CLK, th = 1H

Note2: See the data sheet of LVDS transmitter.

Note3: "th" (CLK number) should be fixed to "16n+k" (n= natural number: 1,2,3⋅⋅⋅, k=0, 2, 4 or 6).

In case "th" is not the specified value, it may cause display deterioration.

e.g.: "th" (CLK number)= 660, 662, 672, 674, 676, 678, 688, 690

4.9.2 Input signal timing chart

DE

Invalid Invalid Invalid Invalid

DE

CLK

DATA (A) to (D)

NL256204AM15-01/01A

Parameter Symbol min. typ. max. Unit Remarks

Frequency 1/tc 80.0 83.26 85.0 MHz 12.01 ns (typ.)

Duty - -

Rise time, Fall time -

Setup time - ns

Hold time - ns

Rise time, Fall time -

Cycle th

Display period thd 640 CLK

Cycle tv

Display period tvd 2,048 H

Setup time - ns

Hold time - ns

Rise time, Fall time -

tvd = 2,048H (fixed)

7.72 8.071 660 672 690 CLK

- 16.667 - ms

2,053 2,064 - H

tv

th

tc

-

-

-

thd = 640CLK (fixed)

ns

ns

μs

ns

Note2

Note2

123.9 kHz (typ.)

Note1, Note3

60.0 Hz (typ.)

Note1

Note2

InvalidInvalid

DATA SHEET DOD-PP-0209 (8th edition)

20

Page 21

4.10 LVDS DATA TRANSMISSION MODE

Transmission mode of LVDS data is selectable by MOD0 and MOD1 terminal.

MOD[1:0]

Note1

1 0

Mode name Data transmission chart

Pixel Data A

Open Open

Mode 0

L/R

transmission

mode

Low Low

Pixel Data B

Pixel Data C

Pixel Data D

LA

CA

RA

LB

CB

RB

CLK1

LC

CC

RC

LD

CD

RD

CLK2

NL256204AM15-01/01A

DO(7:0) D2(7:0) D4(7:0)

D1(7:0) D3(7:0) D5(7:0)

D1280(7:0) D1282(7:0) D1284(7:0)

D1281(7:0) D1283(7:0) D1285(7:0)

Mode 1

Open Low

4 divided

transmission

mode

Low Open Reserved

Note1: High must be Open.

Pixel Data A

Pixel Data B

Pixel Data C

Pixel Data D

LA

CA

RA

LB

CB

RB

CLK1

LC

CC

RC

LD

CD

RD

CLK2

DO(7:0) D1(7:0) D2(7:0)

D640(7:0) D641(7:0) D642(7:0)

D1280(7:0) D1281(7:0) D1282(7:0)

D1920(7:0) D1921(7:0) D1922(7:0)

-

DATA SHEET DOD-PP-0209 (8th edition)

21

Page 22

4.11 DISPLAY POSITIONS

(1) Mode0: MOD0= Open, MOD1= Open / MOD0= Low, MOD1= Low

D (0, 0) D (1, 0) D (1280, 0) D (1281, 0)

NL256204AM15-01/01A

LA CA RA LB CB RB

0, 0 1, 0

0, 1 1, 1

•

•

•

0, 2046 1, 2046

0, 2047 1, 2047

•

•

•

• • •

• • •

•

•

•

• • •

• • •

1278, 2046 1279, 2046 1280, 2046 1281, 2046

1278, 2047 1279, 2047 1280, 2047 1281, 2047

(2) Mode1: MOD0= Open, MOD1= Low

D (0, 0) D (640, 0) D (1280, 0) D (1920, 0)

LA CA RA LB CB RB

1278, 0 1279, 0 1280, 0 1281, 0

1278, 1 1279, 1 1280, 1 1281, 1

•

•

•

•

•

•

LC CC RC LD CD RD

•

•

•

LC CC RC LD CD RD

•

•

•

• • •

• • •

•

•

•

• • •

• • •

2558, 0 2559, 0

2558, 1 2559, 1

•

•

•

2558, 2046 2559, 2046

2558, 2047 2559, 2047

•

•

•

0, 0

0, 1

•

•

•

0, 2046

0, 2047

639, 0 640, 0

•••

639, 1 640, 1

•••

•

•

•

•••

•••

•

•

•

639, 2046 640, 2046

639, 2047 640, 2047

1279, 0 1280, 0

•••

1279, 1 1280, 1

•••

•

•

•

•

•

•

•••

•••

•

•

•

1279, 2046 1280, 2046

1279, 2047 1280, 2047

•

•

•

•••

•••

•••

•••

1919, 0 1920, 0

1919, 1 1920, 1

•

•

•

•

•

•

1919, 2046 1920, 2046

1919, 2047 1920, 2047

2559, 0

•••

2559, 1

•••

•

•

•

•

•

•

•••

•••

•

•

•

2559, 2046

2559, 2047

DATA SHEET DOD-PP-0209 (8th edition)

22

Page 23

4.12 PIXEL ARRANGNMENT

0 1 2,559

NL256204AM15-01/01A

0 L C R L C R

• • • • • • •

LCR

2,047 L C R L C R • • • • • • • L C R

•

•

•

•

•

•

• • • • • • •

•

•

•

DATA SHEET DOD-PP-0209 (8th edition)

23

Page 24

4.13 TEN-bit LOOK UP TABLE FOR GAMMA ADJUSTMENT

Adjustment of gamma characteristics for each 8-bit LCR data is possible by using built-in 10-bit LUT

(look up table) for Gamma characteristics.

The LUT is set with the serial data. The combination of the control command determines

Random/Sequential Address WRITE and Individual/Simultaneous LCR setting.

The serial data is composed as Table1.

Table1: Serial data Composition

DATA DATA name Function Remarks

D31 CMD5 Control Command

D30 CMD4 Control Command

D29 CMD3 Control Command

D28 CMD2 Control Command

D27 CMD1 Control Command

D26 CMD0 Control Command

D25 ADD9 LUT Address (MSB)

D24 ADD8 LUT Address

D23 ADD7 LUT Address

D22 ADD6 LUT Address

D21 ADD5 LUT Address

D20 ADD4 LUT Address

D19 ADD3 LUT Address

D18 ADD2 LUT Address

D17 ADD1 LUT Address

D16 ADD0 LUT Address (LSB)

D15 DATA15 LUT Data (MSB)

D14 DATA14 LUT Data

D13 DATA13 LUT Data

D12 DATA12 LUT Data

D11 DATA11 LUT Data

D10 DATA10 LUT Data

D9 DATA9 LUT Data

D8 DATA8 LUT Data

D7 DATA7 LUT Data

D6 DATA6 LUT Data

D5 DATA5 LUT Data

D4 DATA4 LUT Data

D3 DATA3 LUT Data

D2 DATA2 LUT Data

D1 DATA1 LUT Data

D0 DATA0 LUT Data (LSB)

NL256204AM15-01/01A

See Table2 and 3.

See T able4.

See T able5.

DATA SHEET DOD-PP-0209 (8th edition)

24

Page 25

Table2: Command table (CMD5 to CMD0: 6-bit)

DATA name Parameter Remarks

CMD5 Must be set to "1". CMD4 Must be set to "1". -

Selection of Random/Sequential Address

CMD3

CMD2 Must be set to "1". -

CMD1

CMD0 Must be set to "0". -

WRITE

"1": Random Address WRITE

"0": Sequential Address WRITE

Selection of Individual/Simultaneous LCR

setting

"1": Individual LCR setting

"0": Simultaneous LCR setting

"1": Select the Sub-pixel by using ADD9 and

ADD8. (See Table4.)

"0": ADD9 and ADD8 are invalid.

Table3: Command table (CMD5 to CMD0: 6-bit)

CMD5 CMD4 CMD3 CMD2 CMD1 CMD0 Function

1 1 1 1 1 0 Random Address WRITE, Individual LCR setting

1 1 1 1 0 0 Random Address WRITE, Simultaneous LCR setting

1 1 0 1 1 0 Sequential Address WRITE, Individual LCR setting

1 1 0 1 0 0 Sequential Address WRITE, Simultaneous LCR setting

*Other combinations are prohibited, and may cause function error.

Table4: Address table (ADD9 to ADD0: 10-bit)

DATA name Paramet er Remarks

Sub-pixel Selection

ADD9

ADD8

ADD7

ADD6

ADD5

ADD4

ADD3

ADD2

ADD1

ADD0

ADD[9:8]=

0:0 Left Sub-pixel

0:1 Center Sub-pixel

1:0 Right Sub-pixel

1:1 ON/OFF selection of Gamma

Correction

LUT Address

256 address = 00h - FFh

When "ADD[9:8]=1:1", ON/OFF of Gamma

correction can select according to the GMA[2:0].

(See T able6 and Table7.)

When "ADD[9:8] = 1:1",

ADD[7:0] must be set to 00h.

NL256204AM15-01/01A

-

DATA SHEET DOD-PP-0209 (8th edition)

25

Page 26

Table5: Data table (DATA15 to DATA0: 16-bit)

DATA DATA name Parameter Remarks

DATA15 Dummy

DATA14 Dummy

DATA13 Dummy

DATA12 Dummy

DATA11 Dummy

DATA10 Dummy

DATA9 DATA9

DATA8 DATA8

DATA7 DATA7

DATA6 DATA6

DATA5 DATA5

DATA4 DATA4

DATA3 DATA3

DATA2 DATA2

DATA1 DATA1

DATA0 DATA0

Dummy Data

Must be set to "0".

[MSB]

10-bit LUT Data

000h - 3FFh

[LSB]

Table6: Gamma correction table (DATA15 to DATA0: 16-bit)

DATA DATA name Parameter Remarks

DATA15 Dummy

DATA14 Dummy

DATA13 Dummy

DATA12 Dummy

DATA11 Dummy

DATA10 Dummy

DATA9 Dummy

DATA8 Dummy

DATA7 Dummy

DATA6 Dummy

DATA5 Dummy

DATA4 Dummy

DATA3 Dummy

DATA2 GAM2

DATA1 GAM1

DATA0 GAM0

Dummy Data

Must be set to "0".

[MSB]

GMA Data

[LSB]

Table7: Control code GAM[2:0]

GMA2 GMA1 GMA0 Function

0 0 0 No correction (Initial setting)

0 0 1 Correction according to the LUT Data. Note1

*Other combinations are prohibited, and may cause function error.

Note1: Initial setting of the LUT is undefined data. The LUT should be enabled by setting of the GMA after

writing the LUT data in all the 256 addresses, in order to avoid undefined data display.

Note2: Transfer the data every power-on, because the LUT data isn't stored in the LCD module.

Note3: As writing and reading the LUT data, a noise may appear on the display image. In order to prevent

the noise appearing on the display, following measures should be performed.

(1) The LUT data should be rewritten during invalid period of pixel data (See "4.8 INPUT

SIGNAL TIMINGS".).

(2) The LUT data should be rewritten when the Gamma Correction is OFF (GMA[2:0] = 000).

NL256204AM15-01/01A

-

-

-

See T able7.

DATA SHEET DOD-PP-0209 (8th edition)

26

Page 27

4.14 LUT SERIAL COMMUNICATION TIMINGS

(1) Timing chart

SCLK

CSR, CSL

SDAT

D31 D30 D29 D28 D27 D26 D25 D24 D23 D18 D17 D16 D15 D14 D13 D2 D1 D0

Invalid

Random Address WRITE timing chart

CSR, CSL

SDAT

CMD ADD DATA CMD ADD DATA

Invalid

Sequential Address WRITE timing chart

CSR, CSL

CMD ADD DATA DATA

SDAT

Invalid

ADD[9:0]

NL256204AM15-01/01A

Invalid

D31

DATA[15:0] CMD[5:0]

InvalidInvalid

DATA

Invalid

DATA SHEET DOD-PP-0209 (8th edition)

27

Page 28

NL256204AM15-01/01A

(2) Timing specifications

Parameter Symbol min. typ. max. Unit Remarks

SCLK Frequency 1/Tsck - - 5 MHz SCLK Pulse Twsck 50 - - ns SDAT-SCLK Setup Time Tds 50 - - ns SDAT-SCLK Hold Time Tdh 50 - - ns CSR/CSL-SCLK Setup Time Tcs 50 - - ns CSR/CSL-SCLK Hold Time Tch 50 - - ns -

Twsck Twsck

SCLK

Tds Tdh

SDAT

Tcs

Tch

CSR,

CSL

Note1: During the serial communication mode, the display noise may appear because of rewriting the

data. To avoid this, rewrite the LUT data when the pixel data is invalid or the Gamma

Correction is OFF (GMA[2:0] = 000). The external noise may cause the data change, refresh

the data regularly according to need.

Tsck

V+

50%

V-

V+

V-

V+

V-

DATA SHEET DOD-PP-0209 (8th edition)

28

Page 29

4.15 OPTICS

4.15.1 Optical characteristics

(1) NL256204AM15-01

Parameter Condition Symbol min. typ. max. Unit

Luminance

Contrast ratio

Luminance uniformity

Chromaticity White

Response time

Right

Viewing angle

Left

Up

Down

(2) NL256204AM15-01A

Parameter Condition Symbol min. typ. max. Unit

Luminance

Contrast ratio

Luminance uniformity

Chromaticity White

Response time

Right

Viewing angle

Left

Up

Down

White at center

= 0°, θL = 0°, θU = 0°, θD = 0°

θR

White/Black at center

= 0°, θL = 0°, θU = 0°, θD = 0°

θR

White

= 0°, θL = 0°, θU = 0°, θD = 0°

θR

x coordinate Wx 0.225 0.255 0.285 -

y coordinate Wy 0.280 0.310 0.340 -

Black to White Ton - 15 25 ms

White to Black Toff - 15 25 ms

θU = 0°, θD = 0°, CR ≥ 10 θR

θU = 0°, θD = 0°, CR ≥ 10 θL

θR = 0°, θL = 0°, CR ≥ 10 θU

θR = 0°, θL = 0°, CR ≥ 10 θD

White at center

= 0°, θL = 0°, θU = 0°, θD = 0°

θR

White/Black at center

= 0°, θL = 0°, θU = 0°, θD = 0°

θR

White

= 0°, θL = 0°, θU = 0°, θD = 0°

θR

x coordinate Wx 0.250 0.280 0.310 -

y coordinate Wy 0.274 0.304 0.334 -

Black to White Ton - 15 25 ms

White to Black Toff - 15 25 ms

θU = 0°, θD = 0°, CR ≥ 10 θR

θU = 0°, θD = 0°, CR ≥ 10 θL

θR = 0°, θL = 0°, CR ≥ 10 θU

θR = 0°, θL = 0°, CR ≥ 10 θD

NL256204AM15-01/01A

(Note1, Note2)

Measuring

instrument

BM-5A

2

L 650 850 - cd/m

CR 400 600 - -

LU - 1.1 1.3 - BM-5A Note4

70 85 70 85 70 85 70 85 -

L 650 850 - cd/m

CR 400 600 - -

LU - 1.1 1.3 - BM-5A Note4

70 85 70 85 70 85 70 85 -

or SR-3

BM-5A

or SR-3

SR-3 Note5

BM-5A

°

°

BM-5A Note8

°

°

Measuring

instrument

BM-5A

2

or SR-3

BM-5A

or SR-3

SR-3 Note5

BM-5A

°

°

BM-5A Note8

°

°

Remarks

-

Note3

Note6

Note7

(Note1, Note2)

Remarks

-

Note3

Note6

Note7

DATA SHEET DOD-PP-0209 (8th edition)

29

Page 30

Note1: These are initial characteristics.

Note2: Measurement conditions are as follows.

°C, VDD=12V, VDDB=12V, Luminance control = maximum, Display mode: QSXGA,

Ta=25

Horizontal cycle=1/123.9 kHz, Vertical cycle = 1/60.0 Hz

Optical characteristics are measured after 20minutes from working the product, in the dark

room. Also measurement methods are as follows.

50cm

Photodetector (BM-5A or SR-3)

LCD module

(Product)

1°

Note3: See "4.15.2 Definition of contrast ratio".

Note4: See "4.15.3 Definition of luminance uniformity".

Note5: These coordinates are found on CIE 1931 chromaticity diagram.

Note6: Product surface temperature: TopF=36°C

Note7: See "4.15.4 Definition of response times".

Note8: See "4.15.5 Definition of viewing angles".

NL256204AM15-01/01A

DATA SHEET DOD-PP-0209 (8th edition)

30

Page 31

N

①

②

4.15.2 Definition of contrast ratio

The contrast ratio is calculated by using the following formula.

Contrast ratio (CR) =

4.15.3 Definition of luminance uniformity

The luminance uniformity is calculated by using following formula.

Luminance uniformity (LU) =

The luminance is measured at near the 5 points shown below .

4.15.4 Definition of response times

Response time is measured, the luminance changes from "black" to "white", or "white" to "black" on

the same screen point, by photo-detector. Ton is the time it takes the luminance change from 10% up

to 90%. Also Toff is the time it takes the luminance change from 90% down to 10% (See the

following diagram.).

White

Luminance

Black

4.15.5 Definition of viewing angles

Left

θD

Lower

Luminance of white screen

Luminance of black screen

427

341

1,023

1,706

100%

④

90%

10%

0%

ormal axis (Perpendicular)

θL

θU

Upper

θR

NL256204AM15-01/01A

Maximum luminance from ① to ⑤

Minimum luminance from ① to ⑤

1,279

③

Ton

12 o’clock

Right

2,132

⑤

Toff

DATA SHEET DOD-PP-0209 (8th edition)

31

Page 32

5. RELIABILITY TESTS

Test item Condition Judgment Note1

NL256204AM15-01/01A

High temperature and humidity

(Operation)

Heat cycle

(Operation)

Thermal shock

(Non operation)

Vibration

(Non operation)

Mechanical shock

(Non operation)

ESD

(Operation)

Dust

(Operation)

Non-operation

Low pressure

Operation

① 60 ± 2°C, RH = 60%, 240hours

② Display data is white.

① 0 ± 3°C…1hour

55 ± 3°C…1hour

② 50cycles, 4hours/cycle

③ Display data is white.

① -20 ± 3°C…30minutes

60 ± 3°C…30minutes

② 100cycles, 1hour/cycle

③ Temperature transition time is within 5

minutes.

① 5 to 100Hz, 11.76m/s

② 1 minute/cycle

③ X, Y, Z direction

④ 10 times each directions

① 294m/ s

② X, Y, Z direction

③ 3 times each directions

① 150pF, 150Ω, ±10kV

② 9 places on a panel surface Note2

③ 10 times each places at 1 sec interval

① Sample dust: No.15 (by JIS-Z8901)

② 15 seconds stir

③ 8 times repeat at 1 hour interval

① 15 kPa (Equivalent to altitude 13,600m)

② -20°C±3°C…24 hours

③ +60°C±3°C…24 hours

① 53.3 kPa (Equivalent to altitude 4,850m)

② 0°C±3°C…24 hours

③ +55°C±3°C…24 hours

2

, 11ms

2

No display malfunctions

No display malfunctions

No physical damages

No display malfunctions

No display malfunctions

Note1: Display and appearance are checked under environmental conditions equivalent to the

inspection conditions of defect criteria.

Note2: See the following figure for discharge points

{

{

{

{

{

{

{

{

{

DATA SHEET DOD-PP-0209 (8th edition)

32

Page 33

!

6. PRECAUTIONS

6.1 MEANING OF CAUTION SIGNS

The following caution signs have very important meaning. Be sure to read "6.2 CAUTIONS" and

"6.3 ATTENTIONS", after understanding these contents!

This sign has the meaning that customer will be injured by himself or the product will

sustain a damage, if customer has wrong operations.

This sign has the meaning that customer will get an electrical shock, if customer has

wrong operations.

This sign has the meaning that customer will be injured by himself, if customer has

wrong operations.

6.2 CAUTIONS

∗ Do not touch the working backlight. There is a danger of an electric shock.

NL256204AM15-01/01A

∗ Do not touch the working backlight. There is a danger of burn injury.

∗ Do not shock and press the LCD panel and the backlight! There is a danger of breaking,

because they are made of glass. (Shock: To be not greater 294m/s

11ms, Pressure: To be not greater 19.6N (φ16mm jig))

6.3 ATTENTIONS

6.3.1 Handling of the product

① Take hold of both ends without touching the circuit board when the product (LCD module) is picked

up from inner packing box to avoid broken down or misadjustment, because of stress to mounting

parts on the circuit board.

② Do not hook nor pull cables such as lamp cable, and so on, in order to avoid any damage.

③ When the product is put on the table temporarily, display surface must be placed downward.

④ When handling the product, take the measures of electrostatic discharge with such as earth band,

ionic shower and so on, because the product may be damaged by electrostatic.

⑤ The torque for product mounting screws must never exceed 0.45 N⋅m. Higher torque might result in

distortion of the bezel.

2

and to be not greater

!

DATA SHEET DOD-PP-0209 (8th edition)

33

Page 34

NL256204AM15-01/01A

⑥ When the product is installed, use the mounting holes. The product is very sensitive to a stress (such

as bend or twist). A stress added by installation to any portion cause display mura. Do not add a stress

to any portion (such as bezel flat area).

Recommended installing method: An ideal plane that is defined by datum point and mounting holes is

to be the same plane within ±0.3 mm.

Product

Datum point

⑦ Do not press or rub on the sensitive product surface. When cleaning the product surface, use of the

cloth with ethanolic liquid such as screen cleaner for LCD is recommended.

⑧ Do not push nor pull the interface connectors while the product is working.

⑨ When handling the product, use of an original protection sheet on the product surface (polarizer) is

recommended for protection of product surface. Adhesive type protection sheet may change color or

characteristics of the polarizer.

⑩ Usually liquid crystals don't leak through the breakage of glasses because of the surface tension of

thin layer and the construction of LCD panel. But, if you contact with liquid crystal for the worst,

please wash it out with soap.

6.3.2 Environment

① Do not operate or store in high temperature, high humidity, dewdrop atmosphere or corrosive gases.

Keep the product in packing box with antistatic pouch in room temperature to avoid dusts and

sunlight, when storing the product.

② In order to prevent dew condensation occurring by temperature difference, the product packing box

should be opened after enough time being left under the environment of an unpack ing room. Evaluate

the leaving time sufficiently because a situation of dew condensation occurring is changed by the

environmental temperature and humidity. (Recommended leaving time: 6 hours or more with packing

state)

③ Do not operate in high magnetic field. Circuit boards may be broken down by it.

④ This product is not designed as radiation hardened.

Mounting hole

An ideal plane defined by datum

point and mounting holes

Mounting hole

DATA SHEET DOD-PP-0209 (8th edition)

34

Page 35

6.3.3 Characteristics

The following items are neither defects nor failures.

① Response time, luminance and color may be changed by ambient temperature.

② Display mura, flicker, vertical seam or small spot may be observed depending on display patterns.

③ Optical characteristics (e.g. luminance, display uniformity, etc.) gradually is going to change

④ Do not display the fixed pattern for a long time because it may cause image sticking. Use a screen

⑤ The display color may be changed depending on viewing angle because of the use of condenser sheet

⑥ Optical characteristics may be changed depending on input signal timings.

⑦ The interference noise between input signal frequency for this product's signal processing board and

⑧ After the product is stored under condition of low temperature or dark place for a long time, the cold

6.3.4 Other

① All GND and VCC terminals should be used without any non-connected lines.

② Do not disassemble a product or adjust variable resistors.

③ See "REPLACEMENT MANUAL FOR BACKLIGHT UNIT", when replacing backlight lamps.

④ Pack the product with original shipping package, in order to avoid any damages during transportation,

⑤ The LCD module by itself or integrated into end product should be packed and transported with

NL256204AM15-01/01A

depending on operating time, and especially low temperature, because the LCD has cold cathode

fluorescent lamps.

saver, if the fixed pattern is displayed on the screen.

in the backlight.

luminance control frequency of the inverter may appear on a display. Set up luminance control

frequency of the inverter so that the interference noise does not appear.

cathode fluorescent lamp may not be turned on under the same condition because of the general

characteristic of cold cathode fluorescent lamp. In addition, when Luminance control ratio is low in

pulse width modulation method inverter, the lamp may not be turned on. In this case, power should

be supplied again.

when returning the product to NEC for repair and so on.

display in the vertical position. Otherwise the display characteristics may be degraded.

DATA SHEET DOD-PP-0209 (8th edition)

35

Page 36

7. OUTLINE DRAWINGS

NL256204AM15-01/01A

258

(129)

32 .3

343.5 ±1.0

(BEZEL OPEN ING AREA )

404 .2

DISPLAY AREA CENTER

PRODUCT CEN TER

423 .4 ±1 .0

DISPLAY AREA CENTER

(BEZEL OPEN ING AREA )

324 .4

(399 .36*319 .488 D ISPLAY AREA)

43 .5 ±1 .0

32 .3

43 .5 ±1 .0

(129)

258

(35 .4)

(57 .5)

CN202 CN201

CN2

(25 .8)

(28 .1)

32 .9

CN3

CN8CN1

2441 .637 .9

(60)

Ma te r ia l In fo rma t ion

(100 .95)

Diffuser:> PC <

Note1: The dimensions in parenthesis are for reference.

Note2: Not shown tolerances of the dimensions

0 mm < d ≤ 18mm: ±0.2mm.

18 mm < d ≤ 50mm: ±0.3mm.

50 mm < d ≤ 120mm: ±0.4mm.

120 mm < d ≤ 250mm: ±0.5mm.

250 mm < d : ±0.6mm.

(d: dimension)

Unit: mm

DATA SHEET DOD-PP-0209 (8th edition)

36

Loading...

Loading...