NEC MC-4R64CPE6C-845, MC-4R64CPE6C-653, MC-4R64CPE6C-745 Datasheet

PRELIMINARY DATA SHEET

MOS INTEGRATED CIRCUIT

MC-4R64CPE6C

Direct RambusTM DRAM RIMMTM Module

64M-BYTE (32M-WORD x 16-BIT)

Description

The Direct Rambus RIMM module is a general-purpose high-performance memory module subsystem suitable for

use in a broad range of applications including computer memory, personal computers, workstations, and other

applications where high bandwidth and low latency are required.

MC-4R64CPE6C modules consists of four 128M Direct Rambus DRAM (Direct RDRAM™) devices (

These are extremely high-speed CMOS DRAMs organized as 8M words by 16 bits. The use of Rambus Signaling

Level (RSL) technology permits 600MHz, 711MHz or 800MHz transfer rates while using conventional system and

board design technologies.

Direct RDRAM devices are capable of sustained data transfers at 1.25 ns per two bytes (10 ns per sixteen bytes).

The architecture of the Direct RDRAM enables the highest sustained bandwidth for multiple, simultaneous,

randomly addressed memory transactions. The separate control and data buses with independent row and column

control yield over 95 % bus efficiency. The Direct RDRAM's 32 banks support up to four simultaneous transactions

per device.

µ

PD488448).

Features

• 184 edge connector pads with 1mm pad spacing

• 64 MB Direct RDRAM storage

• Each RDRAM

• Gold plated contacts

• RDRAMs use Chip Scale Package (CSP)

• Serial Presence Detect support

• Operates from a 2.5 V supply

• Low power and powerdown self refresh modes

• Separate Row and Column buses for higher efficiency

• Over Drive Factor (ODF) support

has 32 banks, for 128 banks total on module

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for

availability and additional information.

Document No. M14805EJ2V0DS00 (2nd edition)

Date Published August 2000 NS CP (K)

Printed in Japan

The mark

shows major revised points.

★★★★

©

2000

Order information

MC-4R64CPE6C

Part number Organization I/O Freq.

MHz

MC-4R64CPE6C - 845 32M x 16 800 45 184 edge connector pads RIMM 4 pieces of

MC-4R64CPE6C - 745 711 45 with heat spreader

MC-4R64CPE6C - 653 600 53 Edge connector : Gold plated FBGA (µBGA) package

RAS access time

ns

Package Mounted devices

PD488448FF

µ

2

Preliminary Data Sheet M14805EJ2V0DS00

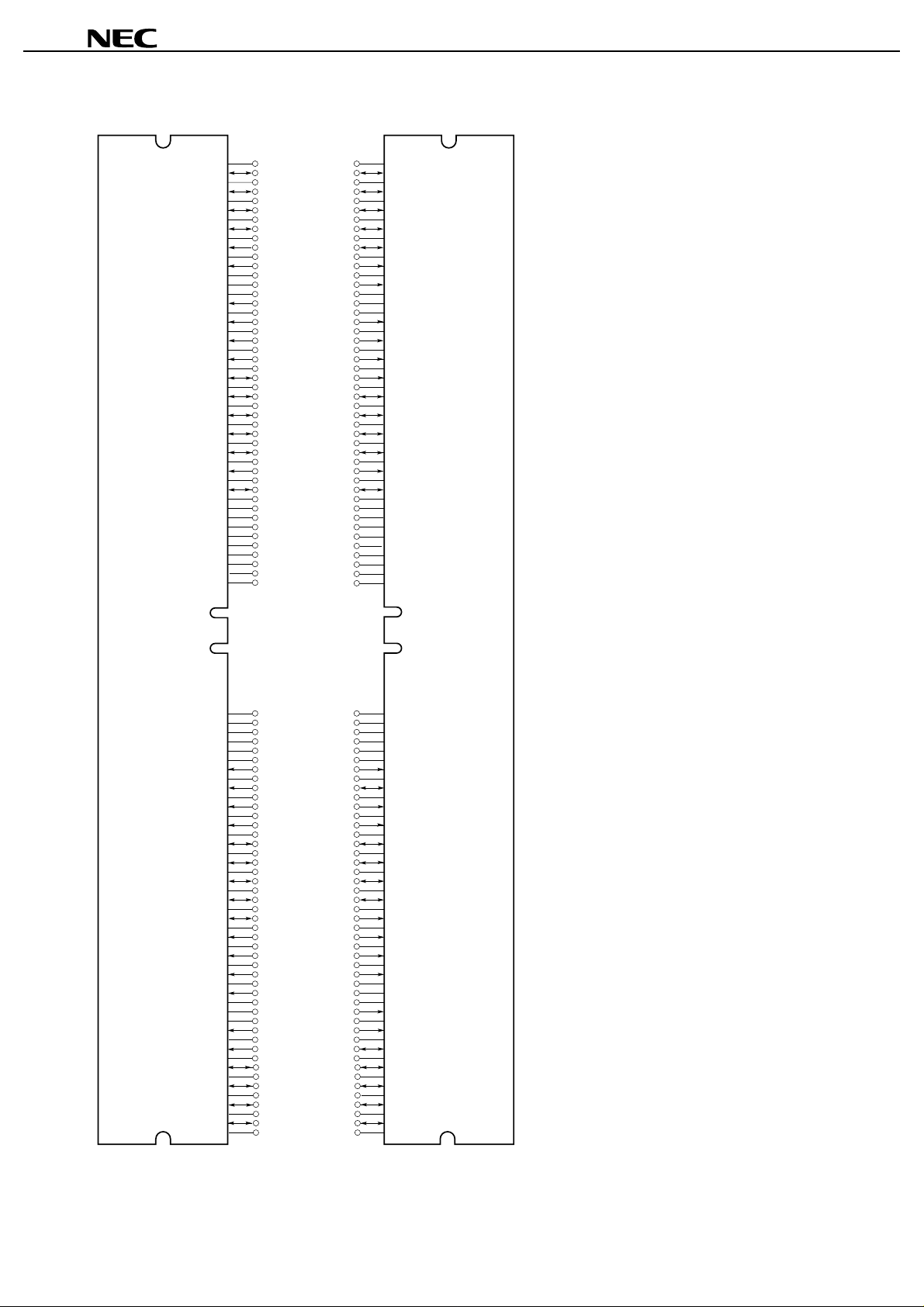

Module Pad Configuration

MC-4R64CPE6C

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B40

B41

B42

B43

B44

B45

B46

B1

B2

B3

B4

B5

B6

B7

B8

B9

GND

LDQA7

GND

LDQA5

GND

LDQA3

GND

LDQA1

GND

LCFM

GND

LCFMN

GND

NC

GND

LROW2

GND

LROW0

GND

LCOL3

GND

LCOL1

GND

LDQB0

GND

LDQB2

GND

LDQB4

GND

LDQB6

GND

LDQB8

GND

LCMD

CMOS

V

SIN

CMOS

V

NC

GND

NC

V

DD

V

DD

NC

NC

NC

NC

GND

LDQA8

GND

LDQA6

GND

LDQA4

GND

LDQA2

GND

LDQA0

GND

LCTMN

GND

LCTM

GND

NC

GND

LROW1

GND

LCOL4

GND

LCOL2

GND

LCOL0

GND

LDQB1

GND

LDQB3

GND

LDQB5

GND

LDQB7

GND

LSCK

V

CMOS

SOUT

V

CMOS

NC

GND

NC

V

V

NC

NC

NC

NC

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

A36

A37

A38

A39

DD

DD

A40

A41

A42

A43

A44

A45

A46

Side B Side A

B47

B48

B49

B50

B51

B52

B53

B54

B55

B56

B57

B58

B59

B60

B61

B62

B63

B64

B65

B66

B67

B68

B69

B70

B71

B72

B73

B74

B75

B76

B77

B78

B79

B80

B81

B82

B83

B84

B85

B86

B87

B88

B89

B90

B91

B92

NC

NC

NC

NC

V

REF

GND

SA0

DD

V

SA1

DD

SV

SA2

DD

V

RCMD

GND

RDQB8

GND

RDQB6

GND

RDQB4

GND

RDQB2

GND

RDQB0

GND

RCOL1

GND

RCOL3

GND

RROW0

GND

RROW2

GND

NC

GND

RCFMN

GND

RCFM

GND

RDQA1

GND

RDQA3

GND

RDQA5

GND

RDQA7

GND

NC

NC

NC

NC

V

REF

GND

SCL

V

SDA

SV

SWP

V

RSCK

GND

RDQB7

GND

RDQB5

GND

RDQB3

GND

RDQB1

GND

RCOL0

GND

RCOL2

GND

RCOL4

GND

RROW1

GND

NC

GND

RCTM

GND

RCTMN

GND

RDQA0

GND

RDQA2

GND

RDQA4

GND

RDQA6

GND

RDQA8

GND

A47

A48

A49

A50

A51

A52

DD

DD

DD

A53

A54

A55

A56

A57

A58

A59

A60

A61

A62

A63

A64

A65

A66

A67

A68

A69

A70

A71

A72

A73

A74

A75

A76

A77

A78

A79

A80

A81

A82

A83

A84

A85

A86

A87

A88

A89

A90

A91

A92

LCFM, LCFMN,

RCFM, RCFMN : Clock from master

LCTM, LCTMN,

RCTM, RCTMN : Clock to master

LCMD, RCMD : Serial Command Pad

LROW2 - LROW0,

RROW2 - RROW0 : Row bus

LCOL4 - LCOL0,

RCOL4 - RCOL0 : Column bus

LDQA8 - LDQA0,

RDQA8 - RDQA0 : Data bus A

LDQB8 - LDQB0,

RDQB8 - RDQB0 : Data bus B

LSCK, RSCK : Clock input

SA0 - SA2 : Serial Presence Detect Address

SCL, SDA : Serial Presence Detect Clock

SIN, SOUT : Serial I/O

DD

SV

: SPD Voltage

SWP : Serial Presence Detect Write Protect

CMOS

V

DD

V

REF

V

: Supply voltage for serial pads

: Supply voltage

: Logic threshold

GND : Ground reference

NC : These pads are not connected

Preliminary Data Sheet M14805EJ2V0DS00

3

MC-4R64CPE6C

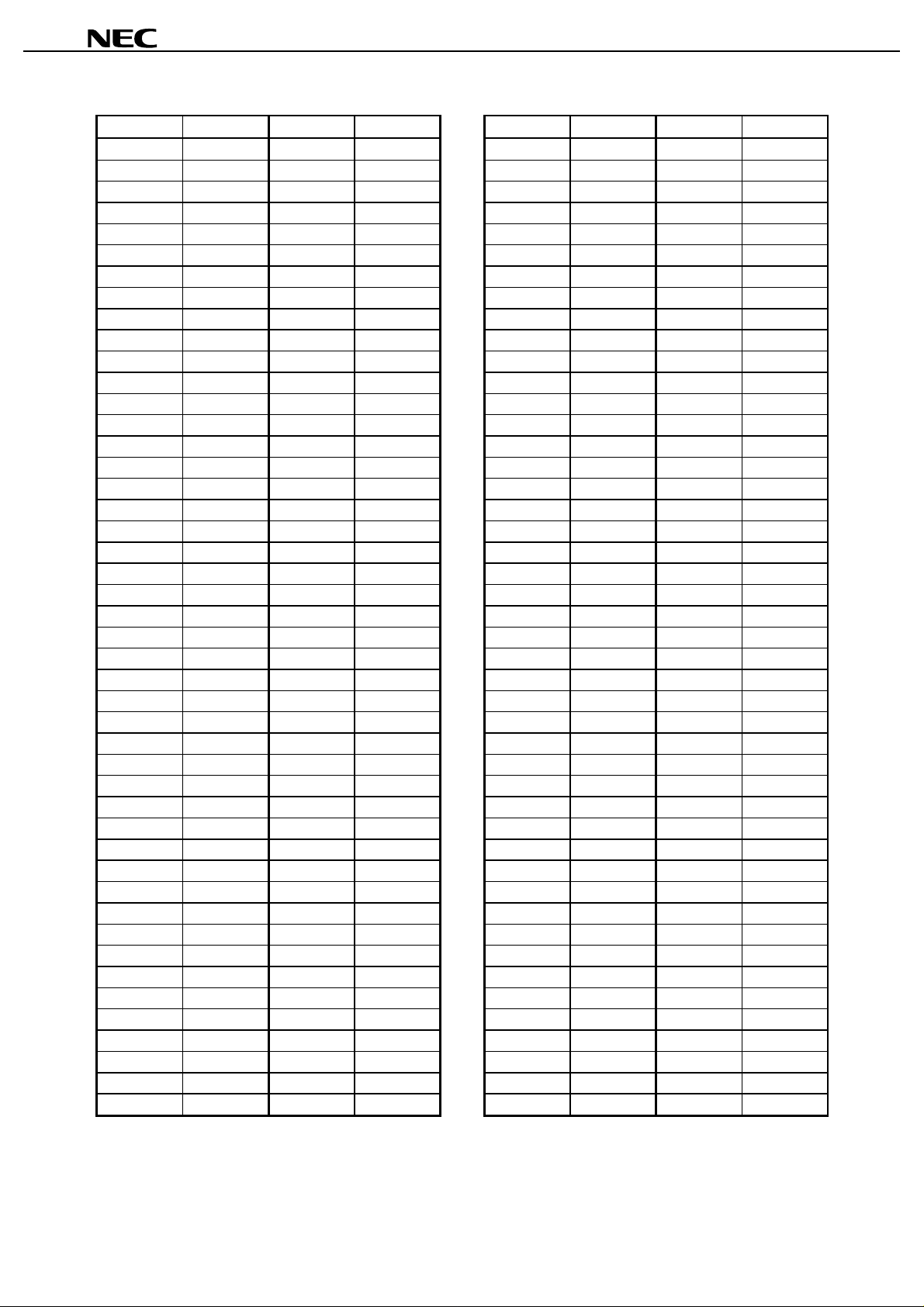

Module Pad Names

Pad Signal Name Pad Signal Name Pad Signal Name Pad Signal Name

A1 GND B1 GND A47 NC B47 NC

A2 LDQA8 B2 LDQA7 A48 NC B48 NC

A3 GND B3 GND A49 NC B49 NC

A4 LDQA6 B4 LDQA5 A50 NC B50 NC

A5 GND B5 GND A51 V

A6 LDQA4 B6 LDQA3 A52 GND B52 GND

A7 GND B7 GND A53 SCL B53 SA0

A8 LDQA2 B8 LDQA1 A54 V

A9 GND B9 GND A55 SDA B55 SA1

A10 LDQA0 B10 LCFM A56 SV

A11 GND B11 GND A57 SWP B57 SA2

A12 LCTMN B12 LCFMN A58 V

A13 GND B13 GND A59 RSCK B59 RCMD

A14 LCTM B14 NC A60 GND B60 GND

A15 GND B15 GND A61 RDQB7 B61 RDQB8

A16 NC B16 LROW2 A62 GND B62 GND

A17 GND B17 GND A63 RDQB5 B63 RDQB6

A18 LROW1 B18 LROW0 A64 GND B64 GND

A19 GND B19 GND A65 RDQB3 B65 RDQB4

A20 LCOL4 B20 LCOL3 A66 GND B66 GND

A21 GND B21 GND A67 RDQB1 B67 RDQB2

A22 LCOL2 B22 LCOL1 A68 GND B68 GND

A23 GND B23 GND A69 RCOL0 B69 RDQB0

A24 LCOL0 B24 LDQB0 A70 GND B70 GND

A25 GND B25 GND A71 RCOL2 B71 RCOL1

A26 LDQB1 B26 LDQB2 A72 GND B72 GND

A27 GND B27 GND A73 RCOL4 B73 RCOL3

A28 LDQB3 B28 LDQB4 A74 GND B74 GND

A29 GND B29 GND A75 RROW1 B75 RROW0

A30 LDQB5 B30 LDQB6 A76 GND B76 GND

A31 GND B31 GND A77 NC B77 RROW2

A32 LDQB7 B32 LDQB8 A78 GND B78 GND

A33 GND B33 GND A79 RCTM B79 NC

A34 LSCK B34 LCMD A80 GND B80 GND

A35 V

CMOS

B35 V

CMOS

A81 RCTMN B81 RCFMN

A36 SOUT B36 SIN A82 GND B82 GND

A37 V

CMOS

B37 V

CMOS

A83 RDQA0 B83 RCFM

A38 NC B38 NC A84 GND B84 GND

A39 GND B39 GND A85 RDQA2 B85 RDQA1

A40 NC B40 NC A86 GND B86 GND

A41 V

A42 V

DD

DD

B41 V

B42 V

DD

DD

A87 RDQA4 B87 RDQA3

A88 GND B88 GND

A43 NC B43 NC A89 RDQA6 B89 RDQA5

A44 NC B44 NC A90 GND B90 GND

A45 NC B45 NC A91 RDQA8 B91 RDQA7

A46 NC B46 NC A92 GND B92 GND

REF

DD

DD

B51 V

B54 V

DD

B56 SV

B58 V

REF

DD

DD

DD

4

Preliminary Data Sheet M14805EJ2V0DS00

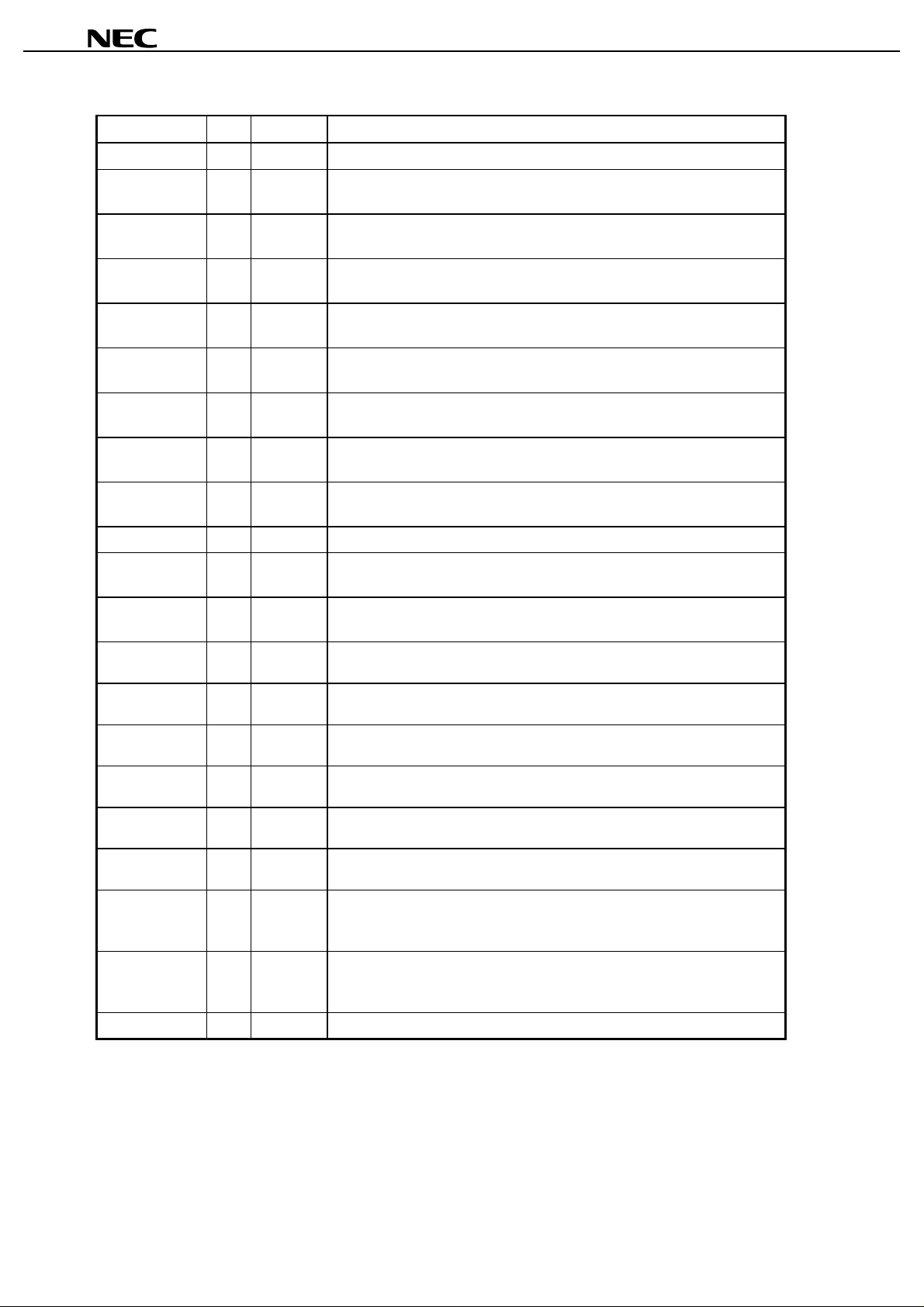

MC-4R64CPE6C

Module Connector Pad Description (1/2)

Signal I/O Type Description

GND – – Ground reference for RDRAM core and interface. 72 PCB connector pads.

LCFM I RSL Clock from mas ter. Interface clock used for receiving RSL signals f rom the

Channel. Positive polarity.

LCFMN I RSL Clock from m as ter. Interface clock used for receiving RSL signals from the

Channel. Negative polarity.

LCMD I V

LCOL4..LCOL0 I RSL Column bus. 5-bit bus containing control and address information for column

LCTM I RSL Clock to master. Interface clock used for transmitting RS L s i gnal s to the

LCTMN I RSL Clock to mast er. Interface clock used for transmitting RS L signals to the

LDQA8..LDQA0 I/O RSL Data bus A. A 9-bit bus carrying a byte of read or write data between the Channel

LDQB8..LDQB0 I/O RSL Data bus B. A 9-bit bus carrying a byte of read or write data between the Channel

LROW2..LROW0 I RSL Row bus. 3-bit bus containing control and address information for row accesses.

LSCK I V

NC – – These pads are not connected. These 24 connector pads are res erved f or future

RCFM I RSL Clock from master. Interfac e clock used for receiving RSL signals from the

RCFMN I RSL Clock from mas ter. Interface clock used for receiving RSL signals f rom the

RCMD I V

RCOL4..RCOL0 I RSL Column bus. 5-bit bus containi ng control and address information for column

RCTM I RSL Clock to master. Interface clock used for transmi t ting RSL signals to the

RCTMN I RSL Clock to master. Interface clock used for transmitting RS L s i gnal s to the

RDQA8..RDQA0 I/O RSL Data bus A. A 9-bit bus carrying a byte of read or write data between the Channel

RDQB8..RDQB0 I/O RSL Data bus B. A 9-bit bus carrying a byte of read or write data between the Channel

RROW2..RROW0 I RSL Row bus. 3-bit bus containing control and address informat i on for row accesses.

CMOS

CMOS

CMOS

Serial Command used t o read from and write to the control regis t ers. Also used

for power management.

accesses.

Channel. Positive polarity.

Channel. Negative polarity.

and the RDRAM. LDQA8 is non-functi onal on modules with x16 RDRAM devices.

and the RDRAM. LDQB8 is non-functi onal on modules with x16 RDRAM devices.

Serial clock input. Cl ock source used to read from and write t o the RDRAM

control registers.

use.

Channel. Positive polarity.

Channel. Negative polarity.

Serial Command Input used to read from and write to the control regi sters. Also

used for power management.

accesses.

Channel. Positive polarity.

Channel. Negative polarity.

and the RDRAM. RDQA8 is non-functi onal on modules with x16 RDRAM

devices.

and the RDRAM. RDQB8 is non-functi onal on modules with x16 RDRAM

devices.

Preliminary Data Sheet M14805EJ2V0DS00

5

Loading...

Loading...