National Semiconductor LMX2310U, LMX2311U, LMX2312U, LMX2313U Technical data

查询LMX2310供应商

LMX2310U/LMX2311U/LMX2312U/LMX2313U

December 2003

LMX2310U/LMX2311U/LMX2312U/LMX2313U PLLatinum Ultra Low Power Frequency Synthesizer

for RF Personal Communications

PLLatinum

™

Ultra Low Power Frequency Synthesizer for

RF Personal Communications

LMX2310U 2.5 GHz LMX2311U 2.0 GHz

LMX2312U 1.2 GHz LMX2313U 600 MHz

General Description

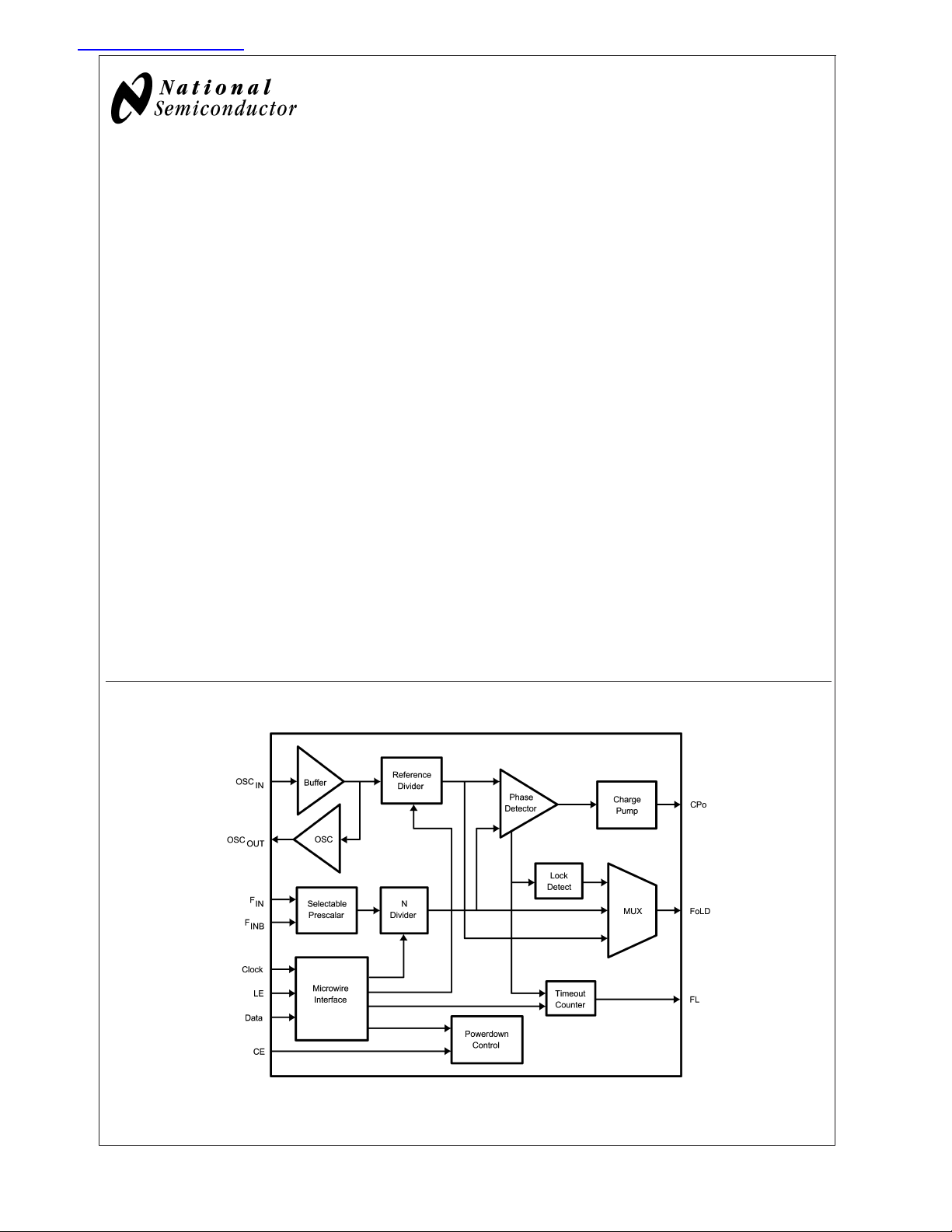

The LMX2310/1/2/3U are high performance frequency synthesizers. The LMX2310/1/2U use a selectable, dual modulus 32/33 and 16/17 prescaler. The LMX2313U uses a selectable, dual modulus 16/17 and 8/9 prescaler. The device,

when combined with a high quality reference oscillator and a

voltage controlled oscillator, generates very stable, low noise

local oscillator signals for up and down conversion in wireless communication devices.

Serial data is transferred into LMX2310/1/2/3U via a threewire interface (Data, Enable, Clock) that can be directly

interfaced with low voltage baseband processors. Supply

voltage can range from 2.7V to 5.5V. LMX2310U features

very low current consumption, typically 2.3 mA at 3.0V.

The LMX2310/1/2/3U are manufactured using National’s

0.5µ ABiC V silicon BiCMOS process and is available in

20-pin CSP packages.

Features

n RF operation up to 2.5 GHz

n 2.7V to 5.5V operation

n Ultra Low Current Consumption

n Low prescaler values

LMX2310/1/2U 32/33 or 16/17

LMX2313U 16/17 or 8/9

n Excellent Phase Noise

n Internal balanced, low leakage charge pump

n Selectable Charge Pump Current Levels

n Selectable Fastlock mode with Time-Out Counter

n Low Voltage MICROWIRE interface (1.72V to V

n Digital and Analog Lock Detect

n Small 20-pad Thin Chip Scale Package

Applications

n Cellular DCS, PCS, WCDMA telephone systems

n Wireless Local Area Networks (WLAN)

n Global Positioning Systems (GPS)

n Other wireless communications systems

)

CC

Functional Block Diagram

20043822

PLLatinum™is a trademark of National Semiconductor Corporation.

© 2003 National Semiconductor Corporation DS200438 www.national.com

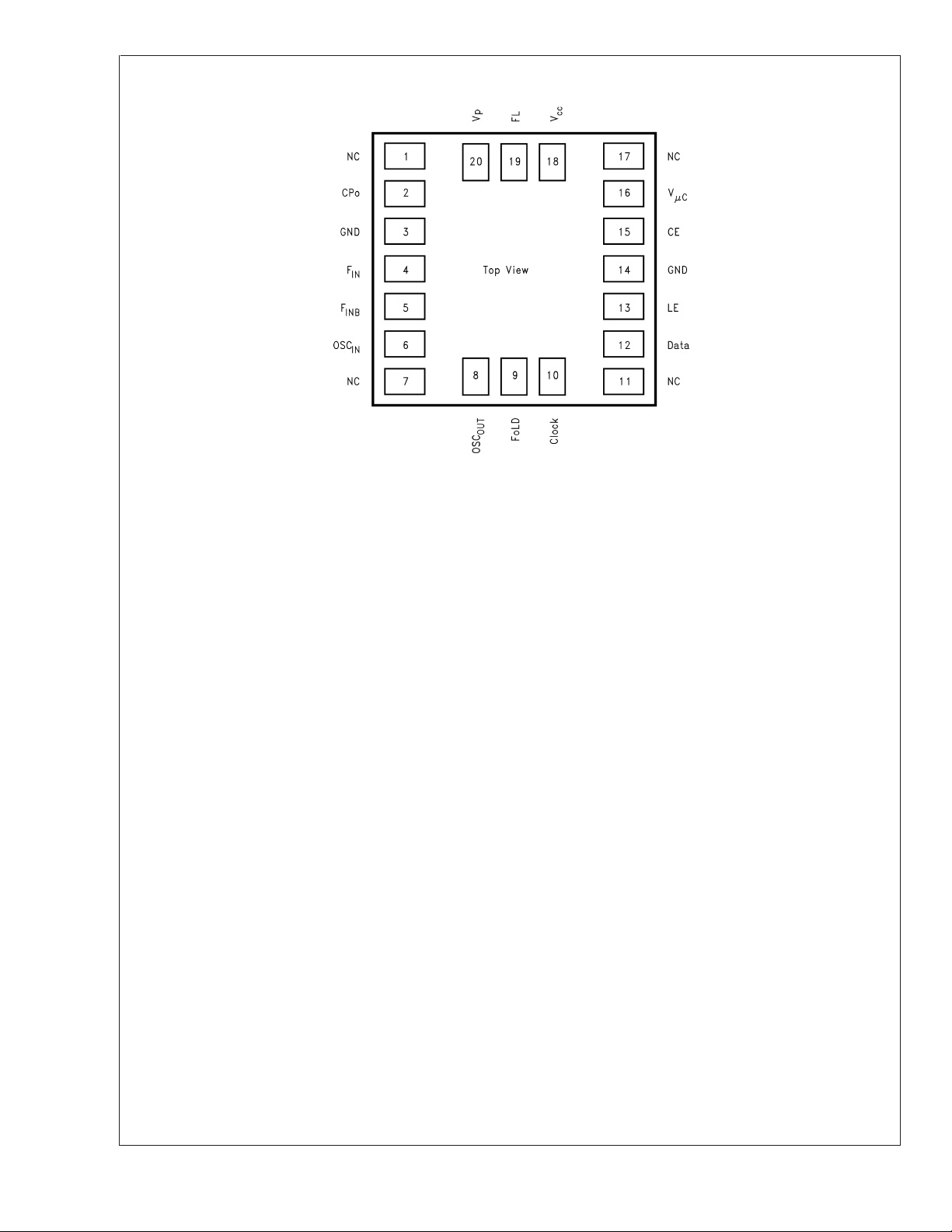

Connection Diagram

LMX2310U/LMX2311U/LMX2312U/LMX2313U

20-Pin Thin Chip Scale Package

NS Package Number SLD20A

20043823

www.national.com 2

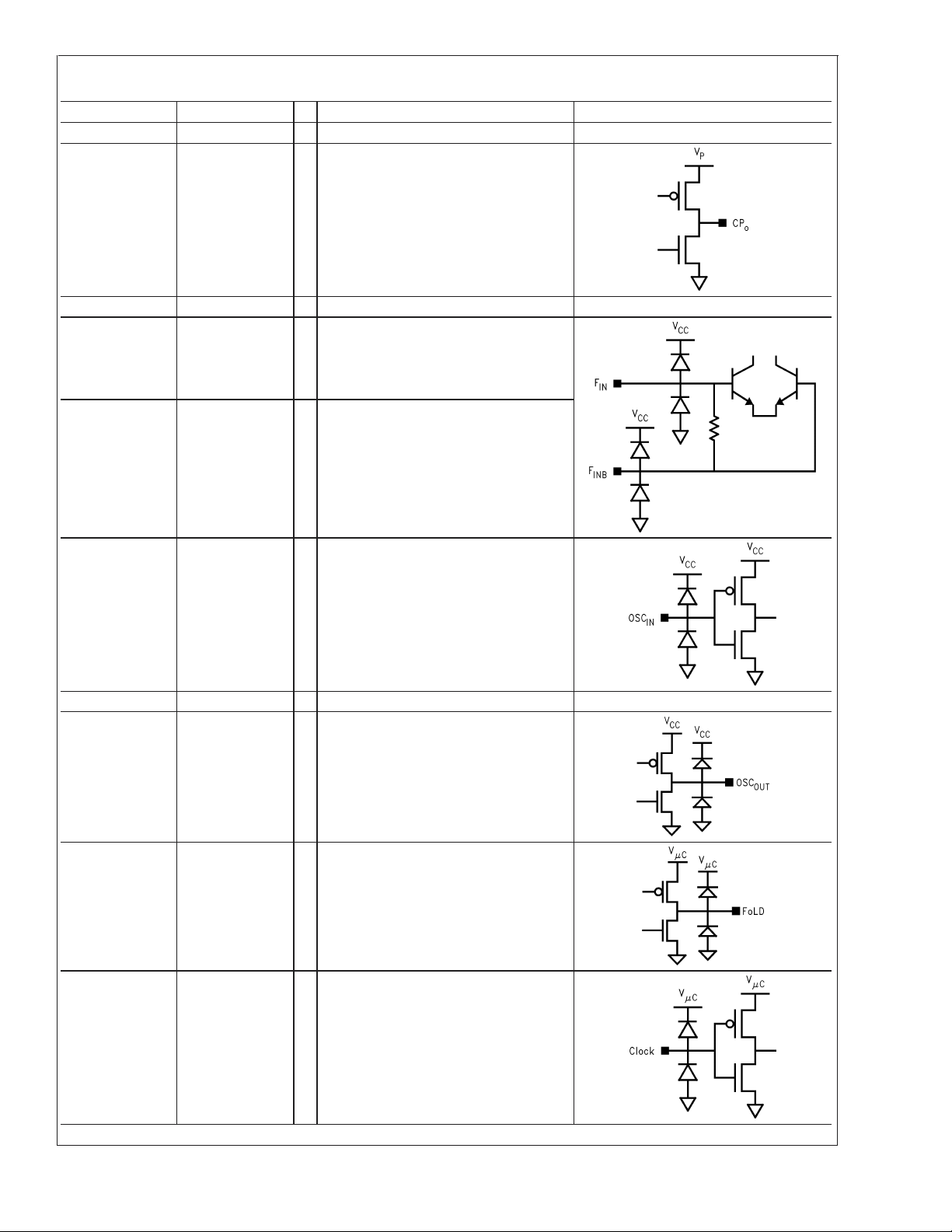

Pin Descriptions

Pin Number Pin Name I/O Description I/O Circuit Configuration

1 NC — No Connect.

2CP

o

3 GND — Analog ground.

4F

IN

O Charge Pump output. For connection to a

loop filter for driving the voltage control

input of an external VCO.

I RF prescaler input. Small signal input

from the VCO.

LMX2310U/LMX2311U/LMX2312U/LMX2313U

5F

INB

I RF prescaler complementary input. For

single ended operation, this pin should be

AC grounded. The LMX2310/1/2/3U can

be driven differentially when a bypass

capacitor is omitted.

6 OSC

IN

I Oscillator input. An input to a CMOS low

noise inverting buffer. The input can be

driven from an external CMOS or TTL

logic gate.

7 NC — No Connect.

8 OSC

OUT

O Oscillator output. The OSCINlow noise

buffer drives an independent oscillator

buffer. Its output is connected to the

OSC

pin. It can be used as a buffer to

OUT

provide the reference oscillator frequency

to other circuitry or as a crystal oscillator.

9 FoLD O Multi-function CMOS output pin that

provides multiplexed access to digital lock

detect, open drain analog lock detect, as

well as the outputs of the R and N

counters. The FoLD pin is internally

referenced to V

.

µC

10 Clock I High impedance CMOS Clock input. Data

for the counters is clocked in on the rising

edge, into the 22-bit shift register. The

Clock is internally referenced to V

.

µC

www.national.com3

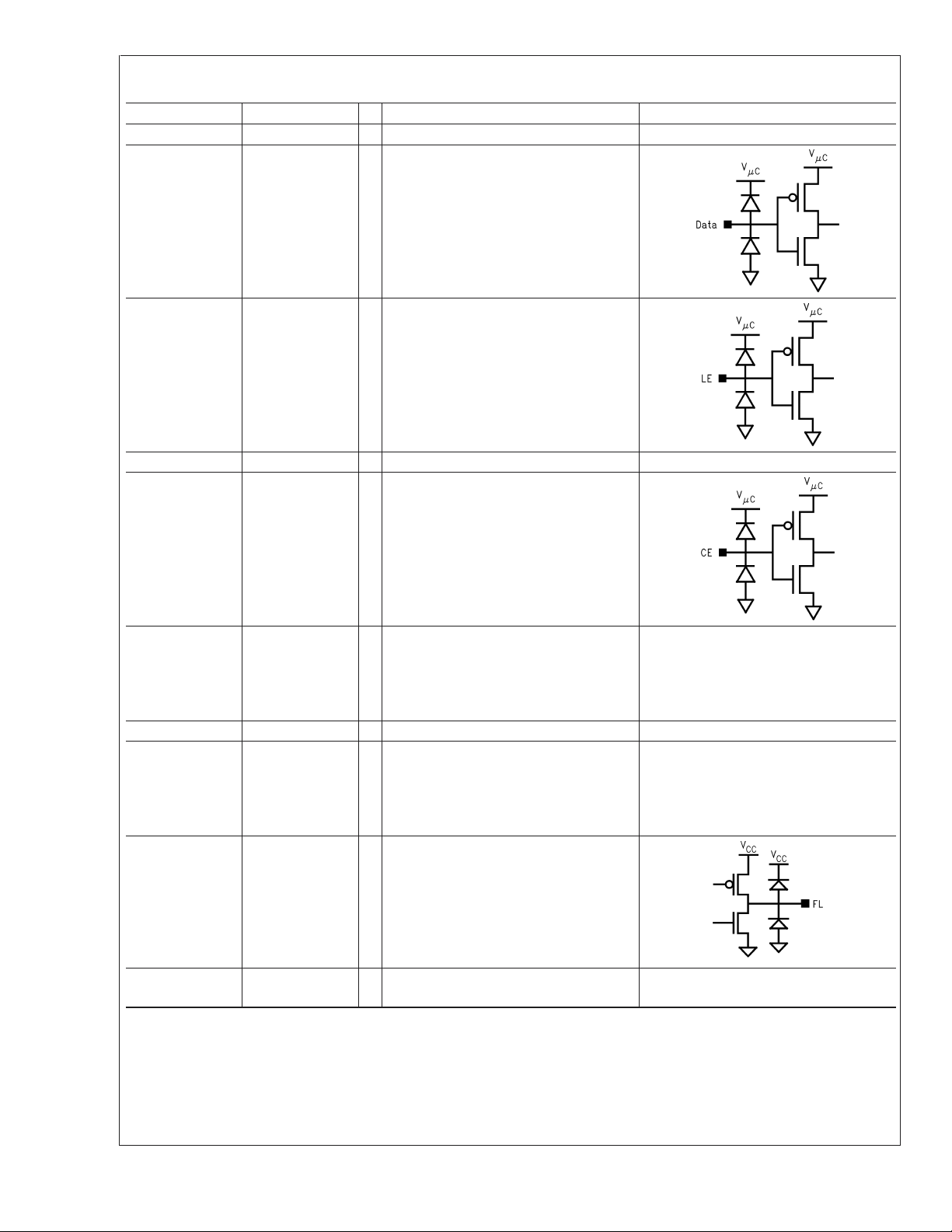

Pin Descriptions (Continued)

Pin Number Pin Name I/O Description I/O Circuit Configuration

11 NC — No Connect.

12 Data I High impedance CMOS Data input. Serial

Data is entered MSB first. The last two

bits are the address for the target

registers. The Data is internally referenced

.

to V

µC

13 LE I High impedance CMOS LE input. When

Latch Enable goes HIGH, data stored in

the 22-bit shift register is loaded into one

the 3 control registers, based on the

LMX2310U/LMX2311U/LMX2312U/LMX2313U

14 GND — Digital ground.

15 CE I High impedance CMOS Chip Enable

address field. The Latch Enable is

internally referenced to V

.

µC

input. Provides logical power-down control

of the device. Pull-up to V

if unused.

µC

The Chip Enable is internally referenced

.

to V

µC

16 V

µC

— Power supply for MICROWIRE™circuitry.

Must be ≤ V

. Typically connected to

CC

same supply level as microprocessor or

baseband controller to enable

programming at low voltages.

17 NC — No Connect.

18 V

CC

— Power supply voltage input. Input may

range from 2.7V to 5.5V. Bypass

capacitors should be placed as close as

possible to this pin and be connected

directly to the ground plane.

19 FL O Fastlock mode output. In Fastlock mode

this pin is at logic low. When not in

Fastlock mode, this pin is in TRI-STATE

mode. This pin can also be forced to

TRI-STATE, forced low or forced high by

the programming of the first two-bits of the

Timeout Counter.

20 V

P

— Power supply for charge pump. Must be ≥

.

V

CC

www.national.com 4

LMX2310U/LMX2311U/LMX2312U/LMX2313U

Absolute Maximum Ratings (Notes 1,

Lead Temp. (solder 4 sec.), (T

) +260˚C

L

2)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Power Supply Voltage,

(V

CC,VP,VµC

) −0.3V to +6.5V

Voltage on any pin with GND=0V

CP

, FL, FIN, OSCIN, OSC

o

Data, Clock, LE, CE, FoLD (V

Storage Temperature Range, (T

) −0.3V to VCC+ 0.3V

OUT(Vi

) −0.3V to VµC+ 0.3V

i

) −65˚C to +150˚C

S

Recommended Operating

Conditions

Power Supply Voltage

(V

) 2.7 5.5 V

CC

(V

)V

P

(V

) 1.72 V

µC

Operating Temperature, (T

(Note 1)

Min Max Unit

5.5 V

CC

CC

) −40 +85 ˚C

A

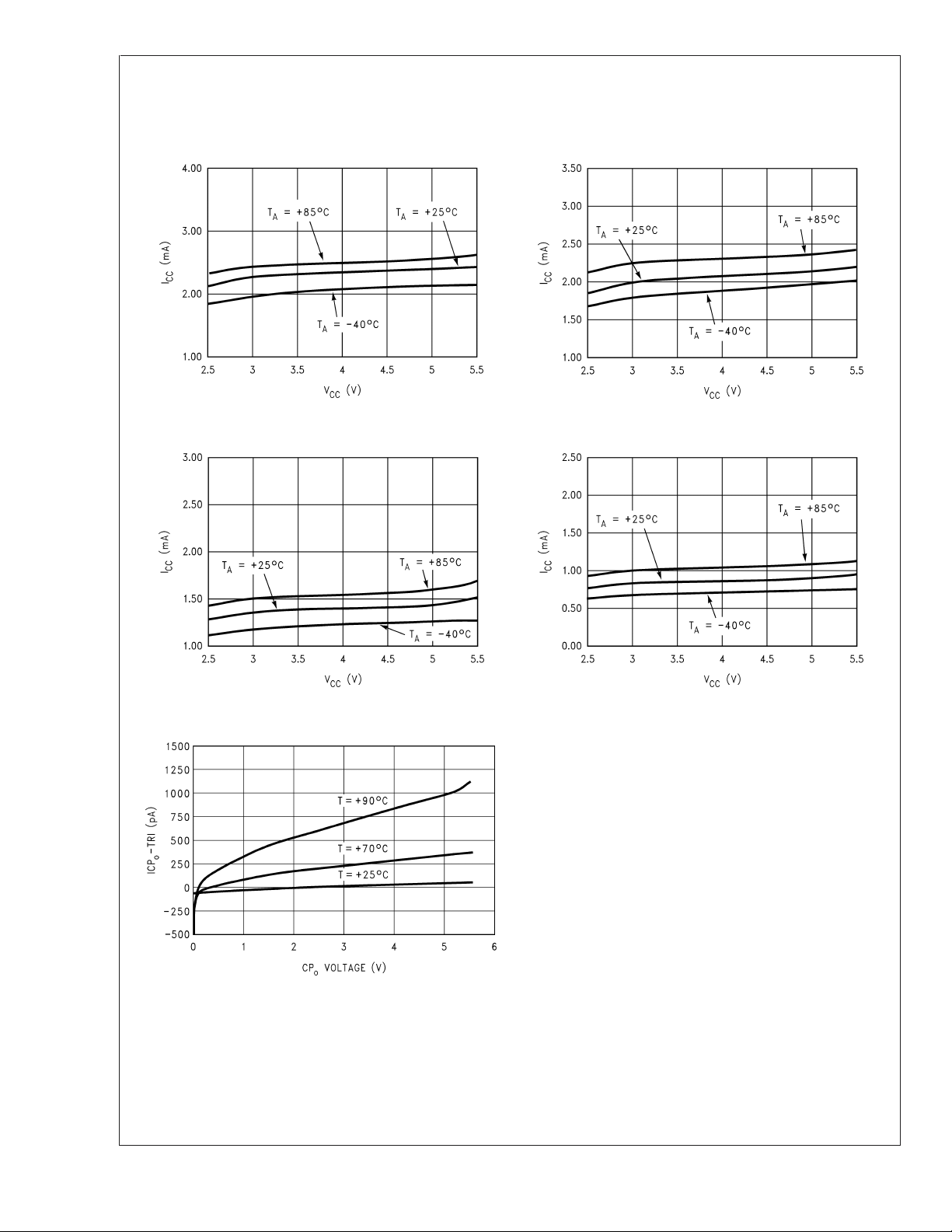

Electrical Characteristics

VCC=VP=VµC= 3.0V, −40˚C<T

Symbol Parameter Conditions (Note 3) Min Typ Max Units

I

CC

l

CC

I

CC-PWDN

Power Supply

Current

Power-Down Current

RF PRESCALER

F

PF

IN

IN

Operating

Frequency

Input Sensitivity, RF

Prescaler

PHASE DETECTOR

Fφ Phase Detector Frequency 10 MHz

REFERENCE OSCILLATOR

F

OSC

V

OSC

IN

I

IH

I

IL

V

OSC

OUT

D

OSC

OUT

V

OSC

OUT

V

OH

V

OL

I

OH

I

OL

Operating Frequency,

Reference Oscillator Input

Input Sensitivity,

Reference Oscillator Input

OSCINInput Current VIH=VCC= 5.5V 100 µA

OSCINInput Current VIL=0,VCC= 5.5V −100 µA

OSC

OSC

OSC

OSC

OSC

OSC

OSC

Bias Level OSCINOpen 1.5 V

OUT

Duty Cycle

OUT

Level

OUT

Output Voltage IOH= -500 µA 2.6 2.8 V

OUT

Output Voltage IOL= 500 µA 0.2 0.4 V

OUT

Output Current VOH= 2.25 V -1.1 mA

OUT

Output Current VOL= 0.75 V 1.1 mA

OUT

<

+85˚C unless specified otherwise.

A

LMX2310U

LMX2311U

LMX2312U

LMX2313U

(Note 4) 2.3 3.0 mA

V

= 5.5V (Note 4) 3.4 mA

CC

(Note 4) 2.0 2.7 mA

V

= 5.5V (Note 4) 3.2 mA

CC

(Note 4) 1.4 2.0 mA

V

= 5.5V (Note 4) 2.4 mA

CC

(Note 4) 1.0 1.3 mA

V

= 5.5V (Note 4) 1.6 mA

CC

Clock, Data and LE = GND

CE = GND

110 µA

LMX2310U 0.5 2.5 GHz

LMX2311U 0.5 2.0 GHz

LMX2312U 0.2 1.2 GHz

LMX2313U 45 600 MHz

2.7 ≤ V

3.0V

≤3.0V (Note 5) −15 0 dBm

CC

<

VCC≤ 5.5V (Note 5) −10 0 dBm

2 50 MHz

(Note 6) 0.5 V

OSC

= 20 MHz, 0.5 V

IN

Duty Cycle = 50%

OSC

IN

OSC

= 20 MHz, 0.5 V

IN

OSC

OUT

Load=10pF||10k

P-P

P-P

,

50 %

,

2.6 V

CC

V

P−P

P-P

Ohm

V

www.national.com5

Electrical Characteristics (Continued)

VCC=VP=VµC= 3.0V, −40˚C<T

Symbol Parameter Conditions (Note 3) Min Typ Max Units

CHARGE PUMP

ICPo-

source

ICPo-

ICPo-

ICPo-

ICPo-

sink

source

sink

tri

Charge Pump Output

Current (Note 7)

Charge Pump TRI-STATE

Current

vs.

ICPoICPo-

sink

source

CP Sink vs. Source

Mismatch

ICPo vs VCPo CP Current vs. Voltage 0.5V ≤ VCPo ≤ V

ICPo vs T

LMX2310U/LMX2311U/LMX2312U/LMX2313U

CP Current vs.

A

Temperature

DIGITAL INTERFACE (Data, Clock, LE, CE)

V

IH

V

IL

I

IH

I

IL

V

OH

High-level Input Voltage VµC= 1.72V to 5.5V 0.8 V

Low-level Input Voltage VµC= 1.72V to 5.5V 0.2 V

High-level Input Current VIH=VµC= 5.5V −1.0 1.0 µA

Low-level Input Current VIL= 0V, VµC= 5.5V −1.0 1.0 µA

High-level Output Voltage

(Pin 7– FoLD)

High-level Output Voltage

(Pin 15– FL)

V

OL

Low-level Output Voltage IOL= 1.0 mA (Note 9) 0.1 0.4 V

MICROWIRE TIMING (Data, Clock, LE, CE)

t

CS

t

CH

t

CWH

t

CWL

t

ES

Data to Clock Set Up Time (Note 10) 50 ns

Data to Clock Hold Time (Note 10) 20 ns

Clock Pulse Width High (Note 10) 50 ns

Clock Pulse Width Low (Note 10) 50 ns

Clock to Load Enable Set

Up Time

t

EW

Load Enable Pulse Width (Note 10) 50 ns

<

+85˚C unless specified otherwise.

A

VCPo = Vp/2, ICPo_4X = 0 0.8 1.0 1.2 mA

VCPo = Vp/2, ICPo_4X = 0 −0.8 −1.0 −1.2 mA

VCPo = Vp/2, ICPo_4X = 1 3.2 4.0 4.8 mA

VCPo = Vp/2, ICPo_4X = 1 −3.2 −4.0 −4.8 mA

0.5V ≤ VCPo ≤ VP− 0.5V

−2.5 2.5 nA

VCPo = Vp/2

T

A

= 25˚C

310 %

(Note 8)

− 0.5V

P

= 25˚C (Note 8)

T

A

VCPo = Vp/2V (Note 7)

IOH= 500 µA

I

= −500 µA

OH

(Note 10)

µC

− 0.4 V

V

µC

− 0.4 V

V

CC

50 ns

815 %

8%

V

µC

V

www.national.com 6

Electrical Characteristics (Continued)

VCC=VP=VµC= 3.0V, −40˚C<T

Symbol Parameter Conditions (Note 3) Min Typ Max Units

PHASE NOISE CHARACTERISTICS

L

L(f)

(f)

N

Normalized Single

Side-Band Phase Noise

Single Side-Band Phase

Noise

<

+85˚C unless specified otherwise.

A

= 200 kHz

F

φ

=10MHz

F

OSC

= 1.0 V

V

OSC

PP

ICPO=4mA

= 25˚C

T

A

(Note 11)

LMX2310U

= 2450 MHz

F

IN

= 200 kHz

F

φ

=10MHz

F

OSC

= 1.0 V

V

OSC

PP

ICPO=4mA

= 25˚C

T

A

(Note 12)

LMX2311U

= 1960 MHz

F

IN

= 200 kHz

F

φ

=10MHz

F

OSC

= 1.0 V

V

OSC

PP

ICPO=4mA

= 25˚C

T

A

(Note 12)

LMX2312U

= 902 MHz

F

IN

= 200 kHz

F

φ

=10MHz

F

OSC

= 1.0 V

V

OSC

PP

ICPO=4mA

= 25˚C

T

A

(Note 12)

LMX2313U

= 450 MHz

F

IN

=50kHz

F

φ

=10MHz

F

OSC

= 1.0 V

V

OSC

PP

ICPO=4mA

= 25˚C

T

A

(Note 12)

−159 dBc/Hz

−78 dBc/Hz

−80 dBc/Hz

−85 dBc/Hz

−85 dBc/Hz

LMX2310U/LMX2311U/LMX2312U/LMX2313U

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is

intended to be functional, but do not guarantee specific performance limits. For guaranteed specifications and conditions, see the Electrical Characteristics. The

guaranteed specifications apply only for the conditions listed.

Note 2: This device is a high performance RF integrated circuit with an ESD rating

workstations.

Note 3: Typical Conditions are at a T

Note 4: Icc current is measured with Clock, Data and LE pins connected to GND. OSCin and Fin pins are connected to Vcc. PWDN bit is program to 0. Icc current

is the current into Vcc pin.

Note 5: See F

Note 6: See OSC

Note 7: Charge Pump Magnitude is controlled by CPo_4X bit [R18].

Note 8: See Charge Pump Measurement Definition for detail on how these measurements are made.

Note 9: Analog Lock Detect open drain output pin only can be pulled up to V

Note 10: See Serial Input Data Timing.

Note 11: Normalized Single-Side Band Phase Noise is defined as: L

Sensitivity Test Setup.

IN

Sensitivity Test Setup.

IN

of 25˚C.

A

(f) = L(f) − 20 log (FIN/Fφ), where L(f) is defined as the Single Side-Band Phase Noise.

N

<

2 kV. Handling and assembly of this device should only be done at ESD free

that will not exceed 6.5V.

ext

www.national.com7

Note 12: Phase Noise is measured using a reference evaluation board with a loop bandwidth of approximately 12 kHz. The phase noise specification is the

composite average of 3 measurements made at frequency offsets of 2.0 kHz, 2.5 kHz and 3.0 kHz.

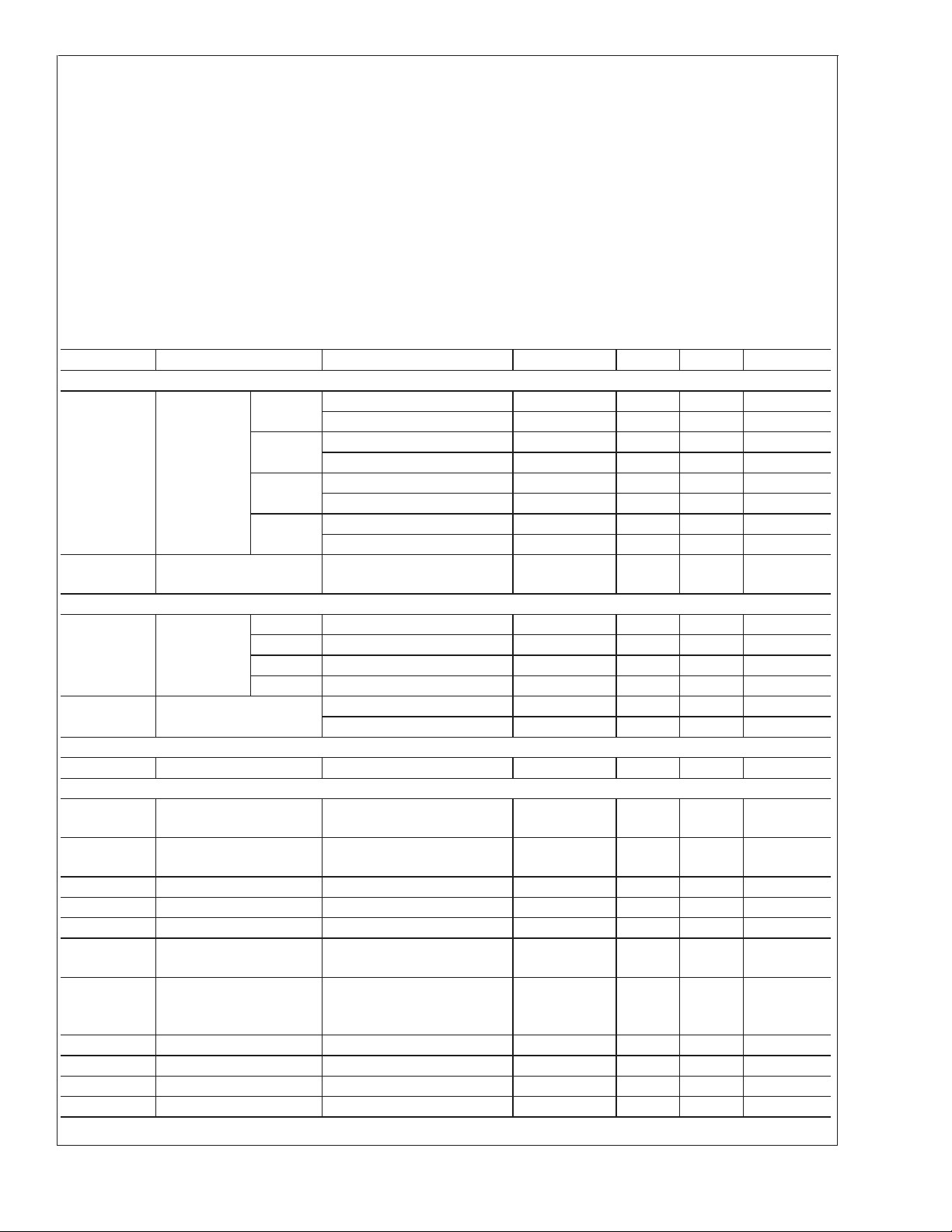

Typical Performance Characteristics

Iccvs VccLMX2310U Iccvs VccLMX2311U

LMX2310U/LMX2311U/LMX2312U/LMX2313U

20043838

Iccvs VccLMX2312U Iccvs VccLMX2313U

20043839

CPOTRI-STATE vs CPOVoltage

20043840 20043841

20043843

www.national.com 8

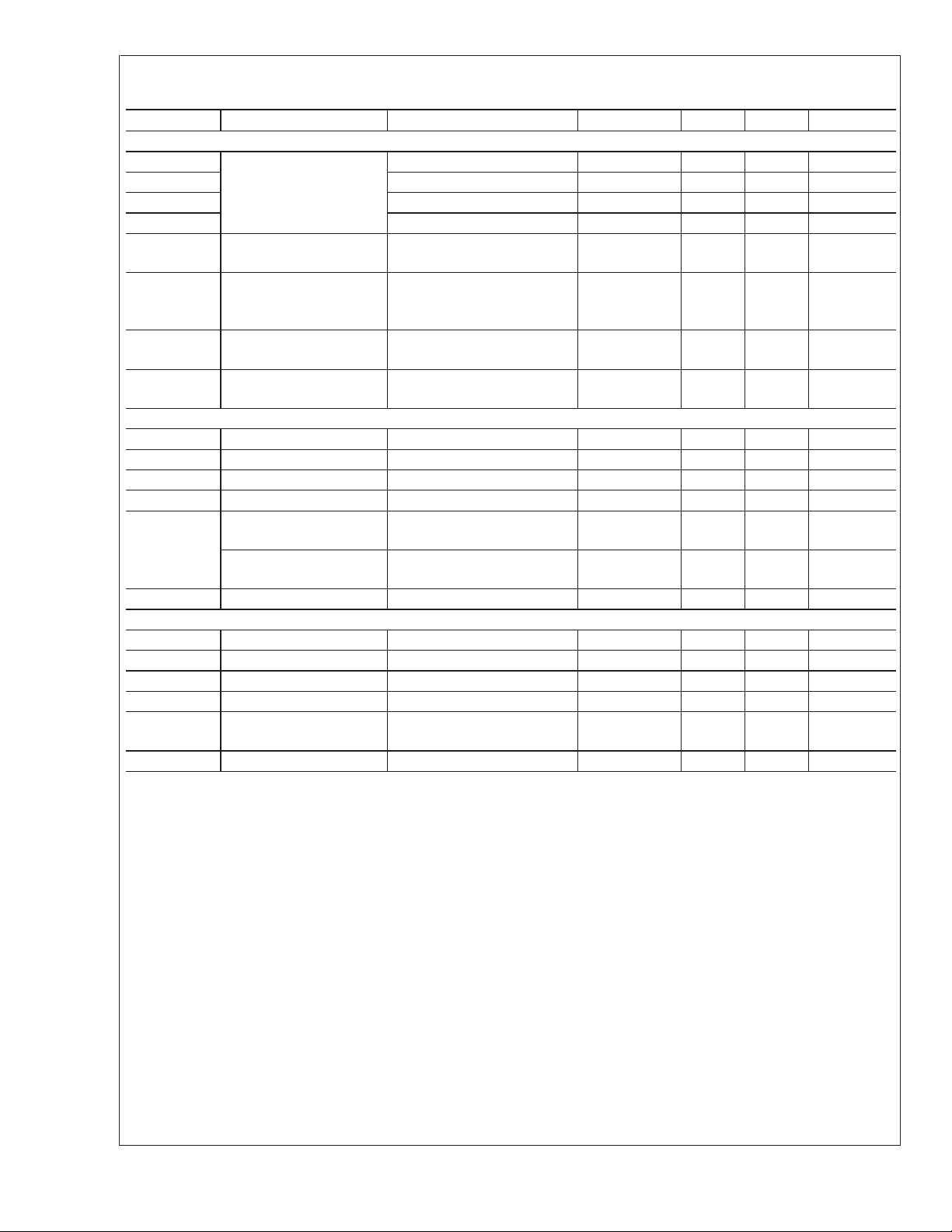

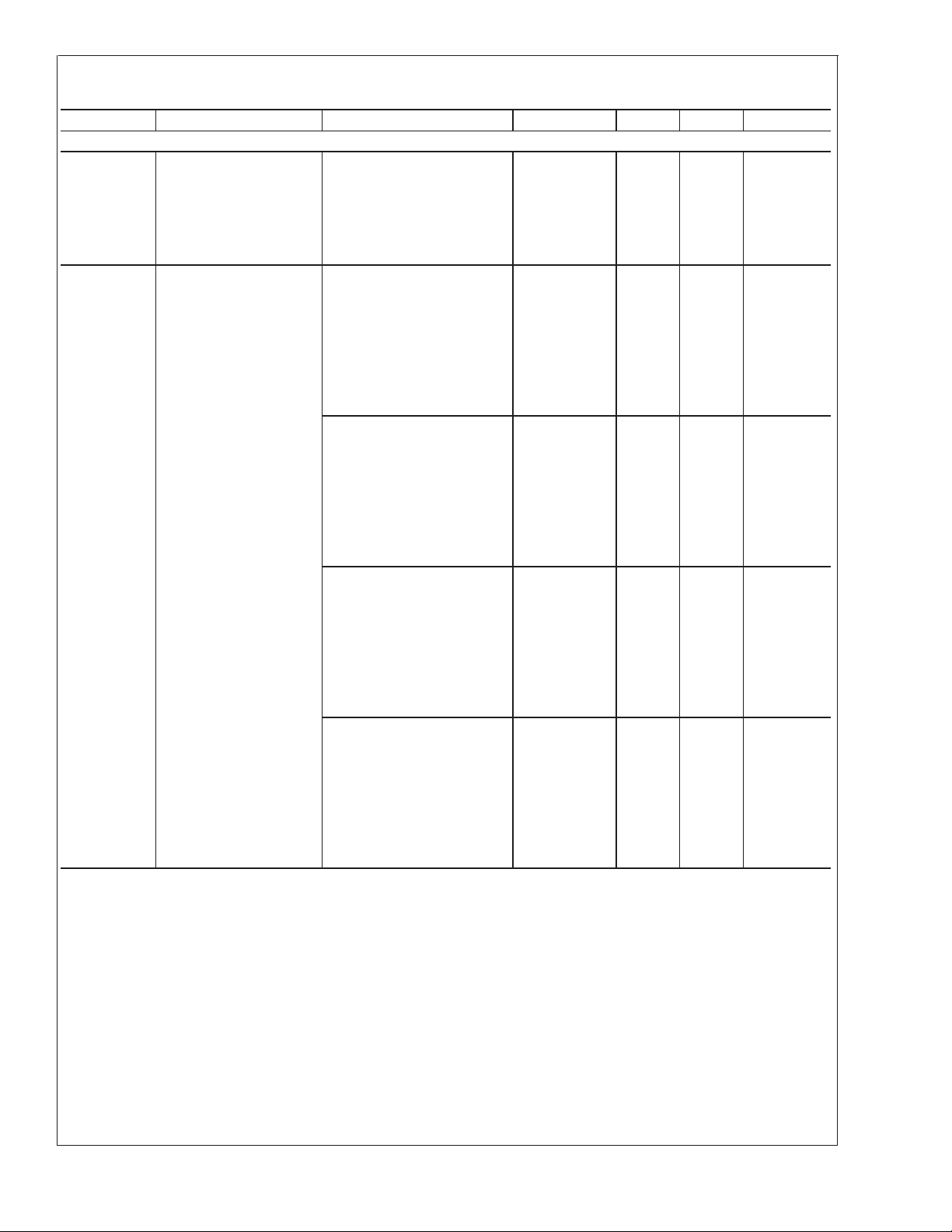

Typical Performance Characteristics (Continued)

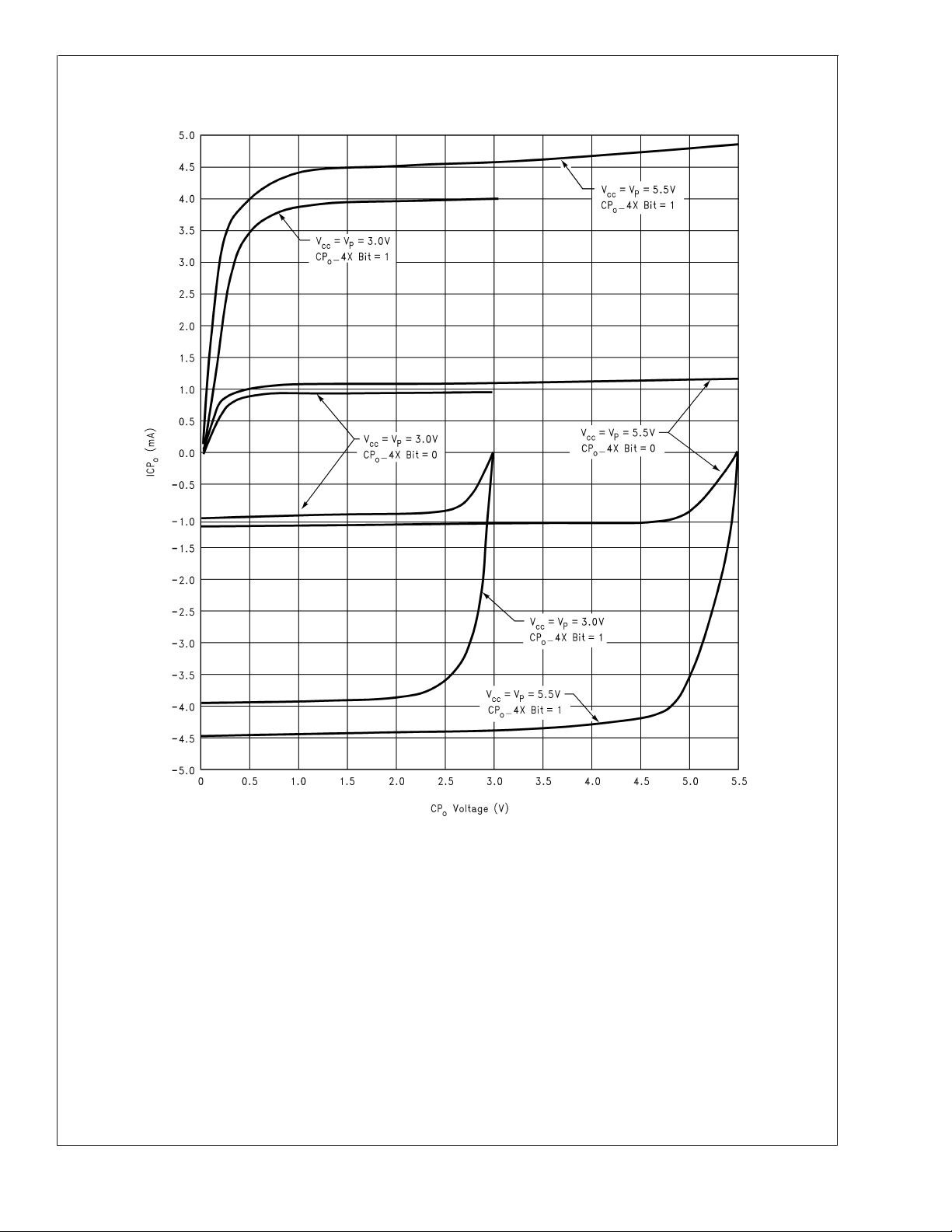

LMX231xU Charge Pump Sweeps

LMX2310U/LMX2311U/LMX2312U/LMX2313U

20043842

www.national.com9

Loading...

Loading...