查询LMX2301供应商

LMX2301

PLLatinum

for RF Personal Communications

TM

160 MHz Frequency Synthesizer

PRELIMINARY

November 1996

LMX2301 PLLatinum 160 MHz Frequency Synthesizer

for RF Personal Communications

General Description

The LMX2301 is a high performance frequency synthesizer

designed for RF operation up to 160 MHz. It is fabricated

using National’s ABiC IV BiCMOS process.

LMX2301, which employs the digital phase lock loop technique, combined with a high quality reference oscillator and

a loop filter, provides the tuning voltage for the voltage controlled oscillator to generate a very stable, low noise local

oscillator signal.

Serial data is transferred into the LMX2301 via a three line

MICROWIRE

age can range from 2.7V to 5.5V.

The LMX2301 features very low current consumption, typically 2 mA at 3V.

The LMX2301 is available in a TSSOP 20-pin surface mount

plastic package.

TM

interface (Data, Enable, Clock). Supply volt-

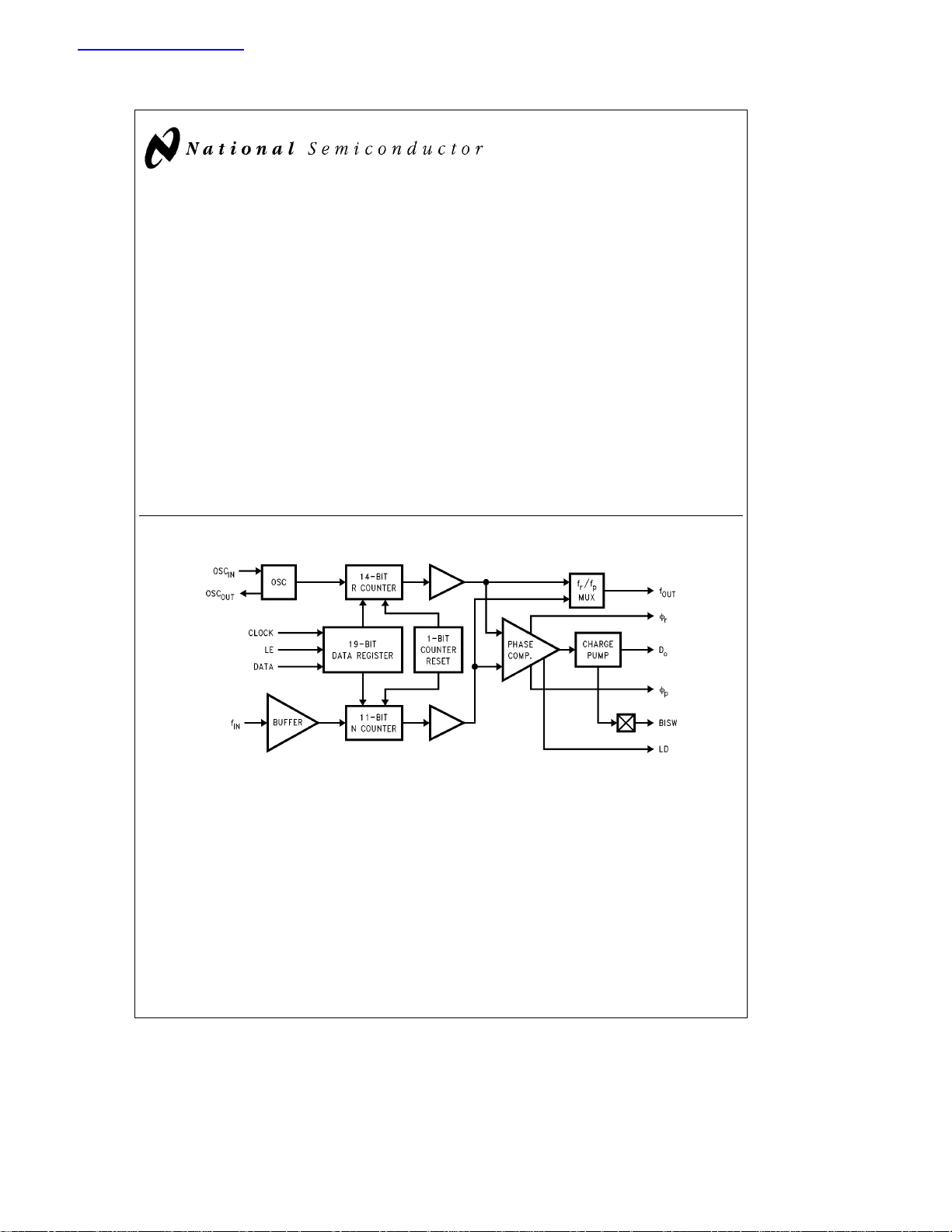

Block Diagram

Features

Y

RF operation up to 160 MHz

Y

2.7V to 5.5V operation

Y

Low current consumption:

e

I

2 mA (typ) at V

CC

Y

Internal balanced, low leakage charge pump

Y

Small-outline, plastic, surface mount TSSOP,

0.173

wide package

×

CC

e

3V

Applications

Y

Analog Cellular telephone systems

(AMPS, ETACS, NMT)

Y

Portable wireless communications

(PCS/PCN, cordless)

Y

Other wireless communication systems

TRI-STATEÉis a registered trademark of National Semiconductor Corporation.

TM

MICROWIRE

C

1996 National Semiconductor Corporation RRD-B30M126/Printed in U. S. A.

and PLLatinumTMare trademarks of National Semiconductor Corporation.

TL/W/12458

TL/W/12458– 1

http://www.national.com

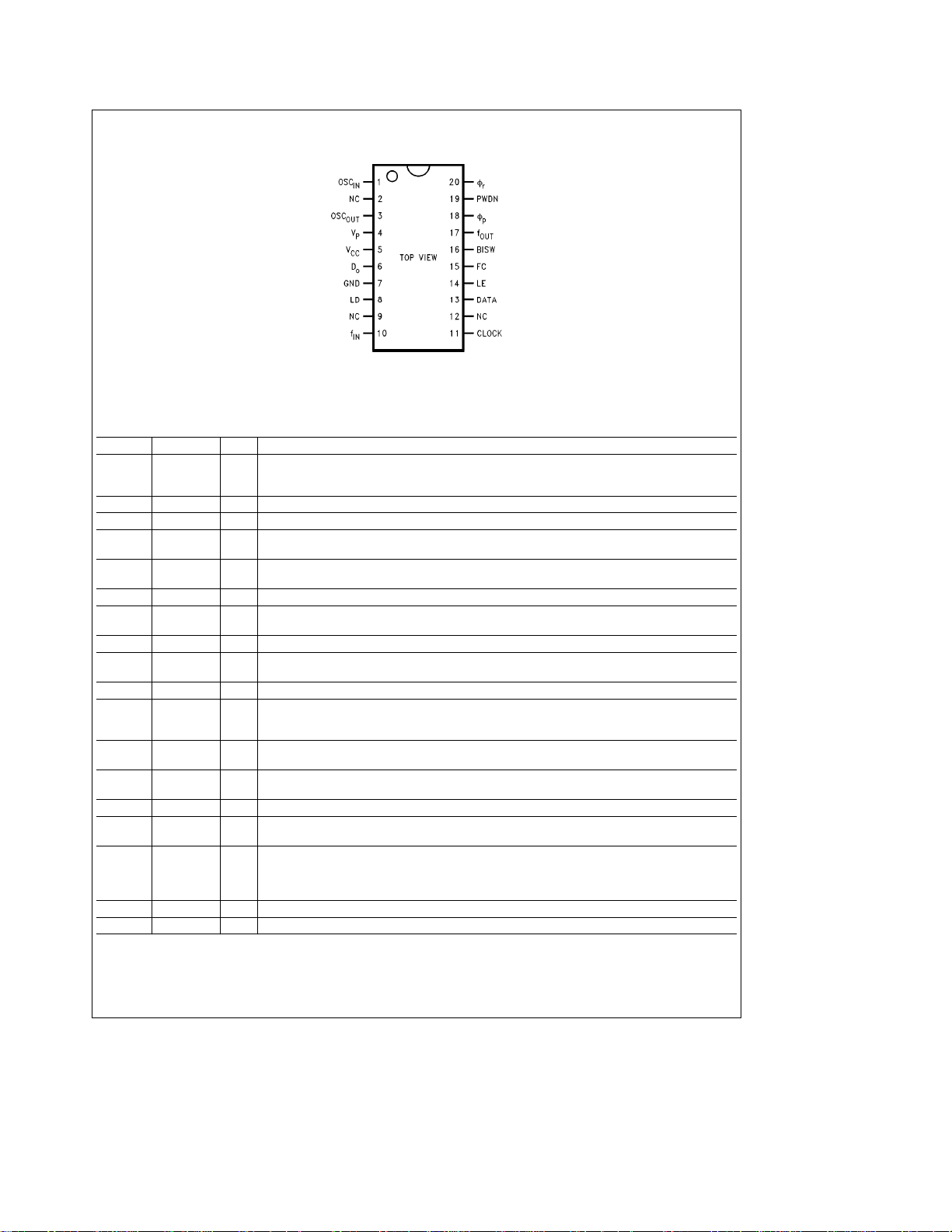

Connection Diagram

LMX2301

20-Lead (0.173×Wide) Thin Shrink

TL/W/12458– 2

Small Outline Package (TM)

Order Number LMX2301TM or LMX2301TMX

See NS Package Number MTC20

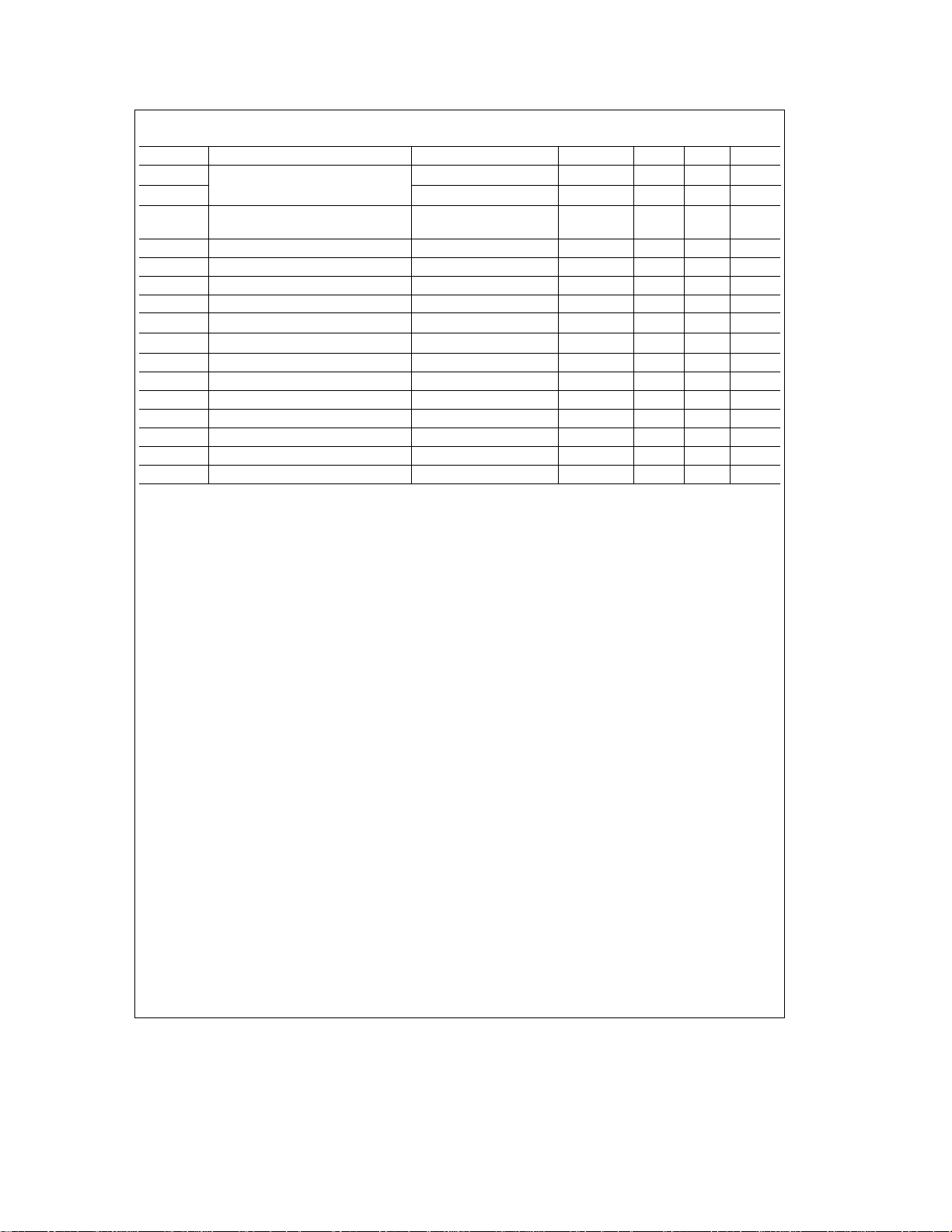

Pin Descriptions

Pin No. Pin Name I/O Description

1 OSC

3 OSC

4V

5V

6D

IN

OUT

P

CC

o

7 GND Ground.

8 LD O Lock detect. Output provided to indicate when the VCO frequency is in ‘‘lock’’. When the loop is

10 f

IN

11 CLOCK I High impedance CMOS Clock input. Data is clocked in on the rising edge, into the various

13 DATA I Binary serial data input. Data entered MSB first. LSB is control bit. High impedance CMOS input.

14 LE I Load enable input (with internal pull-up resistor). When LE transitions HIGH, data stored in the

15 FC I Phase control select (with internal pull-up resistor). When FC is LOW, the polarity of the phase

16 BISW O Analog switch output. When LE is HIGH, the analog switch is ON, routing the internal charge

17 f

18 w

OUT

p

19 PWDN I Power Down (with internal pull-up resistor).

20 w

r

2,9,12 NC No connect.

I Oscillator input. A CMOS inverting gate input intended for connection to a crystal resonator for

operation as an oscillator. The input has a V

external CMOS or TTL logic gate. May also be from a reference oscillator.

/2 input threshold and can be driven from an

CC

O Oscillator output.

Power supply for charge pump. Must betVCC.

Power supply voltage input. Input may range from 2.7V to 5.5V. Bypass capacitors should be

placed as close as possible to this pin and be connected directly to the ground plane.

O Internal charge pump output. For connection to a loop filter for driving the input of an external

VCO.

locked, the pin’s output is HIGH with narrow low pulses.

I RF buffer input. Small signal input from the VCO.

counters and registers.

shift registers is loaded into the appropriate latch (control bit dependent). Clock must be low

when LE toggles high or low. See Serial Data Input Timing Diagram.

comparator and charge pump combination is reversed.

pump output through BISW (as well as through D

).

o

O Monitor pin of phase comparator input. CMOS output.

O Output for external charge pump. wpis an open drain N-channel transistor and requires a pull-up

resistor.

e

PWDN

PWDNeLOW for power saving.

Power down function is gated by the return of the charge pump to a TRI-STATE condition.

HIGH for normal operation.

O Output for external charge pump. wris a CMOS logic output.

http://www.national.com 2

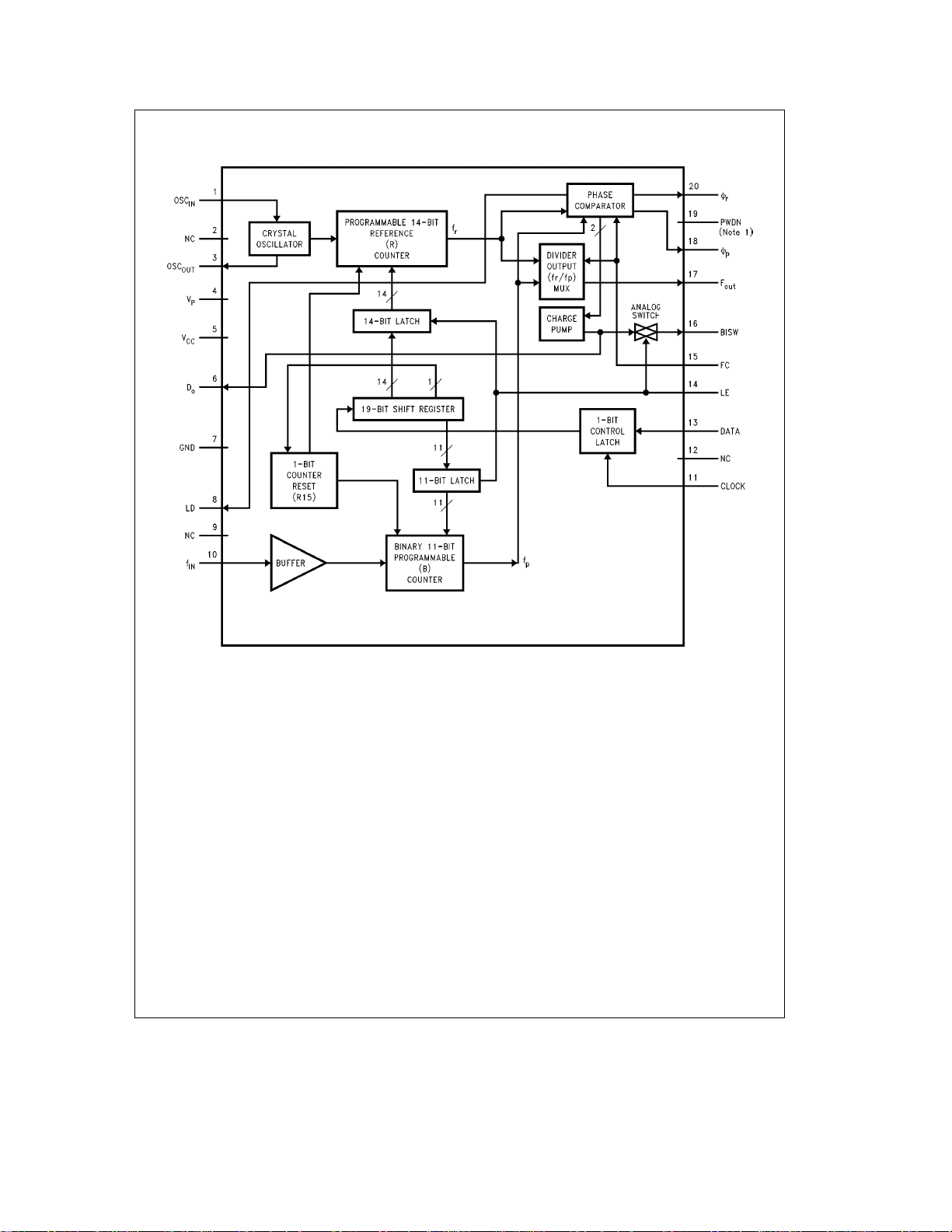

Functional Block Diagram

Note 1: The power down function is gated by the charge pump to prevent any unwanted frequency jumps. Once the power down pin is brought low the part will go

into power down mode when the charge pump reaches a TRI-STATE condition.

TL/W/12458– 3

http://www.national.com3

Absolute Maximum Ratings (Notes 1 and 2)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales

Office/Distributors for availability and specifications.

Power Supply Voltage

V

CC

V

P

Voltage on Any Pin

with GND

e

0V (VI)

Storage Temperature Range (TS)

Lead Temperature (TL) (solder, 4 sec.)

b

0.3V toa6.5V

b

0.3V toa6.5V

b

0.3V to V

b

65§Ctoa150§C

CC

a

a

0.3V

260§C

Recommended Operating

Conditions

Power Supply Voltage

V

CC

V

P

Operating Temperature (TA)

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to

the device may occur. Operating Ratings indicate conditions for which the

device is intended to be functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test

conditions listed.

Note 2: This device is a high performance RF integrated circuit with an ESD

k

2 keV and is ESD sensitive. Handling and assembly of this device

rating

should only be done at ESD workstations.

2.7V to 5.5V

VCCtoa5.5V

b

40§Ctoa85§C

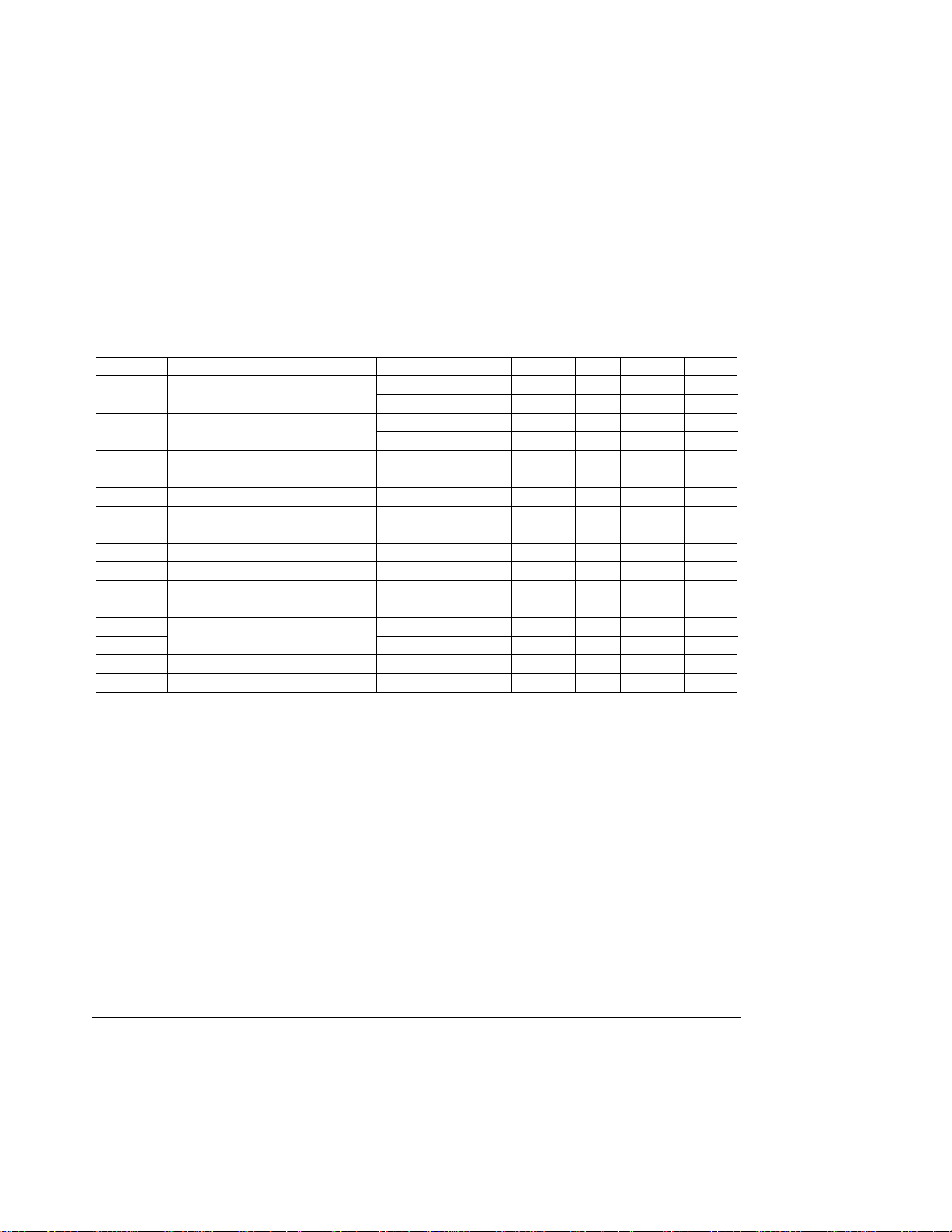

Electrical Characteristics V

CC

e

5V, V

e

5V;b40§CkT

P

k

85§C, except as specified

A

Symbol Parameter Conditions Min Typ Max Units

I

CC

I

CC-PWDN

f

IN

f

OSC

f

w

Pf

IN

V

OSC

V

IH

V

IL

I

IH

I

IL

I

IH

I

IL

I

IH

I

IL

*Except fINand OSC

Power Supply Current V

Power Down Current V

RF Input Operating Frequency 45 160 MHz

Oscillator Input Operating Frequency 5 20 MHz

Phase Detector Frequency 10 MHz

Input Sensitivity V

Oscillator Sensitivity OSC

High-Level Input Voltage * 0.7 V

Low-Level Input Voltage * 0.3 V

High-Level Input Current (Clock, Data) V

Low-Level Input Current (Clock, Data) V

Oscillator Input Current V

High-Level Input Current (LE, FC) V

Low-Level Input Current (LE, FC) V

IN

e

3.0V 2.0 5 mA

CC

e

V

5.0V 3.0 mA

CC

e

3.0V 30 180 mA

CC

e

V

5.0V 60 350 mA

CC

CC

IH

IL

IH

V

IL

IH

IL

e

2.7V to 5.5V

IN

e

V

CC

e

0V, V

e

V

CC

e

0V, V

e

V

CC

e

0V, V

e

5.5V

e

5.5V

CC

e

5.5V 100 mA

e

5.5V

CC

e

5.5V

e

5.5V

CC

b

10

0.5 V

CC

b

1.0 1.0 mA

b

1.0 1.0 mA

b

100 mA

b

1.0 1.0 mA

b

100 1.0 mA

a

6 dBm

CC

PP

V

V

http://www.national.com 4

Electrical Characteristics V

CC

e

5.0V, V

e

5.0V;b40§CkT

P

k

85§C, except as specified (Continued)

A

Symbol Parameter Conditions Min Typ Max Units

I

Do-source

I

Do-sink

I

Do-Tri

V

OH

V

OL

V

OH

V

OL

I

OL

I

OH

R

ON

t

CS

t

CH

t

CWH

t

CWL

t

ES

t

EW

**Except OSC

Charge Pump Output Current V

Charge Pump TRI-STATEÉCurrent 0.5VsV

High-Level Output Voltage I

Low-Level Output Voltage I

High-Level Output Voltage (OSC

Low-Level Output Voltage (OSC

)I

OUT

)I

OUT

Open Drain Output Current (wp)V

Open Drain Output Current (wp)V

e

VP/2

D

o

e

V

VP/2 5.0 mA

D

o

s

b

V

D

o

e

T

25§C

A

eb

1.0 mA** V

OH

e

1.0 mA** 0.4 V

OL

eb

200 mAV

OH

e

200 mA 0.4 V

OL

e

5.0V, V

CC

e

5.5V 100 mA

OH

0.5V

P

e

0.4V 1.0 mA

OL

b

5.0 5.0 nA

b

CC

b

CC

Analog Switch ON Resistance 100 X

Data to Clock Set Up Time See Data Input Timing 50 ns

Data to Clock Hold Time See Data Input Timing 10 ns

Clock Pulse Width High See Data Input Timing 50 ns

Clock Pulse Width Low See Data Input Timing 50 ns

Clock to Enable Set Up Time See Data Input Timing 50 ns

Enable Pulse Width See Data Input Timing 50 ns

OUT

b

5.0 mA

0.8 V

0.8 V

http://www.national.com5

Functional Description

The simplified block diagram below shows the 19-bit data register, the 14-bit R Counter and the R15 Latch, and the 11-bit

N Counter (intermediate latches are not shown). The data stream is clocked (on the rising edge) into the DATA input, MSB first.

If the Control Bit (last bit input) is HIGH, the DATA is transferred into the R Counter (programmable reference divider) and the

S Latch (power up counter reset). If the Control Bit (LSB) is LOW, the DATA is transferred into the N Counter (programmable

divider).

TL/W/12458– 1

PROGRAMMABLE REFERENCE DIVIDER (R COUNTER) AND COUNTER RESET (R15 LATCH)

If the Control Bit (last bit shifted into the Data Register) is HIGH, data is transferred from the 19-bit shift register into a 14-bit

latch (which sets the 14-bit R Counter) and the 1-bit R15 Latch, which can be used to force an immediate load of the R and N

counters during a cold power up condition. Serial data format is shown below.

14-BIT PROGRAMMABLE REFERENCE DIVIDER RATIO

(R COUNTER)

Divide

Ratio

14R13R12R11R10

R

RR9R8R7R6R5R4R3R2R

1

3 0 0 0 0 0 000000011

4 0 0 0 0 0 000000100

# # # # # # #########

16383 1 1 1 1 1 1 1 1 1 1 1 1 1 1

Notes: Divide ratios less than 3 are prohibited.

Divide ratio: 3 to 16383

R1 to R14: These bits select the divide ratio of the programmable

reference divider.

C: Control bit (set to HIGH level to load R counter and R15 Latch)

Data is shifted in MSB first.

SUGGESTED PROGRAMMING SEQUENCE AFTER COLD POWER-UP

1. Program N counter with desired divide ratio.

2. Program R counter with R15

3. Program R counter with R15e0 and desired divide ratio. (N and R counters start counting.)

http://www.national.com 6

e

1 and desired divide ratio. (N and R counters hold at load state.)

TL/W/12458– 14

1-BIT COUNTER RESET

(R15 LATCH)

Counter R

Reset 15

Remove

Forced Load

Force

Load State

0

1

The 1-bit counter reset latch controls

whether the R and N counters are immediately forced to load conditions

upon power up. If R[15

e

]

HIGH, the

N and R latch states are immediately

read into the respective counters.

Functional Description (Continued)

PROGRAMMABLE DIVIDER (N COUNTER)

The N counter consists of the 11-bit programmable counter. If the Control Bit (last bit shifted into the Data Register) is LOW,

data is transferred from the 19-bit shift register into an 11-bit latch, which sets the 11-bit programmable Counter. Serial data

format is shown below.

Note: R8 to R18: Programmable counter divide ratio control bits (3 to 2047)

7 LSB BITS OF N REGISTER

Divide N N N N N N N

Ratio 7 6 5 4 3 2 1

X XXXXXXX

Note: XeDon’t care state

11-BIT PROGRAMMABLE COUNTER DIVIDE RATIO

Divide

Ratio

18N17N16N15N14N13N12N11N10

N

NN9N

8

3 00000000011

4 00000000100

# ###########

2047 1 1 1 1 1 1 1 1 1 1 1

Note: Divide ratio: 3 to 2047 (Divide ratios less than 3 are prohibited)

TL/W/12458– 15

EQUATION FOR OUTPUT FREQUENCY

DETERMINATION

e

c

[N]

f

VCO

f

: Output frequency of external voltage controlled oscil-

VCO

f

lator (VCO)

OSC

/R

N: Preset divide ratio of binary 11-bit programmable

counter (3 to 2047)

f

: Output frequency of the external reference frequency

OSC

oscillator

R: Preset divide ratio of binary 14-bit programmable ref-

erence counter (3 to 16383)

http://www.national.com7

Functional Description (Continued)

SERIAL DATA INPUT TIMING

Notes: Parenthesis data indicates programmable reference divider data.

Data shifted into register on clock rising edge.

Data is shifted in MSB first.

Test Conditions: The Serial Data Input Timing is tested using a symmetrical waveform around V

amplitudes of 2.2V

@

V

CC

e

2.7V and 2.6V@V

e

5.5V.

CC

Phase Characteristics

In normal operation, the FC pin is used to reverse the polarity of the phase detector. Both the internal and any external

charge pump are affected.

Depending upon VCO characteristics, FC pin should be set

accordingly:

When VCO characteristics are like (1), FC should be set

HIGH or OPEN CIRCUIT;

When VCO characteristics are like (2), FC should be set

LOW.

When FC is set HIGH or OPEN CIRCUIT, the monitor pin of

the phase comparator input, f

divider output, f

programmable divider output, f

. When FC is set LOW, f

r

PHASE COMPARATOR AND INTERNAL CHARGE PUMP CHARACTERISTICS

, is set to the reference

out

.

p

is set to the

out

TL/W/12458– 16

/2. The test waveform has an edge rate of 0.6 V/ns with

CC

VCO Characteristics

TL/W/12458– 17

Notes: Phase difference detection range:b2q toa2q

The minimum width pump up and pump down current pulses occur at the Dopin when the loop is locked.

e

FC

HIGH

http://www.national.com 8

TL/W/12458– 18

Analog Switch

The analog switch is useful for radio systems that utilize a frequency scanning mode and a narrow band mode. The purpose of

the analog switch is to decrease the loop filter time constant, allowing the VCO to adjust to its new frequency in a shorter

amount of time. This is achieved by adding another filter stage in parallel. The output of the charge pump is normally through the

D

pin, but when LE is set HIGH, the charge pump output also becomes available at BISW. A typical circuit is shown below. The

o

second filter stage (LPF-2) is effective only when the switch is closed (in the scanning mode).

TL/W/12458– 19

Typical Crystal Oscillator Circuit

A typical circuit which can be used to implement a crystal

oscillator is shown below.

TL/W/12458– 20

Typical Lock Detect Circuit

A lock detect circuit is needed in order to provide a steady

LOW signal when the PLL is in the locked state. A typical

circuit is shown below.

TL/W/12458– 21

http://www.national.com9

Typical Application Example

Operational Notes:

* VCO is assumed AC coupled.

** R

increases impedance so that VCO output power is provided to the load rather than the PLL. Typical values are 10X to 200X depending on the VCO power

IN

level. f

RF impedance ranges from 40X to 100 X.

IN

*** 50X termination is often used on test boards to allow use of external reference oscillator. For most typical products a CMOS clock is used and no terminating

resistor is required. OSC

Application Hints:

Proper use of grounds and bypass capacitors is essential to achieve a high level of performance.

Crosstalk between pins can be reduced by careful board layout.

This is an electrostatic sensitive device. It should be handled only at static free work stations.

may be AC or DC coupled. AC coupling is recommended because the input circuit provides its own bias. (See

IN

TL/W/12458– 23

TL/W/12458– 22

Figure

below)

http://www.national.com 10

Application Information

LOOP FILTER DESIGN

A block diagram of the basic phase locked loop is shown.

FIGURE 1. Basic Charge Pump Phase Locked Loop

An example of a passive loop filter configuration, including

the transfer function of the loop filter, is shown in

Z(s)

e

s (C2#R2)a1

s2(C1#C2#R2)asC1asC2

Figure 2

TL/W/12458– 25

FIGURE 2. 2nd Order Passive Filter

Define the time constants which determine the pole and

zero frequencies of the filter transfer function by letting

T2eR2#C2 (1a)

and

T1

#

C1aC2 (1b)

C1#C2

e

R2

The PLL linear model control circuit is shown along with the

open loop transfer function in

detector and VCO gain constants[Kw and K

loop filter transfer function[Z(s)], the open loop Bode plot

Figure 3

. Using the phase

]

and the

VCO

can be calculated. The loop bandwidth is shown on the

Bode plot (

is shown to be the difference between the phase at the unity

gain point and

Open Loop Gaineii/i

Closed Loop Gaineio/i

0p) as the point of unity gain. The phase margin

b

180§.

e

H(s) G(s)

e

Kw Z(s) K

VCO

/Ns

e

e

G(s)/[1aH(s) G(s)

i

TL/W/12458– 27

]

.

FIGURE 3. Open Loop Transfer Function

Thus we can calculate the 3rd order PLL Open Loop Gain in

terms of frequency

G(s)

l

sej

e

0

#

2

0

H(s)

#

Kw#K

(1aj0#T2)

VCO

C1#N(1aj0#T1)

b

From equation 2 we can see that the phase term will be

dependent on the single pole and zero such that

b

1

e

w(

0)

tan

(0#T2)btan

b

1

(0#T1)a180§(3)

By setting

dw

d0

e

1a(0#T2)

T2

2

b

1a(0#T1)

T1

we find the frequency point corresponding to the phase inflection point in terms of the filter time constants T1 and T2.

This relationship is given in equation 5.

e

0

1/0T2#T1 (5)

For the loop to be stable the unity gain point must occur

before the phase reaches

p

b

180 degrees. We therefore

want the phase margin to be at a maximum when the magnitude of the open loop gain equals 1. Equation 2 then gives

C1

e

Kw#K

0

p

2

VCO

#N#

#

T2

T1

(1aj0

(1aj0

Ó

T2)

#

p

T1)

#

p

TL/W/12458– 24

TL/W/12458– 26

T1

#

T2 (2)

e

0

2

Ó

(4)

(6)

http://www.national.com11

Application Information (Continued)

0

Ð0

c

p

p

(1

2

T2)

#

T1)

#

a

1

a

T12)(1

#

, and the

p

2

2

opt/fref

(T1aT3)

[

tanw

2

0

T22)

#

c

a

(7)

(9)

(10)

#

0

Therefore, if we specify the loop bandwidth,

phase margin, w

late the two time constants, T1 and T2, as shown in equations 7 and 8. A common rule of thumb is to begin your

design with a 45

From the time constants T1, and T2, and the loop bandwidth,

0

equations 9 to 11.

K

(MHz/V) Voltage Controlled Oscillator (VCO)

VCO

Kw (mA) Phase detector/charge pump gain

N Main divider ratio. Equal to RF

RF

(MHz) Radio Frequency output of the VCO at

opt

f

(kHz) Frequency of the phase detector in-

ref

T2

0

C1

, Equations 1 through 6 allow us to calcu-

p

phase margin.

§

e

T1

T2

, the values for C1, R2, and C2 are obtained in

p

T1

Kw#K

e

C1

#

T2

e

C2

Tuning Voltage constant. The frequency vs voltage tuning ratio.

constant. The ratio of the current output to the input phase differential.

which the loop filter is optimized.

puts. Usually equivalent to the RF

channel spacing.

e

e

c

e

1

2

0

(T1aT3) (15)

#

c

tanw#(T1aT3)

a

[

(T1

T3)

T1

Kw#K

#

T2

0

c

b

secw

tanw

p

p

0

p

1

e

2

0

T1 (8)

#

p

1a(0

VCO

2

0

N

1a(0

#

0

p

T2

C1

R2

2

2

#

b

1

#

T1

#

J

T2

e

C2 (11)

T1#T3

#

(1

Ð

#

]

a

0

a

VCO

N

In choosing the loop filter components a trade off must be

made between lock time, noise, stability, and reference

spurs. The greater the loop bandwidth the faster the lock

time will be, but a large loop bandwidth could result in higher

reference spurs. Wider loop bandwidths generally improve

close in phase noise but may increase integrated phase

noise depending on the reference input, VCO and division

ratios used. The reference spurs can be reduced by reducing the loop bandwidth or by adding more low pass filter

stages but the lock time will increase and stability will decrease as a result.

THIRD ORDER FILTER

A low pass filter section may be needed for some applications that require additional rejection of the reference sidebands, or spurs. This configuration is given in

order to compensate for the added low pass section, the

component values are recalculated using the new open

loop unity gain frequency. The degradation of phase margin

caused by the added low pass is then mitigated by slightly

increasing C1 and C2 while slightly decreasing R2.

The added attenuation from the low pass filter is:

Defining the additional time constant as

Then in terms of the attenuation of the reference spurs added by the low pass pole we have

We then use the calculated value for loop bandwidth

equation 11, to determine the loop filter component values

in equations 15 –17.

the frequency jump lock time will increase.

2

a

T1#T3

2

(T1aT3)

c

]

(/2

2

T32)

#

(

ATTEN

b

1

(

e

20 log[(2qf

T3eR3#C3 (13)

e

T3

0

0

c

#R3#

ref

ATTEN/20

10

(2q#f

is slightly less than 0p, therefore

2

C3)

b

1

2

)

ref

Figure 4

a

1](12)

0

.In

(14)

c

(16)

(17)

in

http://www.national.com 12

Application Information (Continued)

EXTERNAL CHARGE PUMP

The LMX PLLatinum series of frequency synthesizers are

equipped with an internal balanced charge pump as well as

outputs for driving an external charge pump. Although the

superior performance of NSC’s on board charge pump eliminates the need for an external charge pump in most applications, certain system requirements are more stringent. In

these cases, using an external charge pump allows the designer to take direct control of such parameters as charge

pump voltage swing, current magnitude, TRI-STATE leakage, and temperature compensation.

One possible architecture for an external charge pump current source is shown in

the diagram, correspond to the phase detector outputs of

the LMX2301 frequency synthesizer. These logic signals are

converted into current pulses, using the circuitry shown in

Figure 9

, to enable either charging or discharging of the

loop filter components to control the output frequency of the

PLL.

Referring to

Figure 9

current which is relatively constant to within 0.5V of the

power supply rail. To accomplish this, it is important to establish as large of a voltage drop across R5, R8 as possible

without saturating Q2, Q4. A voltage of approximately 300

mV provides a good compromise. This allows the current

source reference being generated to be relatively repeatable in the absence of good Q1, Q2/Q3, Q4 matching.

(Matched transistor pairs is recommended.) The wp and wr

outputs are rated for a maximum output load current of 1

mA while 5 mA current sources are desired. The voltages

developed across R4, 9 will consequently be approximately

258 mV, or 42 mV

À

ences

0.026*1n (5 mA/1 mA)Óthrough the Q1, Q2/Q3, Q4

pairs.

In order to calculate the value of R7 it is necessary to first

estimate the forward base to emitter voltage drop (Vfn,p) of

the transistors used, the V

of wr’s under 1 mA loads. (wp’s V

k

V

0.1V.)

OH

Knowing these parameters along with the desired current

allow us to design a simple external charge pump. Separating the pump up and pump down circuits facilitates the nodal analysis and give the following equations.

b

V

R5

e

R

4

b

V

R8

e

R

9

V

R5

e

R

5

i

p max

V

R8

e

R

8

i

r max

b

(V

p

e

R

6

b

(V

P

e

R

7

Figure 9

. The signals wpand wrin

, the design goal is to generatea5mA

k

R8, 5, due to the current density differ-

drop of wp, and the VOHdrop

V

T

i

V

T

V

VOLwp

V

VOHwr

ln

#

source

ln

#

i

sink

i

#

#

)b(V

p max

)b(V

i

max

OL

i

source

i

p max

i

sink

i

n max

J

J

R5

R8

k

0.1V and wr’s

OL

a

Vfp)

a

Vfn)

EXAMPLE

Typical Device Parameters b

Typical System Parameters V

Design Parameters I

FIGURE 9

Therefore select

0.3Vb0.026#1n(5.0 mA/1.0 mA)

e

e

R

R

4

9

0.3V

e

R

5

e

R

8

e

R

6

e

1.0 mA

1.0 mA

R

300X

0.3V

e

300X

(5Vb0.1V)b(0.3Va0.8V)

e

7

1.0 mA

n

P

V

cntl

V

wp

SINK

V

fn

I

rmax

V

R8

V

OLwp

5mA

e

100, b

e

5.0V;

e

0.5Vb4.5V;

e

0.0V; V

e

I

SOURCE

e

V

fp

e

I

pmax

e

V

R5

e

V

p

e

e

OHwr

e

50

e

wr

e

0.8V

e

1mA

0.3V

e

TL/W/12458– 28

e

e

3.8 kX

5.0V

5.0 mA;

100 mV

51.6X

http://www.national.com13

Physical Dimensions inches (millimeters) unless otherwise noted

for RF Personal Communications

LMX2301 PLLatinum 160 MHz Frequency Synthesizer

20-Lead (0.173

For Tape and Reel Order Number LMX2301TMX (2500 Units per Reel)

LIFE SUPPORT POLICY

NATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL

SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or 2. A critical component is any component of a life

systems which, (a) are intended for surgical implant support device or system whose failure to perform can

into the body, or (b) support or sustain life, and whose be reasonably expected to cause the failure of the life

failure to perform, when properly used in accordance support device or system, or to affect its safety or

with instructions for use provided in the labeling, can effectiveness.

be reasonably expected to result in a significant injury

to the user.

National Semiconductor National Semiconductor National Semiconductor National Semiconductor

Corporation Europe Southeast Asia Japan Ltd.

Americas

Tel: 1(800) 272-9959

Fax: 1(800) 737-7018

Email: support

http://www.national.com

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

@

nsc.com

Deutsch Tel:

English Tel:

Fran3ais Tel:

Italiano Tel:

NS Package Number MTC20

Wide) Thin Shrink Small Outline Package (TM)

×

Order Number LMX2301TM

a

Fax:

49 (0) 180-530 85 86 Fax: (852) 2376 3901 Tel: 81-3-5620-7561

@

Email: europe.support

a

49 (0) 180-530 85 85

a

49 (0) 180-532 78 32

a

49 (0) 180-532 93 58

a

49 (0) 180-534 16 80

nsc.com Email: sea.support@nsc.com Fax: 81-3-5620-6179

Loading...

Loading...