LMD18201

3A, 55V H-Bridge

General Description

The LMD18201 is a 3A H-Bridge designed for motion control

applications. The device is built using a multi-technology

process which combines bipolar and CMOS control circuitry

with DMOS power devices on the same monolithic structure.

The H-Bridge configuration is ideal for driving DC and stepper motors. The LMD18201 accommodates peak output

currents up to 6A. Current sensing can be achieved via a

small sense resistor connected in series with the power

ground lead. For current sensing without disturbing the path

of current to the load, the LMD18200 is recommended.

Features

n Delivers up to 3A continuous output

n Operates at supply voltages up to 55V

n Low R

typically 0.33Ω per switch

DS(ON)

LMD18201 3A, 55V H-Bridge

October 2000

n TTL and CMOS compatible inputs

n No “shoot-through” current

n Thermal warning flag output at 145˚C

n Thermal shutdown (outputs off) at 170˚C

n Internal clamp diodes

n Shorted load protection

n Internal charge pump with external bootstrap capability

Applications

n DC and stepper motor drives

n Position and velocity servomechanisms

n Factory automation robots

n Numerically controlled machinery

n Computer printers and plotters

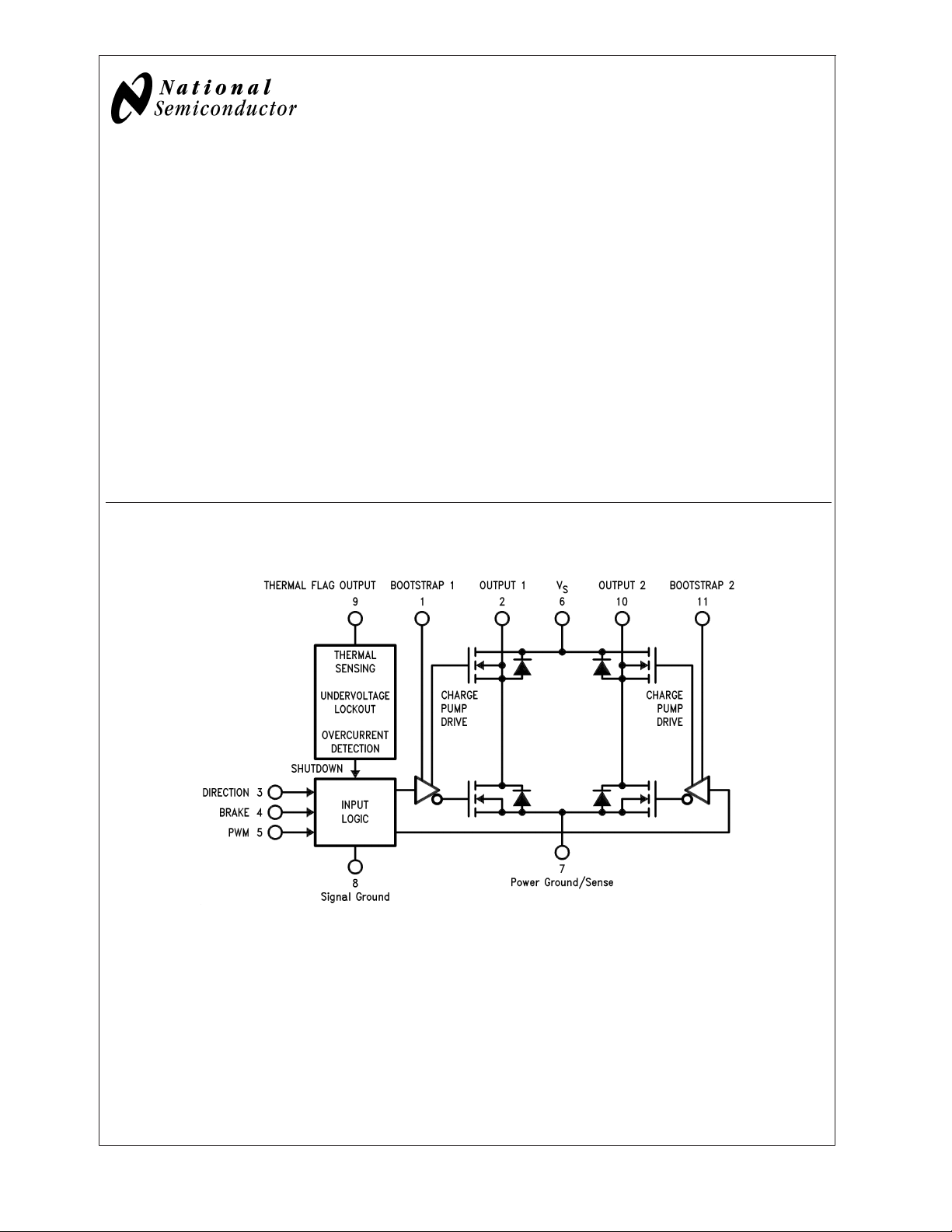

Functional Diagram

01079301

FIGURE 1. Functional Block Diagram of LMD18201

© 2004 National Semiconductor Corporation DS010793 www.national.com

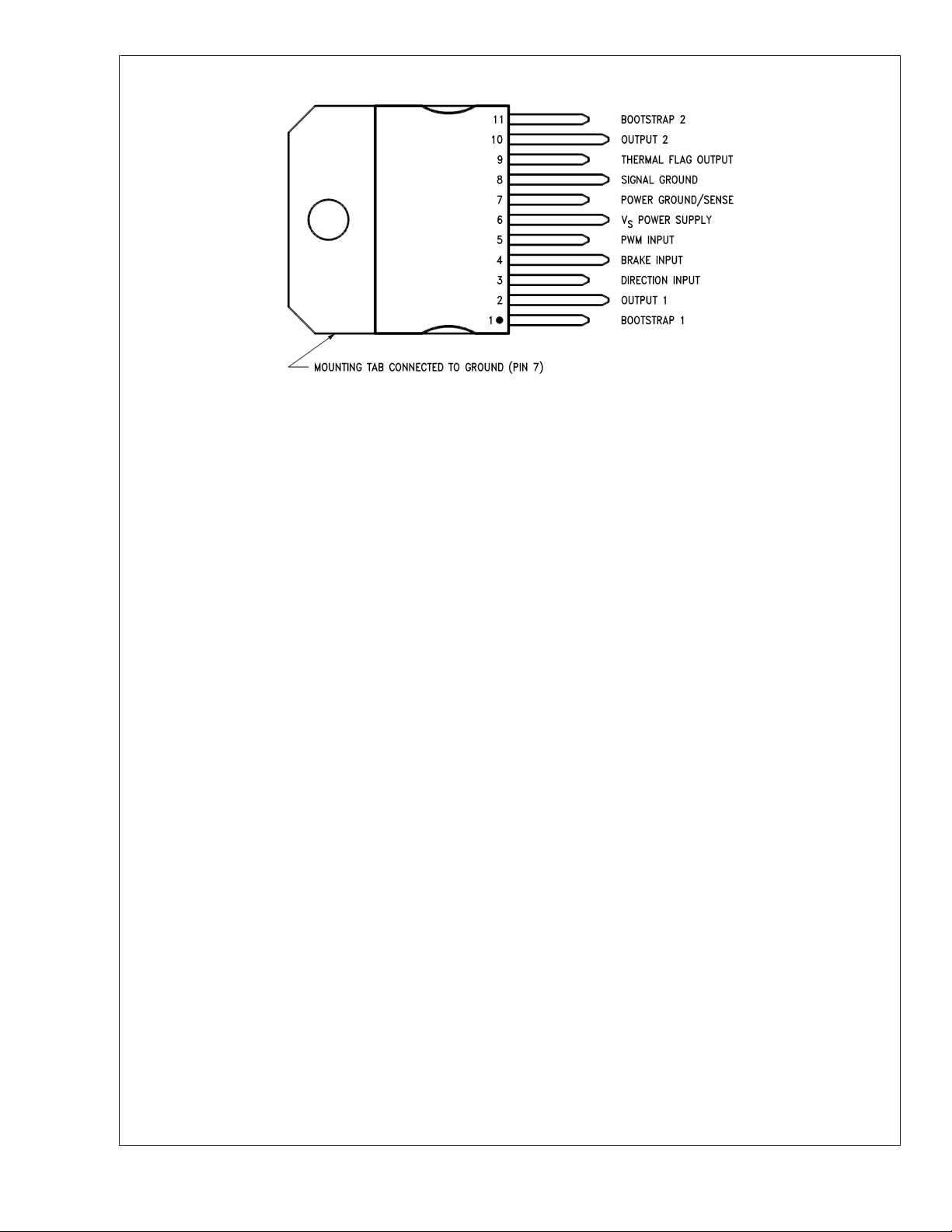

Connection Diagram and Ordering Information

LMD18201

Top View

Order Number LMD18201T

See NS Package Number TA11B

01079302

www.national.com 2

LMD18201

Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Total Supply Voltage (V

, Pin 6) 60V

S

Power Dissipation (T

Junction Temperature, T

= 25˚C, Free Air) 3W

A

J(max)

150˚C

ESD Susceptibility (Note 4) 1500V

Storage Temperature, T

STG

−40˚C to +150˚C

Lead Temperature (Soldering, 10 sec.) 300˚C

Voltage at Pins 3, 4, 5 and 9 12V

Voltage at Bootstrap Pins (Pins 1 and 11) V

OUT

+ 16V

Operating Ratings(Note 1)

Peak Output Current (200 ms) 6A

Continuous Output Current (Note 2) 3A

Power Dissipation (Note 3) 25W

Junction Temperature, T

V

Supply Voltage +12V to +55V

S

J

−40˚C to +125˚C

Sense Voltage (Pin 7 to Pin 8) +0.5V to −1.0V

Electrical Characteristics(Note 5)

The following specifications apply for VS= 42V, unless otherwise specified. Boldface limits apply over the entire operating

temperature range, −40˚C ≤ T

Symbol Parameter Conditions Typ Limit Units

R

R

V

V

I

IL

V

I

IL

DS(ON)

DS(ON)

CLAMP

IL

IH

Switch ON Resistance Output Current = 3A (Note 6) 0.33 0.4/0.6 Ω (max)

Switch ON Resistance Output Current = 6A (Note 6) 0.33 0.4/0.6 Ω (max)

Clamp Diode Forward Drop Clamp Current = 3A (Note 6) 1.2 1.5 V (max)

Logic Low Input Voltage Pins 3, 4, 5 −0.1 V (min)

Logic Low Input Current VIN= −0.1V, Pins = 3, 4, 5 −10 µA (max)

Logic High Input Voltage Pins 3, 4, 5 2 V (min)

Logic High Input Current VIN= 12V, Pins = 3, 4, 5 10 µA (max)

Undervoltage Lockout Outputs Turn OFF 9 V (min)

T

JW

V

F(ON)

I

F(OFF)

T

JSD

I

S

t

D(ON)

t

ON

t

D(OFF)

t

OFF

t

PW

t

CPR

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating

the device beyond its rated operating conditions.

Note 2: See Application Information for details regarding current limiting.

Note 3: The maximum power dissipation must be derated at elevated temperatures and is a function of T

dissipation at any temperature is P

junction to case (θ

Note 4: Human-body model, 100 pF discharged through a 1.5 kΩ resistor. Except Bootstrap pins (pins 1 and 11) which are protected to 1000V of ESD.

Note 5: All limits are 100% production tested at 25˚C. Temperature extreme limits are guaranteed via correlation using accepted SQC (Statistical Quality Control)

methods. All limits are used to calculate AOQL, (Average Outgoing Quality Level).

Note 6: Output currents are pulsed (t

Warning Flag Temperature Pin 9 ≤ 0.8V, IL= 2 mA 145 ˚C

Flag Output Saturation Voltage TJ=TJW,IL= 2 mA 0.15 V

Flag Output Leakage VF= 12V 0.2 10 µA (max)

Shutdown Temperature Outputs Turn OFF 170 ˚C

Quiescent Supply Current All Logic Inputs Low 13 25 mA (max)

Output Turn-On Delay Time Sourcing Outputs, I

Output Turn-On Switching Time Bootstrap Capacitor = 10 nF

Output Turn-Off Delay Times Sourcing Outputs, I

Output Turn-Off Switching Times Bootstrap Capacitor = 10 nF

Minimum Input Pulse Width Pins 3, 4 and 5 1 µs

Charge Pump Rise Time No Bootstrap Capacitor 20 µs

) is 1.0˚C/W and from junction to ambient (θJA) is 30˚C/W. For guaranteed operation T

JC

≤ +125˚C, all other limits are for TA=TJ= 25˚C.

J

Sinking Outputs, I

Sourcing Outputs, I

Sinking Outputs, I

Sinking Outputs, I

Sourcing Outputs, I

Sinking Outputs, I

=(T

D(max)

J(max)−TA

<

2 ms, Duty Cycle<5%).

W

)/θJA, or the number given in the Absolute Ratings, whichever is lower. The typical thermal resistance from

0.8 V (max)

12 V (max)

11 V (max)

= 3A 300 ns

OUT

= 3A 300 ns

OUT

= 3A 100 ns

OUT

=3A 80 ns

OUT

= 3A 200 ns

OUT

= 3A 200 ns

OUT

=3A 75 ns

OUT

=3A 70 ns

OUT

, θJA, and TA. The maximum allowable power

J(max)

= 125˚C.

J(max)

www.national.com3

Typical Performance Characteristics

V

vs Flag Current R

SAT

LMD18201

01079312 01079313

vs Temperature

DS(ON)

R

DS(ON)

vs

Supply Voltage

Supply Current vs

Frequency (V

S

= 42V)

01079314

Supply Current vs

Supply Voltage

01079315

Supply Current vs

Temperature (VS= 42V)

01079316

www.national.com 4

01079317

Test Circuit

01079308

Pin 5, PWM Input: See Table 1. How this input (and DIREC-

TION input, Pin 3) is used is determined by the format of the

PWM Signal.

Pin 6, V

Pin 7, POWER GROUND/SENSE Connection: This pin is

the ground return for the power DMOS transistors of the

H-Bridge. The current through the H-Bridge can be sensed

by adding a small, 0.1Ω, sense resistor from this pin to the

power supply ground.

Pin 8, SIGNAL GROUND: This is the ground return for the

internal logic circuitry used to control the PWM switching of

the H-Bridge.

Pin 9, THERMAL FLAG Output: This pin provides the

thermal warning flag output signal. Pin 9 becomes active-low

at 145˚C (junction temperature). However the chip will not

shut itself down until 170˚C is reached at the junction.

Pin 10, OUTPUT 2: Half H-Bridge number 2 output.

Pin 11, BOOTSTRAP 2 Input: Bootstrap capacitor pin for

half H-Bridge number 2. The recommended capacitor

(10 nF) is connected between pins 10 and 11.

Power Supply

S

LMD18201

Switching Time Definitions

01079309

Pinout Description (See Connection Dia-

gram)

Pin 1, BOOTSTRAP 1 Input: Bootstrap capacitor pin for half

H-Bridge number 1. The recommended capacitor (10 nF) is

connected between pins 1 and 2.

Pin 2, OUTPUT 1: Half H-Bridge number 1 output.

Pin 3, DIRECTION Input: See Table 1. This input controls

the direction of current flow between OUTPUT 1 and OUTPUT 2 (pins 2 and 10) and, therefore, the direction of rotation

of a motor load.

Pin 4, BRAKE Input: See Table 1. This input is used to

brake a motor by effectively shorting its terminals. When

braking is desired, this input is taken to a logic high level and

it is also necessary to apply logic high to PWM input, pin 5.

The drivers that short the motor are determined by the logic

level at the DIRECTION input (Pin 3): with Pin 3 logic high,

both current sourcing output transistors are ON; with Pin 3

logic low, both current sinking output transistors are ON. All

output transistors can be turned OFF by applying a logic high

to Pin 4 and a logic low to PWM input Pin 5; in this case only

a small bias current (approximately −1.5 mA) exists at each

output pin.

TABLE 1. Logic Truth Table

PWM Dir Brake Active Output Drivers

H H L Source 1, Sink 2

H L L Sink 1, Source 2

L X L Source 1, Source 2

H H H Source 1, Source 2

H L H Sink 1, Sink 2

L X H NONE

Application Information

TYPES OF PWM SIGNALS

The LMD18201 readily interfaces with different forms of

PWM signals. Use of the part with two of the more popular

forms of PWM is described in the following paragraphs.

Simple, locked anti-phase PWM consists of a single, variable duty-cycle signal in which is encoded both direction and

amplitude information (see Figure 2). A 50% duty-cycle

PWM signal represents zero drive, since the net value of

voltage (integrated over one period) delivered to the load is

zero. For the LMD18201, the PWM signal drives the direction input (pin 3) and the PWM input (pin 5) is tied to logic

high.

01079304

FIGURE 2. Locked Anti-Phase PWM Control

www.national.com5

Application Information (Continued)

Sign/magnitude PWM consists of separate direction (sign)

and amplitude (magnitude) signals (see Figure 3). The (ab-

LMD18201

solute) magnitude signal is duty-cycle modulated, and the

FIGURE 3. Sign/Magnitude PWM Control

absence of a pulse signal (a continuous logic low level)

represents zero drive. Current delivered to the load is proportional to pulse width. For the LMD18201, the DIRECTION

input (pin 3) is driven by the sign signal and the PWM input

(pin 5) is driven by the magnitude signal.

01079305

FIGURE 4. Transitions in Brake, Direction, or PWM Must be Separated by At Least 1 µsec

SIGNAL TRANSITION REQUIREMENTS

To ensure proper internal logic performance, it is good practice to avoid aligning the falling and rising edges of input

signals. A delay of at least 1 µsec should be incorporated

between transitions of the Direction, Brake, and/or PWM

input signals. A conservative approach is be sure there is at

least 500ns delay between the end of the first transition and

the beginning of the second transition. See Figure 4.

USING THE THERMAL WARNING FLAG

The THERMAL FLAG output (pin 9) is an open collector

transistor. This permits a wired OR connection of thermal

warning flag outputs from multiple LMD18201’s, and allows

the user to set the logic high level of the output signal swing

to match system requirements. This output typically drives

www.national.com 6

01079324

the interrupt input of a system controller. The interrupt service routine would then be designed to take appropriate

steps, such as reducing load currents or initiating an orderly

system shutdown. The maximum voltage compliance on the

flag pin is 12V.

SUPPLY BYPASSING

During switching transitions the levels of fast current

changes experienced may cause troublesome voltage transients across system stray inductances.

It is normally necessary to bypass the supply rail with a high

quality capacitor(s) connected as close as possible to the V

Power Supply (Pin 6) and POWER GROUND (Pin 7). A 1 µF

high-frequency ceramic capacitor is recommended. Care

should be taken to limit the transients on the supply pin

S

Application Information (Continued)

below the Absolute Maximum Rating of the device. When

operating the chip at supply voltages above 40V a voltage

suppressor (transorb) such as P6KE62A is recommended

from supply to ground. Typically the ceramic capacitor can

be eliminated in the presence of the voltage suppressor.

Note that when driving high load currents a greater amount

of supply bypass capacitance (in general at least 100 µF per

Amp of load current) is required to absorb the recirculating

currents of the inductive loads.

CURRENT LIMITING

Current limiting protection circuitry has been incorporated

into the design of the LMD18201. With any power device it is

important to consider the effects of the substantial surge

currents through the device that may occur as a result of

shorted loads. The protection circuitry monitors the current

through the upper transistors and shuts off the power device

as quickly as possible in the event of an overload condition

(the threshold is set to approximately 10A). In a typical motor

driving application the most common overload faults are

caused by shorted motor windings and locked rotors. Under

these conditions the inductance of the motor (as well as any

series inductance in the V

the magnitude of a current surge to a safe level for the

LMD18201. Once the device is shut down, the control circuitry will periodically try to turn the power device back on.

This feature allows the immediate return to normal operation

once the fault condition has been removed. While the fault

remains however, the device will cycle in and out of thermal

shutdown. This can create voltage transients on the V

supply line and therefore proper supply bypassing techniques are required.

The most severe condition for any power device is a direct,

hard-wired (“screwdriver”) long term short from an output to

ground. This condition can generate a surge of current

through the power device on the order of 15 Amps and

require the die and package to dissipate up to 500W of

power for the short time required for the protection circuitry

to shut off the power device. This energy can be destructive,

particularly at higher operating voltages (

precautions are in order. Proper heat sink design is essential

and it is normally necessary to heat sink the V

(pin 6) with 1 square inch of copper on the PC board.

supply line) serves to reduce

CC

>

30V) so some

supply pin

CC

CC

LMD18201

01079306

FIGURE 5. Internal Charge Pump Circuitry

For higher switching frequencies, the LMD18201 provides

for the use of external bootstrap capacitors. The bootstrap

principle is in essence a second charge pump whereby a

large value capacitor is used which has enough energy to

quickly charge the parasitic gate input capacitance of the

power device resulting in much faster rise times. The switching action is accomplished by the power switches themselves (Figure 6). External 10 nF capacitors, connected from

the outputs to the bootstrap pins of each high-side switch

provide typically less than 100 ns rise times allowing switching frequencies up to 500 kHz.

INTERNAL CHARGE PUMP AND USE OF BOOTSTRAP CAPACITORS

To turn on the high-side (sourcing) DMOS power devices,

the gate of each device must be driven approximately 8V

more positive than the supply voltage. To achieve this an

internal charge pump is used to provide the gate drive voltage. As shown in (Figure 5), an internal capacitor is alternately switched to ground and charged to about 14V, then

switched to V

than V

S

thereby providing a gate drive voltage greater

S

. This switching action is controlled by a continuously

running internal 300 kHz oscillator. The rise time of this drive

voltage is typically 20 µs which is suitable for operating

frequencies up to 1 kHz.

01079307

FIGURE 6. Bootstrap Circuitry

INTERNAL PROTECTION DIODES

A major consideration when switching current through inductive loads is protection of the switching power devices from

the large voltage transients that occur. Each of the four

switches in the LMD18201 have a built-in protection diode to

clamp transient voltages exceeding the positive supply or

ground to a safe diode voltage drop across the switch.

The reverse recovery characteristics of these diodes, once

the transient has subsided, is important. These diodes must

come out of conduction quickly and the power switches must

be able to conduct the additional reverse recovery current of

the diodes. The reverse recovery time of the diodes protecting the sourcing power devices is typically only 70 ns with a

www.national.com7

Application Information (Continued)

reverse recovery current of 1A when tested with a full 3A of

forward current through the diode. For the sinking devices

LMD18201

the recovery time is typically 100 ns with 4A of reverse

current under the same conditions.

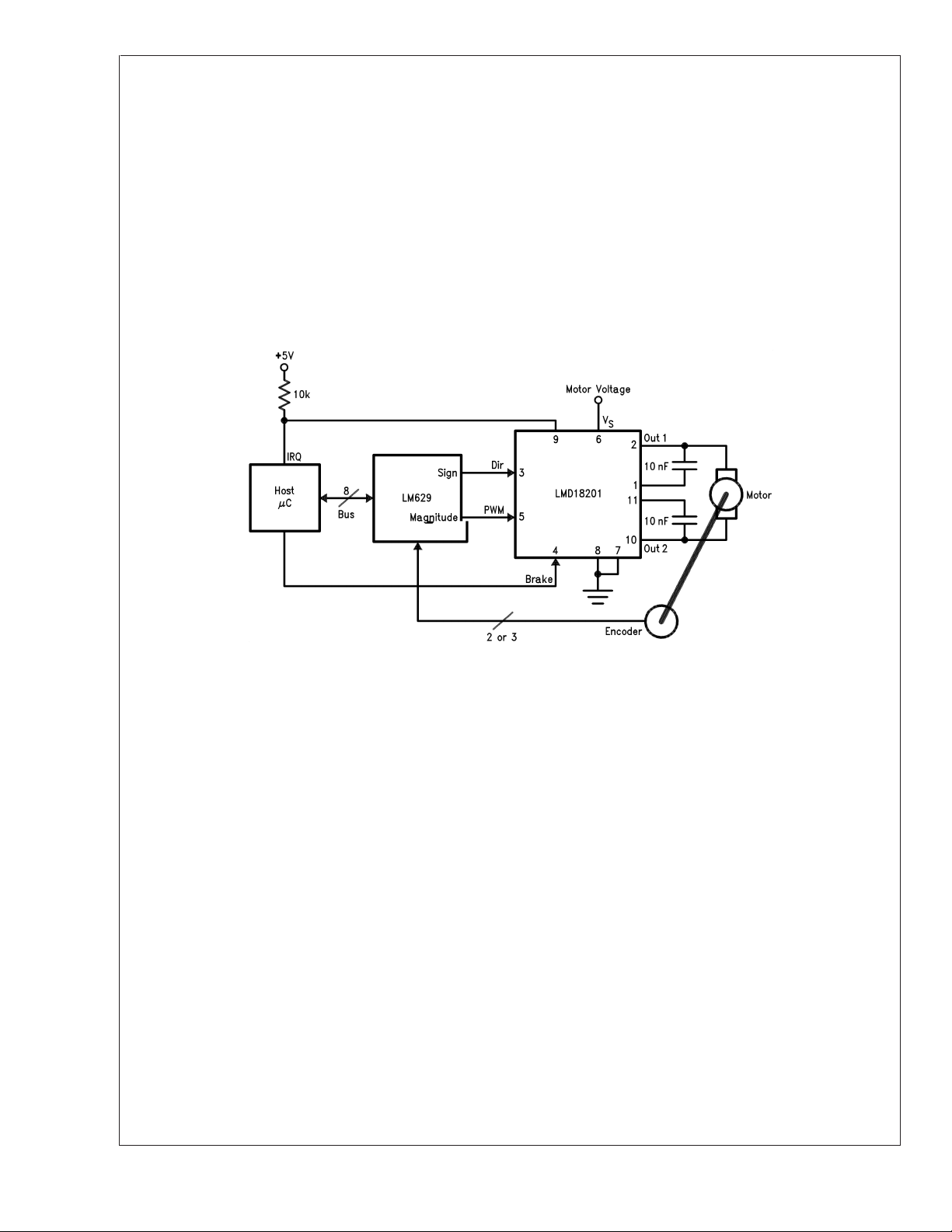

Typical Applications

BASIC MOTOR DRIVER

The LMD18201 can directly interface to any Sign/Magnitude

PWM controller. The LM629 is a motion control processor

that outputs a Sign/Magnitude PWM signal to coordinate

either positional or velocity control of DC motors. The

LMD18201 provides fully protected motor driver stage.

FIGURE 7. Basic Motor Driver

CURRENT SENSING

In many motor control applications it is desirable to sense

and control the current through the motor. For these types of

applications a companion product, the LMD18200, is also

available. The LMD18200 is identical to the LMD18201 but

has current sensing transistors that output a current directly

proportional to the current conducted by the two upper

DMOS power devices to a separate current sense pin. This

technique does not require a low valued, power sense resistor and does not subtract from the available voltage drive to

the motor.

To sense the bridge current through the LMD18201 requires

the addition of a small sense resistor between the power

ground/sense pin (Pin 7) and the actual circuit ground (see

Figure 8). This resistor should have a value of 0.1Ω or less to

01079310

stay within the allowable voltage compliance of the sense

pin, particularly at higher operating current levels. The voltage between power ground/sense (Pin 7) and the signal

ground (Pin 8) must stay within the range of −1V to +0.5V.

Internally there is approximately 25Ω between pins 7 and 8

and this resistance will slightly reduce the value of the external sense resistor. Approximately 70% of the quiescent

supply current (10 mA) flows out of pin 7. This will cause a

slight offset to the voltage across the sense resistor when

the bridge is not conducting. During reverse recovery of the

internal protection diodes the voltage compliance between

pins 7 and 8 may be exceeded. The duration of these spikes

however are only approximately 100 ns and do not have

enough time or energy to disrupt the operation of the

LMD18201.

www.national.com 8

Typical Applications (Continued)

LMD18201

01079311

FIGURE 8. Current Sensing

www.national.com9

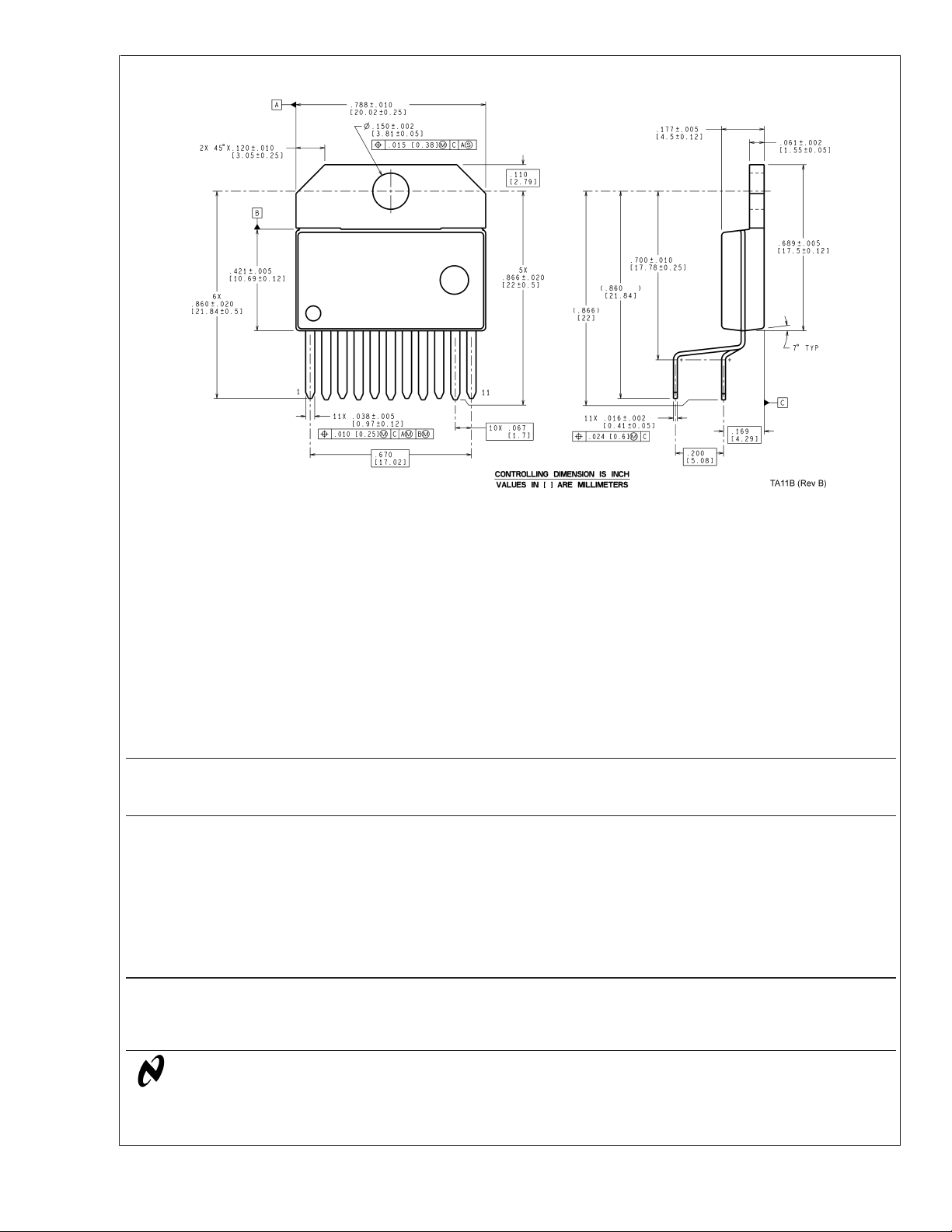

Physical Dimensions inches (millimeters) unless otherwise noted

LMD18201 3A, 55V H-Bridge

11-Lead TO-220 Power Package (T)

Order Number LMD18201T

NS Package Number TA11B

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves

the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

LIFE SUPPORT POLICY

NATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS

WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR

CORPORATION. As used herein:

1. Life support devices or systems are devices or systems

which, (a) are intended for surgical implant into the body, or

(b) support or sustain life, and whose failure to perform when

properly used in accordance with instructions for use

2. A critical component is any component of a life support

device or system whose failure to perform can be reasonably

expected to cause the failure of the life support device or

system, or to affect its safety or effectiveness.

provided in the labeling, can be reasonably expected to result

in a significant injury to the user.

BANNED SUBSTANCE COMPLIANCE

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship

Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no ‘‘Banned

Substances’’ as defined in CSP-9-111S2.

National Semiconductor

Americas Customer

Support Center

Email: new.feedback@nsc.com

Tel: 1-800-272-9959

www.national.com

National Semiconductor

Europe Customer Support Center

Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor

Asia Pacific Customer

Support Center

Email: ap.support@nsc.com

National Semiconductor

Japan Customer Support Center

Fax: 81-3-5639-7507

Email: jpn.feedback@nsc.com

Tel: 81-3-5639-7560

Loading...

Loading...