查询LM40供应商

LM40

Hardware Monitor with Dual Thermal Diodes and

LM40 Hardware Monitor with Dual Thermal Diodes and SensorPath

May 2004

SensorPath

™

Bus

General Description

The LM40 is a hardware monitor that measures 3 temperature zones, 5 voltages and has a single-wire interface compatible with National Semiconductor’s SensorPath bus. SensorPath data is pulse width encoded, thereby allowing the

LM40 to be easily connected to many general purpose

micro-controllers. Several National Semiconductor Super I/O

products include a fully integrated SensorPath master, that

when connected to the LM40 can realize a hardware monitor

function that includes limit checking for measured values,

autonomous fan speed control and many other functions.

The LM40 measures the temperature of its own die as well

as two external devices such as a processor thermal diode

or a diode connected transistor. The LM40 can resolve temperatures up to 255˚C and down to -256˚C. The operating

temperature range of the LM40 is 0˚C to +125˚C. Using Σ∆

ADC it measures +1.2V, +2.5V, +3.3V, +5V and +12V analog

input voltages with internal scaling resistors.The address

programming pin allows two LM40s to be placed on one

SensorPath bus.

Features

n SensorPath Interface

— 2 hardware programmable addresses

n Voltage Monitoring

— 9-bit Σ∆ ADC

— Internal scaling resistors for all inputs

— Monitors +1.2V, +2.5 V, +3.3 V, +5 V and +12 V

n Temperature Sensing

— 2 remote diode temperature sensor zones

— Internal local temperature zone

— 0.5 ˚C resolution

— Measures temperatures up to 140 ˚C

n 14-lead TSSOP package

Key Specifications

n Voltage Measurement Accuracy

n Temperature Sensor Accuracy

n Temperature Range:

— LM40 junction 0 ˚C to +85 ˚C

— Remote Temp Accuracy 0 ˚C to +100 ˚C

n Power Supply Voltage +3.0 V to +3.6 V

n Average Power Supply Current 0.5 mA (typ)

n Conversion Time (all Channels) 29.6ms to 1456ms

±

2 % (max)

±

3 ˚C (max)

Applications

n Microprocessor based equipment

(Motherboards, Video Cards, Base-stations, Routers,

ATMs, Point of Sale, …)

n Power Supplies

Typical Application

20068401

SensorPath™is a trademark of National Semiconductor Corporation

© 2004 National Semiconductor Corporation DS200684 www.national.com

™

Bus

Connection Diagram

LM40

TSSOP-14

Order

Number

LM40CIMT LM40

LM40CIMTX LM40

Package

Marking

CIMT

CIMT

NS

Package

Number

MTC14C 94 units per

MTC14C 2500 units in

Transport

Media

rail

tape and reel

Top View

National Package Number MTC14C

20068402

Pin Description

Pin Number Pin Name Description Typical Connection

1, 14 NC No Connect May be tied to V+, GND or left floating

2 GND Ground System ground

3 V+/+3.3V_SBY Positive power supply pin as well

as a +3.3V voltage monitor

4 SWD SensorPath Bus line; Open-drain

output

5 ADD Digital input - device number select

input for the serial bus device

number

6 +1.2V +1.2V voltage monitoring input with

scaling resistors

7 +2.5V +2.5V voltage monitoring input with

scaling resistors

8, 10 D1-, D2- Thermal diode analog voltage

output and negative monitoring

input

9, 11 D1+, D2+ Thermal diode analog current

output and positive monitoring input

12 +5V +5V voltage monitoring input with

scaling resistors

13 +12V +12V voltage monitoring input with

scaling resistors

Connected system 3.3 V standby power and

to a 0.1 µF bypass capacitor in parallel with

100 pF. A bulk capacitance of approximately

10 µF needs to be in the near vicinity of the

LM40.

Super I/O, Pull-up resistor, 1.6k

Pull-up to 3.3 V or pull-down to GND resistor,

10k; must never be left floating

Processor core voltage to be monitored

Power supply voltage to be monitored

Remote Thermal Diode cathode

(THERM_DC) - Diode 1 should always be

connected to the processor thermal diode.

Diode 2 may be connected to an MMBT3904

or GPU thermal diode. A 100 pF capacitor

should be connected between respective Dand D+ for noise filtering.

Remote Thermal Diode anode (THERM_DA) Diode 1 should always be connected to the

processor thermal diode. Diode 2 may be

connected to an MMBT3904 or GPU thermal

diode. A 100 pF capacitor should be

connected between respective D- and D+ for

noise filtering.

Power supply voltage to be monitored

Power supply voltage to be monitored

www.national.com 2

Block Diagram

LM40

20068403

www.national.com3

Absolute Maximum Ratings

LM40

(Notes 2, 1)

Supply Voltage (V

+

) −0.5 V to 6.0 V

Voltage at Any Digital Input or

Output Pin −0.5 V to 6.0 V

Voltage on 12V Analog Input −0.5 V to 16 V

Voltage on 5V Analog Input −0.5 V to 6.67 V

Voltage on D1+ and D2+ −0.5 V to (V+ + 0.05 V)

Voltage on Other Analog Inputs −0.5 V to 6.0 V

Current on D1- and D2-

Input Current per Pin(Note 3)

Package Input Current (Note 3)

Package Power Dissipation (Note 4)

Output Sink Current 10 mA

±

1mA

±

5mA

±

30 mA

Soldering process must comply with National’s reflow

temperature profile specifications. Refer to

www.national.com/packaging/. (Note 6)

Operating Ratings

(Notes 1, 2)

Temperature Range for Electrical Characteristics

LM40CIMT (T

MIN≤TA≤TMAX

Operating Temperature Range 0˚C ≤ T

Remote Diode Temperature (T

Range -5 ˚C ≤T

Supply Voltage Range (V+) +3.0 V to +3.6 V

Analog Input Voltage Rage:

+1.2V and +2.5V −0.05V to

) 0˚C ≤ TA≤ +85˚C

)

D

ESD Susceptibility (Note 5)

Human Body Model 2500 V

Machine Model 250 V

Storage Temperature −65˚C to +150˚C

+3.3V_SBY (V+) +3.0V to +3.6V

+5V −0.05V to +6.67V

+12V −0.05V to +16V

DC Electrical Characteristics

The following specifications apply for V+ = +3.0 VDCto +3.6 VDC, and all analog source impedance RS=50Ω unless other-

wise specified in the conditions. Boldface limits apply for LM40CIMT T

= +25˚C. TAis the ambient temperature of the LM40; TJis the junction temperature of the LM40; TDis the junction tem-

T

A

A=TJ=TMIN

=0˚C to T

perature of the remote thermal diode.

=85˚C; all other limits

MAX

≤ +125˚C

A

≤+140 ˚C

D

(V+ + 0.05V)

POWER SUPPLY CHARACTERISTICS

Symbol Parameter Conditions

V+ Power Supply Voltage 3.3

I+

Shutdown

Shutdown Power Supply Current

SensorPath Bus Inactive

(Note 9)

Typical

(Note 7)

260 420 µA (max)

Limits

(Note 8)

3.0

3.6

Units

(Limit)

V (min)

V (max)

SensorPath Bus Inactive; all

I+

Average

I+

Peak

Average Power Supply Current

Peak Power Supply Current

Power-On Reset Threshold Voltage

sensors enabled;

=182 ms; (Note 9)

t

CONV

SensorPath Bus Inactive

(Note 9)

900 µA (max)

3.3 mA (max)

1.6 V (min)

2.8 V (max)

TEMPERATURE-TO-DIGITAL CONVERTER CHARACTERISTICS

Parameter Conditions

Temperature Accuracy Using the Remote Thermal

Diode, see (Note 12) for Thermal Diode Processor

Type.

Temperature Accuracy Using the Local Diode T

T

J

= 0˚C to

TD= +25˚C

+85˚C

T

= 0˚C to

J

+85˚C

TJ = 0˚C to

+85˚C

= 0˚C to +85˚C (Note 10)

J

TD= 0˚C to

+100˚C

T

+125˚C

= +100˚C to

D

Typical

(Note 7)

±

1

±

1

Limits

(Note 8)

±

2.5 ˚C (max)

±

3 ˚C (max)

±

4 ˚C (max)

±

3 ˚C (max)

Units

(Limits)

Remote Diode and Local Temperature Resolution 10 Bits

0.5 ˚C

D− Source Voltage 0.7 V

www.national.com 4

TEMPERATURE-TO-DIGITAL CONVERTER CHARACTERISTICS

Parameter Conditions

Diode Source Current

Diode Source Current High Current to Low Current

Ratio

Typical

(Note 7)

(V

D+−VD−

) = +0.65 V; High Current 188 280 µA (max)

Low Current 11.75 µA

16

Limits

(Note 8)

Units

(Limits)

ANALOG TO DIGITAL CONVERTER CHARACTERISTICS

Symbol Parameter Conditions Typical

(Note 7)

TUE Total Unadjusted Error(Note 11)

Limits

(Note 8)

±

2 %FS

Units

(Limit)

(max)

Resolution 9 Bits

DNL Differential Non-linearity 1 LSB

Power Supply Sensitivity

Input Resistance, all analog inputs (total resistance

of divider chain)

±

1 %/V

210 140 kΩ (min)

400 kΩ (max)

SWD and ADD DIGITAL INPUT CHARACTERISTICS

Symbol Parameter Conditions

V

IH

SWD Logical High Input Voltage 2.1 V (min)

Typical

(Note 7)

Limits

(Note 8)

Units

(Limit)

V+ + 0.5 V (max)

V

IL

SWD Logical Low Input Voltage 0.8 V (max)

-0.5 V (min)

V

V

IH

V

IL

HYST

I

L

ADD Logical High Input Voltage 90%xV+ V (min)

ADD Logical Low Input Voltage 10%xV+ V (max)

Input Hysteresis 300 mV

SWD and ADD Input Current GND ≤ VIN≤ V+

SWD Input Current with V+ Open or

Grounded

GND ≤ V

≤ 3.6V,

IN

and V+ Open or

±

0.005

±

0.005 µA

±

10 µA (max)

GND

C

IN

Digital Input Capacitance 10 pF

SWD DIGITAL OUTPUT CHARACTERISTICS

Symbol Parameter Conditions

V

OL

Open-drain Output Logic “Low”

Voltage

I

OH

C

OUT

Open-drain Output Off Current

Digital Output Capacitance 10 pF

IOL= 4mA 0.4 V (max)

I

= 50µA 0.2 V (max)

OL

Typical

(Note 7)

±

0.005

Limits

(Note 8)

±

10 µA (max)

Units

(Limit)

LM40

AC Electrical Characteristics

The following specification apply for V+ = +3.0 VDCto +3.6 VDC, unless otherwise specified. Boldface limits apply for

T

A=TJ=TMIN

=0˚C to T

specification revision 0.98. Please refer to that speciation for further details.

Symbol Parameter Conditions

HARDWARE MONITOR CHARACTERISTICS

t

CONV

Total Monitoring Cycle Time (Note 13) All Voltage and

SensorPath Bus CHARACTERISTICS

t

f

SWD fall time (Note 16) R

=85˚C; all other limits TA=TJ= 25˚C. The SensorPath Characteristics conform to the SensorPath

MAX

Typical

(Note 7)

Limits

(Note 8)

182 163.8 ms (min)

Temperature readings

(Default)

=1.25 kΩ±30%,

pull-up

=400 pF

C

L

200.2 ms (max)

300 ns (max)

Units

(Limits)

www.national.com5

AC Electrical Characteristics (Continued)

LM40

The following specification apply for V+ = +3.0 VDCto +3.6 VDC, unless otherwise specified. Boldface limits apply for

T

A=TJ=TMIN

=0˚C to T

=85˚C; all other limits TA=TJ= 25˚C. The SensorPath Characteristics conform to the SensorPath

MAX

specification revision 0.98. Please refer to that speciation for further details.

Typical

Symbol Parameter Conditions

t

INACT

t

r

SWD rise time (Note 16) R

Minimum inactive time (bus at high level)

=1.25 kΩ±30%,

pull-up

=400 pF

C

L

(Note 7)

guaranteed by the slave before an attention

request

t

Mtr0

Master drive for Data Bit 0 write and for Data

Bit 0-1read

t

Mtr1

t

SFEdet

t

SLout1

t

MtrS

t

SLoutA

t

RST

t

RST_MAX

Master drive for Data Bit 1 write 35.4 µs (min)

Time allowed for LM40 activity detection 9.6 µs (max)

LM40 drive for Data Bit 1 read by master 28.3 µs (min)

Master drive for Start Bit 80 µs (min)

LM40 drive for Attention Request 165 µs (min)

Master or LM40 drive for Reset 354 µs (min)

Maximum drive of SWD by an LM40, after the

power supply is raised above 3V

Limits

(Note 8)

Units

(Limits)

1000 ns (max)

11 µs (min)

11.8 µs (min)

17.0 µs (max)

48.9 µs (max)

38.3 µs (max)

109 µs (max)

228 µs (max)

500 ms (max)

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is

functional, but do not guarantee performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed

specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test

conditions.

Note 2: All voltages are measured with respect to GND, unless otherwise noted.

Note 3: When the input voltage (V

components and/or ESD protection circuitry are shown below for the LM40’s pins. The nominal breakdown voltage of the zener is 6.5 V. SNP stands for snap-back

device.

) at any pin exceeds the power supplies (V

IN

IN

<

GND or V

>

V+), the current at that pin should be limited to 5 mA. Parasitic

IN

www.national.com 6

LM40

PIN#Pin

Name

Pin

Circuit

1NC A

2 GND B

V+/

3

3.3V SB

B

4 SWD A

5 ADD A

6 +1.2V C

7 +2.5V C

8 D1- D

9 D1+ E

10 D2- D

11 D2+ E

12 +5V C

13 +12V C

Circuit A

Circuit C

All Input Structure Circuits

Circuit B

Circuit D

14 NC A

Note 4: Thermal resistance junction-to-ambient in still air when attached to a printed circuit board with 1 oz. foil is 148 ˚C/W.

Note 5: Human body model, 100 pF discharged through a 1.5 kΩ resistor. Machine model, 200 pF discharged directly into each pin.

Note 6: Reflow temperature profiles are different for lead-free and non lead-free packages.

Note 7: “Typicals” are at T

Note 8: Limits are guaranteed to National’s AOQL (Average Outgoing Quality Level).

Note 9: The supply current will not increase substantially with a SensorPath transaction.

Note 10: Local temperature accuracy does not include the effects of self-heating. The rise in temperature due to self-heating is the product of the internal power

dissipation of the LM40 and the thermal resistance. See (Note 4) for the thermal resistance to be used in the self-heating calculation.

Note 11: TUE , total unadjusted error, includesADC gain, offset, linearity and reference errors. TUE is defined as the "actual Vin" to achieve a given code transition

minus the "theoretical Vin" for the same code. Therefore, a positive error indicates that the input voltage is greater than the theoretical input voltage for a given code.

If the theoretical input voltage was applied to an LM40 that has positive error, the LM40’s reading would be less than the theoretical.

Note 12: The accuracy of the LM40CIMT is guaranteed when using the thermal diode of an Intel 90 nm Pentium 4 processor or any thermal diode with a non-ideality

factor of 1.011 and series resistance of 3.33Ω. When using a MMBT3904 type transistor as a thermal diode the error band will be typically shifted by -4.5 ˚C.

Note 13: This specification is provided only to indicate how often temperature and voltage data are updated.

Note 14: The output fall time is measured from (V

Note 15: The output rise time is measured from (V

Note 16: The rise and fall times are not tested but guaranteed by design.

= 25˚C and represent most likely parametric norm. They are to be used as general reference values not for critical design calculations.

A

IH min

IL max

)to(V

)to(V

IL max

IH min

).

).

Circuit E

www.national.com7

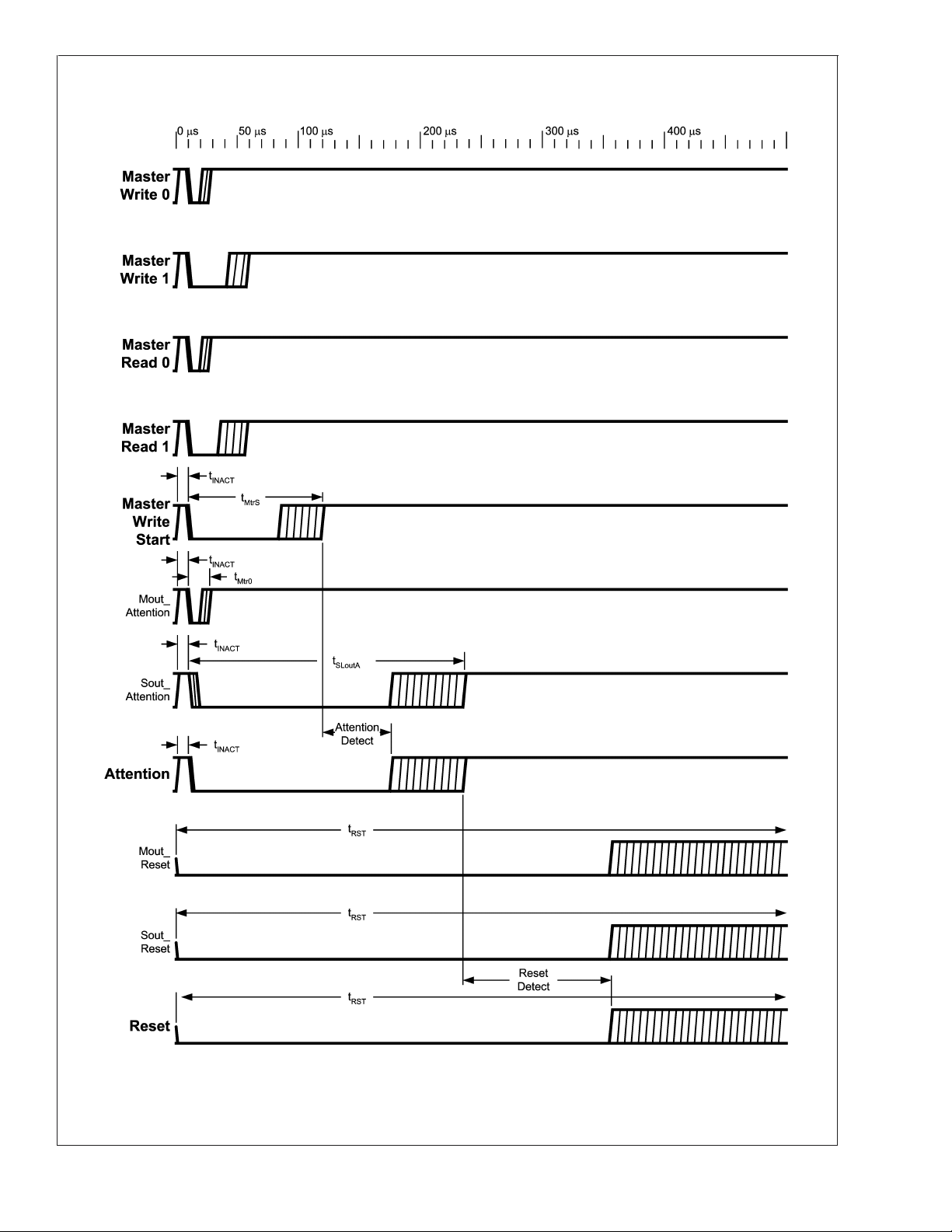

Timing Diagrams

LM40

20068404

FIGURE 1. Timing for Data Bits 0, 1 and Start Bit. See Section 1.2 "SensorPath BIT SIGNALING" for further details.

www.national.com 8

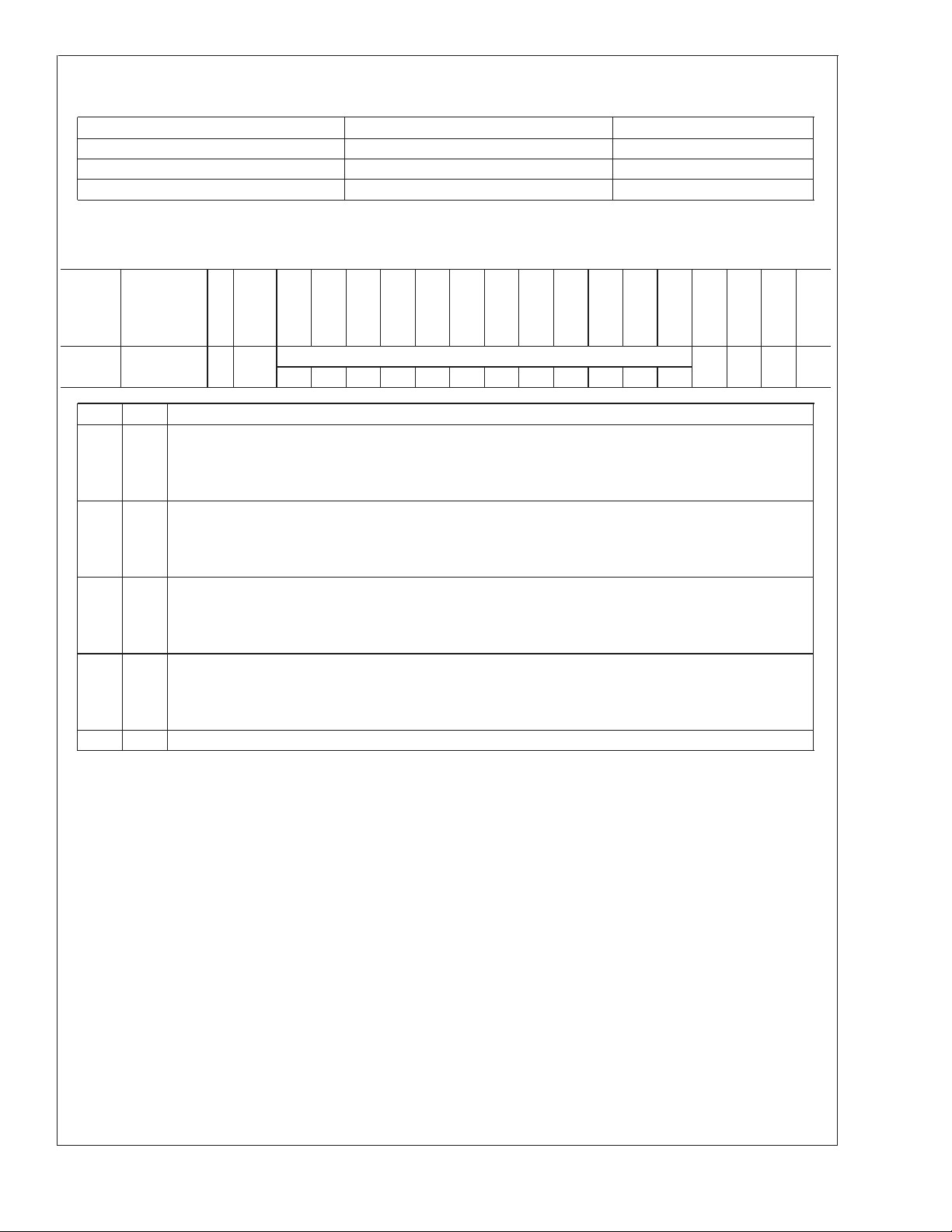

Timing Diagrams (Continued)

LM40

20068405

FIGURE 2. Timing for Attention Request and Reset. See Section 1.2 "SensorPath BIT SIGNALING" for further details.

www.national.com9

Typical Performance Characteristics

LM40

Remote Diode Temperature Reading Sensitivity to Diode

Filter Capacitance

1.0 Functional Description

The LM40 hardware monitor measures up to 3 temperature

zones and 5 power supply voltages. The LM40 uses a ∆V

temperature sensing method. A differential voltage, representing temperature, is digitized using a Sigma-Delta analog

to digital converter. Internal scaling resistors allow direct

measurement of the +1.6V, +2.5V, +5V, +3.3V and +12V

power supply inputs. The digitized data can be retrieved over

a simple single-wire interface called SensorPath. SensorPath has been defined by National Semiconductor and is

optimized for hardware monitoring. National offers a royaltyfree license in connection with its intellectual property rights

in the SensorPath bus.

The LM40 has one address pin to allow up to two LM40s to

be connected to one SensorPath bus. The physical interface

of SensorPath’s SWD signal is identical to the familiar industry standard SMBus SMBDAT signal. The digital information

is encoded in the pulse width of the signal being transmitted.

Every bit can be synchronized by the master simplifying the

implementation of the master when using a micro-controller.

For micro-controller’s with greater functionality an asynchronous attention signal can be transmitted by the LM40 to

interrupt the micro-controller and notify it that temperature/

voltage data has been updated in the readout registers.

To optimize the LM40’s power consumption to the system

requirements, the LM40 has a shutdown mode and supports

multiple conversion rates.

1.1 SensorPath BUS SWD

SWD is the Single Wire Data line used for communication.

SensorPath uses 3.3V single-ended signaling, with a pull-up

resistor and open-drain low-side drive (see Figure 3). For

timing purposes SensorPath is designed for capacitive loads

) of up to 400pF. Note that in many cases a 3.3V standby

(C

L

rail of the PC will be used as a power supply for both the

sensor and the master. Logic high and low voltage levels for

SWD are TTL compatible. The master may provide an internal pull-up resistor. In this case the external resistor is not

needed. The minimum value of the pull-up resistor must take

into account the maximum allowable output load current of

4mA.

Thermal Diode Capacitor or PCB Leakage Current Effect

on Remote Diode Temperature Reading

20068421 20068422

be

FIGURE 3. SensorPath SWD simplified schematic

1.2 SensorPath BIT SIGNALING

Signals are transmitted over SensorPath using pulse-width

encoding. There are five types of "bit signals":

Data Bit 0

•

Data Bit 1

•

Start Bit

•

Attention Request

•

Reset

•

All the "bit signals" involve driving the bus to a low level. The

duration of the low level differentiates between the different

"bit-signals". Each "bit signal" has a fixed pulse width. SensorPath supports a Bus Reset Operation and Clock Training

sequence that allows the slave device to synchronize its

internal clock rate to the master. Since the LM40 meets the

±

15% timing requirements of SensorPath, the LM40 does

not require the Clock Training sequence and does not support this feature. This section defines the "bit signal" behavior in all the modes. Please refer to the timing diagrams in

the Electrical Characteristics section (Figure 1 and Figure 2)

while going through this section. Note that the timing diagrams for the different types of "bit signals" are shown

together to better highlight the timing relationships between

them. However, the different types of "bit signals" appear on

SWD at different points in time. These timing diagrams show

the signals as driven by the master and the LM40 slave as

well as the signal as seen when probing SWD. Signal labels

20068407

www.national.com 10

1.0 Functional Description (Continued)

that begin with the label Mout_ depict a drive by the master.

Signal labels that begin with the label Slv_ depict the drive by

the LM40. All other signals show what would be seen when

probing SWD for a particular function (e.g. "Master Wr 0" is

the Master transmitting a Data Bit with the value of 0).

1.2.1 Bus Inactive

The bus is inactive when the SWD signal is high for a period

of at least t

signal".

1.2.2 Data Bit 0 and 1

All Data Bit signal transfers are started by the master. A Data

Bit 0 is indicated by a "short" pulse; a Data Bit 1 is indicated

by a longer pulse. The direction of the bit is relative to the

master, as follows:

Data Write - a Data Bit transferred from the master to the

•

LM40.

Data Read - a Data Bit transferred from the LM40 to the

•

master.

A master must monitor the bus as inactive before starting a

Data Bit (Read or Write).

A master initiates a data write by driving the bus active (low

level) for the period that matches the data value (t

for a write of "0" or "1", respectively). The LM40 will detect

that the SWD becomes active within a period of t

will start measuring the duration that the SWD is active in

order to detect the data value.

A master initiates a data read by driving the bus for a period

. The LM40 will detect that the SWD becomes active

of t

Mtr0

within a period of t

will not drive the SWD. For a data read of "1" the LM40 will

start within t

. Both master and LM40 must monitor the time at

t

SLout1

which the bus becomes inactive to identify a data read of "0"

or "1".

During each Data Bit, both the master and all the LM40s

must monitor the bus (the master for Attention Request and

Reset; the LM40s for Start Bit, Attention Request and Reset)

by measuring the time SWD is active (low). If a Start Bit,

Attention Requests or Reset "bit signal" is detected, the

current "bit signal" is not treated as a Data Bit.

Note that the bit rate of the protocol varies depending on the

data transferred. Thus, the LM40 has a value of "0" in

reserved or unused register bits for bus bandwidth efficiency.

1.2.3 Start Bit

A master must monitor the bus as inactive before beginning

a Start Bit.

The master uses a Start Bit to indicate the beginning of a

transfer. LM40s will monitor for Start Bits all the time, to allow

synchronization of transactions with the master. If a Start Bit

occurs in the middle of a transaction, the LM40 being addressed will abort the current transaction. In this case the

transaction is not "completed" by the LM40 (see Section 1.3

"SensorPath Bus Transactions").

During each Start Bit, both the master and all the LM40s

must monitor the bus for Attention Request and Reset, by

. The bus is inactive between each "bit

INACT

. For a data read of "0", the LM40

SFEdet

to drive the SWD low for a period of

SFEdet

Mtr0

SFEdet

or t

Mtr1

, and

measuring the time SWD is active (low). If an Attention

Request or Reset condition is detected, the current "bit

signal" is not treated as a Start Bit. The master may attempt

to send the Start Bit at a later time.

1.2.4 Attention Request

The LM40 may initiate an Attention Request when the SensorPath bus is inactive.

Note that a Data Bit, or Start Bit, from the master may start

simultaneously with an Attention Request from the LM40. In

addition, two LM40s may start an Attention Request simultaneously. Due to its length, the Attention Request has priority over any other "bit signal", except Reset. Conflict with

Data Bits and Start Bits are detected by all the devices, to

allow the bits to be ignored and re-issued by their originator.

The LM40 will either check to see that the bus is inactive

before starting an Attention Request, or start the Attention

Request within the t

active. The LM40 will drive the signal low for t

time interval after SWD becomes

SFEdet

SLoutA

time.

After this, both the master and the LM40 must monitor the

bus for a Reset Condition. If a Reset condition is detected,

the current "bit signal" is not treated as an Attention Request.

After Reset, an Attention Request can not be sent before the

master has sent 14 Data Bits on the bus. See Section 1.3.5

for further details on Attention Request generation.

1.2.5 Bus Reset

The LM40 issues a Reset at power up. The master must also

generate a Bus Reset at power-up for at least the minimum

reset time, it must not rely on the LM40. SensorPath puts no

limitation on the maximum reset time of the master. Following a Bus Reset, the LM40 may generate an Attention Request only after the master has sent 14 Data Bits on the bus.

See Section 1.3.5 for further details on Attention Request

generation.

1.3 SensorPath BUS TRANSACTIONS

SensorPath is designed to work with a single master and up

to seven slave devices. Each slave has a unique address.

The LM40 supports up to 2 device addresses that are selected by the state of the address pin ADD. The Register Set

of the LM40 is defined in Section 2.0.

1.3.1 Bus Reset Operation

A Bus Reset Operation is global on the bus and affects only

the communication interface of all the devices connected to

it. The Bus Reset operation does not affect either the contents of the device registers, or device operation, to the

extent defined in LM40 Register Set, see Section 2.0.

The Bus Reset operation is performed by generating a Reset

signal on the bus. The master must apply Reset after powerup, and before it starts operation. The Reset signal end will

be monitored by all the LM40s on the bus.

After the Reset Signal the SensorPath specification requires

that the master send a sequence of 8 Data Bits with a value

of "0", without a preceding Start Bit. This is required to

enable slaves that "train" their clocks to the bit timing. The

LM40 does not require nor does it support clock training.

LM40

www.national.com11

1.0 Functional Description (Continued)

LM40

20068408

FIGURE 4. Bus Reset Transaction

1.3.2 Read Transaction

During a read transaction, the master reads data from a

register at a specified address within a slave. A read transaction begins with a Start Bit and ends with an ACK bit, as

shown in Figure 5.

Device Number This is the address of the LM40 device

•

accessed. Address "000" is a broadcast address and can

be responded to by all the slave devices. The LM40

ignores the broadcast address during a read transaction.

Internal Address The address of a register within the

•

LM40 that is read.

Read/Write (R/W) A "1" indicates a read transaction.

•

Data Bits During a read transaction the data bits are

•

driven by the LM40. Data is transferred serially with the

most significant bit first. This allows throughput optimization based on the information that needs to be read.

The LM40 supports 8-bit or 16-bit data fields, as described in Section 2.0 "Register Set".

Even Parity (EP) This bit is based on all preceding bits

•

(device number, internal address, Read/Write and data

bits) and the parity bit itself. The parity -number of 1’s - of

all the preceding bits and the parity bit must be even - i.e.,

the result must be 0. During a read transaction, the EP bit

is sent by the LM40 to the master to allow the master to

check the received data before using it.

Acknowledge (ACK) During a read transaction the ACK

•

bit is sent by the master indicating that the EP bit was

received and was found to be correct, when compared to

the data preceding it, and that no conflict was detected

on the bus (excluding Attention Request - see Section

1.3.5 "Attention Request Transaction"). A read transfer is

considered "complete" only when the ACK bit is received.

A transaction that was not positively acknowledged is not

considered "complete" by the LM40 and following are

performed:

— The BER bit in the LM40 Device Status register is set

— The LM40 generates an Attention Request before, or

together with the Start Bit of the next transaction

A transaction that was not positively acknowledged is

also not considered "complete" by the master (i.e. internal operations related to the transaction are not performed). The transaction may be repeated by the master,

after detecting the source of the Attention Request (the

LM40 that has a set BER bit in the Device Status register). Note that the SensorPath protocol neither forces, nor

automates re-execution of the transaction by the master.

The values of the ACK bit are:

— 1: Data was received correctly

— 0: An error was detected (no-acknowledge).

FIGURE 5. Read Transaction, master reads data from LM40

1.3.3 Write Transaction

In a write transaction, the master writes data to a register at

a specified address in the LM40. A write transaction begins

with a Start Bit and ends with an ACK Data Bit, as show in

Figure 6.

Device Number This is the address of the slave device

•

accessed. Address "000" is a broadcast address and is

responded to by all the slave devices. The LM40 responds to broadcast messages to the Device Control

Register.

www.national.com 12

20068409

Internal Address This is the register address in the

•

LM40 that will be written.

Read/Write (R/W) A "0" data bit directs a write transac-

•

tion.

1.0 Functional Description (Continued)

Data Bits This is the data written to the LM40 register,

•

are driven by the master. Data is transferred serially with

the most significant bit first. The number of data bits may

vary from one address to another, based on the size of

the register in the LM40. This allows throughput optimization based on the information that needs to be written.

The LM40 supports 8-bit or 16-bit data fields, as described in Section 2.0 "Register Set".

Even Parity (EP) This data bit is based on all preceding

•

bits (Device Number, Internal Address, Read/Write and

Data bits) and the Even Parity bit itself. The parity (number of 1’s) of all the preceding bits and the parity bit must

be even - i.e. the result must be 0. During a write transaction, the EP bit is sent by the master to the LM40 to

allow the LM40 to check the received data before using it.

Acknowledge (ACK) During the write transaction the

•

ACK bit is sent by the LM40 indicating to the master that

the EP was received and was found correct, and that no

conflict was detected on the bus (excluding Attention

LM40

Request - see Section 1.3.5 "Attention Request Transaction"). A write transfer is considered "completed" only

when the ACK bit is generated. A transaction that was not

positively acknowledged is not considered complete by

the LM40 (i.e. internal operation related to the transaction

are not performed) and the following are performed:

— The BER bit in the LM40 Device Status register is set;

— The LM40 generates an Attention Request before, or

together with the Start Bit of the next transaction

A transaction that was not positively acknowledged is

also not considered "complete" by the master (i.e. internal operations related to the transaction are not performed). The transaction may be repeated by the master,

after detecting the source of the Attention Request (the

LM40 that has a set BER bit in the Device Status register). Note that the SensorPath protocol neither forces, nor

automates re-execution of the transaction by the master.

The values of the ACK bit are:

— 1: Data was received correctly;

— 0: An error was detected (no-acknowledge).

FIGURE 6. Write Transaction, master write data to LM40

1.3.4 Read and Write Transaction Exceptions

This section describes master and LM40 handling of special

bus conditions, encountered during either Read or Write

transactions.

If an LM40 receives a Start Bit in the middle of a transaction,

it aborts the current transaction (the LM40 does not "complete" the current transaction) and begins a new transaction.

Although not recommend for SensorPath normal operation,

this situation is legitimate, therefore it is not flagged as an

error by the LM40 and Attention Request is not generated in

response to it. The master generating the Start Bit, is responsible for handling the not "complete" transaction at a

"higher level".

If LM40 receives more than the expected number of data bits

(defined by the size of the accessed register), it ignores the

unnecessary bits. In this case, if both master and LM40

identify correct EP and ACK bits they "complete" the transaction. However, in most cases, the additional data bits differ

from the correct EP and ACK bits. In this case, both the

master and the LM40 do not "complete" the transaction. In

addition, the LM40 performs the following:

the BER bit in the LM40 Device Status register is set

•

the LM40 generates an Attention Request

•

If the LM40 receives less than the expected number of data

bits (defined by the size of the accessed register), it waits

indefinitely for the missing bits to be sent by the master. If

then the master sends the missing bits, together with the

correct EP/ACK bits, both master and LM40 "complete" the

transaction. However, if the master starts a new transaction

20068410

generating a Start Bit, the LM40 aborts the current transaction (the LM40 does not "complete" the current transaction)

and begins the new transaction. The master is not notified by

the LM40 of the incomplete transaction.

1.3.5 Attention Request Transaction

Attention Request is generated by the LM40 when it needs

the attention of the master. The master and all LM40s must

monitor the Attention Request to allow bit re-sending in case

of simultaneous start with a Data Bit or Start Bit transfer.

Refer to the "Attention Request" section, Section 1.2.4 in the

"Bit Signaling" portion of the data sheet.

The LM40 will generate an Attention Request using the

following rules:

1. A Function event that sets the Status Flag has occurred

and Attention Request is enabled and

2. The "physical" condition for an Attention Request is met

(i.e., the bus is inactive), and

3. At the first time 2 is met after 1 occurred, there has not

been an Attention request on the bus since a read of the

Device Status register, or since a Bus Reset.

OR

1. A bus error event occurred, and

2. the "physical" condition for an Attention Request is met

(i.e., the bus is inactive), and

3. At the first time 2. is met after 1 occurred, there has not

been a Bus Reset.

www.national.com13

1.0 Functional Description (Continued)

LM40

All devices (master or slave) must monitor the bus for an

Attention Request signal. The following notes clarify the

intended system operation that uses the Attention Request

Indication.

Masters are expected to use the attention request as a

•

trigger to read results from the LM40. This is done in a

sequence that covers all LM40s. This sequence is referred to as "master sensor read sequence".

After an Attention Request is sent by an LM40 until after

•

the next read from the Device Status register the LM40

does not send Attention Requests for a function event

since it is guaranteed that the master will read the Status

register as part of the master sensor read sequence.

Note that the LM40 will send an attention for BER, regardless of the Status register read, to help the master

with any error recovery operations and prevent deadlocks.

A master must record the Attention Request event. It

•

must then scan all slave devices in the system by reading

their Device Status register and must handle any pending

event in them before it may assume that there are no

more events to handle.

Note: there is no indication of which slave has sent the

request. The requirement that multiple requests are not sent

allows the master to know within one scan of register reads

that there are no more pending events.

1.3.6 Fixed Device Number Setting

The LM40 device number is defined by strapping of the ADD

pin. The LM40 will wake (after Device Reset) with the Device

Number field of the Device Number register set to the address as designated in Section 2.3 "Device Number". It is the

responsibility of the system designer to avoid having two

devices with the same Device Number on the bus.

Devices should be detected by the master by a read operation of the Device Number register. The read returns "000" if

there is no device at that address on the bus (the EP bit must

be ignored).

www.national.com 14

2.0 Register Set

2.1 REGISTER SET SUMMARY

Reg Add

000 000

00h

000 001

01h

000 010

02h

000 011

03h

000 100

04h

000 101

05h

001 000

08h

001 001

09h

001 010

0Ah

001 011

-001 111

0Bh-0Fh

010 000

10h

010 001

11h

010 010

12h

010 011

-011 111

13h-1Fh

100 000

20h

100 001

-111 111

21h-3Fh

Register

Name

Device

Number

Manufacturer

ID

Device ID R 22h

Capabilities

Fixed

Device

Status

Device

Control

Temperature

Capabilities

Processor/

Remote

Temperature

Data

Readout

Local

Temperature

Data

Readout

Temperature

Control

Reserved R Undefined

Voltage

Capabilities

Voltage

Readout

Voltage

Control

Reserved R Undefined

Conversion

Rate

Undefined

Registers

R/

W

R * Not Available

R 100Bh 0001000000001011

R 21h

R 0h Not Available BER

R/

W

R 0549h

R

R/

W

R 0051h

R

R/

W

R/

W

R Undefined

P

Bit

O

R

Val

0h

0h

1Fh

2h Not Available

Bit14Bit13Bit12Bit11Bit10Bit9Bit8Bit7Bit6Bit5Bit4Bit3Bit2Bit

15

MSb

Reserved

00000

RevID Device ID

0000000000100010

Reserved

0000000000100001

Reserved

0000000000 0

Reserved # of Remotes

0000010101001001

MSb

128

Sign

000000000000

0000000001010001

MSb LSb 0 0

00000 11111

64˚C 32˚C 16˚C 8˚C 4˚C 2˚C

˚C

Reserved

Reserved # of Voltage Sensors

Voltage Readout Reserved

Reserved

EN4 EN3 EN2 EN1 EN0 ATE

Sens

FuncDescriptor 2

(Voltage-Only)

Res

ERF2 ERF1

000

EnF2 EnF1

Int

Rout

Sign 10-Bits

Size

Res

LSb

1

˚C

000000

00 0

0.5

˚C

Res Res Res

00 00

Reserved

See Section 2.3

FuncDescriptor 1

(Temperature)

Reserved

Res

Low

Pwr

SNUM

EN2 EN1 EN0 ATE

Rout

Size

SNUM

Low Rate Function

(Read Only)

1

SF2 SF1

Shut

downReset

0.5˚C

Resolution

EF

Resolution

9-Bits

Reserved

00

CR1 CR0

LM40

Bit

0

LSb

Res

www.national.com15

2.0 Register Set (Continued)

LM40

* Depends on state of ADD pins see Section 2.3 "Device Number".

2.2 DEVICE RESET OPERATION

A Device Reset operation is performed in the following conditions:

At device power-up.

•

When the Reset bit in the Device Control register is set to 1 (see Section 2.8 "Device Control").

•

The Device Reset operation performs the following:

Aborts any device operation in progress and restarts device operation.

•

Sets all device registers to their "Reset" (default) value.

•

2.3 DEVICE NUMBER (Addr: 000 000; 00h)

This register is used to specify a unique address for each device on the bus.

P

Reg Add Register Name

000 000 Device Number R 7h or 1h

The value of [AS2:AS0] is determined by the setting of the ADD input pin:

ADD [AS2:AS0]

R/

W

0 001

1 111

O

R

Val

TABLE 1. Device Number Assignment

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1

00000

Reserved

Bit 0

LSb

AS2 AS1 AS0

The value of [AS2:AS0] will directly change and follow the value determined by ADD. Since this is a read only register the value

of the address cannot be changed by software.

2.4 MANUFACTURER ID (Addr: 000 001; 01h)

P

Reg

Register

Add

000 001

The manufacturer ID matches that assigned to National Semiconductor by the PCI SIG. This register may be used to identify the

manufacturer of the device in order to perform manufacturer specific operations.

Name

Manufacturer

ID

R/

W

R 100Bh 0001000000001011

O

R

Val

Bit

Bit14Bit13Bit12Bit11Bit10Bit9Bit8Bit7Bit6Bit5Bit4Bit3Bit2Bit

15

MSb

1

Bit

0

LSb

www.national.com 16

2.0 Register Set (Continued)

2.5 DEVICE ID (Addr: 000 010; 02h)

P

Reg

Register

Add

000 010 Device ID R 22h

The device ID is defined by the manufacturer of the device and is unique for each device produced by a manufacturer. Bits 15-11

identify the revision number of the die and will be incremented upon revision of the device.

2.6 CAPABILITIES FIXED (Addr: 000 011; 03h)

Add

000 011

Name

Bit Type Description

10-0 RO DeviceID (Device ID Value) A fixed value that identifies the device.

15-11 RO RevID (Revision ID Value) A fixed value that identifies the device revision.

Reg

Register

Name

Capabilities

Fixed

R/

W

R/

W

R 21h

Bit

O

R

Val

P

O

R

Val

Bit14Bit13Bit12Bit11Bit10Bit9Bit8Bit7Bit6Bit5Bit4Bit3Bit2Bit

15

MSb

RevID DeviceID

0000000000100010

Bit

Bit14Bit13Bit12Bit11Bit10Bit9Bit8Bit7Bit6Bit5Bit4Bit3Bit2Bit

15

MSb

Reserved FuncDescriptor2 FuncDescriptor1

0000000000100001

1

1

LM40

Bit

0

LSb

Bit

0

LSb

The value of this register defines the capabilities of the LM40. The LM40 supports two functions, that of Temperature

Measurement type (Function 1) and Voltage-Only Measurement type (Function 2). Please refer to the SensorPath specification

for further details on other FuncDescriptor values.

2.7 DEVICE STATUS (Addr: 000 100; 04h)

This register is set to the reset value by a Device Reset.

P

Reg Add Register Name

000 100 Device Status R 0h BER

Bit Type Description

0ROSF1 (Status Function 1) This bit is set by a Function Event within Function 1. Event details are function

dependent and are described within the function. SF1 is cleared by Device Reset or by handling the event

within the Temperature Measurement Function (see Section 2.9 for further details).

0: Status flag for Function 1 is inactive (no event).

1: Status flag for Function 1 is active indicating that a Function Event has occurred.

1ROSF2 (Status Function 2) Same as SF1 for Function 2, Voltage-Only Measurement Function. (see Section

2.10 for further details)

3-2 RO Reserved. Will always read "0".

4ROERF1 (Error Function 1) This bit is set in response to an error indication within Function 1. ERF1 is cleared

by Device Reset or by handling the error condition within the Temperature Measurement Function (see

Section 2.9 for further details).

0: No error occurred in Function 1.

1: Error occurred in Function 1.

5ROERF2 (Error Function 2) Same as ERF1 for Function 2, Voltage-Only Measurement Function. (see Section

2.10 for further details)

6ROReserved. Will always read "0".

R/

W

O

R

Val

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1

Res

ERF2 ERF1

000

Res

SF2 SF1

Bit 0

LSb

www.national.com17

2.0 Register Set (Continued)

LM40

Bit Type Description

7ROBER (Bus Error) This bit is set when the device either generates, or receives an error indication in the ACK

bit of the transaction (i.e., no-acknowledge). BER is cleared by Device Reset or by reading the Device Status

register.

0: No transaction error occurred.

1: An ACK bit error (no-acknowledge) occurred during the last transaction.

2.8 DEVICE CONTROL (Addr: 000 101; 05h)

This register responds to a broadcast write command (Device Number 000). Write using broadcast address is ignored by bits

15-2. This register is set to the reset value by a Device Reset.

P

Reg

Register

Add

000 101

Name

Device

Control

Bit Type Description

0 R/W Reset (Device Reset). When set to "1" this bit initiates a Device Reset operation ( See Section 2.2). This bit

1 R/W Shutdown (Shutdown Mode). When set to "1" this bit stops the operation of all functions and places the

2 R/W LowPwr (Low-Power Mode). When set to "1" this bit slows the operation of all functions and places the

3RONot supported. Will always read "0".

4 R/W EnF1 (Enable Function 1). When bit is set to "1" this bit Function 1 is enabled for operation. A function may

5 R/W EnF2 (Enable Function 2). Same as EnF1 for Function 2.

15-6 RO Not supported. Will always read "0".

R/

W

R/

W

self-clears after the Device Reset operation is completed.

0: Normal device operation. (default)

1: Device Reset

The LM40 does not require a Device Reset command after power.

device in the lowest power consumption mode.

0: Device in Active Mode. (default)

1: Device in Shutdown Mode.

device in a low power consumption mode. In Low-Power Mode, the conversion rate of the LM40 is effected

see Section 2.11 for further details.

0: Device in Active Mode. (default)

1: Device in Low-Power Mode.

require setup before this bit is set. The function registers can be accessed even when the function is

disabled.

0: Function 1 is disabled. (default)

1: Function is enabled.

Bit

O

R

Val

0h

Bit14Bit13Bit12Bit11Bit

15

MSb

0000000000

10

Reserved

Bit8Bit7Bit6Bit5Bit4Bit3Bit2Bit

Bit9

EnF2 EnF1 Res

Low

Pwr

Bit

1

LSb

Shut

downReset

0

2.9 TEMPERATURE MEASUREMENT FUNCTION (TYPE - 0001)

This section defines the register structure and operation of a Temperature Measurement function as it applies to the LM40. The

FuncDescriptor value of this function is ‘0001’.

2.9.1 Operation

The Temperature Measurement function as implemented in the LM40 supports 3 temperature zones, the LM40’s internal

temperature (LM40’s junction temperature) and the remote temperature of 2 thermal diodes (stand alone transistors or integrated

in chips). The function measures multiple temperature points and reports the readout to the master. The measurement of all the

enabled temperature sensors is cyclic and continuous.

Sensor Scan The Control register of the function defines which temperature sensors are included in the scan. A sensor is

scanned only if it is enabled by the Sensor Enable bits (EN0, EN1, and EN2). The sensors are scanned in an ascending,

round-robin order, based on the sensor number. Disabled sensors are skipped and the next enabled sensor in ascending order

is scanned.

www.national.com 18

2.0 Register Set (Continued)

The minimum scan rate is recommended to be 4Hz (i.e. the measurement data is updated at least once in 250 ms), see Section

2.11 for further details. In Low-Power Mode, the scan rate is four times lower than the scan rate in Active Mode. The scan rate

effects the bus bandwidth required to read the results. The sampling rate of the temperature measurements can also be controlled

via the Conversion Rate register, see Section 2.11 for further details.

Data Readout When a new result is stored in the Readout register a Function Event is generated. Reading the Readout

register clears the Status Function 1 flag (SF1). The result is available in the Readout register waiting for the master to read it

during the master sensor read sequence. If a new result is ready before the previous result has been read, the new result

overwrites the previous result and the Error Function 1 flag (ERF1) is set (indicating an overrun event). Reading the Readout

register clears also the Error Function 1 flag (ERF1). The Readout register contains the temperature data, and the sensor number.

Since the LM40 only supports three temperature zones the sensor number field will be zero to two. Other fields in the Readout

register as defined by the SensorPath specification are not supported.

Readout Resolution The resolution of the readout is defined in the Temperature Capabilities register. The resolution of the

LM40 is fixed and cannot be modified by software. The temperature readout type is common to all the sensors and is signed two’s

complement fixed point value. The readout type is specified in the Capabilities register of the function.

Sensor 0 in the Temperature Measurement function is reserved for local temperature measurement (i.e., the junction temperature

of the LM40).

Function Event The Temperature Measurement function generates a Function Event whenever a conversion cycle is

completed and new data is stored in the Readout Register. When the new data is stored into the Readout register the SF1 bit in

the device Status register is set to "1" and remains set, until it is cleared by reading the Readout register. An Attention Request

is generated on the bus, only if it is enabled by the Attention Enable bit (ATE) in the Temperature Control register.

Setup Before Enabling No setup is required for the Temperature Measurement function before the function is enabled.

2.9.2 Temperature Capabilities (Addr: 001 000; 08h)

LM40

P

Reg

Register

Add

001 000

This register defines the format of the temperature data in the readout register. The LM40 only supports one format for all

temperatures as defined by the values of this register.

Name

Temperature

Capabilities

Bit Type Description

2-0 RO Resolution. This field defines the value of 1 LSb of the Temperature Readout field in the Readout Register.

5-3 RO Number of Bits. This field defines the total number of significant bits of the Temperature Readout field in the

6ROSign (Signed Data). Defines the type of data in the Temperature Readout field of the Readout register.

7RORoutSize (Readout Register size). Defines the total size of the Readout register.

8ROIntSens (Internal Sensor Support). Indicates if the device supports internal temperature measurements, as

11-9 RO # of Remotes (Number of Remote Sensors). Specifies the number of remote Temperature Sensors

15-12 RO Reserved. Will always read "0".

R/

W

R 0549h

The SensorPath specification defines many different weights for the temperature LSb. The LM40 supports a

resolution of 0.5 ˚C and thus a value of 001 for this field. For a full definition of this field, please refer to the

SensorPath specification.

Readout register. The total number of significant bits includes the number of bits representing the integer

part of the temperature data and the fractional part of it, as defined by the Resolution field. The LM40

supports 10-bits and thus a value of 001 for this field. For a full definition of this field please refer to the

SensorPath specification.

0: Unsigned, positive fixed point value.

1: Signed, 2’s complement fixed point value. (value for the LM40)

0: 16 bits. (value for the LM40)

the LM40 does.

0: No internal temperature measurement

1: Internal temperature sensor implemented. (value for the LM40)

supported by the function.

2: The number of Remote Temperature Sensors. (value for the LM40)

Bit

O

R

Val

Bit14Bit13Bit12Bit11Bit10Bit9Bit8Bit7Bit6Bit5Bit4Bit3Bit2Bit

15

MSb

Int

Reserved # of Remotes

0000010101001001

Sens

Rout

Sign 10-Bits

Size

1

0.5˚C

Resolution

Bit

0

LSb

www.national.com19

2.0 Register Set (Continued)

LM40

2.9.3 Temperature Data Readout (Addr: 001 001; 09h)

P

Reg

Register

Add

001 001

Name

Local

Temperature

Data

Readout

Processor/

Remote

Temperature

Data

Readout

Bit Type Description

0ROReserved. Will always read "0".

1ROReserved for Local Temperature Data Readout. Will always read "0".

3-2 RO SNUM (Sensor Number). This field indicates the number of the current Temperature Sensor, to which the

5-4 RO Reserved. Will always read "0".

15-6 RO Temperature Readout. This field holds the result of the temperature measurement. The active size of this

R/

W

R

EF (Error Flag) for Remote Temperature Data Readout. This bit indicates that an error was detected

during the measurement of the current remote Temperature sensor such as a diode fault condition. When a

diode fault occurs the value of the temperature reading will be 200h or -256˚C.

0: No error detected.

1: Error detected.

data in the Temperature Readout field belongs. Temperature Sensor 0 is always assigned to the local

sensor of the LM40.

0: Local temperature sensor (see Table Thermal Diode Input Mapping)

1-2: Remote sensor 1 and 2 (see Table Thermal Diode Input Mapping)

field for the LM40 is 10-bits, left justified. See Table Temperature Data Format for examples.

O

R

Val

Bit

Bit14Bit13Bit12Bit11Bit10Bit9Bit8Bit7Bit6Bit5Bit4Bit3Bit2Bit

15

MSb

Reserved

00 00

MSb

Sign

128

64˚C 32˚C 16˚C 8˚C 4˚C 2˚C 1˚C

˚C

0.5

˚C

Reserved

00 0

SNUM

Bit

0

1

LSb

Reserved

Res

EF

Thermal Diode Input Mapping

Sensor Number

(SNUM) Sensor Input Board Connection

0 Local none

1 Processor, D1+/D1- CPU Thermal Diode

2 Remote, D2+/D2- MMBT3904 Thermal Diode or GPU

Thermal Diode

All LM40 temperature data has a common format. The LM40’s temperature data format is two’s complement and has 10-bits of

resolution with the LSb having a weight of 0.5 ˚C. The LM40 can resolve temperature between +255.5 ˚C and -256 ˚C, inclusive.

It can measure local temperatures between +85 ˚C and 0 ˚C and remote temperatures between +125 ˚C and 0 ˚C with an

accuracy of

www.national.com 20

±

3.0 ˚C.

Temperature Data Format

Temperature Binary Hex

+140 ˚C 01 0001 1000 118h

+100 ˚C 00 1100 1000 0C8h

+1 ˚C 00 0000 0010 002h

0 ˚C 00 0000 0000 000h

- 0.5 ˚C 11 1111 1111 3FFh

-1 ˚C 11 1111 1110 3FEh

2.0 Register Set (Continued)

Temperature Data Format (Continued)

Temperature Binary Hex

- 40 ˚C 11 1011 0000 2B0h

-255.5 ˚C 10 0000 0001 201h

-256 ˚C 10 0000 0000 200h

2.9.4 Temperature Control (Addr: 001 010; 0Ah)

This register is set to the reset value by a Device Reset.

P

Reg

Register

Add

001 010

Name

Temperature

Control

Bit Type Description

0 R/W ATE (Attention Enable). When set, this bit enables an Attention Request signal to be generated by the

1 R/W EN0 (Enable Sensor 0). When this bit is set, the Local Temperature Sensor is enabled for temperature

2 R/W EN1 (Enable Sensor 1). When this bit is set, the Remote Thermal Diode 1 Temperature Sensor is enabled

3 R/W EN2 (Enable Sensor 2). When this bit is set, the Remote Thermal Diode 2 Temperature Sensor is enabled

15-4 RO Reserved. Will always read "0".

R/

W

R/

W

LM40, if the EN0, EN1 or EN2 bits of this register are set.

0: Attention Request disabled (from enabled Temperature Sensor- default)

1: Attention Request enabled (from enabled Temperature Sensor)

measurements.

0: Temperature Sensor disabled (default)

1: Temperature Sensor enabled

for temperature measurements.

0: Temperature Sensor disabled (default)

1: Temperature Sensor enabled

for temperature measurements.

0: Temperature Sensor disabled (default)

1: Temperature Sensor enabled

Bit

O

R

Val

0h

Bit14Bit13Bit12Bit11Bit10Bit9Bit8Bit7Bit6Bit5Bit4Bit3Bit2Bit

15

MSb

Reserved

000000000000

EN2 EN1 EN0 ATE

LM40

Bit

0

1

LSb

2.10 VOLTAGE-ONLY MEASUREMENT FUNCTION (TYPE 0010)

This section defines the register structure and operation of the Voltage-Only Measurement Function. The FuncDescriptor value

of this function is ‘0010’.

2.10.1 Operation

The Voltage-Only measurement function is capable of measuring the voltage of voltage measurement points ("sensors"). These

may be general or dedicated inputs (e.g., for backup battery measurement or the supply voltage to the device). The measurement

of all the enabled voltage sensors is cyclic and continuous.

Sensor Scan The control register of the function defines which voltage sensors (inputs) are included in the scan. A sensor is

scanned only if it is enable by the Sensor Enable bit (EN0, EN1, EN2, EN3 and EN4). The sensors are scanned in an ascending,

round-robin order, based on the sensor number. Disabled sensors are skipped and the next enabled sensor in ascending order

is scanned.

The minimum scan rate is recommended to be 4Hz (i.e., the measurement data is updated at least once in 250 ms), see Section

2.11 for further details. In Low-Power Mode, the scan rate is four times lower than the scan rate in Active Mode. The scan rate

effects the bus bandwidth required to read the results. The sampling rate of the voltage measurements can also be controlled via

the Conversion Rate register, see Section 2.11 for further details.

Data Readout When a new result is stored in the readout register a Function Event is generated. Reading the Readout register

clears the Status Function 2 flag (SF2) for the Voltage-Only Measurement Function in the Device Status register. The result is

available in the Readout register waiting for the master to read it during the master sensor read sequence. The device should

delay or buffer additional conversions to allow the master time to read the result (see Sensor Scan Rate Section 2.11). If a new

www.national.com21

2.0 Register Set (Continued)

LM40

result is ready before the previous result has been read, the new results overwrites the previous result and the Error Function 2

flag (ERF2) for the Voltage-Only function in the Device Status register is set (indicating an overrun event). Reading the

Voltage-Only Measurement Readout register clears also the ERF2 flag.

Readout Resolution The resolution of the readout register is defined in the Voltage Capabilities register. The resolution of the

LM40 is fixed and cannot be modified by software. The voltage readout format is common to all voltage sensors and is 9-bits

unsigned. For over or under input voltage conditions the data is guaranteed to saturate at all "1"s or "0"s so long as Operating

Ratings of the LM40 are adhered to.

Function Event The Voltage-Only Measurement function generates a Function Event to the master whenever a conversion

cycle is completed and new data is stored in the Readout register. When the new data is stored into the Readout register the SF2

bit in the Device Status register is set to 1 and remains set, until it is cleared by reading the Readout register. An Attention Request

is generated on the bus, only if it is enabled by the Attention Enable bit (ATE) in the Control register.

Setup Before Enabling No setup is required for the Voltage-Only Measurement function before it is enabled.

2.10.2 Voltage Capabilities (Addr: 010 000; 10h)

P

Reg

Register

Add

010 000

This register defines the format of the voltage data in the voltage readout register. The LM40 only supports one format for all

voltage measurements as defined by the values of this register.

Name

Voltage

Capabilities

Bit Type Description

2-0 RO Resolution. This field defines the total number of significant bits in the Voltage Readout field in the Readout

3RORoutSize (Readout Register size). Defines the total size of the Readout register.

8-4 RO # of Voltage Sensors (Number of Voltage Sensors). Specifies the number of Voltage Sensors supported

15-9 RO Reserved. Will always read "0".

R/

W

R 0051h

register for this function. The voltage data is always aligned to the left in the Voltage Readout filed and is

extended with zeros.

001: 9-bit (value for the LM40, for other field values see the SensorPath specification)

0: 16 bits. (value for the LM40 for other field values see the SensorPath specification)

by this function.

5: The number of Voltage Sensors. (value for the LM40 for other field values see the SensorPath

specification)

Bit

O

R

Val

Bit14Bit13Bit12Bit11Bit10Bit9Bit8Bit7Bit6Bit5Bit4Bit3Bit2Bit

15

MSb

Reserved # of Voltage Sensors

0000000001010001

Rout

Size

Bit

0

1

LSb

9-bit Resolution

2.10.3 Voltage Readout (Addr: 010 001; 11h)

P

Reg

Register

Add

010 001

www.national.com 22

Name

Voltage

Readout

Bit Type Description

0-1 RO Reserved. Will always read "0".

4-2 RO SNUM (Sensor Number). This field indicates the number of the current Voltage Sensor, to which the data in

6-5 RO Reserved. Will always read "0".

15-7 RO Voltage Readout. This field holds the result of the voltage measurement. The active size of this field for the

R/

W

R

the Voltage Readout field belongs. See Table Analog Input Voltage Mapping for assignments.

LM40 is 9-bits, left justified. See Table Analog Input Voltage Mapping for voltage mapping details.

Bit

O

R

Val

Bit14Bit13Bit12Bit11Bit10Bit9Bit8Bit7Bit6Bit5Bit4Bit3Bit2Bit

15

MSb

Voltage Readout Reserved

MSb LSb 0 0 0 0

SNUM

Bit

0

1

LSb

Reserved

2.0 Register Set (Continued)

Analog Input Voltage Mapping

Input Voltage

for Nominal

Sensor

Number

(SNUM) Voltage Input

0 +2.5V 2.5V 3.32V to 6V 1FFh -0.5V to

1 +1.2V 1.2V 1.6V to 6V 1FFh -0.5V to

2 +3.3V_SBY

(V+)

3 +5V 5V 6.65V 1FFh -0.5V to

4 +12V 12V 15.95V to 16V 1FFh -0.5V to

2.10.4 Voltage Control (Addr: 010 010; 12h)

This register is set to the reset value by a Device Reset.

Reg

Add

010 010

Register

Name

Voltage

Control

R/

W

R/

W

Reading

(code 384 or

180h)

3.3V 4.39V to 6V 1FFh 3.0V 15Dh 8.59mV

P

Bit

O

15

R

MSb

Val

1Fh

00000 11111

Maximum

Input Voltage

(code 510.5)

Bit14Bit13Bit12Bit11Bit10Bit9Bit8Bit7Bit6Bit5Bit4Bit3Bit2Bit

Reserved

Register

Reading at

Maximum

Voltage

EN4 EN3 EN2 EN1 EN0 ATE

Minimum

Input Voltage

3.26mV

2.63mV

6.51mV

15.63mV

Register

Reading at

Minimum

Voltage Resolution

00h 6.51mV

00h 5.86mV

00h 13.02mV

00h 31.25mV

1

Low Rate Function

(Read Only)

LM40

Bit

0

LSb

Bit Type Description

4-0 RO Low Rate Function This function is not supported by the LM40 and therefore this field is read only.

5 R/W ATE (Attention Enable). When set, this bit enables an Attention Request signal to be generated by the

LM40, if one or more EN0-EN4 bits of this register are set.

0: Attention Request disabled (from enabled Temperature Sensor- default)

1: Attention Request enabled

6 R/W EN0 (Enable Sensor 0). When this bit is set, the Voltage Sensor 0 is enabled for voltage measurements.

0: Voltage Sensor disabled (default)

1: Voltage Sensor enabled

10-7 R/W EN1-EN4 (Enable Sensor 1-4). Same as EN0 for Voltage sensors 1-4.

0: Voltage Sensor disabled (default)

1: Voltage Sensor enabled

15-11 RO Reserved. Will always read "0".

2.11 CONVERSION RATE (Addr: 100 000; 20h)

P

Reg Add Register Name

100 000 Conversion Rate

Bit Type Description

1-0 RO CR0 and CR1 (Conversion Rate bits 0 and 1) These bits control the conversion rate of the LM40 for

more details see Table Conversion Rate Control and desciption below.

R/

W

R/

W

O

R

Val

2h

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1

Reserved

000000

CR1 CR0

Bit 0

LSb

www.national.com23

2.0 Register Set (Continued)

LM40

Bit Type Description

7-2 RO Reserved. Will always read "0".

Conversion Rate Control

LowPwr [CR1:CR0] Typical Conversion Rate (ms)

0 00 Fastest*: continuous

100 91

001 91

1 01 364

0 10 182 (default)

1 10 728

0 11 364

1 11 1456

*Fastest: 2x7.5ms(remote) + 7.5msec (local) + 5x1.42msec (voltage) = 29.6 ms total

The sensor conversion rate is controlled by this register as well as the Low Power Bit of Device Control Register. This register is

not defined by the SensorPath specification. Therefore, on a motherboard when using a Super I/O host this register must be

modified during BIOS run time. The conversion rate is dependent on system physical requirements and limitations. The thermal

response time of the MSOP package is one such requirement. Most systems will function properly with the default settings. The

master scan rate is related to the conversion rate of the LM40. If attentions are enabled the conversion rate and scan rate will be

equal.

3.0 Application Hints

The LM40 can be applied easily in the same way as other

integrated-circuit temperature sensors, and its remote diode

sensing capability allows it to be used in new ways as well.

It can be soldered to a printed circuit board, and because the

path of best thermal conductivity is between the die and the

pins, its temperature will effectively be that of the printed

circuit board lands and traces soldered to the LM40’s pins.

This presumes that the ambient air temperature is almost the

same as the surface temperature of the printed circuit board;

if the air temperature is much higher or lower than the

surface temperature, the actual temperature of the of the

LM40 die will be at an intermediate temperature between the

surface and air temperatures. Again, the primary thermal

conduction path is through the leads, so the circuit board

temperature will contribute to the die temperature much

more strongly than will the air temperature.

To measure temperature external to the LM40’s die, use a

remote diode. This diode can be located on the die of a

target IC, allowing measurement of the IC’s temperature,

independent of the LM40’s temperature. The LM40 has been

optimized to measure the remote diode of a 90 nm Pentium

4 processor as shown in Figure 7. A discrete diode can also

be used to sense the temperature of external objects or

ambient air. Remember that a discrete diode’s temperature

will be affected, and often dominated, by the temperature of

its leads.

FIGURE 7. 90 nm Pentium 4 Temperature vs LM40

Temperature Reading

Most silicon diodes do not lend themselves well to this

application. It is recommended that a 2N3904 transistor

base emitter junction be used with the collector tied to the

base.

A diode connected 2N3904 approximates the junction available on a Pentium microprocessor for temperature measurement. Therefore, the LM40 can sense the temperature of this

diode effectively. Although, an offset will be observed. The

temperature reading will be offset by approximately −4.5˚C,

therefore a correction factor of +4.5˚C should be added to all

temperature readings when using a 2N3904 transistor.

20068415

www.national.com 24

LM40

3.0 Application Hints (Continued)

3.1 DIODE NON-IDEALITY

3.1.1 Diode Non-Ideality Factor Effect on Accuracy

When a transistor is connected as a diode, the following

relationship holds for variables V

where:

q = 1.6x10

•

T = Absolute Temperature in Kelvin

•

k = 1.38x10

•

η is the non-ideality factor of the process the diode is

•

−19

Coulombs (the electron charge),

−23

joules/K (Boltzmann’s constant),

manufactured on,

IS= Saturation Current and is process dependent,

•

If= Forward Current through the base emitter junction

•

VBE= Base Emitter Voltage drop

•

In the active region, the -1 term is negligible and may be

eliminated, yielding the following equation

, T and If:

BE

Processor Family η, non-ideality Series

R

min typ max

Pentium II 1 1.0065 1.0173

Pentium III CPUID 67h 1 1.0065 1.0125

Pentium III CPUID

1.0057 1.008 1.0125

68h/PGA370Socket/Celeron

Pentium 4, 423 pin 0.9933 1.0045 1.0368

Pentium 4, 478 pin 0.9933 1.0045 1.0368

Pentium 4 on 0.13

1.0011 1.0021 1.0030 3.64 Ω

micron process,

2-3.06GHz

Pentium 4 on 90 nm

1.011 3.33 Ω

process

Pentium M Processor

1.00151 1.00220 1.00289 3.06 Ω

(Centrino)

MMBT3904 1.003

AMD Athlon MP model61.002 1.008 1.016

3.2 PCB LAYOUT for MINIMIZING NOISE

In the above equation, η and ISare dependant upon the

process that was used in the fabrication of the particular

diode. By forcing two currents with a very controlled ration

(N) and measuring the resulting voltage difference, it is

possible to eliminate the I

term. Solving for the forward

S

voltage difference yields the relationship:

The non-ideality factor, η, is the only other parameter not

accounted for and depends on the diode that is used for

measurement. Since ∆V

is proportional to both η and T,

BE

the variations in η cannot be distinguished from variations in

temperature. Since the non-ideality factor is not controlled by

the temperature sensor, it will directly add to the inaccuracy

±

of the sensor. For the Pentium III Intel specifies a

1%

variation in η from part to part. As an example, assume a

±

temperature sensor has an accuracy specification of

3˚C at

room temperature of 25 ˚C and the process used to manu-

±

facture the diode has a non-ideality variation of

1%. The

resulting accuracy of the temperature sensor at room temperature will be:

=±3˚C+(±1% of 298 ˚K) =±6˚C

T

ACC

The additional inaccuracy in the temperature measurement

caused by η, can be eliminated if each temperature sensor is

calibrated with the remote diode that it will be paired with.

The following table shows the variations in non-ideality for a

variety of processors.

20068417

FIGURE 8. Ideal Diode Trace Layout

In a noisy environment, such as a processor mother board,

layout considerations are very critical. Noise induced on

traces running between the remote temperature diode sensor and the LM40 can cause temperature conversion errors.

Keep in mind that the signal level the LM40 is trying to

measure is in microvolts. The following guidelines should be

followed:

1. Place the 100 pF and 0.1 µF power supply bypass

capacitors as close as possible to the LM40’s power pin.

Place the recommended thermal diode 100 pF capacitor

as close as possible to the LM40’s D+ and D− pins.

Make sure the traces to the thermal diode 100 pF capacitor are matched.

2. The recommended 100 pF diode capacitor actually has

a range of 0 pF to 3.3 nF (see curve in Typical Performance Characteristics for effect on accuracy). The average temperature accuracy will not degrade. Increasing

the capacitance will lower the corner frequency where

differential noise error affects the temperature reading

thus producing a reading that is more stable. Conversely, lowering the capacitance will increase the corner frequency where differential noise error affects the

temperature reading thus producing a reading that is

less stable.

www.national.com25

3.0 Application Hints (Continued)

LM40

3. Ideally, the LM40 should be placed within 10cm of the

Processor diode pins with the traces being as straight,

short and identical as possible. Trace resistance of 0.7Ω

can cause as much as 1˚C of error. This error can be

compensated for by adding or subtracting an offset to

the remote temperature reading(s).

4. Diode traces should be surrounded by a GND guard ring

to either side, above and below if possible. This GND

guard should not be between the D+ and D− lines. In the

event that noise does couple to the diode lines it would

be ideal if it is coupled common mode. That is equally to

the D+ and D− lines.

5. Avoid routing diode traces in close proximity to power

supply switching or filtering inductors.

6. Avoid running diode traces close to or parallel to high

speed digital and bus lines. Diode traces should be kept

at least 2cm apart from the high speed digital traces.

7. If it is necessary to cross high speed digital traces, the

diode traces and the high speed digital traces should

cross at a 90 degree angle.

8. The ideal place to connect the LM40’s GND pin is as

close as possible to the Processors GND associated

with the sense diode.

9. Leakage current between D+ and GND should be kept

to a minimum. Seventeen nano-amperes of leakage can

cause as much as 0.2˚C of error in the diode temperature reading (see curve in Section Typical Performance

Characteristics). Keeping the printed circuit board as

clean as possible will minimize leakage current.