查询DP83864供应商

DP83864 Quad GigPHYTER™ 10/100/1000 Ethernet Physical Layer

ADVANCED INFORMATION

September 2003

DP83864 Quad GigPHYTER

™

10/100/1000 Ethernet Physical Layer

General Description

The DP83864 is an extremely efficient full featured Quad

Physical L ayer tran sceiver wit h integrat ed PMD sub layers

to support 10BASE-T, 100BASE-TX and 1000BASE-T

Ethernet protocols.

The DP83864 contains four integrated ultra low power

Gigabit Physical layers. It uses advanced 0.18 µm, 1.8 V

CMOS technology, fabricated at National’s South Portland,

Maine facilities.

The DP83864 is designed for easy implementation of

10/100/1000 Mb/s Ethernet LANs. Each port interfaces

directly to Twisted Pair media via an external transformer.

This device in terfa ce s dire ct ly to the MAC layer throug h th e

IEEE 802.3u Standard Media Independent Interface (MII)

or the IEEE 802.3z Gigabit Media Independent Interface

(GMII). It also supports the reduced pin count RGMII (12

pins per port) and serial GMII (8 pins per port).

The DP83864 is a fourth generation of Gigabit Physical

layer product with field proven architecture and performance. Its robust performance ensures drop in replacement of existing 10/100M equipment with 10/100/1000M

Networking infrastructure.

Applications

The DP83864 fits applications in:

■ Switches with 10/100/1000 Mb/s capable ports

■ High speed uplink ports with redundancies (backbone)

■ Servers with Quad Ethernet ports

Features

■ IEEE compliant 10BASE-T,100BASE-TX, 1000BASE-T

■ Adaptive equalization and Baseline Wander comp.

■ IEEE 802.3u Auto-Negotiation and Parallel Detection

– Fully auto-negotiat es betw een 10 00 Mb/s, 100 Mb/s,

and 10 Mb/s full duplex and half duplex devices

■ 2.5 V/3.3 V MAC interfaces:

– IEEE 802.3u MII with programmable bus ordering

– IEEE 802.3z GMII with programmable bus ordering

– Reduced GMII (RGMII) ver. 1.3

– Serial GMII (SGMII)

■ LED support (Link10, Link100, Link1000, Activity and

Duplex indicators); Direct drive LED’s thru management

■ User Programmable Interrupt

■ A 25Mhz or 125Mhz oscillator as reference clock input

■ PHY level CRC checking on received packets and PHY

level CRC generation for test mode transmit packets

■ 292 BGA package

■ Power dissipation approximately 1 W / port

■ 1.8 V CMOS (core & analog); 2.5 V (analo g & I/O); 3.3 V

is optional for 3.3 V I/O voltage

■ One management port per chip

■ Supports Auto-MDIX/polarity at all speeds

■ One JTAG interface per chip

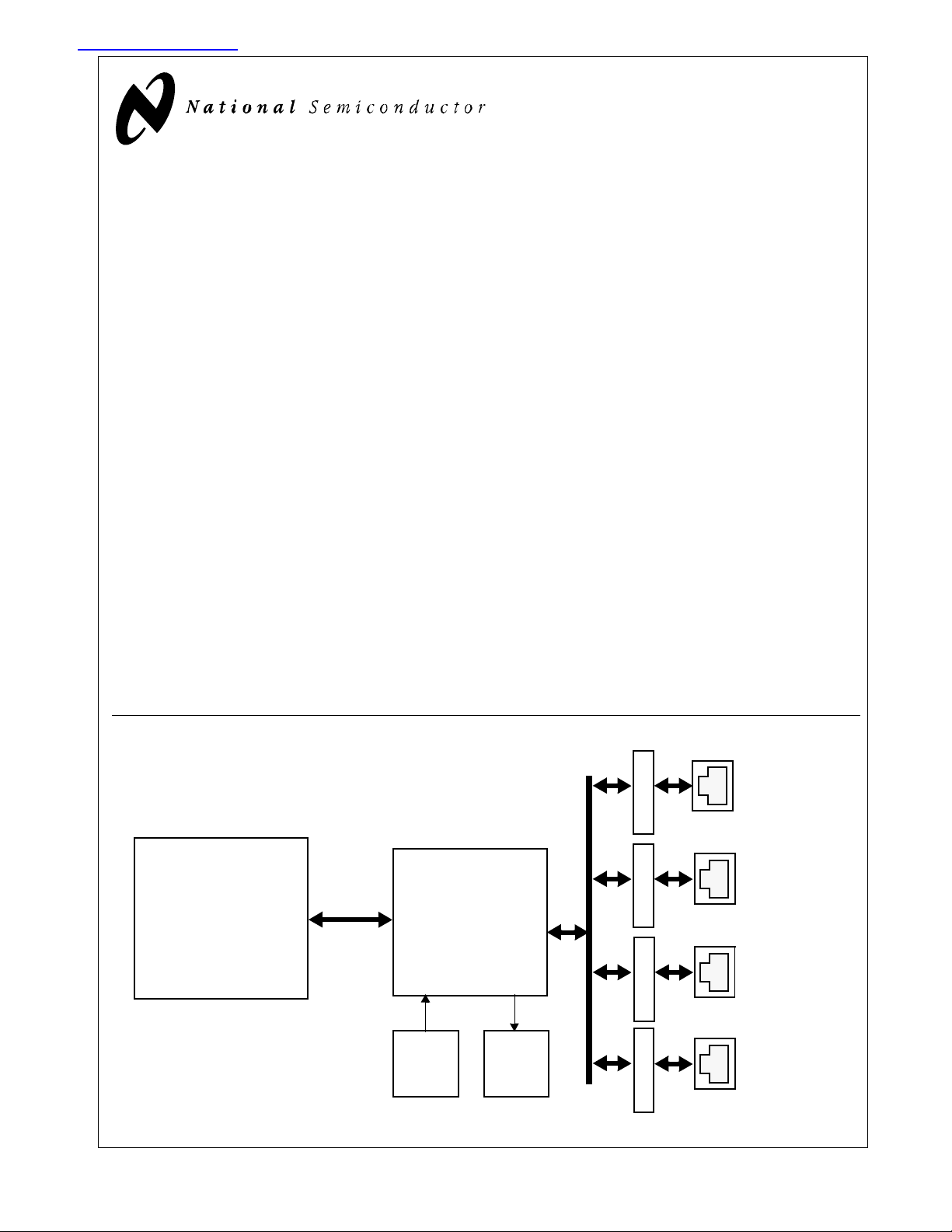

System Diagram

MII

GMII

Quad Port

10/100/1000 Mb/s

ETHERNET

MAC

™

GigPHYTER

is a trademark of National Semiconductor Corporation.

© 2003 National Semiconductor Corporation

RGMII

SGMII

RJ-45

MAGNETICS

DP83864

10/100/1000 Mb/s

ETHERNET

PHYSICAL LAYER

25 MHz or

125 MHz

Oscillator

MAGNETICS

MAGNETICS

Status

LED’s

Per Port

MAGNETICS

RJ-45

10BASE-T,

100BASE-TX,

or

1000BASE-T

RJ-45

RJ-45

www.national.com

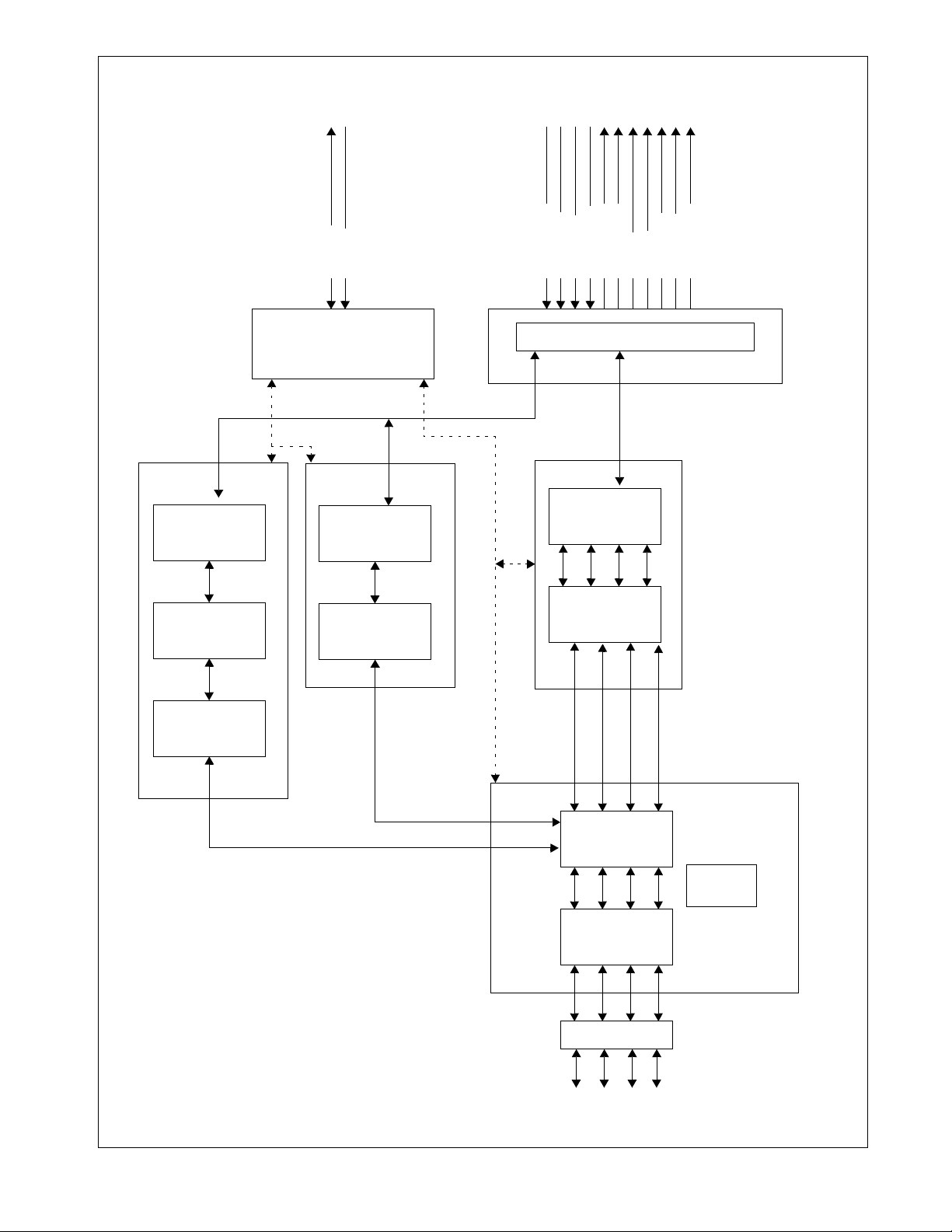

Block Diagram (Showing One Port)

DP83864

100BASE-TX Block

MII

100BASE-TX

PCS

MGMT INTERFACE

MDIO

MDC

µC MGMT

& PHY CNTRL

10BASE-T Block

MII

10BASE-T

PLS

COMBINED GMII, RGMII, SGMII, and MII INTERFACE

GTX_CLK

TX_EN

TXD[7:0]

TX_CLK

RX_CLK

COL

CRS

RX_ER

RX_DV

TX_ER

MUX/DMUX

GMII, RGMII, SGMIIMII

1000BASE-T Block

GMII

1000BASE-T

PCS

RXD[7:0]

100BASE-TX

PMA

100BASE-TX

PMD

MLT-3

100 Mb/s

Block Diagram for One Port

10BASE-T

PMA

Manchester

10 Mb/s

1000BASE-T

PMA

DAC/ADC

SUBSYSTEM

DRIVERS/

RECEIVERS

MAGNETICS

PAM-5

PR Shaped

125 Msymbols/s

DAC/ADC

TIMING BLOCK

TIMING

4-pair CAT- 5 Cable

2 www.national.com

Notes:

DP83864

3 www.national.com

Physical Dimensions

inches (millimeters) unless otherwise noted

NS Package BGA-292

Order Number DP83864AUT

DP83864 Quad GigPHYTER™ 10/100/1000 Ethernet Physical Layer

LIFE SUPPORT POLICY

NATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL

COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devic es or sy stems are devices or sys t em s

which, (a) are inte nded for sur gical implant in to the body,

or (b) support or sustain life, and whose failure to perform, when properly used in accord ance with instructions

for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

2. A critical component is any component of a life support

device or system whose failure to perform can be reasonably expected to cause the failure of the life support

device or system, or to affect its safety or effectiveness.

National Semiconductor

Americas Customer

Support Center

Email: new.feedback@nsc.com

Tel: 1-800-272-9959

www.national.com

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

National Semiconductor

EuropeCustomer

Support Center

Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Francais Tel: +33 (0) 1 41 91 8790

National Semiconductor

Asia Pacific Customer

Support Center

Email: ap.support@nsc.com

National Semiconductor

Japan Custom er

Support Center

Fax: 81-3-5639-7507

Email: jpn.feedback@nsc.com

Tel: 81-3-5639-7560

Loading...

Loading...