August 2006

DP83849IF PHYTER® DUAL Industrial Temperature with Fiber Support (FX) and

Flexible Port Switching Dual Po rt 10/ 10 0 Mb/s Ethernet Physical Layer Transceiver

DP83849IF PHYTER® DUAL Industrial Temperature with Fiber Support (FX) and Flexible Switching

Dual Port 10/100 Mb/s Ethernet Physical Layer Transceiver

General Description

The number of applications requiring Ethernet Connectivity continues to expand. Along with this

increased market demand is a change in application

requirements. Where single channel Ethernet used to

be sufficient, many applications such as wireless

remote base stations and industrial networking now

require DUAL Port functionality for redundancy or system management.

The DP83849IF is a highly reliable, feature rich device

perfectly suited for industrial applications enabling

Ethernet on the factory floor. The DP83849IF features

two fully independent 10/100 ports for multi-port applications. NATIONAL’s unique po rt switching capabilit y

also allows the two ports to be configured to provide

fully integrated range extension, media conversion,

hardware based failover and port monitoring.

The DP83849IF provides optimum flexibility in MPU

selection by supporting both MII and RMII interfaces.

The device also provides flexibility by supporting both

copper and fiber media. In additio n this de vice includ es

a powerful new diagnostics tool to ensure initial network operation and maintenance.

In addition to the TDR scheme, commonly used for

detecting faults during installation, NATIONAL’s innovative cable diagnostics provides for real time continuous monitoring of the link quality. This allows the

system designer to implement a fault prediction mechanism to detect and warn of changing or deteriorating

link conditions.

With the DP83849IF, National Semiconductor continues to build on its Ethernet expertise and leadership

position by providing a powerful combination of features and flexibility, easing Ethernet implementation for

the system designer.

Features

• Low-power 3.3V, 0.18µm CMOS technology

• Low power consumption <600mW Typical

• 3.3V MAC Interface

• Auto-MDIX for 10/100 Mb/s

• Energy Detection Mode

• Flexible MII Port Assignment

• Dynamic Integrity Utility

• Dynamic Link Quality Monito r ing

• TDR based Cable Diagnostic and Cable Length Detection

• Optimized Latency for Real Time Ethernet Operation

• Reference Clock out

• RMII Rev. 1.2 Interface (configurable)

• SNI Interface (configurable)

• MII Serial Management Interface (MDC and MDIO)

• IEEE 802.3u MII

• IEEE 802.3u Auto-Negotiation and Parallel Detection

• IEEE 802.3u ENDEC, 10BASE-T transceivers and filters

• IEEE 802.3u PCS, 100BASE-TX transceivers and filters

• IEEE 802.3u 100BASE-FX Fiber Interface

• IEEE 1149.1 JTAG

• Integrated ANSI X3.263 compliant TP-PMD physical sub-layer

with adaptive equalization and Baseline Wander compensation

• Programmable LED support for Link, 10 /100 Mb/s Mode, Activ-

ity, Duplex and Collision Detect

• Single register access for complete PHY status

• 10/100 Mb/s packet BIST (Built in Self Test)

• 80-pin TQFP package (12mm x 12mm)

Applications

• Medical Instrumentation

• Factory Automation

• Motor & Motion Control

• Wireless Remote Base Station

• General Embedded Applications

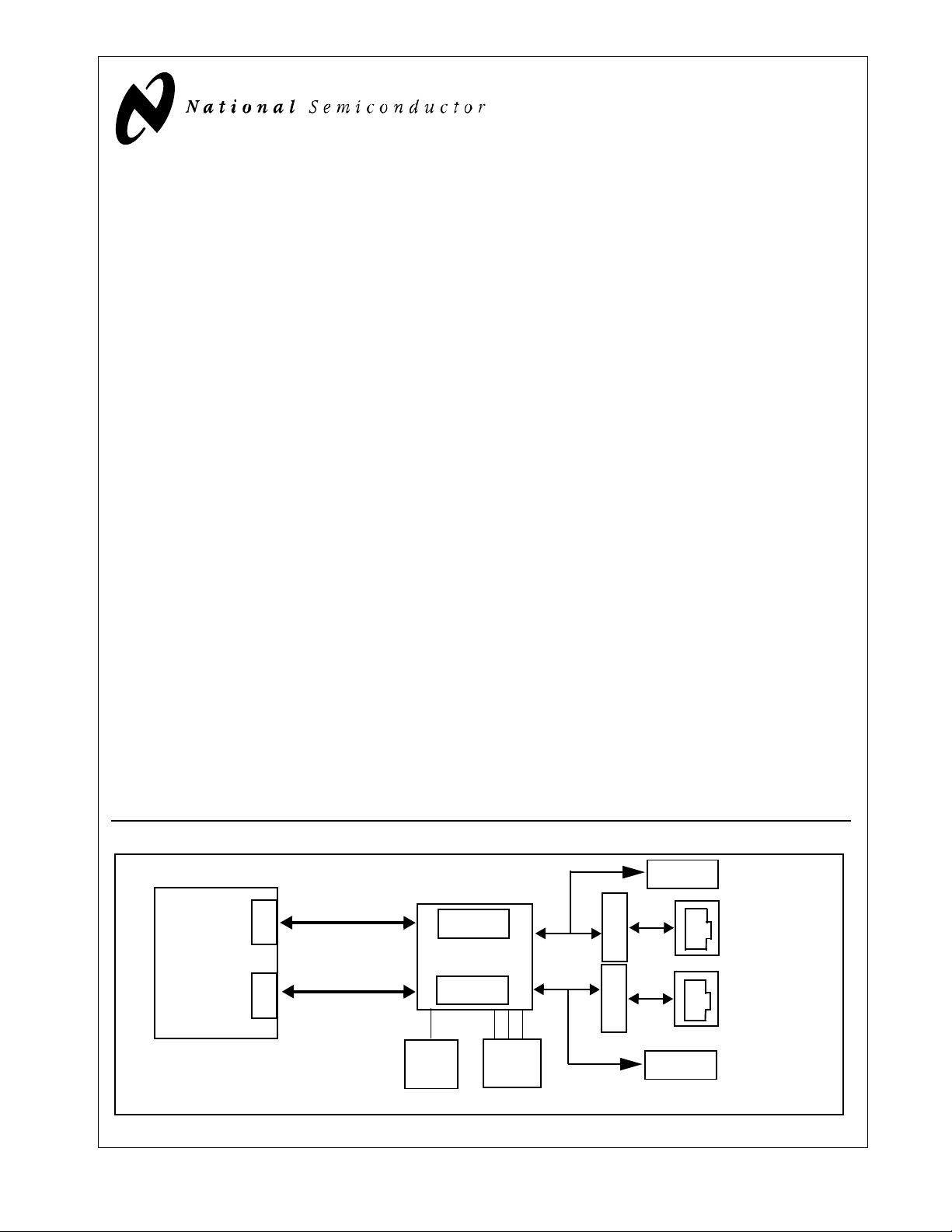

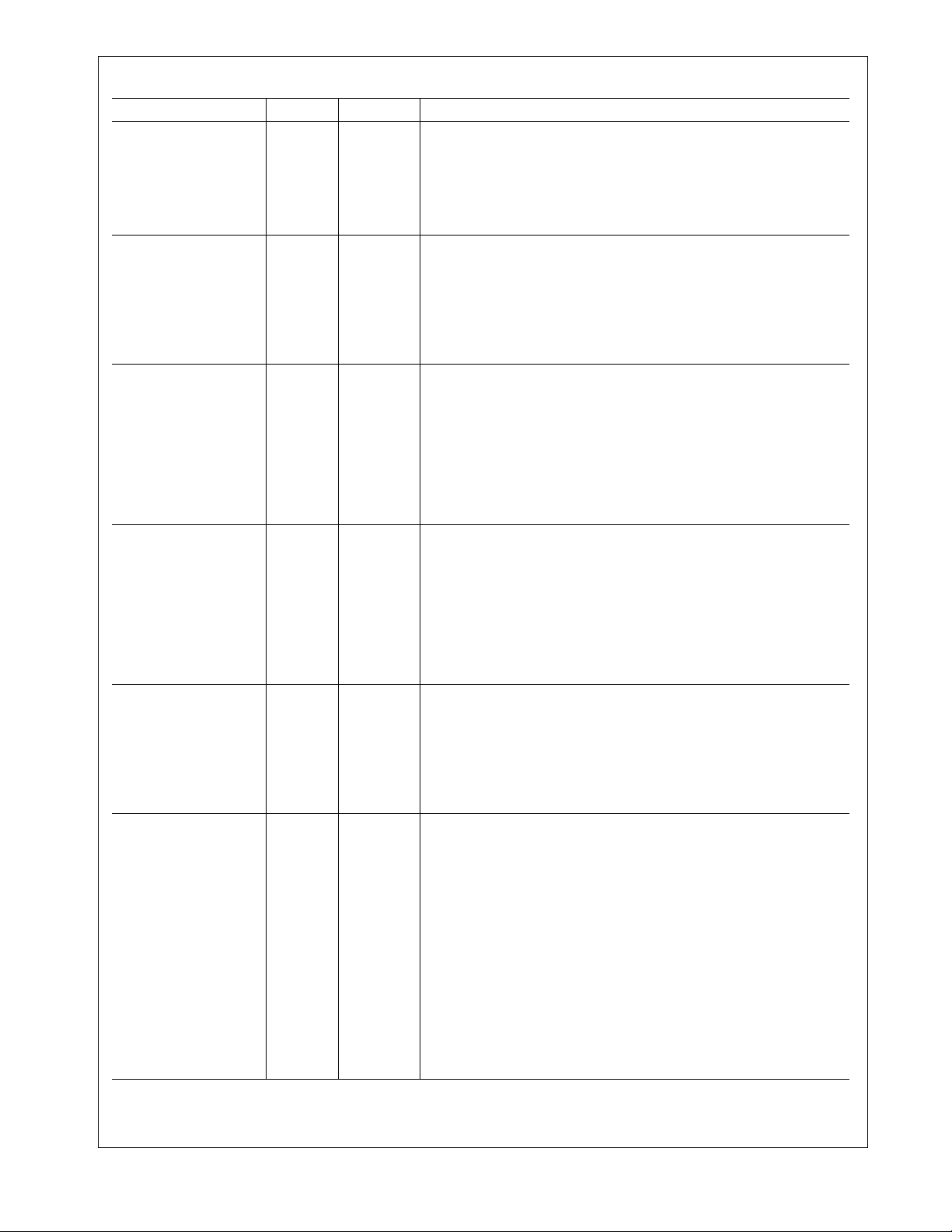

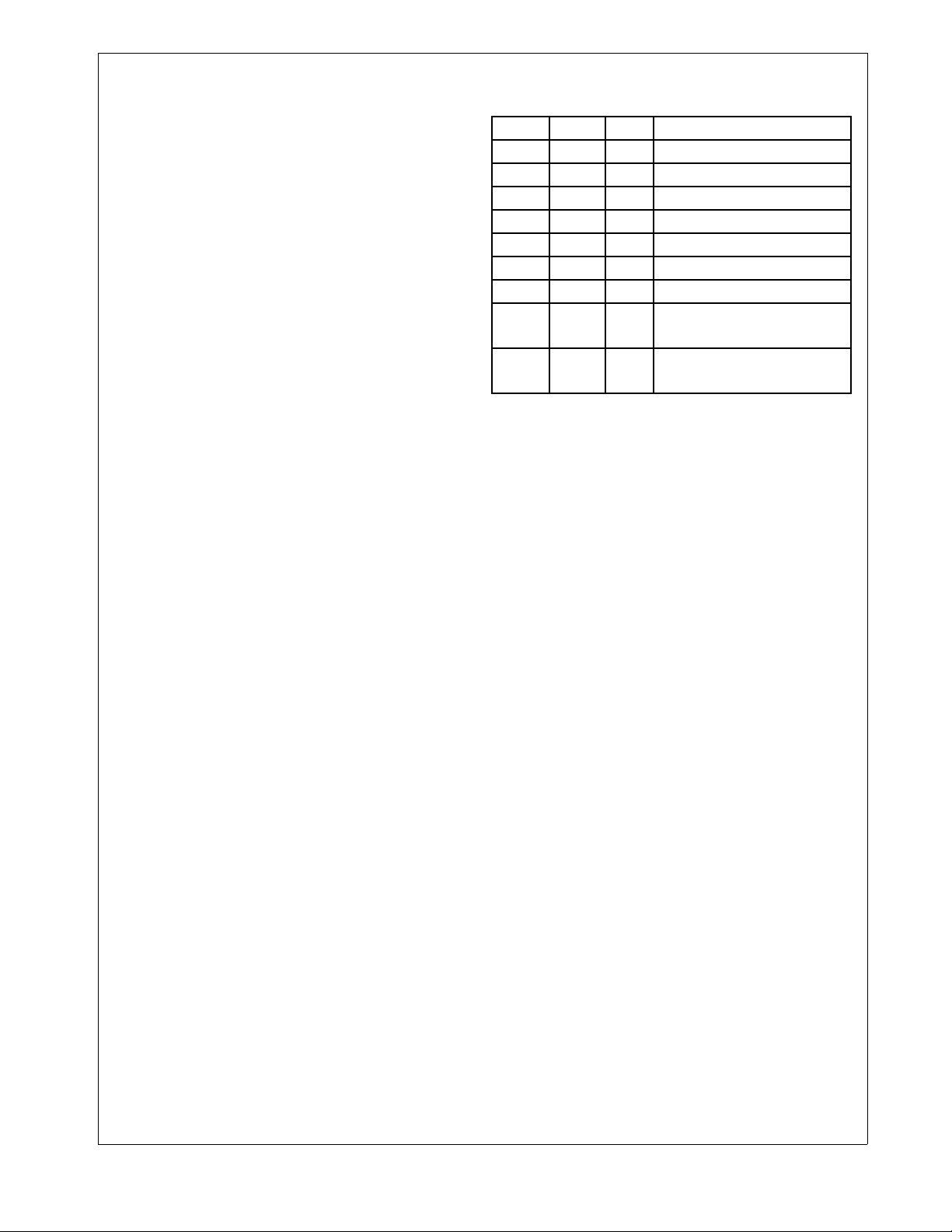

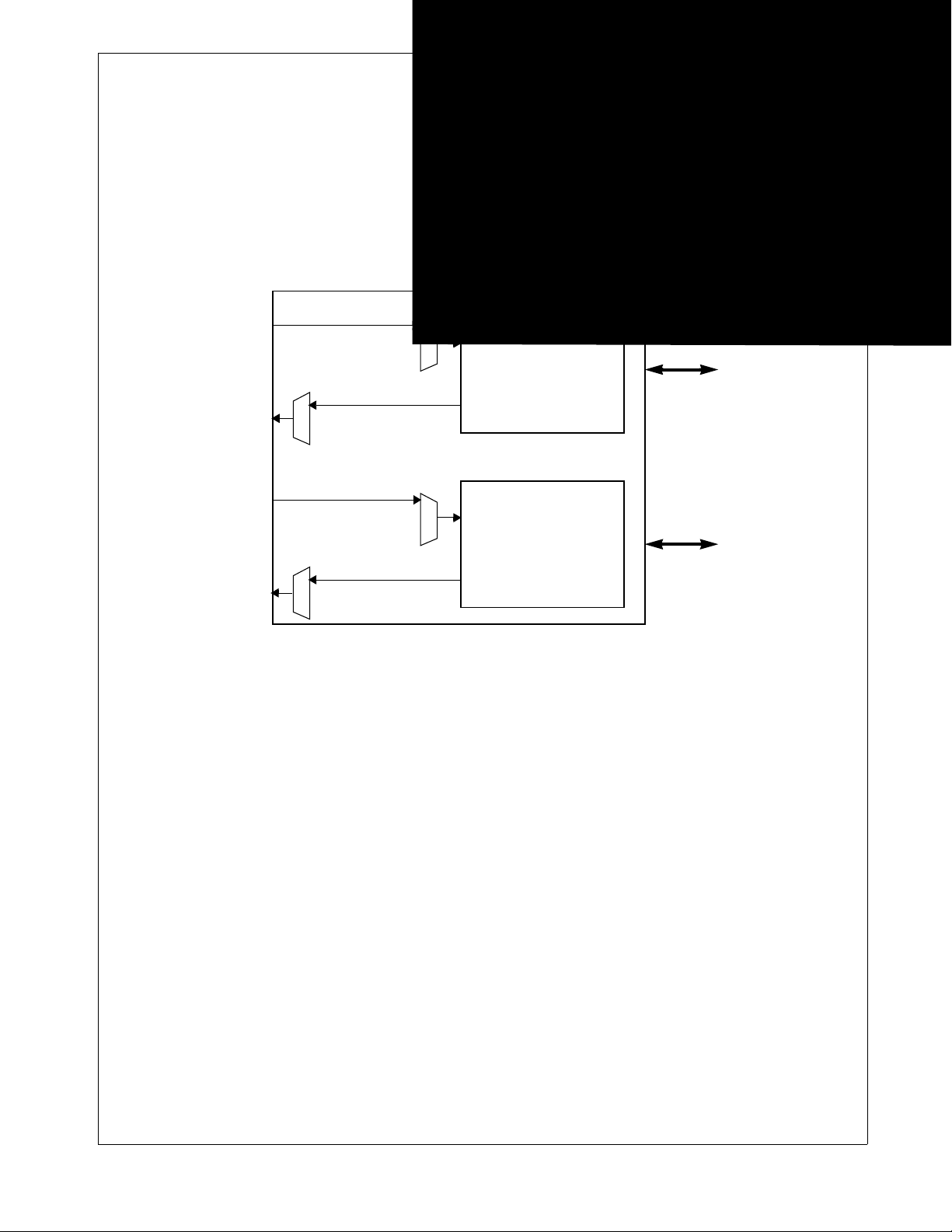

System Diagram

100BASE-FX

Port B

DP83849IF

Port A

Status

LEDs

Magnetics

Magnetics

100BASE-FX

MPU/CPU

MII/RMII/SNI

MAC

MII/RMII/SNI

MAC

25 MHz

Clock

Source

Typical Application

PHYTER is a registered trademark of National Semiconductor Corporation

© 2006 National Semiconductor Corporation www.national.com

1

10BASE-T

RJ-45

100BASE-TX

10BASE-T

RJ-45

100BASE-TX

or

or

DP83849IF

LED

DRIVERS

PORT A

MII/RMII/SNI

10/100 PHY CORE

PORT A

MII MANAGEMENT

INTERFACE

MDC

MANAGEMENT

INTERFACE

BOUNDARY

SCAN

MDIO

PORT B

MII/RMII/SNI

RXTXTX RX

10/100 PHY CORE

PORT B

LED

DRIVERS

LEDS

TPTD/FXTD±

TPRD/FXRD±

JTAG

TPTD/FXTD±

Figure 1. DP83849IF Functional Block Diagram

LEDS

TPRD/FXRD±

2 www.national.com

Table of Contents

1.0 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

1.1 Serial Management Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

1.2 MAC Data Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

1.3 Clock Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

1.4 LED Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

1.5 JTAG Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

1.6 Reset and Power Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

1.7 Strap Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

1.8 10 Mb/s and 100 Mb/s PMD Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

1.9 Special Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

1.10 Power Supply Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

1.11 Package Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

2.0 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2.1 Media Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

2.2 Auto-Negotiation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

2.2.1 Auto-Negotiation Pin Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2.2.2 Auto-Negotiation Register Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2.2.3 Auto-Negotiation Parallel Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

2.2.4 Auto-Negotiation Restart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

2.2.5 Enabling Auto-Negotiation via Software . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

2.2.6 Auto-Negotiation Complete Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

2.3 Auto-MDIX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

2.4 PHY Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

2.4.1 MII Isolate Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.5 LED Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

2.5.1 LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.5.2 LED Direct Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

2.6 Half Duplex vs. Full Duplex . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

2.7 Internal Loopback . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

2.8 BIST . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

3.0 MAC Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.1 MII Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

3.1.1 Nibble-wide MII Data Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.1.2 Collision Detect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.1.3 Carrier Sense . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.2 Reduced MII Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

3.3 10 Mb Serial Network Interface (SNI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

3.4 Single Clock MII Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

3.5 Flexible MII Port Assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

3.5.1 RX MII Port Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.5.2 TX MII Port Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

3.5.3 Common Flexible MII Port Configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

3.5.4 Strapped Extender or Media Converter Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.5.5 Notes and Restrictions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.6 802.3u MII Serial Management Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

3.6.1 Serial Management Register Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.6.2 Serial Management Access Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.6.3 Serial Management Preamble Suppression . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

3.6.4 Simultaneous Register Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

4.0 Architecture. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

4.1 100BASE-TX TRANSMITTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

4.1.1 Code-group Encoding and Injection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

4.1.2 Scrambler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

4.1.3 NRZ to NRZI Encoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

4.1.4 Binary to MLT-3 Convertor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

4.2 100BASE-TX RECEIVER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

4.2.1 Analog Front End . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

DP83849IF

3 www.national.com

4.2.2 Digital Signal Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

4.2.2.1 Digital Adaptive Equalization and Gain Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

4.2.2.2 Base Line Wander Compensation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

4.2.3 Signal Detect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

4.2.4 MLT-3 to NRZI Decoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

4.2.5 NRZI to NRZ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

4.2.6 Serial to Parallel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

4.2.7 Descrambler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

4.2.8 Code-group Alignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

4.2.9 4B/5B Decoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

4.2.10 100BASE-TX Link Integrity Monitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

4.2.11 Bad SSD Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

4.3 100BASE-FX Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

4.3.1 100BASE-FX Transmit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

4.3.2 100BASE-FX Receive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

4.3.3 Far-End Fault . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

4.4 10BASE-T TRANSCEIVER MODULE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

4.4.1 Operational Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

4.4.2 Smart Squelch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

4.4.3 Collision Detection and SQE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

4.4.4 Carrier Sense . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

4.4.5 Normal Link Pulse Detection/Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

4.4.6 Jabber Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

4.4.7 Automatic Link Polarity Detection and Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

4.4.8 Transmit and Receive Filtering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

4.4.9 Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

4.4.10 Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

5.0 Design Guidelines. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

5.1 TPI Network Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

5.2 Fiber Network Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

5.3 ESD Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

5.4 Clock In (X1) Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

5.5 Power Feedback Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

5.6 Power Down/Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

5.6.1 Power Down Control Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

5.6.2 Interrupt Mechanisms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

5.7 Energy Detect Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

5.8 Link Diagnostic Capabilities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

5.8.1 Linked Cable Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

5.8.1.1 Polarity Reversal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

5.8.1.2 Cable Swap Indication . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

5.8.1.3 100MB Cable Length Estimation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

5.8.1.4 Frequency Offset Relative to Link Partner . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

5.8.1.5 Cable Signal Quality Estimation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

5.8.2 Link Quality Monitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

5.8.2.1 Link Quality Monitor Control and Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

5.8.2.2 Checking Current Parameter Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

5.8.2.3 Threshold Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

5.8.3 TDR Cable Diagnostics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

5.8.3.1 TDR Pulse Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

5.8.3.2 TDR Pulse Monitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

5.8.3.3 TDR Control Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

5.8.3.4 TDR Results . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

6.0 Reset Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

6.1 Hardware Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

6.2 Full Software Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

6.3 Soft Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

7.0 Register Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

7.1 Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

7.1.1 Basic Mode Control Register (BMCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

DP83849IF

4 www.national.com

7.1.2 Basic Mode Status Register (BMSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

7.1.3 PHY Identifier Register #1 (PHYIDR1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

7.1.4 PHY Identifier Register #2 (PHYIDR2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

7.1.5 Auto-Negotiation Advertisement Register (ANAR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

7.1.6 Auto-Negotiation Link Partner Ability Register (ANLPAR) (BASE Page) . . . . . . . . . . . . . . . . 60

7.1.7 Auto-Negotiation Link Partner Ability Register (ANLPAR) (Next Page) . . . . . . . . . . . . . . . . . 61

7.1.8 Auto-Negotiate Expansion Register (ANER) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

7.1.9 Auto-Negotiation Next Page Transmit Register (ANNPTR) . . . . . . . . . . . . . . . . . . . . . . . . . . 63

7.1.10 PHY Status Register (PHYSTS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

7.1.11 MII Interrupt Control Register (MICR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

7.1.12 MII Interrupt Status and Misc. Control Register (MISR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

7.1.13 Page Select Register (PAGESEL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

7.2 Extended Registers - Page 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

7.2.1 False Carrier Sense Counter Register (FCSCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

7.2.2 Receiver Error Counter Register (RECR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

7.2.3 100 Mb/s PCS Configuration and Status Register (PCSR) . . . . . . . . . . . . . . . . . . . . . . . . . . 68

7.2.4 RMII and Bypass Register (RBR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

7.2.5 LED Direct Control Register (LEDCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

7.2.6 PHY Control Register (PHYCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

7.2.7 10 Base-T Status/Control Register (10BTSCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

7.2.8 CD Test and BIST Extensions Register (CDCTRL1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

7.2.9 Phy Control Register 2 (PHYCR2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

7.2.10 Energy Detect Control (EDCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

7.3 Link Diagnostics Registers - Page 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .78

7.3.1 100Mb Length Detect Register (LEN100_DET), Page 2, address 14h . . . . . . . . . . . . . . . . . 78

7.3.2 100Mb Frequency Offset Indication Register (FREQ100), Page 2, address 15h . . . . . . . . . 78

7.3.3 TDR Control Register (TDR_CTRL), Page 2, address 16h . . . . . . . . . . . . . . . . . . . . . . . . . . 79

7.3.4 TDR Window Register (TDR_WIN), Page 2, address 17h . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

7.3.5 TDR Peak Register (TDR_PEAK), Page 2, address 18h . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

7.3.6 TDR Threshold Register (TDR_THR), Page 2, address 19h . . . . . . . . . . . . . . . . . . . . . . . . . 80

7.3.7 Variance Control Register (VAR_CTRL), Page 2, address 1Ah . . . . . . . . . . . . . . . . . . . . . . 81

7.3.8 Variance Data Register (VAR_DATA), Page 2, address 1Bh . . . . . . . . . . . . . . . . . . . . . . . . 81

7.3.9 Link Quality Monitor Register (LQMR), Page 2, address 1Dh . . . . . . . . . . . . . . . . . . . . . . . . 82

7.3.10 Link Quality Data Register (LQDR), Page 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

8.0 Electrical Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

8.1 DC Specs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .84

8.2 AC Specs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .86

8.2.1 Power Up Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

8.2.2 Reset Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

8.2.3 MII Serial Management Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

8.2.4 100 Mb/s MII Transmit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

8.2.5 100 Mb/s MII Receive Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

8.2.6 100BASE-TX and 100BASE-FX MII Transmit Packet Latency Timing . . . . . . . . . . . . . . . . . 89

8.2.7 100BASE-TX and 100BASE-FX MII Transmit Packet Deassertion Timing . . . . . . . . . . . . . . 90

8.2.8 100BASE-TX Transmit Timing (tR/F & Jitter) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

8.2.9 100BASE-TX and 100BASE-FX MII Receive Packet Latency Timing . . . . . . . . . . . . . . . . . 92

8.2.10 100BASE-TX and 100BASE-FX MII Receive Packet Deassertion Timing . . . . . . . . . . . . . 92

8.2.11 10 Mb/s MII Transmit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

8.2.12 10 Mb/s MII Receive Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

8.2.13 10 Mb/s Serial Mode Transmit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

8.2.14 10 Mb/s Serial Mode Receive Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

8.2.15 10BASE-T Transmit Timing (Start of Packet) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

8.2.16 10BASE-T Transmit Timing (End of Packet) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

8.2.17 10BASE-T Receive Timing (Start of Packet) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

8.2.18 10BASE-T Receive Timing (End of Packet) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

8.2.19 10 Mb/s Heartbeat Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

8.2.20 10 Mb/s Jabber Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

8.2.21 10BASE-T Normal Link Pulse Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

8.2.22 Auto-Negotiation Fast Link Pulse (FLP) Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

8.2.23 100BASE-TX Signal Detect Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

8.2.24 100 Mb/s Internal Loopback Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

DP83849IF

5 www.national.com

8.2.25 10 Mb/s Internal Loopback Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

8.2.26 RMII Transmit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

8.2.27 RMII Receive Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

8.2.28 Single Clock MII (SCMII) Transmit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

8.2.29 Single Clock MII (SCMII) Receive Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

8.2.30 Isolation Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

8.2.31 CLK2MAC Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

9.0 Physical Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

DP83849IF

6 www.national.com

List of Figures

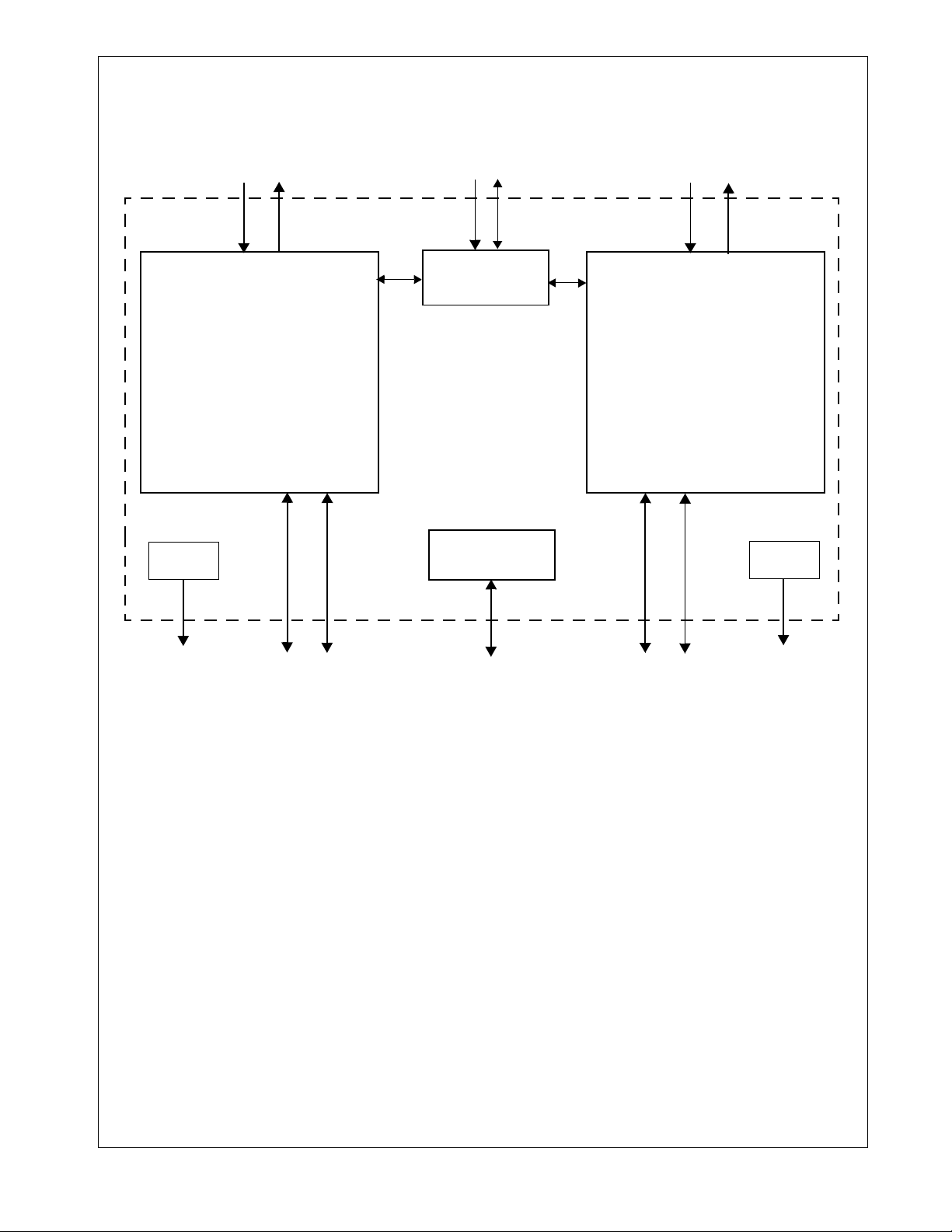

Figure 1. DP83849IF Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

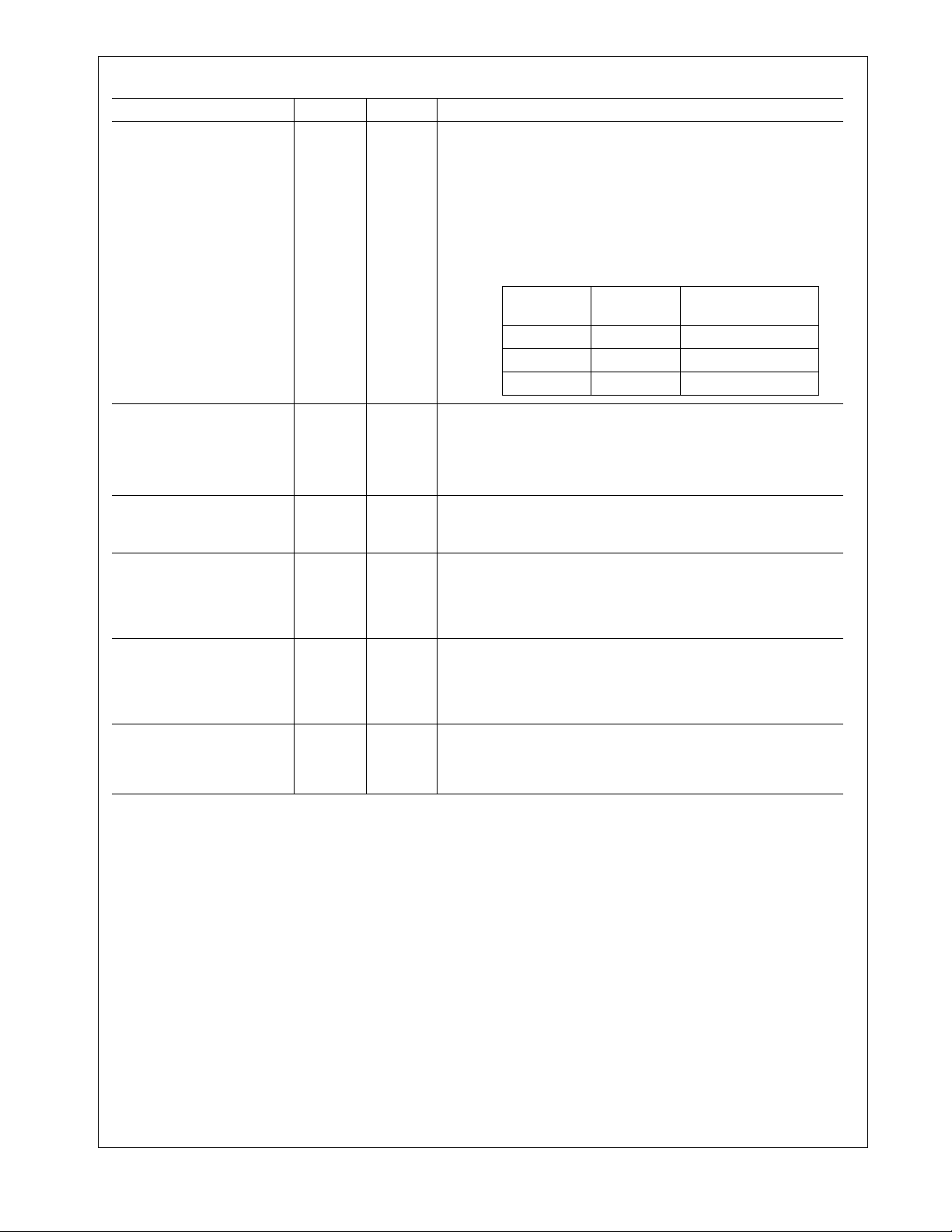

Figure 2. PHYAD Strapping Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 3. AN Strapping and LED Loading Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

Figure 4. MII Port Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

Figure 5. Typical MDC/MDIO Read Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

Figure 6. Typical MDC/MDIO Write Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Figure 7. 100BASE-TX Transmit Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Figure 8. 100BASE-TX Receive Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Figure 9. EIA/TIA Attenuation vs. Frequency for 0, 50, 100, 130 & 150 meters of CAT 5 cable . . . . . . . . . . . 36

Figure 10. 100BASE-TX BLW Event . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Figure 11. 10BASE-T Twisted Pair Smart Squelch Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Figure 12. 10/100 Mb/s Twisted Pair Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Figure 13. 100 Mb/s Fiber Pair Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Figure 14. Crystal Oscillator Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Figure 15. Power Feeback Connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

DP83849IF

7 www.national.com

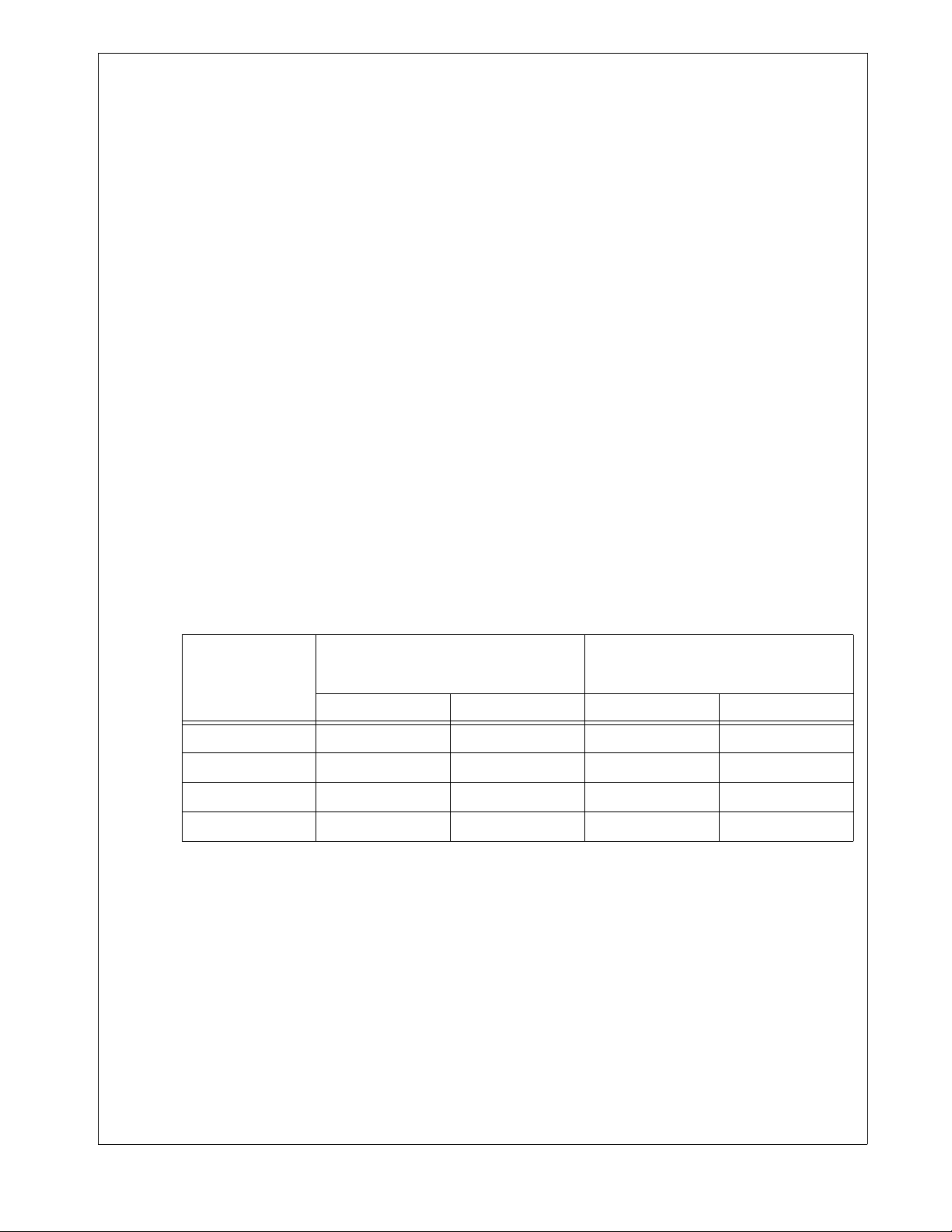

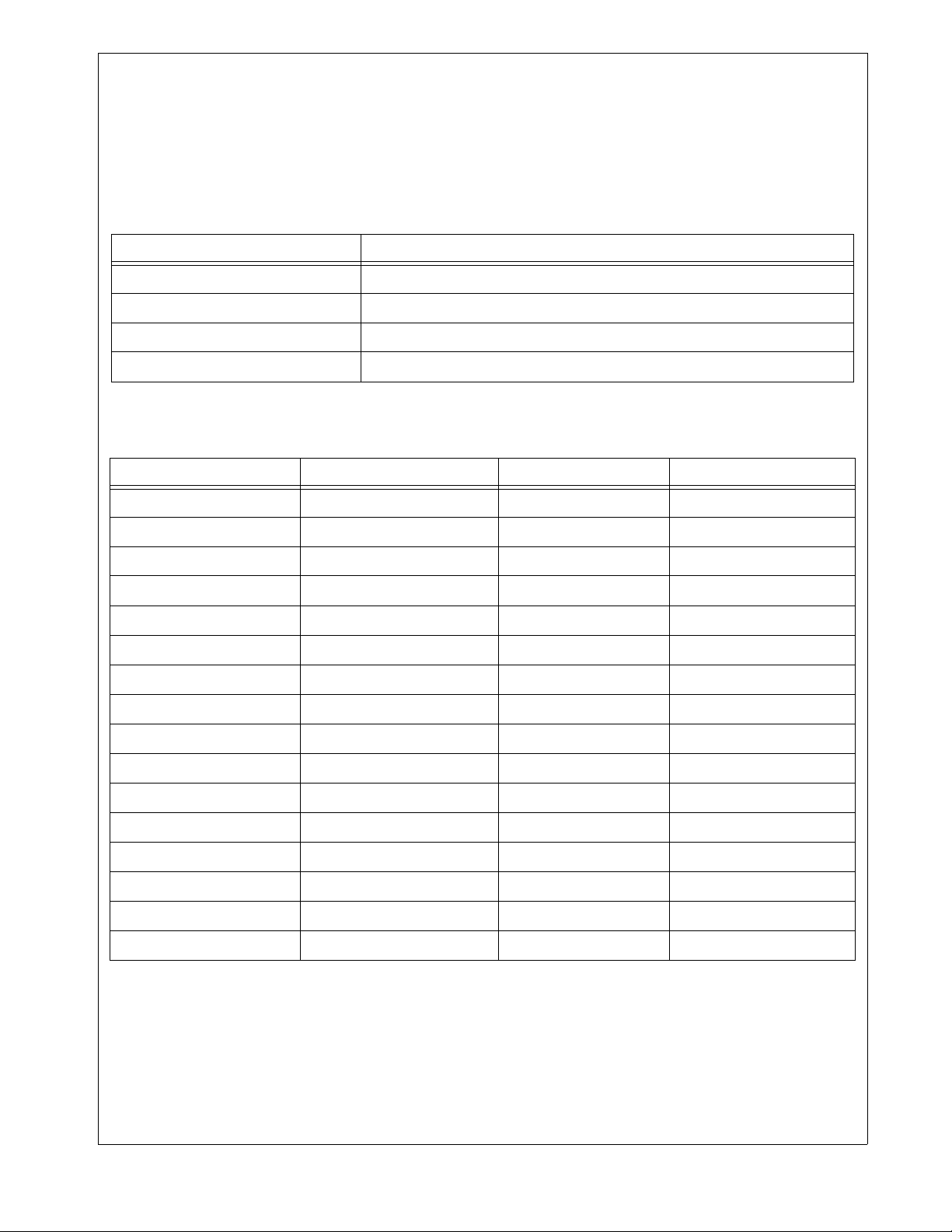

List of Tables

Table 1. Auto-Negotiation Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

Table 2. PHY Address Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

Table 3. LED Mode Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

Table 4. Supported packet sizes at +/-50ppm frequency accuracy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

Table 5. Supported SCMII packet sizes at +/-50ppm frequency accuracy . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Table 6. RX MII Port Mapping Controls . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

Table 7. RX MII Port Mapping Configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

Table 8. TX MII Port Mapping Controls . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

Table 9. TX MII Port Mapping Configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

Table 10. Common Flexible MII Port Configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

Table 11. Common Strapped Extender/Media Converter Mode Configurations . . . . . . . . . . . . . . . . . . . . . . .29

Table 12. Typical MDIO Frame Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

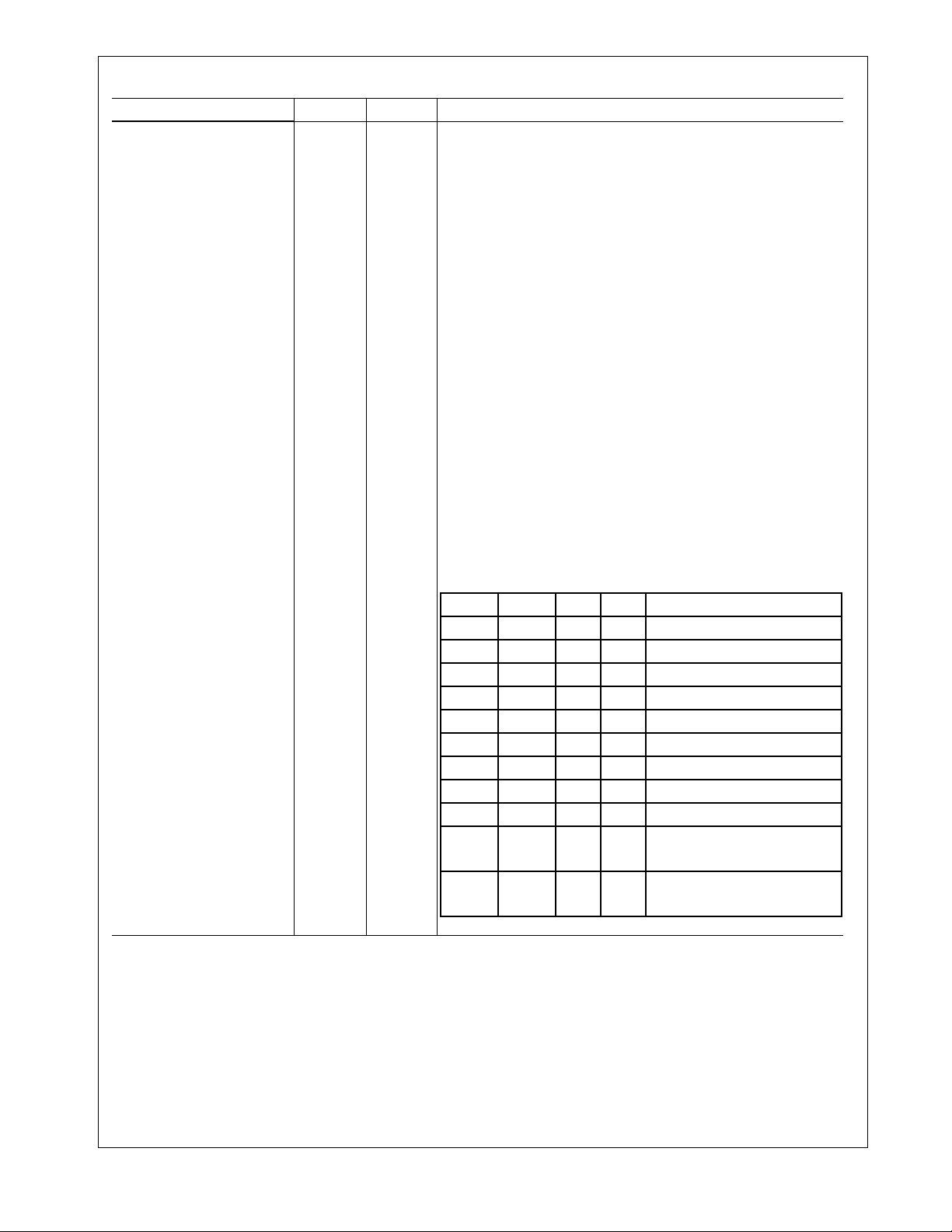

Table 13. 4B5B Code-Group Encoding/Decoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

Table 14. 25 MHz Oscillator Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

Table 15. 50 MHz Oscillator Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

Table 16. 25 MHz Crystal Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

Table 17. Link Quality Monitor Parameter Ranges . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

Table 18. Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

Table 19. Register Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

Table 20. Basic Mode Control Register (BMCR), address 00h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

Table 21. Basic Mode Status Register (BMSR), address 01h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

Table 22. PHY Identifier Register #1 (PHYIDR1), address 02h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

Table 23. PHY Identifier Register #2 (PHYIDR2), address 03h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

Table 24. Negotiation Advertisement Register (ANAR), address 04h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

Table 25. Auto-Negotiation Link Partner Ability Register (ANLPAR) (BASE Page), address 05h . . . . . . . . .60

Table 26. Auto-Negotiation Link Partner Ability Register (ANLPAR) (Next Page), address 05h . . . . . . . . . .61

Table 27. Auto-Negotiate Expansion Register (ANER), address 06h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

Table 28. Auto-Negotiation Next Page Transmit Register (ANNPTR), address 07h . . . . . . . . . . . . . . . . . . . .63

Table 29. PHY Status Register (PHYSTS), address 10h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

Table 30. MII Interrupt Control Register (MICR), address 11h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

Table 31. MII Interrupt Status and Misc. Control Register (MISR), address 12h . . . . . . . . . . . . . . . . . . . . . . .66

Table 32. Page Select Register (PAGESEL), address 13h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

Table 33. False Carrier Sense Counter Register (FCSCR), address 14h . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

Table 34. Receiver Error Counter Register (RECR), address 15h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

Table 35. 100 Mb/s PCS Configuration and Status Register (PCSR), address 16h . . . . . . . . . . . . . . . . . . . . .68

Table 36. RMII and Bypass Register (RBR), addresses 17h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .70

Table 37. LED Direct Control Register (LEDCR), address 18h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

Table 38. PHY Control Register (PHYCR), address 19h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

Table 39. 10Base-T Status/Control Register (10BTSCR), address 1Ah . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

Table 40. CD Test and BIST Extensions Register (CDCTRL1), address 1Bh . . . . . . . . . . . . . . . . . . . . . . . . . .76

Table 41. Phy Control Register 2 (PHYCR2), address 1Ch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

Table 42. Energy Detect Control (EDCR), address 1Dh . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .77

Table 43. 100Mb Length Detect Register (LEN100_DET), address 14h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .78

Table 44. 100Mb Frequency Offset Indication Register (FREQ100), address 15h . . . . . . . . . . . . . . . . . . . . . .78

Table 45. TDR Control Register (TDR_CTRL), address 16h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .79

Table 46. TDR Window Register (TDR_WIN), address 17h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .80

Table 47. TDR Peak Register (TDR_PEAK), address 18h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .80

Table 48. TDR Threshold Register (TDR_THR), address 19h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .80

Table 49. Variance Control Register (VAR_CTRL), address 1Ah . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .81

Table 50. Variance Data Register (VAR_DATA), address 1Bh . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .81

Table 51. Link Quality Monitor Register (LQMR), address 1Dh . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .82

Table 52. Link Quality Data Register (LQDR), address 1Eh . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .83

DP83849IF

8 www.national.com

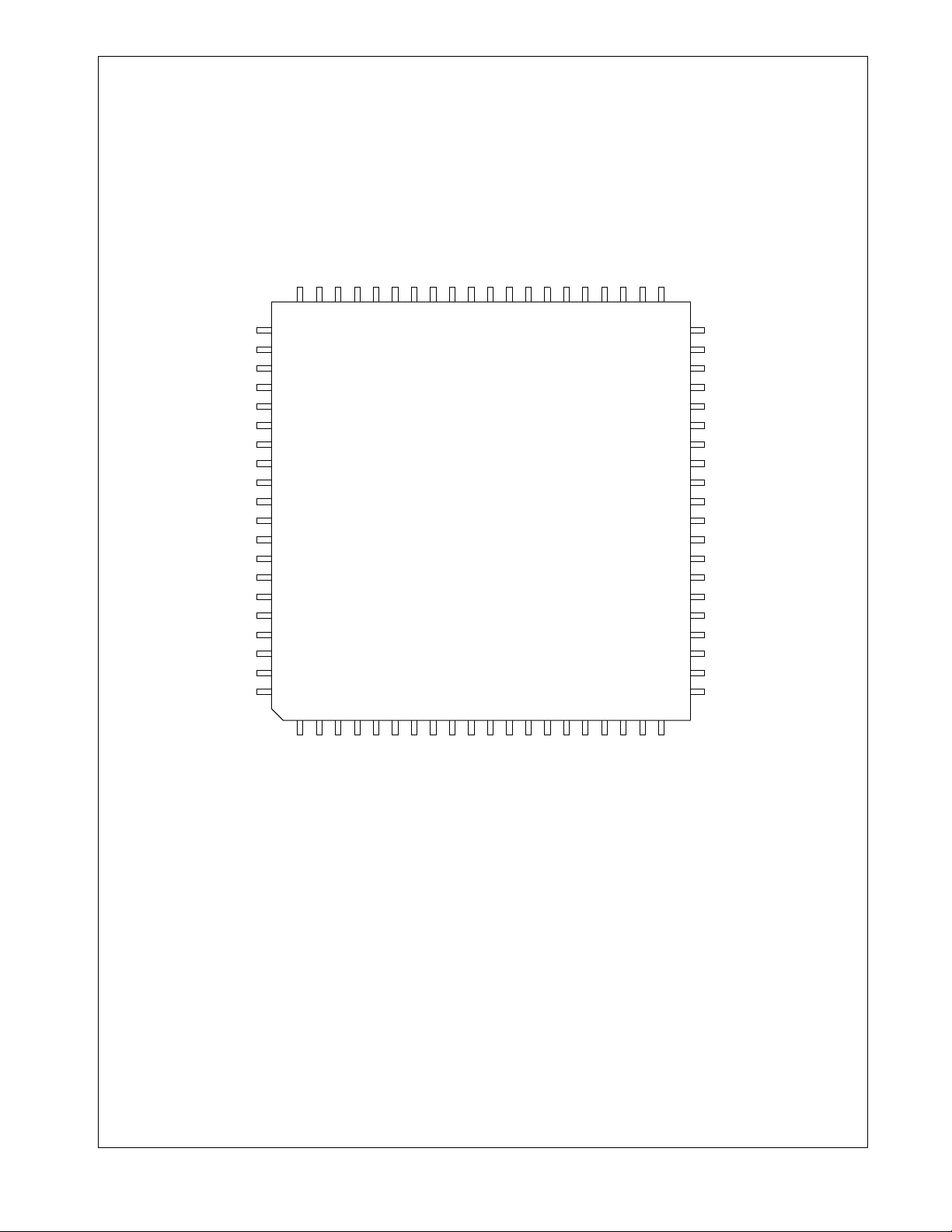

Pin Layout

C

DP83849IF

RX_ER_B/MDIX_EN_B

COL_B/FX_EN_B

RXD0_B/PHYAD3

RXD1_B/PHYAD4

RXD2_B/EXTENDER_EN

COREGND2

PFBIN4

RXD3_B/ED_EN_B

IOGND2

IOVDD2

TX_CLK_B

TX_EN_B

TXD0_B

TXD1_B

TXD2_B

TXD3_B/SNI_MODE_B

PWRDOWN_INT_B

LED_LINK_B/AN0_B

LED_SPEED_B/FXSD_B/AN1_B

LED_ACT/LED_COL/AN_EN_B

60595857565554535251504948474645444342

TCK

TDI

61

62

63

64

65

66

67

68

69

X2

70

X1

71

72

73

74

75

76

77

78

79

80

1

2

3

o

4

DP83849IFVS

5

6

7

8

9

1011121314151617181920

RS_B/CRS_DV_B/LED_CFG_B

RX_DV_B/MII_MODE_B

RX_CLK_B

IOGND3

IOVDD3

MDIO

MDC

CLK2MAC

RESET_N

TDO

TMS

TRSTN

IOGND4

IOVDD4

RX_CLK_A

RX_DV_A/MII_MODE_A

41

40

ANAGND4

39

TPRDM_B/FXRDM_B

38

TPRDP_B/FXRDP_B

37

CDGND2

36

TPTDM_B/FXTDM_B

35

TPTDP_B/FXTDP_B

34

PFBIN3

33

ANAGND3

32

RBIAS

31

PFBOUT

30

ANA33VDD

29

ANAGND2

28

PFBIN2

27

TPTDP_A/FXTDP_A

26

TPTDM_A/FXTDM_A

25

CDGND1

24

TPRDP_A/FXRDP_A

23

TPRDM_A/FXRDM_A

22

ANAGND1

LED_ACT/LED_COL/AN_EN_A

21

PFBIN1

COREGND1

COL_A/FX_EN_A

RXD0_A/PHYAD1

RXD1_A/PHYAD2

RX_ER_A/MDIX_EN_A

CRS_A/CRS_DV_A/LED_CFG_A

RXD2_A/CLK2MAC_DIS

IOVDD1

IOGND1

RXD3_A/ED_EN_A

TXD0_A

TXD1_A

TX_EN_A

TX_CLK_A

TXD2_A

PWRDOWN_INT_A

LED_LINK_A/AN0_A

TXD3_A/SNI_MODE_A

LED_SPEED_A/FXSD_A/AN1_A

Top View

NS Package Number VHB80A

9 www.national.com

1.0 Pin Descriptions

The DP83849IF pins are classified into the following interface categories (each interface is described in the sections

that follow):

— Serial Management Interface

— MAC Data Interface

— Clock Interface

— LED Interface

—JTAG Interface

— Reset and Power Down

— Strap Options

— 10/100 Mb/s PMD Interface

— Special Connect Pins

— Power and Ground pins

1.1 Serial Management Interface

Signal Name Type Pin # Description

MDC I 67 MANAGEMENT DATA CLOCK: Synchronous clock to the MDIO

management data input/output serial interface which may be asynchronous to transmit and receive clocks. The maximum clock rate is

25 MHz with no minimum clock rate.

MDIO I/O 66 MANAGEMENT DATA I/O: Bi-directional management instruc-

tion/data signal that may be sou rced by the stati on management en tity

or the PHY . This pin requires a 1.5 kΩ pullup resistor.

Note: Strapping pin option. Please s ee Section 1.7 for strap

definitions.

All DP83849IF signal pins are I/O cells regardless of the

particular use. The defi nition s below define the functiona lit y

of the I/O cells for each pin.

Type: I Input

Type: O Output

Type: I/O Input/Output

Type OD Open Drain

Type: PD,PU Internal Pulldown/Pullup

Type: S Strapping Pin (All strap pins have weak in-

ternal pu ll-ups or pull- downs. If the default

strap value is to be changed then an exter

nal 2.2 kΩ resistor should be used. Please

see Section 1.7 for details.)

DP83849IF

-

1.2 MAC Data Interface

Signal Name Type Pin # Description

TX_CLK_A

TX_CLK_B

TX_EN_A

TX_EN_B

TXD[3:0]_A

TXD[3:0]_B

O 12

50

I 13

49

I 17,16,15,14

45,46,47,48

MII TRANSMIT CLOCK: 25 MHz Transmit clock output in 100 Mb/s

mode or 2.5 MH z in 10 Mb/s m ode derived f rom the 25 MHz reference

clock.

Unused in RMII mo de. T he d evi ce uses the X1 reference cloc k in put

as the 50 MHz reference for both transmit and receive.

SNI TRANSMIT CLOCK: 10 MHz Transmit cloc k output in 10 Mb SNI

mode. The MAC should source TX_EN and TXD_0 using this clock.

MII TRANSMIT ENABLE: Active high input indic ates th e prese nce of

valid data inputs on TXD[3:0].

RMII TRANSMIT ENABLE: Active high input indicates the presence

of valid data on TXD[1:0].

SNI TRANSMIT ENABLE: Active high input indic ates the presence of

valid data on TXD_0.

MII TRANSMIT DATA: Transmit data MII input pins, TXD[3:0], that

accept data synchronous to the TX_CLK (2.5 MHz in 10 Mb/s mode

or 25 MHz in 100 Mb/s mode).

RMII TRANSMIT DATA: Transmit data RMII input pins, TXD[1:0],

that accept data synchronous to the 50 MHz reference clock.

SNI TRANSMIT DATA: Transmit data SNI input p in, T XD _0, that accept data synch ronous to the TX_CL K (10 MHz in 10 Mb/s SNI mode).

10 www.national.com

1.2 MAC Data Interface (Continued)

Signal Name Type Pin # Description

RX_CLK_A

RX_CLK_B

RX_DV_A

RX_DV_B

RX_ER_A

RX_ER_B

RXD[3:0]_A

RXD[3:0]_B

CRS_A/CRS_DV_A

CRS_B/CRS_DV_B

COL_A

COL_B

O 79

63

O 80

62

O 2

60

O 9,8,5,4

53,56,57,58

O 1

61

O 3

59

MII RECEIVE CLOCK: Provides the 25 MHz recovered receive

clocks for 100 Mb/s mode and 2.5 MHz for 10 Mb/s mode.

Unused in RMII mo de. T he d evi ce uses the X1 reference clock input

as the 50 MHz reference for both transmit and receive.

SNI RECEIVE CLOCK: Provides the 10 MHz recovered receive

clocks for 10 Mb/s SNI mode.

MII RECEIVE DATA VALID: Asserted high to i ndi ca te th at v al id d ata

is present on the corresponding RXD[3:0].

RMII RECEIVE DATA VALID: Asserted high to indicate that valid

data is present on the corresponding RXD[1:0]. This signal is not re

quired in RMII mode, since CRS_DV includes the RX_DV signal, but

is provided to allow simpler recovery of the Receive data.

This pin is not used in SNI mode.

MII RECEIVE ERROR: Asserted high synchronously to RX_CLK to

indicate that an invalid symbol has been detected within a received

packet in 100 Mb/s mode.

RMII RECEIVE ERROR: Asserted high synchronou sly to X1 when ever an invalid symbo l is detected, and CRS _DV is asserted in 100 Mb/s

mode. This pin is als o ass ert ed on d ete cti on of a Fa ls e C arr ier eve nt.

This pin is not required to be used by a MAC in RMII mode, since the

Phy is required to corrupt data on a receive error.

This pin is not used in SNI mode.

MII RECEIVE DATA: Nibble wide receive data signals driven syn-

chronously to the RX_CLK, 25 MHz for 100 Mb/s mode, 2.5 MHz for

10 Mb/s mode). RXD[3:0] signals contain valid data when RX_DV is

asserted.

RMII RECEIVE DATA: 2-bits receive data signals, RXD[1:0], driven

synchronousl y to the X1 clock, 50 MHz.

SNI RECEIVE DATA: Receive data signal, RXD_0, driven synchronously to the RX_CLK. RXD_0 contains valid data when CRS is asserted. RXD[3:1] are not used in this mode.

MII CARRIER SENSE: Asserted high to indicate th e receive me dium

is non-idle.

RMII CARRIER SENSE/RECEIVE DATA VALID: This signal combines the RMII Carrier and Receive Data Valid indications. For a detailed description of this signal, see the RMII Specification.

SNI CARRIER SENSE: Asserted high to in dicate the receive medium

is non-idle. It is used to fra me valid receive data on the RXD _0 sign al.

MII COLLISION DETECT: Asserted high to indicate detection of a

collision condition (simultaneous transmit and receive activity) in 10

Mb/s and 100 Mb/s Half Duplex Modes.

While in 10BASE-T Half Duplex mode with heartbeat enabled this pin

is also asserted for a duration of approximately 1µs at the end of

transmission to indicate heartbeat (SQE test).

In Full Duplex M ode, fo r 10 M b/s or 100 Mb /s op eration , this signa l is

always logic 0. There is no heartbeat function during 10 Mb/s full du

plex operation.

RMII COLLISION DETECT: Per the RMII Specification, no COL signal is required. The MAC will recover CRS from the CRS_DV signal

and use that along with its TX_EN signal to determine collision.

SNI COLLISION DETECT: Asserted high to indicate detection of a

collision condition (simultaneous transmit and receive activity) in 10

Mb/s SNI mode.

DP83849IF

-

-

11 www.national.com

1.3 Clock Interface

Signal Name Type Pin # Description

X1 I 70 CRYSTAL/OSCILLATOR INPUT: This pin i s the primary clock

X2 O 69 CRYSTAL OUTPUT: This pin is the primary clock reference out-

CLK2MAC O 68 CLOCK TO MAC:

reference input fo r the DP83849IF and must be co nnected to a 25

MHz 0.005% (

either an external crys tal resonator connecte d across pins X1 and

X2, or an external CMO S-level oscil lator sourc e connec ted to pin

X1 only.

RMII REFERENCE CLOCK: This pin is the primary clock reference input for the RMII mode and mu st be connected to a 50 MHz

0.005% (

put to connect to an external 25 MHz crystal resonator device.

This pin must be left unconnected if an ex tern al C MOS os c ill ato r

clock source is used.

In MII mode, this pin provides a 25 MHz clock output to the system.

In RMII mode, this pin prov ides a 50 MHz cloc k outpu t to the sys tem.

This allows other devices to use the reference clock from the

DP83849IF without requiring additional clock sources.

If the system does not require the CLK2MAC signal, the

CLK2MAC output should be disabled via the CLK2MAC disable

strap.

+50 ppm) clock source. The DP83849IF supports

+50 ppm) CMOS-level oscillator source.

DP83849IF

1.4 LED Interface

The DP83849IF supports three configurable LED pins. The

LEDs support two operational modes which are selected

by the LED mode s trap an d a thi rd ope rationa l mod e whic h

Signal Name Type Pin # Description

LED_LINK_A

LED_LINK_B

LED_SPEED_A

LED_SPEED_B

LED_ACT/LED_COL_A

LED_ACT/LED_COL_B

I/O 19

43

I/O 20

42

I/O 21

41

LINK LED: In Mode 1, this pin indicates the status of the LINK.

The LED will be ON when Link is good.

LINK/ACT LED: In Mode 2 and Mode 3, this pi n indicates tra nsmit

and receive activity in addition to the status of the Link. The LED

will be ON when Link is good. It will blink when the transmitter or

receiver is active.

SPEED LED: The LED is ON when device is i n 100 Mb/s and OFF

when in 10 Mb/s. Functionality of this LED is independ ent of mode

selected.

ACTIVITY LED: In Mode 1, this pin is the A ctivity L ED which i s

ON when activity is present on either Transmit or Receive.

COLLISION/DUPLEX LED: In Mode 2, this pin by default indicates Collision detection. For Mode 3, this LED output may be

programmed to indicate Full-duplex status instead of Collision.

is register configurable. The definitions for the LEDs for

each mode are detailed below. Since the LEDs are also

used as strap options, the polarity of the LED output is

dependent on whether the pin is pulled up or down.

12 www.national.com

1.5 JTAG Interface

Signal Name Type Pin # Description

TCK I, PU 72 TEST CLOCK

This pin has a weak internal pullup.

TDO O 73 TEST OUTPUT

TMS I, PU 74 TEST MODE SELECT

This pin has a weak internal pullup.

TRSTN I, PU 75 TEST RESET Active low test reset.

This pin has a weak internal pullup.

TDI I, PU 76 TEST DATA INPUT

This pin has a weak internal pullup.

1.6 Reset and Power Down

Signal Name Type Pin # Description

RESET_N I, PU 71 RESET: Active Low input that initializes or re-initializes the

PWRDOWN_INT_A

PWRDOWN_INT_B

I, PU 18

44

DP83849IF. Asserting this pin low for at least 1 µs will force a re

set process to occur. All internal registers will re-initialize to their

default stat es as sp eci fie d for ea ch bi t in th e Regi ste r Bloc k section. All strap options are re-initialized as well.

The default function of this pin is POWER DOWN.

POWER DOWN: The pin is an active low input in this mode and

should be asserted low to put the device in a Power Down mode.

INTERRUPT: The pin is an open drain output in thi s mode and will

be asserted low when a n in terru pt co nd itio n oc c urs . Alth oug h the

pin has a weak internal pull-up, some applications may require an

external pull-up resi ster. R egister a ccess i s requi red for th e pin to

be used as an in terrupt me chanism. Se e

Mechanism for more details on the interrupt mechanisms.

Section 5.6.2 Interrupt

DP83849IF

-

1.7 Strap Options

The DP83849IF uses many of the functional pins as strap

options. The values of these pins are sampled during reset

and used to strap the device into specific modes of opera

tion. The strap option pin assignments are defined below.

The functional pin name is indicated in parentheses.

Signal Name Type Pin # Description

PHYAD1 (RXD0_A)

PHYAD2 (RXD1_A)

PHYAD3 (RXD0_B)

PHYAD4 (RXD1_B)

S, O, PD

S, O, PD

S, O, PD

S, O, PD

58

57

4

PHY ADDRESS [4:1]: The DP83849IF provides four PHY address pins, the state of which are la tch ed into the PHYC TRL re g-

5

ister at system Hardware-Reset. Phy Address[0] selects betwe en

ports A and B.

The DP83849IF supports PHY Address strapping for Port A even

values 0 (<0000_0>) through 30 (<1111_0>). Port B will be

strapped to odd values 1 (<0000_1>) through 31 (<1111_1>).

PHYAD[4:1] pins have weak internal pull-down resistors.

A 2.2 kΩ resistor should be used for pull-down or pull-up to

change the default strap option. If the default option is

required, then there is no need for external pull-up or pull

down resistors. Since these pins may have alternate func

tions after reset is deasserted, they should not be connected directly to VCC or GND.

-

13 www.national.com

1.7 Strap Options (Continued)

x

x

Signal Name Type Pin # Description

FX_EN_A (COL_A)

FX_EN_B (COL_B)

AN_EN

(LED_ACT/LED_COL_A)

AN1_A (LED_SPEED_A)

AN0_A (LED_LINK_A)

AN_EN

(LED_ACT/LED_COL_B)

AN1_B (LED_SPEED_B)

AN0_B (LED_LINK_B)

S, O, PU

S, I, PD

59

21

20

19

41

42

43

3

FX ENABLE: Default is to disable 100BASE-FX (Fiber) mode.

This strapping option enables 100BASE-FX. An external pull-up

will enable 100BASE-FX mode.

Auto-Negotiation Enable: When high, thi s enable s Auto-Negot iation with the capab ility se t by AN0 and AN1 pin s. When low , this

puts the part into Forced Mode with the capability set by AN0 and

AN1 pins.

AN0 / AN1: These input pins control the forced or advertised operating mode of the DP83849IF according to the following table.

The value on these pins is set by connecting the input pins to

GND (0) or V

NEVER be connected directly to GND or VCC.

Fiber Mode Duplex Selection: If Fiber mode is strapped using

the FX_EN pi n , t he A N0 st ra p va lu e i s u s ed to s el e ct Hal f or F u ll

Duplex. AN_EN and AN1are ignored if FX_EN is asserted, since

Fiber mode is 100Mb on ly and does not s upport Auto-Negotia tion.

The value set at this input is latc hed into the D P83 84 9IF at Ha rdware-Reset.

The float/pull-down status of these pins are latched into the Basic

Mode Control Register and the Auto_Negotiation Advertisement

Register during Hardware-Reset.

The default is 0111 si nce the FX_EN pin has an i nternal pull-down

and the Auto-Negotiation pins have internal pull-ups.

(1) through 2.2 kΩ resistors. These pin s should

CC

DP83849IF

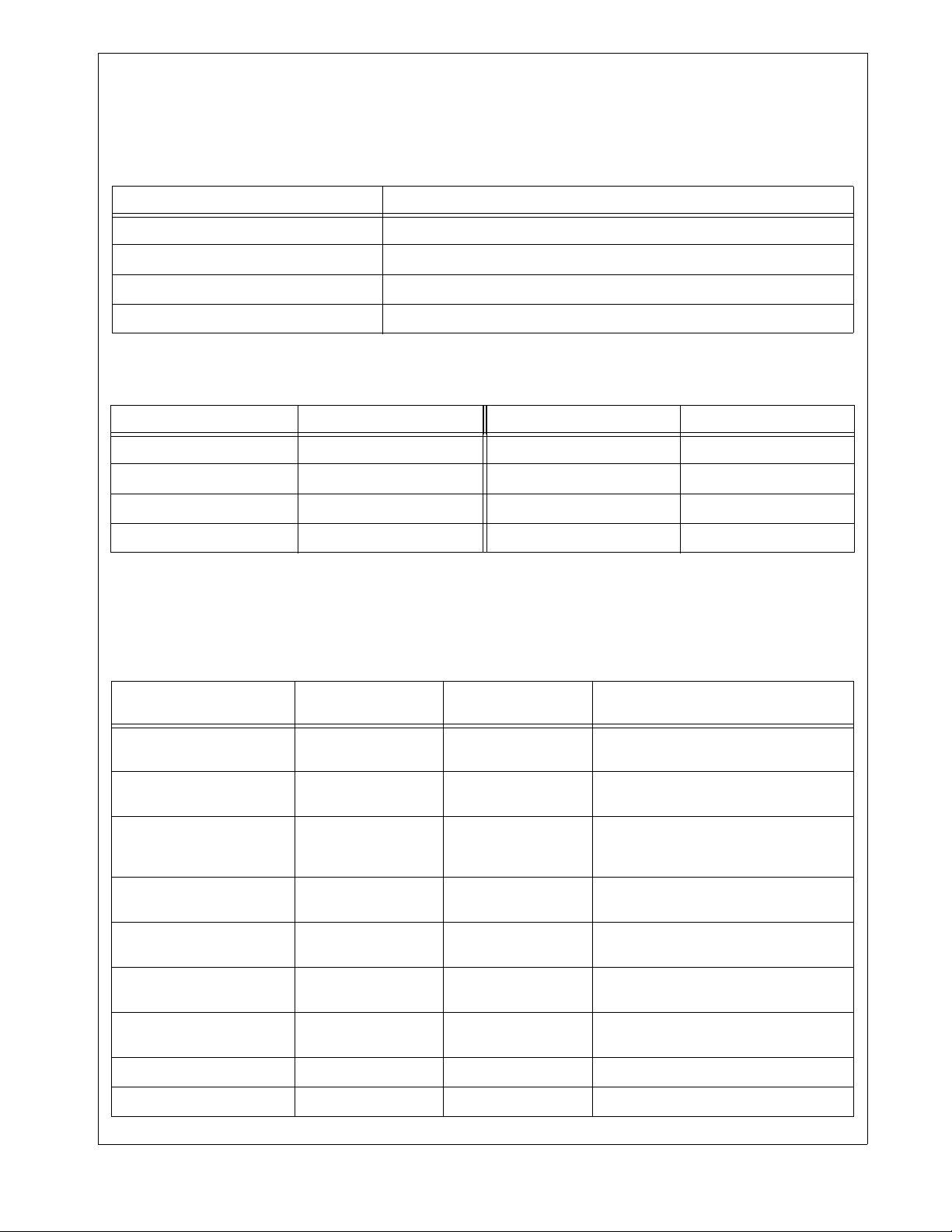

FX_EN AN_EN AN1 AN0 Forced Mode

0 0 0 0 10BASE-T, Half-Duplex

0 0 0 1 10BASE-T, Full-Duplex

0 0 1 0 100BASE-TX, Half-Duplex

0 0 1 1 100BASE-TX, Full-Duplex

1 X X 0 100BASE-FX, Half-Duplex

1 X X 1 100BASE-FX, Full-Duplex

FX_EN AN_EN AN1 AN0 Advertised Mode

0 1 0 0 10BASE-T, Half/Full-Duplex

0 1 0 1 100BASE-TX, Half/Full-Duple

0 1 1 0 10BASE-T Half-Duplex

100BASE-TX, Half-Duplex

0 1 1 1 10BASE-T, Half/Full-Duplex

100BASE-TX, Half/Full-Duple

14 www.national.com

1.7 Strap Options (Continued)

Signal Name Type Pin # Description

MII_MODE_A (RX_DV_A)

SNI_MODE_A (TXD3_A)

MII_MODE_B (RX_DV_B)

SNI_MODE_B (TXD3_B)

S, O, PD 80

17

62

45

DP83849IF

MII MODE SELECT: This strapping option pair determines the

operating mode of the MAC Data Interface. Default operation

(No pull-ups) will ena ble no rmal M II Mo de of o peratio n. Strappin g

MII_MODE high will c ause th e dev ice to be in RM II or SNI mo des

of operation, determined by the status of the SNI_MODE strap.

Since the pins include internal pull-downs, the default values are

0. Both MAC Data Interface s mus t ha ve the ir RMII M od e setti ngs

the same, i.e. both in RMII mode or both not in RMII mode.

The following table details the configurations:

MII_MODE SNI_MODE MAC Interface

0 X MII Mode

1 0 RMII Mode

1 1 10 Mb SNI Mode

LED_CFG_A

(CRS_A/CRS_DV_A)

LED_CFG_B

(CRS_B/CRS_DV_B)

MDIX_EN_A (RX_ER_A)

MDIX_EN_B (RX_ER_B)

ED_EN_A (RXD3_A)

ED_EN_B (RXD3_B)

CLK2MAC_DIS (RXD2_A) S, O, PD 8 Clock to MAC Disable: This strapp ing option disab les (floats) the

EXTENDER_EN (RXD2_B) S, O, PD 56 Extender Mode Enab le: This strapping option en abl es Ext ender

S, O, PU 1

S, O, PU 2

S, O, PD 9

61

60

53

LED CONFIGURATION: This strapping option determines the

mode of operation of the LED pin s. Default is Mode 1. Mode 1 and

Mode 2 can be controlle d via the strap opt ion. All mode s are co n

figurable via register access.

See Table 3 on page 21 for LED Mode Selection.

MDIX ENABLE: Default is to enable MDIX. Thi s strap pin g option

disables Auto-MDIX. An external pull-down will disable AutoMDIX mode.

Energy Detect ENABLE: Default is to disable Energy Detect

mode. This strapping option enables Energy Detect mode for the

port. In Energy Detect mode, the device will initially be in a lowpower state until de tecting a ctivity on the wire . An extern al pull-u p

will enable Energy Detect mode.

CLK2MAC pin. Default is to enable CLK2 MAC output. An external

pullup will disa ble (float) t he CLK2MAC pin. If th e system does not

require the CLK2MAC si gnal, the CLK2MAC output should be dis

abled via this strap option.

Mode for both ports. When enabled, the strap will enable Single

Clock MII TX and RX modes unless RMII Mode is also strapped.

SNI Mode cannot be strapped if Extender Mode is strapped.

Mode

-

-

15 www.national.com

1.8 10 Mb/s and 100 Mb/s PMD Interface

Signal Name Type Pin # Description

TPTDM_A/FXTDM_A

TPTDP_A/FXTDP_A

TPTDM_B/FXTDM_B

TPTDP_B/FXTDP_B

TPRDM_A/FXRDM_A

TPRDP_A/FXRDP_A

TPRDM_B/FXRDM_B

TPRDP_B/FXRDP_B

FXSD_A

(LED_SPEED_A/AN1_A)

FXSD_B

(LED_SPEED_B/AN1_B)

I/O 26

I/O 23

I 20

27

36

35

24

39

38

42

DP83849IF

10BASE-T or 100BASE-TX or 100BASE-FX Transmit Data

In 10BASE-T or 100BASE-TX: Differential common driver transmit output (PMD Ou tput Pair). Th ese different ial ou tputs are a utomatically configured to either 10BASE-T or 100BASE-TX

signaling.

In Auto-MDIX mode of opera tion, this pa ir can be used as the Receive Input pair.

In 100BASE-FX mode, this pair becomes the 100BASE-FX

Transmit pair.

These pins require 3.3V bias for operation.

10BASE-T or 100BASE-TX or 100BASE-FX Receive Data

In 10BASE-T or 100BASE-TX: Differenti al receiv e input (PMD In put Pair). These differential in puts are autom atically configured to

accept either 100BASE-TX or 10BASE-T signaling.

In Auto-MDIX mode of operation, this pair can be used as the

Transmit Output pair.

In 100BASE-FX mode, this pair becomes the 100BASE-FX

Receive pair.

These pins require 3.3V bias for operation.

FX Signal Detect: This pin provides the Signal Detect input for

100BASE-FX mode.

1.9 Special Connections

Signal Name Type Pin # Description

RBIAS I 32 Bias Resistor Connection: A 4.87 kΩ 1% resistor should be con -

PFBOUT O 31 Power Feedback Output: Parallel caps, 10µ F and 0.1µF, should

PFBIN1

PFBIN2

PFBIN3

PFBIN4

I 7

28

34

54

nected from RBIAS to GND.

be placed close to the PFBOUT. Connect this pin to PFBIN1 (pin

13), PFBIN2 (pin 27), PFBIN3 (pin35), PFBIN4 (pin 49). See

Section 5.5 for proper placement pin.

Power Feedback Input: These pins are fed with power from

PFBOUT pin. A small capacitor of 0.1µF should be connected

close to each pin.

Note: Do not supply power to these pins other than from

PFBOUT.

1.10 Power Supply Pins

Signal Name Pin # Description

IOVDD1, IOVDD2, IOVDD3,

IOVDD4

IOGND1, IOGND2,

IOGND3, IOGND4

COREGND1, COREGND2 6,55 Core Ground

CDGND1, CDGND2 25,37 CD Ground

ANA33VDD 30 Anal og 3.3V Supply

ANAGND1, ANAGND2,

ANAGND3, ANAGND4

11,51,65,78 I/O 3.3V Supply

10,52,64,77 I/O Ground

22,29,33,40 Analog Ground

16 www.national.com

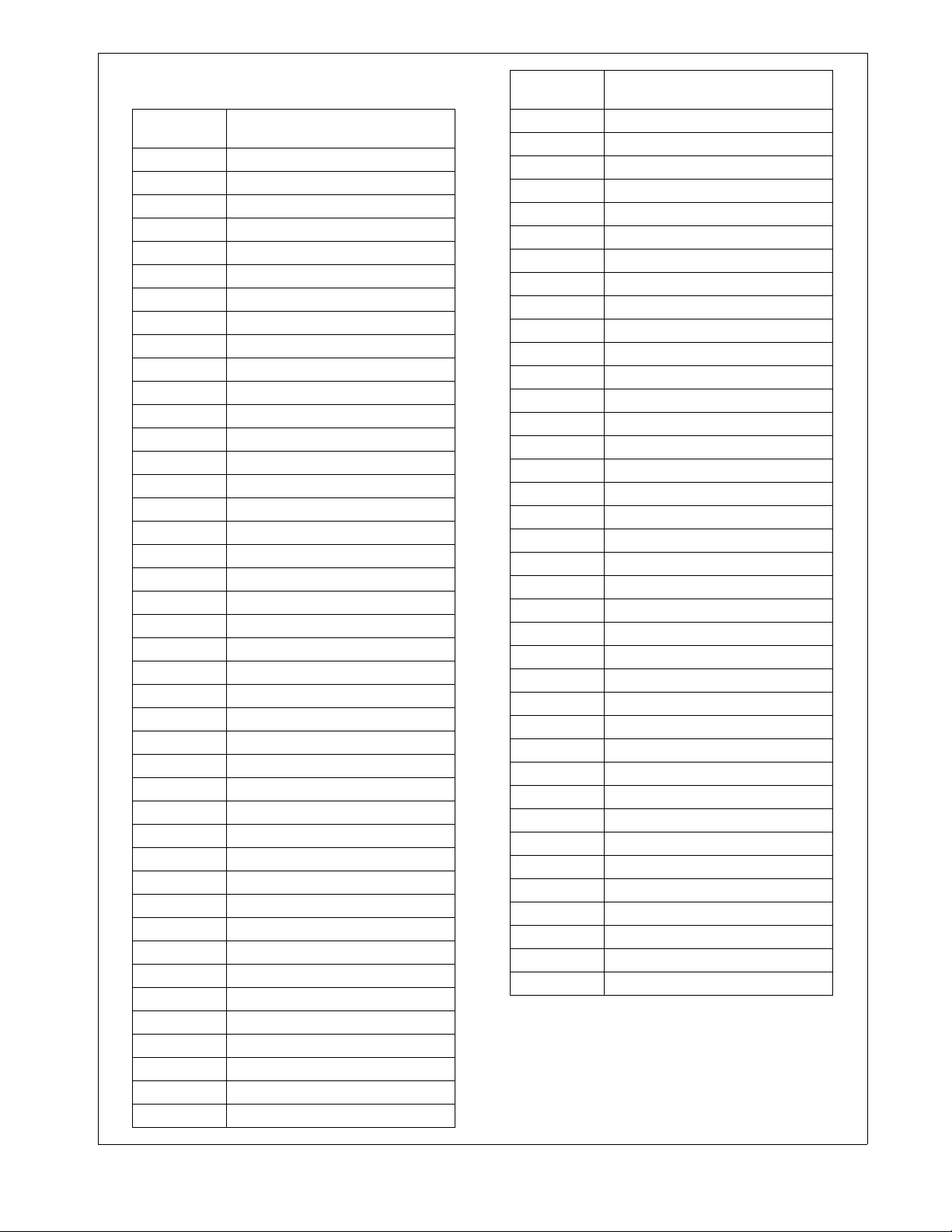

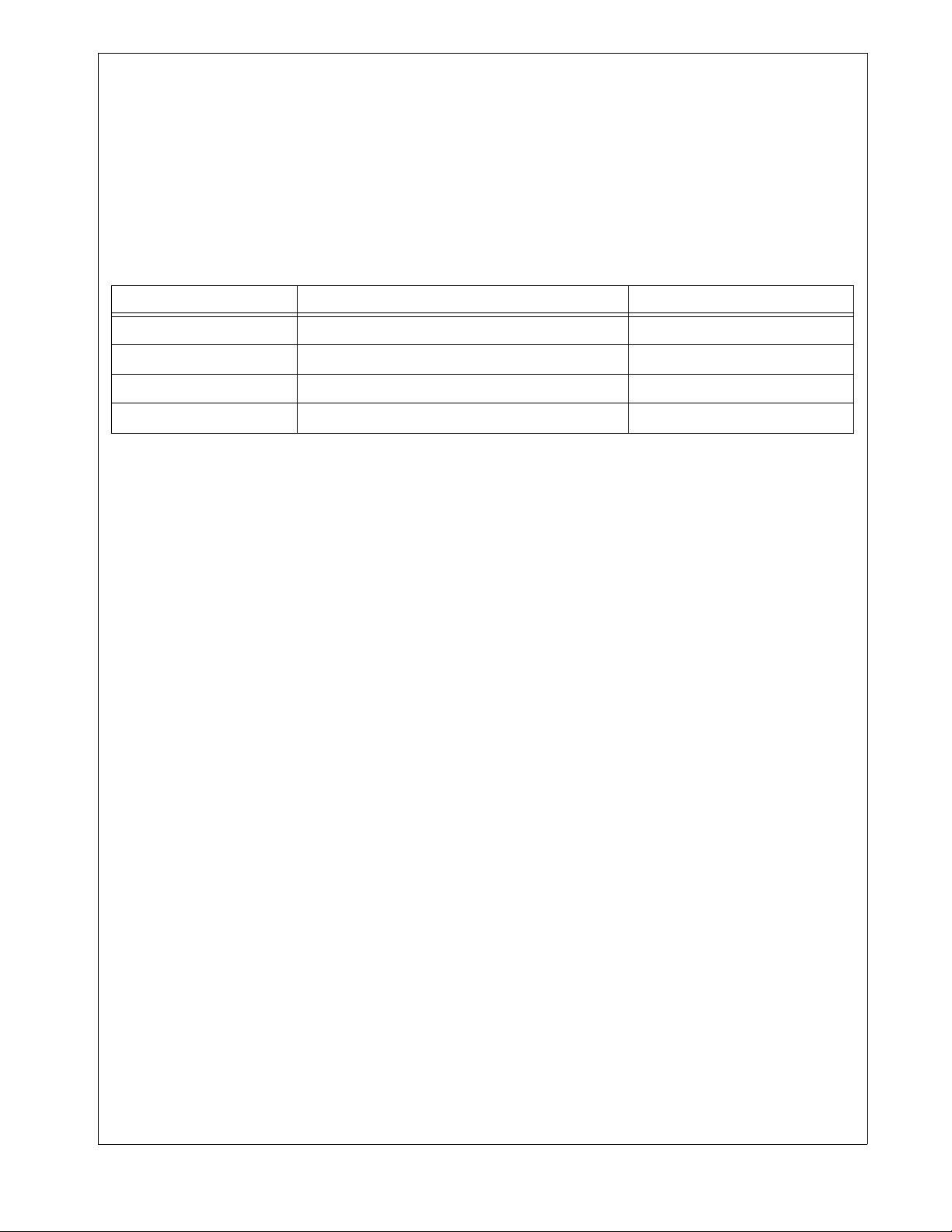

1.11 Package Pin Assignments

DP83849IF

VHB80A Pin #Pin Name

VHB80A Pin #Pin Name

1 CRS_A/CRS_DV_A/LED_CFG_A

2 RX_ER_A/MDIX_EN_A

3 COL_A/FX_EN_A

4 RXD0_A/PHYAD1

5 RXD1_A/PHYAD2

6 COREGND1

7 PFBIN1

8 RXD2_A/CLK2MAC_DIS

9 RXD3_A/ED_EN_A

10 IOGND1

11 IOVDD1

12 TX_CLK_A

13 TX_EN_A

14 TXD0_A

15 TXD1_A

16 TXD2_A

17 TXD3_A/SNI_MODE_A

18 PWRDOWN_INT_A

19 LED_LINK_A/AN0_A

20 LED_SPEED_A/FXSD_A/AN1_A

21 LED_ACT/LED_COL/AN_EN_A

22 ANAGND1

23 TPRDM_A/FXRDM_A

24 TPRDP_A/FXRDP_A

25 CDGND1

26 TPTDM_A/FXTDM_A

27 TPTDP_A/FXTDP_A

28 PFBIN2

29 ANAGND2

30 ANA33VDD

31 PFBOUT

32 RBIAS

33 ANAGND3

34 PFBIN3

35 TPTDP_B/FXTDP_B

36 TPTDM_B/FXTDM_B

37 CDGND2

38 TPRDP_B/FXRDP_B

39 TPRDM_B/FXRDM_B

40 ANAGND4

41 LED_ACT/LED_COL/AN_EN_B

42 LED_SPEED_B/FXSD_B/AN1_B

43 LED_LINK_B/AN0_B

44 PWRDOWN_INT_B

45 TXD3_B/SNI_MODE_B

46 TXD2_B

47 TXD1_B

48 TXD0_B

49 TX_EN_B

50 TX_CLK_B

51 IOVDD2

52 IOGND2

53 RXD3_B/ED_EN_B

54 PFBIN4

55 COREGND2

56 RXD2_B/EXTENDER_EN

57 RXD1_B/PHYAD4

58 RXD0_B/PHYAD3

59 COL_B/FX_EN_B

60 RX_ER_B/MDIX_EN_B

61 CRS_B/CRS_DV_B/LED_CFG_B

62 RX_DV_B/MII_MODE_B

63 RX_CLK_B

64 IOGND3

65 IOVDD3

66 MDIO

67 MDC

68 CLK2MAC

69 X2

70 X1

71 RESET_N

72 TCK

73 TDO

74 TMS

75 TRSTN

76 TDI

77 IOGND4

78 IOVDD4

79 RX_CLK_A

80 RX_DV_A/MII_MODE_A

17 www.national.com

2.0 Configuration

This section in clude s inform atio n on the var ious con figura tion options available with the DP83849IF. The configuration options described below include:

— Media Configuration

— Auto-Negotiation

— PHY Address and LEDs

— Half Duplex vs. Full Duplex

— Isolate mode

— Loopback mode

—BIST

2.1 Media Configuration

The DP83849IF supports both Twister Pair (100BASE-TX

and 10BASE-T) and Fiber (100BASE-FX) media. Each

port may be independe ntly confi gu r ed fo r Twisted Pair (TP)

or Fiber (FX) operation by strap option or by register

access.

At power-up/reset, the st ate of the COL_A and COL_B pins

will select the media for ports A and B respectively. The

default selection is TP mode, while an external pull-up will

select FX mode of operation. Strapping a port into FX

mode also automatically sets the Far-End Fault Enable, bit

3 of PCSR (16h), the Scramble Bypass, bit 1 of PCSR

(16h) and the Descrambler Bypass, bit 0 of PCSR (16h). In

addition, the media selection may be controlled by writing

to bit 6, FX_EN, of PCSR (16h).

2.2 Auto-Negotiation

The Auto-Negotiation function provides a mechanism for

exchanging configuration information between two ends of

a link segment and automatically selecting the highest per

formance mode of operation supported by both devices.

Fast Link Pulse (FLP) Bursts provide the signalling used to

communicate Auto-Negotiation abilities between two

devices at each end of a link segment. For further detail

regarding Auto-Negotiation, refer to Clause 28 of the IEEE

802.3u specification. The DP83849IF supports four differ

ent Ethernet protocols (10 Mb/s Half Duplex, 10 Mb/s Full

Duplex, 100 Mb/s Half Duplex, and 100 Mb/s Full Duplex),

so the inclusion of Auto-Negotiation ensures that the high

est performance protocol will be selected based on the

advertised ability of the Link Partner. The Auto-Negotiation

function within the DP83849IF can be controlled either by

internal register access or by the use of the AN_EN, AN1

and AN0 pins.

2.2.1 Auto-Negotiation Pin Control

The state of AN_EN, AN0 an d AN1 det ermine s wheth er the

DP83849IF is forced into a specific mode or Auto-Negotia

tion will advertise a specific ability (or set of abilities) as

given in

be selected without requiring internal register access.

The state of AN _EN, AN0 and A N1, upon po wer-up/ reset,

determines the state of bits [8:5] of the ANAR register.

The Auto-Negotiation function selected at power-up or

reset can be cha nged at any time by writin g to the Basic

Mode Contro l Register (BMCR) at address 00h.

Table 1. These pins allow configuration options to

-

-

-

-

Table 1. Auto-Negotiation Modes

AN_EN AN1 AN0 Forced Mode

0 0 0 10BASE-T, Half-Duplex

0 0 1 10BASE-T, Full-Duplex

0 1 0 100BASE-TX, Half-Duplex

0 1 1 100BASE-TX, Full-Duplex

AN_EN AN1 AN0 Advertised Mo0e

1 0 0 10BASE-T, Half/Full-Duplex

1 0 1 100BASE-TX, Half/Full-Duplex

1 1 0 10BASE-T Half-Duplex

100BASE-TX, Half-Duplex

1 1 1 10BASE-T, Half/Full-Duplex

100BASE-TX, Half/Full-Duplex

2.2.2 Auto-Negotiation Register Control

When Auto-Negotiation is enabled, the DP83849IF transmits the abilities programmed into the Auto-Negotiation

Advertisement register (ANAR) at address 04h via FLP

Bursts. Any combination of 10 Mb/s, 100 Mb/s, HalfDuplex, and Full Duplex modes may be selected.

Auto-Negotiation Priority Resolution:

— (1) 100BASE-TX Full Duplex (Highest Priority)

— (2) 100BASE-TX Half Duplex

— (3) 10BASE-T Full Duplex

— (4) 10BASE-T Half Duplex (Lowest Priority)

The Basic Mode Control Register (BMCR) at address 00h

provides control for enabling, disabling, and restarting the

Auto-Negotiation process. When Auto-Negotiation is dis

abled, the Speed Selection bit in the BMCR controls

switching between 10 Mb/s or 100 Mb/s operation, and the

Duplex Mode bit controls switching between full duplex

operation and half duplex operation. The Speed Selection

and Duplex Mode bits have no effect on the mode of oper

ation when the Auto-Negotiation Enable bit is set.

The Link Speed can be examined through the PHY Status

Register (PHYSTS) at address 10h after a Link is

achieved.

The Basic Mode Status Register (BMSR) indicates the set

of available abilities for technology types, Auto-Negotiation

ability, and Extended Register Capability. These bits are

permanently set to indicate the full functionality of the

DP83849IF (only the 100BASE-T4 bit is not set since the

DP83849IF does not support that function).

The BMSR also provides status on:

— Whether or not Auto-Negotiation is complete

— Whether or not the Link Partner is advertising that a re-

mote fault has occurred

— Whether or not valid link has been established

— Support for Management Frame Preamble suppression

The Auto-Negotiation Advertisement Register (ANAR) indi-

cates the Auto-Negotiation abilities to be advertised by the

DP83849IF. All available abilities are transmitted by

default, but any ability can be suppressed by writing to the

-

-

DP83849IF

18 www.national.com

ANAR. Updating the ANAR to suppress an ability is one

way for a management agent to change (restrict) the tech

nology that is used.

The Auto-Negotiation Link Partner Ability Register

(ANLPAR) at address 05h is used to receive the base link

code word as well as all next page code words during the

negotiati on. Furthermore, the ANLPAR will be updat ed to

either 0081h or 0021h for parallel detection to either 100

Mb/s or 10 Mb/s respectively.

The Auto-Negotiation Expansion Register (ANER) indicates additional Auto-Negotiation status. The ANER provides status on:

— Whether or not a Parallel Detect Fault has occurred

— Whether or not the Link Partne r supp orts the N ext Pag e

function

— Whether or not the DP83849IF supports the Next Page

function

— Whether or not the current page being exchanged by

Auto-Negotiation has been receiv ed

— Whether or not the Link Partner supports Auto-Negotia-

tion

2.2.3 Auto-Negotia tion Para llel Detection

The DP83849IF supports the Parallel Detection function as

defined in the IEEE 802.3u specifi ca tio n. Para lle l De tect io n

requires both the 10 Mb/s and 100 Mb/s receivers to moni

tor the receive signal and report link status to the AutoNegotiation function. Auto-Negotiation uses this informa

tion to configure th e corre ct techno logy i n the e vent th at the

Link Partner does not support Auto-Negotiation but is

transmitting link signals that the 100BASE-TX or 10BASET PMAs recognize as valid link signa ls .

If the DP83849IF co mp lete s Au to-Negotiation as a result of

Parallel Detection, bits 5 and 7 within the ANLPAR register

will be set to reflect the mode of operation present in the

Link Partner. Note that bits 4:0 of the ANLPAR will also be

set to 00001 based on a successful parallel detection to

indicate a valid 802.3 selector field. Software may deter

mine that negotiation completed via Parallel Detection by

reading a zero in the Link Partn er Au to-N eg oti ati on Ab le b it

once the Auto-Negotiat io n Compl ete b it i s s et. I f co nfi gure d

for parallel detect mode and any condition other than a sin

gle good link occurs then the parallel detect fault bit will be

set.

-

-

-

-

-

2.2.5 Enabling Auto-Negotiation via Software

It is important to not e that i f the DP 8384 9IF has been initia lized upon power-up as a non-auto-negotiating device

(forced technology), and it is then requ ire d that Auto-Negotiation or re-Auto-Negotiation be initiated via software,

12 (Auto-Negotiation Enable) of the Basic Mode Control

bit

Register (BMCR) must first be cleared and then set for any

Auto-Negotiation function to take effect.

2.2.6 Auto-Negotiation Complete Time

Parallel detection and Auto-Negotiation take approximately

2-3 seconds to co mp let e. In addition, Auto-Negotia tio n wi th

next page should take approximately 2-3 seconds to com

plete, depending on the number of next pages sent.

Refer to Clause 28 of the IEEE 802.3u standard for a full

description of the individual timers related to Auto-Negotiation.

-

2.3 Auto-MDIX

When enabled, this function utilizes Auto-Negotiation to

determine the proper configuration for transmission and

reception of data and subsequently selects the appropriate

MDI pair for MD I/ MD IX o pe ra ti on. T h e fu nc t io n us es a r an

dom seed to control switching of the crossover circuitry.

-

DP83849IF

2.2.4 Auto-Negotiation Rest art

Once Auto-Negotiation has completed, it may be restarted

at any time by setting bit 9 (Res tart Auto- Negotiat ion) of th e

BMCR to one. If the mode confi gured b y a su cces sful Au toNegotiation loses a valid link, then the Auto-Negotiation

process will resume and attempt to determine the configu

ration for the link. This function ensures that a valid configuration is maintained if the cable becomes disconnected.

A renegotiation requ es t fro m any en tity, such as a management agent, wi ll cause th e DP83849I F to halt any tr ansmit

data and link pulse activity until the break_link_timer

expires (~1500 ms). Consequently, the Link Partner will go

into link fail and normal Auto-Negotiation resumes. The

DP83849IF will resume Auto-Negotiation after the

break_link_timer has expired by issuing FLP (Fast Link

Pulse) bursts.

-

19 www.national.com

MDIO bus in a system must have a unique physical

address.

The DP83849IF supports PHY Address strapping of Port A

to even values 0 (<0000_0>) through 30 (<1111_0>). Port

B is strapped to odd values 1 (<0000_1>) through 31

(<1111_1>). Note that Port B address is always 1 greater

than Port A address.

For further detail rela ting to the la tch -in timi ng requi rement s

of the PHY Address pins, as well as the other hardware

configuration pins, refer to the Reset summary in

Section 6.0.

Refer to Figure 2 for an exam ple o f a PH YAD connection to

external components. In this example, the PHYAD strapping results in address 00010 (02h) for Port A and address

00011 (03h) for Port B.

DP83849IF

2.4.1 MII Isolate Mode

The DP83849IF can be put into MII Isolate mode by writing

to bit 10 of the BMCR register.

When in the MII isolate mode, the DP83849IF does not

respond to packet data present at TXD[3:0], TX_EN inputs

and presents a high impedance on the TX_CLK, RX_CLK,

RX_DV, RX_ER, RXD[3:0], COL, and CRS outputs. When

in Isolate mode, the DP83849IF will continue to respond to

all management transactions.

While in Isolate mod e, th e PM D ou tput pair will not transm it

packet data but will continue to source 100BASE-TX

scrambled idles or 10BASE-T normal link pulses.

The DP83849IF can Auto-Negotiate or parallel detect to a

specific technology depending on the receive signal at the

PMD input pair. A valid link can be established for the

receiver even when the DP83849IF is in Isolate mode.

RXD1_B

PHYAD4= 0

RXD0_B

Figure 2. PHYAD Strapping Example

RXD1_A

PHYAD2 = 0PHY AD3 = 0

RXD0_A

PHYAD1 = 1

2.2kΩ

VCC

20 www.national.com

2.5 LED Interface

The DP83849IF supports three configurable Light Emitting

Diode (LED) pins for each port.

Several functions can be multiplexed onto the three LEDs

using three different modes of operation. The LED operation mode can be selected by writing to the LED_CFG[1:0]

register bits in the PHY Control Register (PHYCR) at

address 19h, bits [6:5]. In addition, LED_CFG[0] for each

port can be set by a strap option on the CRS_A and

CRS_B pins. LED_CFG[1] is only controllable through reg

ister access and cannot be set by as strap pin.

See Table 3 for LED Mode selection.

-

DP83849IF

The LED_LINK pin in Mode 1 indicates the link status of

the port. In 100BASE-T mode, link is established as a

result of input receive amplitude compliant with the TPPMD specifications which will result in internal generation

of signal detect. A 10 Mb/s Link is est abli shed as a result of

the reception of at least seven consecutive normal Link

Pulses or the reception of a valid 10BASE-T packet. This

will cause the as sertion of LED_LINK. L ED _LIN K w il l d ea s

sert in accordance with the Link Loss Timer as specified in

the IEEE 802.3 specification.

The LED_LINK p in in Mode 1 w i ll be O FF w h en no LI N K is

present.

The LED_LINK pin in Mode 2 and Mode 3 will be ON to

indicate Link is good and BLINK to indicate activity is

present on activity. The BLINK frequency is defined in

BLINK_FREQ, bits [7:6] of register LEDCR (18h).

Activity is defined as configured in LEDACT_RX, bit 8 of

register LEDCR (18h). If LEDACT_RX is 0, Activity is sig

naled for either transmit or receive. If LEDACT_RX is 1,

Activity is only signaled for receive.

The LED_SPEED pin indicates 10 or 100 Mb/s data rate of

the port. The LED is ON when operating in 100Mb/s mode

and OFF when operating in 10Mb/s mode. The functional

ity of this LED is independent of mode selected.

The LED_ACT/LED_COL pin in Mo de 1 ind ic ates the pre sence of either transmit or receive activity. The LED will be

ON for Activity and OFF for No Activity. In Mode 2, this pin

indicates the Collision status of the port. The LED will be

ON for Collision and OFF for No Collision.

-

-

-

The LED_ACT/LED_COL pin in Mode 3 indicates Duplex

status for 10 Mb/s or 100 Mb/s operation. The LED will be

ON for Full Duplex and OFF for Half Duplex.

In 10 Mb/s half duplex mode, the collision LED is based on

the COL signal.

Since these LED pins are also used as strap options, the

polarity of the LED is dependent on whether the pin is

pulled up or down.

2.5.1 LEDs

Since the Auto-Negotiation (AN) strap options share the

LED output pins, the external components required for

strapping and LED usage must be considered in order to

avoid contention.

Specifically, when the LED outputs are used to drive LEDs

directly, the active state of each output driver is dependent