DP83843BVJE PHYTER

DP83843BVJE PHYTER

July 1999

General Description

TheDP83843BVJEisafullfeaturePhysicalLayerdevice

withintegratedPMDsublayerstosupportboth10BASE-T

and 100BASE-X Ethernet protocols.

ThisVLSIdeviceisdesignedforeasyimplementationof

10/100Mb/sEthernetLANs.ItinterfacesdirectlytoTwisted

Pairmediathroughanexternaltransformerortofiber

mediaviaindustrystandardelectrical/opticalfiberPMD

transceivers.Thisdevicealsointerfacesdirectlytothe

MAClayerthroughtheIEEE802.3ustandardMediaIndependentInterface(MII),ensuringinteroperabilitybetween

products from different vendors.

TheDP83843isdesignedwithNationalSemiconductor's

advancedCMOSprocess.Itssystemarchitectureisbased

ontheintegrationofseveralofNational'sindustryproven

core technologies:

—IEEE 802.3 ENDEC with AUI/10BASE-T transceiver

module to provide the 10 Mb/s functions

—ClockRecovery/GeneratorModulesfromNational'sFast

Ethernet and FDDI products

—FDDI Stream Cipher scrambler/descrambler for

TP-PMD

—100BASE-Xphysicalcodingsub-layer(PCS)andcontrol

logicthatintegratesthecoremodulesintoadualspeed

Ethernet physical layer controller

—ANSI X3T12 Compliant TP-PMD Transceiver

technology with Baseline Wander (BLW) compensation

Features

—IEEE 802.3 ENDEC with AUI/10BASE-T transceivers

and built-in filters

—IEEE 802.3u 100BASE-TX compatible - directly drives

standard Category 5 UTP, no need for external

100BASE-TX transceiver

—Fully Integrated and fully compliant ANSI X3.263 TP-

PMD physical sublayer which includes adaptive equalization and BLW compensation

—IEEE802.3u100BASE-FXcompatible-connectsdirect-

ly to industry standard Electrical/Optical transceivers

—IEEE 802.3u Auto-Negotiation for automatic speed se-

lection

—IEEE 802.3u compatible Media Independent Interface

(MII) with Serial Management Interface

—Integrated high performance 100 Mb/s clock recovery

circuitry requiring no external filters

—Full Duplex support for 10 and 100 Mb/s data rates

—MII Serial 10 Mb/s mode

—Fully configurable node/switch and 100Mb/s repeater

modes

—Programmableloopbackmodesforflexiblesystemdiag-

nostics

—Flexible LED support

—Single register access to complete PHY status

—MDIO interrupt support

—Individualized scrambler seed for 100BASE-TX applica-

tions using multiple PHYs

—Low power consumption for multi-port applications

—Small footprint 80-pin PQFP package

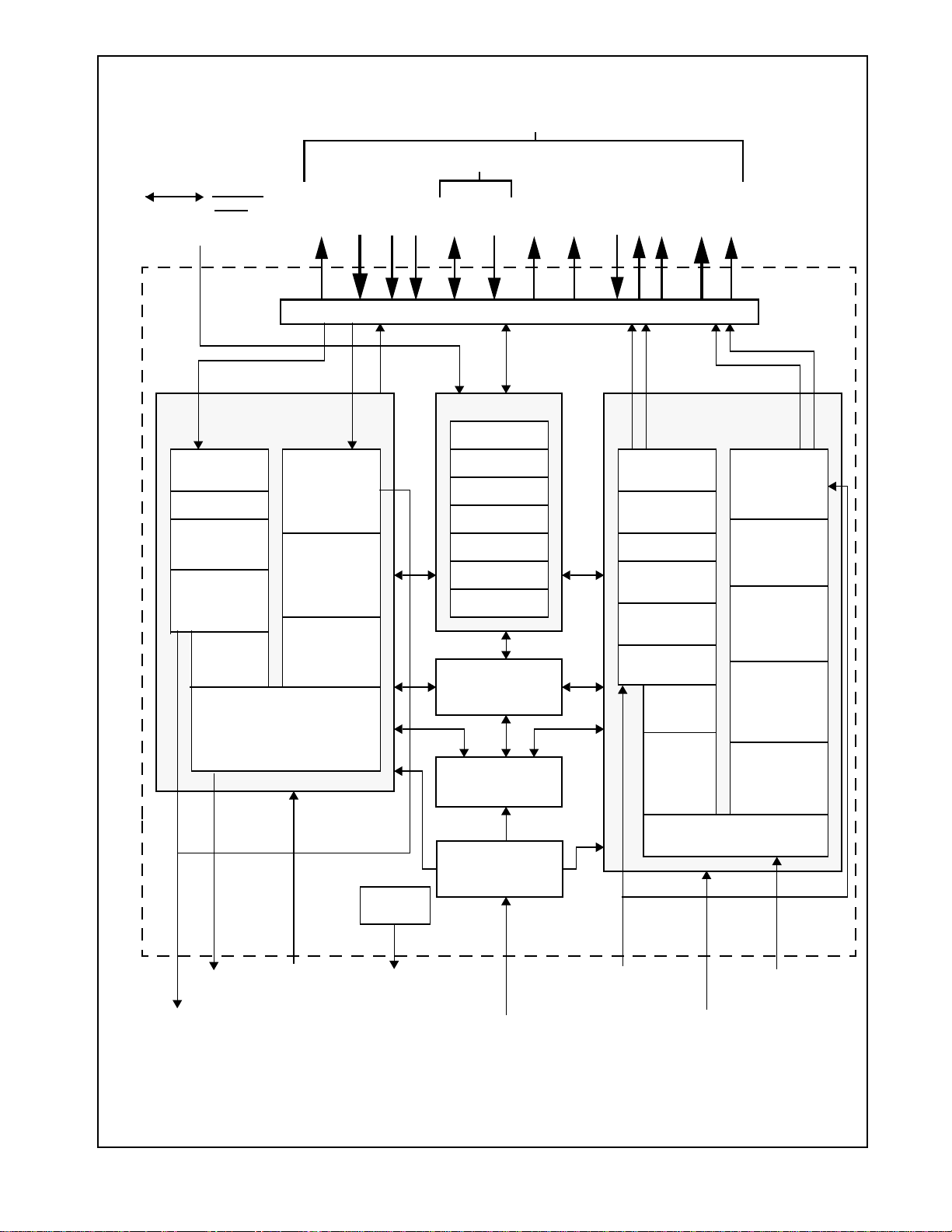

System Diagram

10 AND/OR 100 Mb/s

ETHERNET MAC OR

100Mb/s REPEATER

CONTROLLER

ThunderLAN® is a registered trademark of Texas Instruments.

TWISTER™ is a trademark of National Semiconductor Corporation.

TRI-STATE

®

is a registered trademark of National Semiconductor Corporation.

© 1999 National Semiconductor Corporation

MII

DP83843

10/100 Mb/s

ETHERNET PHYSICAL LAYER

25 MHz

CLOCK

STATUS

LEDS

10BASE-T or

100BASE-TX

MAGNETICS

100BASE-FX/

AUI

RJ-45

10BASE-T

100BASE-TX

www.national.com

or

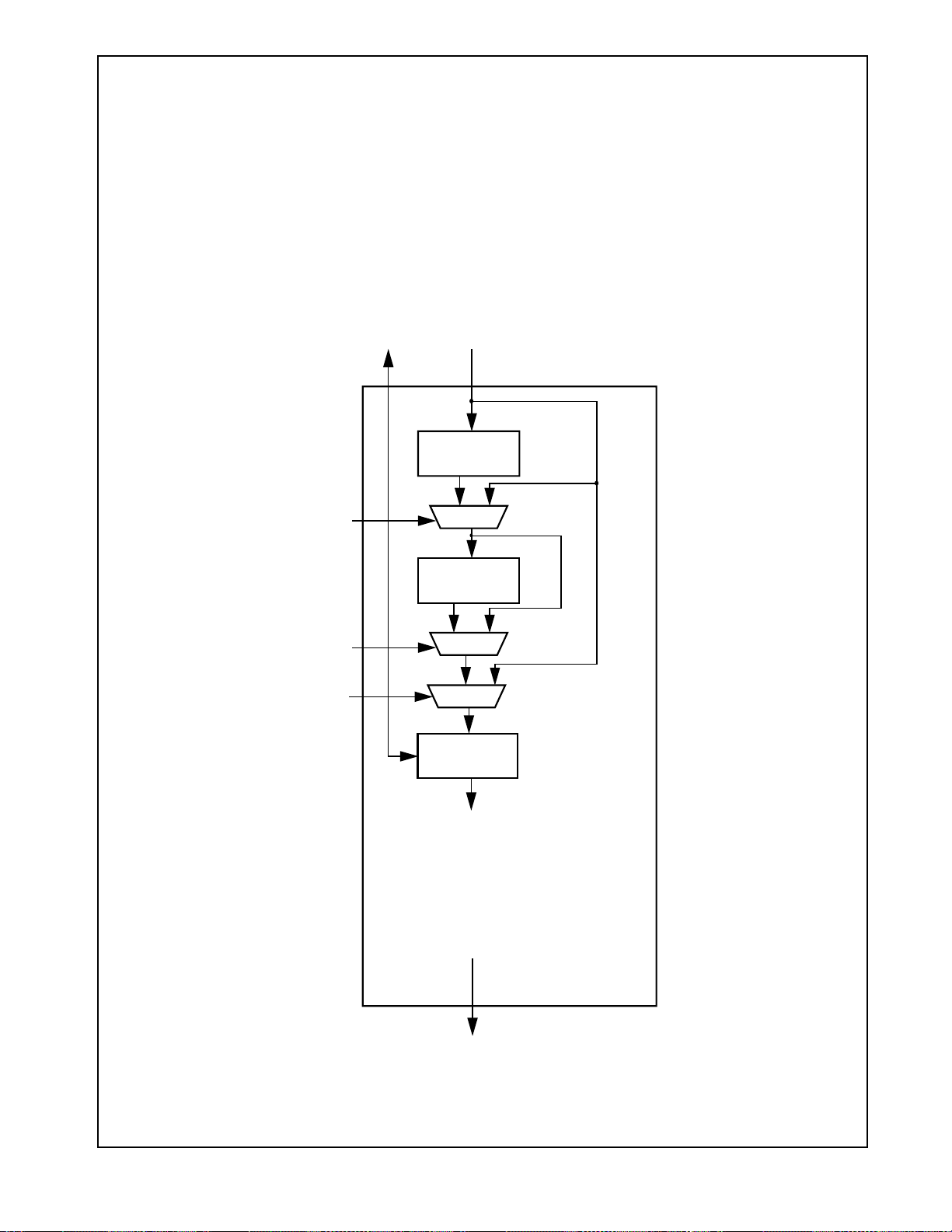

Block Diagram

HARDWARE

CONFIGURATION

PINS

(REPEATER,

SERIAL10, SYMBOL,

,

AN0, AN1,FXEN

PHYAD[4:0])

TX_CLK

TX_ER

TXD[3:0]

MII

SERIAL

MANAGEMENT

TX_EN

MDIO

MII INTERFACE/CONTROL

MDC

COL

CRS

RX_ER

RX_EN

RX_DV

RX_CL

RXD[3:0]

TX_DATA

TRANSMIT CHANNELS &

STATE MACHINES

100 MB/S 10 MB/S

4B/5B

ENCODER

MANCHESTER

SCRAMBLER

PARALLEL TO

SERIAL

NRZ TO NRZI

ENCODER

BINARY TO

MLT-3

ENCODER

10/100 COMMON

OUTPUT DRIVER

TX_DATA

NRZ TO

ENCODER

LINK PULSE

GENERATOR

TRANSMIT

FILTER

TX_CLK

REGISTERS

MII

PHY ADDRESS

AUTO

NEGOTIATION

NODE/RPTR

PCS CONTROL

10BASE-T

100BASE-X

FAR-END-FAULT

STATE MACHINE

AUTO-NEGOTIATION

STATE MACHINE

RX_CLK

DESCRAMBLER

RX_DATA

RECEIVE CHANNELS &

STATE MACHINES

100 MB/S 10 MB/S

4B/5B

DECODER

CODE GROUP

ALIGNMENT

SERIAL TO

PARALLEL

NRZI TO NRZ

DECODER

CLOCK

RECOVERY

MLT-3 TO

BINARY

DECODER

ADAPTIVE

EQ

AND

BLW

COMP.

RX_DATA

RX_CLK

MANCHESTER

TO NRZ

DECODER

CLOCK

RECOVERY

LINK PULSE

DETECTOR

RECEIVE

FILTER

SMART

SQUELCH

FXTD/AUITD+/−

TXAR100

LED

DRIVERS

LEDS

10/100 COMMON

INPUT BUFFER

CLOCK

GENERATION

TPRD+/−TPTD+/−

SYSTEM CLOCK

REFERENCE

FXRD/AUIRD+/−

FXSD/CD+/−

2 www.national.com

Table of Contents

1.0 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

1.1 MII Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

1.2 10 Mb/s and 100 Mb/s PMD Interface . . . . . . . . . .6

1.3 Clock Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

1.4 Device Configuration Interface . . . . . . . . . . . . . . .8

1.5 LED Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

1.6 PHY Address Interface . . . . . . . . . . . . . . . . . . . .11

1.7 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

1.8 Power And Ground Pins . . . . . . . . . . . . . . . . . . .12

1.9 Special Connect Pins . . . . . . . . . . . . . . . . . . . . . .12

2.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . .13

2.1 802.3u MII . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

2.2 100BASE-TX TRANSMITTER . . . . . . . . . . . . . . .15

2.3 100BASE-TX RECEIVER . . . . . . . . . . . . . . . . . . 18

2.4 10BASE-T TRANSCEIVER MODULE . . . . . . . . .22

2.5 100 BASE-FX . . . . . . . . . . . . . . . . . . . . . . . . . . .24

2.6 AUI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

3.0 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

3.1 Auto-Negotiation . . . . . . . . . . . . . . . . . . . . . . . . . 28

3.2 PHY Address and LEDs . . . . . . . . . . . . . . . . . . .30

3.3 Half Duplex vs. Full Duplex . . . . . . . . . . . . . . . . .31

3.4 100 Mb/s Symbol Mode . . . . . . . . . . . . . . . . . . . . 32

3.5 100BASE-FX Mode . . . . . . . . . . . . . . . . . . . . . . .32

3.6 10 Mb/s Serial Mode . . . . . . . . . . . . . . . . . . . . . .32

3.7 10 Mb/s AUI Mode . . . . . . . . . . . . . . . . . . . . . . . . 32

3.8 Repeater vs. Node . . . . . . . . . . . . . . . . . . . . . . . .33

3.9 Isolate Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

3.10 Loopback . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

4.0 Clock Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

4.1 Clock Generation Module (CGM) . . . . . . . . . . . .34

4.2 100BASE-X Clock Recovery Module . . . . . . . . . .36

4.3 10 Mb/s Clock Recovery Module . . . . . . . . . . . . . 36

4.4 Reference Clock Connection Options . . . . . . . . .36

5.0 Reset Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

5.1 Power-up / Reset . . . . . . . . . . . . . . . . . . . . . . . . . 37

5.2 Hardware Reset . . . . . . . . . . . . . . . . . . . . . . . . . .37

5.3 Software Reset . . . . . . . . . . . . . . . . . . . . . . . . . .37

6.0 DP83843 Application . . . . . . . . . . . . . . . . . . . . . . . . . .38

6.1 Typical Node Application . . . . . . . . . . . . . . . . . . .38

6.2 Power And Ground Filtering . . . . . . . . . . . . . . . .38

6.3 Power Plane Considerations . . . . . . . . . . . . . . . .38

7.0 User Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

7.1 Link LED While in Force 100Mb/s Good Link . . . 42

7.2 False Link Indication When in Forced 10Mb/s . . 42

7.3 10Mb/s Repeater Mode . . . . . . . . . . . . . . . . . . . 42

7.4 Resistor Value Modifications . . . . . . . . . . . . . . . 42

7.5 Magnetics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

7.6 Next Page Toggle Bit Initialization . . . . . . . . . . . 43

7.7 Base Page to Next Page Initial FLP Burst Spacing

43

7.8 100Mb/s FLP Exchange Followed by Quiet . . . . 43

7.9 Common Mode Capacitor for EMI improvement 44

7.10 BAD_SSD Event Lockup . . . . . . . . . . . . . . . . . . 44

8.0 Register Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

8.1 Register Definitions . . . . . . . . . . . . . . . . . . . . . . 45

9.0 Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . 63

9.1 DC Electrical Specification . . . . . . . . . . . . . . . . . 64

9.2 CGM Clock Timing . . . . . . . . . . . . . . . . . . . . . . 66

9.3 MII Serial Management AC Timing . . . . . . . . . . 66

9.4 100 Mb/s AC Timing . . . . . . . . . . . . . . . . . . . . . . 67

9.5 10 Mb/s AC Timing . . . . . . . . . . . . . . . . . . . . . . . 74

9.6 Auto-Negotiation Fast Link Pulse (FLP) Timing 80

9.7 100BASE-XClock Recovery Module(CRM) Timing

80

9.8 Reset Timing . . . . . . . . . . . . . . . . . . . . . . . . . . 82

9.9 Loopback Timing . . . . . . . . . . . . . . . . . . . . . . . 83

9.10 Isolation Timing . . . . . . . . . . . . . . . . . . . . . . . . 84

10.0 Test Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

10.1 FXTD/AUITD+/- Outputs (sourcing AUI levels) . 85

10.2 FXTD/AUITD+/- Outputs (sourcing PECL) . . . . . 85

10.3 CMOS Outputs (MII and LED) . . . . . . . . . . . . . . 85

10.4 TPTD+/- Outputs (sourcing 10BASE-T) . . . . . . . 85

10.5 TPTD+/- Outputs (sourcing 100BASE-TX) . . . . . 85

10.6 Idd Measurement Conditions . . . . . . . . . . . . . . . 85

11.0 Package Dimensions inches (millimeters) unless other-

wise noted . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

3 www.national.com

Connection Diagram

TWREF

60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41

BGREF

NC

THIN/REPEATER

TW_AGND

TPRD-

VCM_CAP

TPRD+

TW_AVDD

SERIAL10

SUB_GND1

CD_GND0

CD_VDD0

TPTD-

TPTD+

CD_GND1

CD_VDD1

SUB_GND2

TXAR100

TR_AVDD

TR_AGND

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

NC

NC

ATP_GND

NC

CPTW_DVSS

CPTW_DVDDNCCP_AVDD

CP_AGND

FXRD-/AUIRD-

FXRD+/AUIRD+

DP83843BVJE

PHYTER

FXSD-/CD-

AUIFX_VDD

FXSD+/CD+

AUIFX_GND

FXTD-/AUITD-

FXTD+/AUITD+

LED_COL/PHYAD[0]

LED_TX/PHYAD[1]

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

LED_RX/PHYAD[2]

LED_LINK/PHYAD[3]

LED_FDPOL/PHYAD[4]

IO_VSS5

IO_VDD5

MDC

MDIO

TX_CLK

IO_VSS4

TXD[0]

TXD[1]

TXD[2]

TXD[3]

IO_VSS3

IO_VDD3

TX_EN

TX_ER

RX_EN

SYMBOL

CRS/

FXEN

COL/

NC

RESET

AN1

X2

IO_VSS1

X1

PCS_VDD

PCS_VSS

AN0

SPEED10

IO_VDD1

Order Number DP83843BVJE

NS Package Number VJE80

4 www.national.com

RXD[2]

RXD[3]

RXD[0]

RXD[1]

RX_CLK

IO_VSS2

IO_VDD2

RX_DV

RX_ER

1.0 Pin Descriptions

The DP83843 pinsare classified into the following interface

categories. Each interface is described in the sections that

follow.

— MII INTERFACE

— 10/100 Mb/s PMD INTERFACE

— CLOCK INTERFACE

— DEVICE CONFIGURATION INTERFACE

— LED INTERFACE

— PHY ADDRESS INTERFACE

— RESET

— POWER AND GROUND PINS

— SPECIAL CONNECT PINS

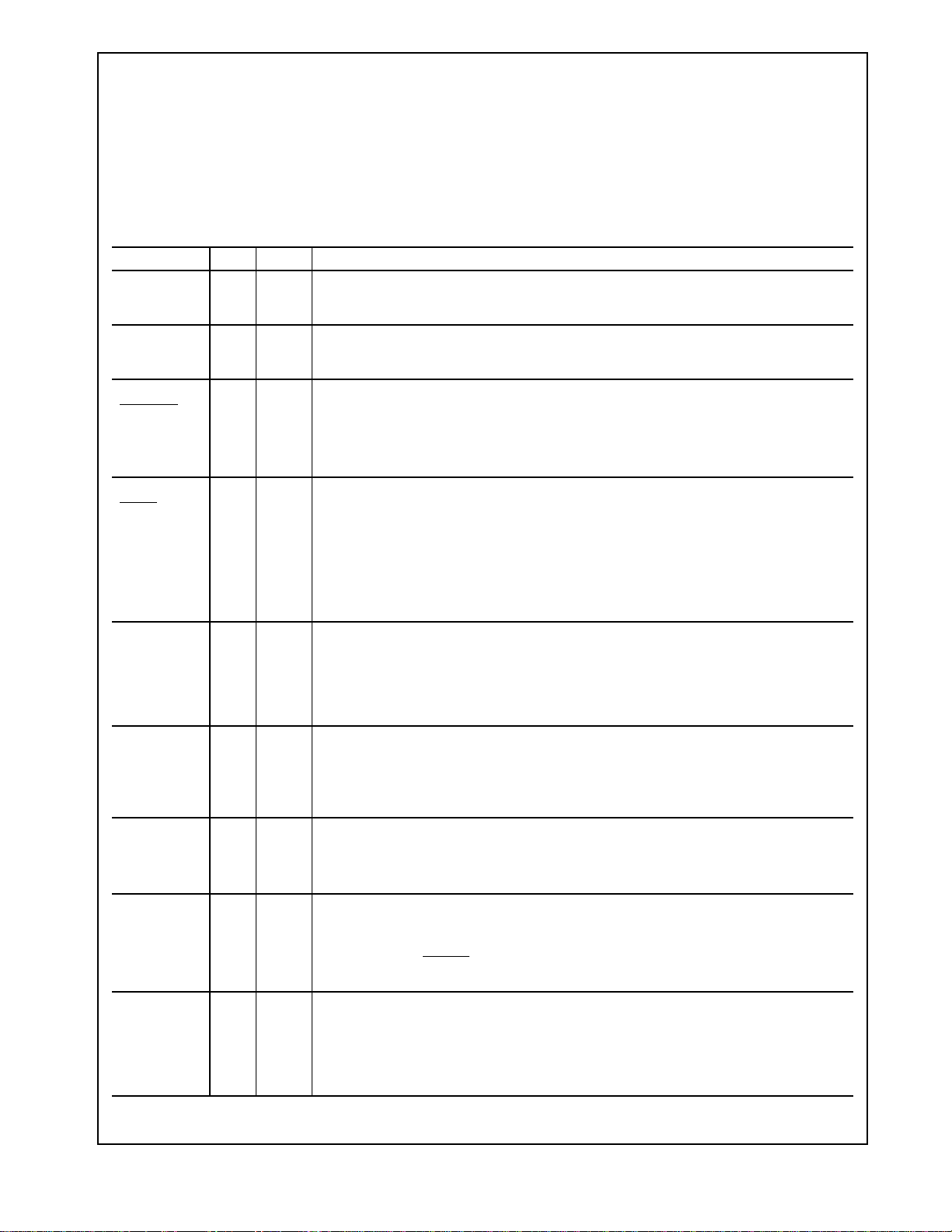

1.1 MII Interface

Signal Name Type Pin # Description

MDC I 35 MANAGEMENT DATA CLOCK: Synchronous clock to the MDIO managementdata in-

MDIO I/O, Z 34 MANAGEMENT DATA I/O: Bi-directional management instruction/data signal that may

CRS

SYMBOL)

(

COL

FXEN)

(

TX_CLK O, Z 33 TRANSMIT CLOCK: Transmit clock output from the DP83843:

TXD[3]

TXD[2]

TXD[1]

TXD[0]

TX_EN I 25 TRANSMIT ENABLE: Active high input indicates the presence of valid nibble data on

TX_ER

(TXD[4])

RX_CLK O, Z 18 RECEIVE CLOCK: Provides the recovered receive clock for different modes of opera-

I/O, Z 22 CARRIER SENSE: This pin is asserted high to indicate the presence of carrier due to

I/O, Z 21 COLLISION DETECT: Asserted high to indicate detection of collision condition (asser-

I28

29

30

31

I24TRANSMIT ERROR: In 100 Mb/s mode, when this signal is high and TX_EN is active

put/output serial interface which may be asynchronous to transmit and receive clocks.

The maximum clock rate is 2.5 MHz. There is no minimum clock rate.

be sourcedby thestation managemententity or thePHY. Thispin requiresa 1.5 kΩpullup resistor.

receive or transmit activities in 10BASE-T or 100BASE-X Half Duplex modes.

In Repeater or Full Duplex mode, this pin is asserted high to indicate the presence of

carrier due only to receive activity.

In Symbol mode this pin indicatesthe signal detect status of the TP-PMD (active high).

tion ofCRS due tosimultaneous transmit and receiveactivity) in 10Mb/s and 100Mb/s

Half Duplex modes.

While in 10BASE-T HalfDuplex mode with Heartbeat enabled (bit 7,register 18h), this

pin is also asserted for a duration of approximately 1 µs at the end of transmission to

indicate heartbeat(SQE test).During Repeatermode the heartbeatfunction isdisabled.

In Full Duplex mode, for 10 Mb/s or 100 Mb/s operation, this signal is always logic 0.

There is no heartbeat function during 10 Mb/s full duplex operation.

25 MHz nibble transmit clock derived from Clock Generator Module's (CGM) PLL in

100BASE-TX mode.

2.5 MHz transmit clock in 10BASE-T Nibble mode.

10 MHz transmit clock in 10BASE-T Serial mode.

TRANSMIT DATA: Transmit data MII input pins that accept nibble data during normal

nibble-wide MIIoperation at either 2.5MHz (10BASE-T mode) or25 MHz (100BASE-X

mode).

In 10 Mb/s Serial mode, the TXD[0] pin is used as the serial data input pin, and TXD[3:1]

are ignored.

TXD[3:0] for both 100 Mb/s or 10 Mb/s nibble mode.

In 10 Mb/s Serial mode, active high indicates the presence of valid 10 Mb/s data on

TXD[0].

the HALT symbol is substituted for the actual data nibble.

In 10 Mb/s mode, this input is ignored.

In Symbolmode (

transmit 5-bit data symbol.

tion:

25 MHz nibble clock in 100 Mb/s mode

2.5 MHz nibble clock in 10 Mb/s nibble mode

10 MHz receive clock in 10 Mb/s serial mode

Symbol=0), TX_ERbecomes theTXD [4] pin which isthe MSBfor the

5 www.national.com

1.0 Pin Descriptions (Continued)

Signal Name Type Pin # Description

RXD[3]

RXD[2]

RXD[1]

RXD[0]

RX_EN I 23 RECEIVE ENABLE:Active highenable forreceive signalsRXD[3:0], RX_CLK,RX_DV

RX_ER

(RXD[4])

RX_DV O, Z 20 RECEIVE DATA VALID:Asserted hightoindicate thatvaliddata ispresenton RXD[3:0]

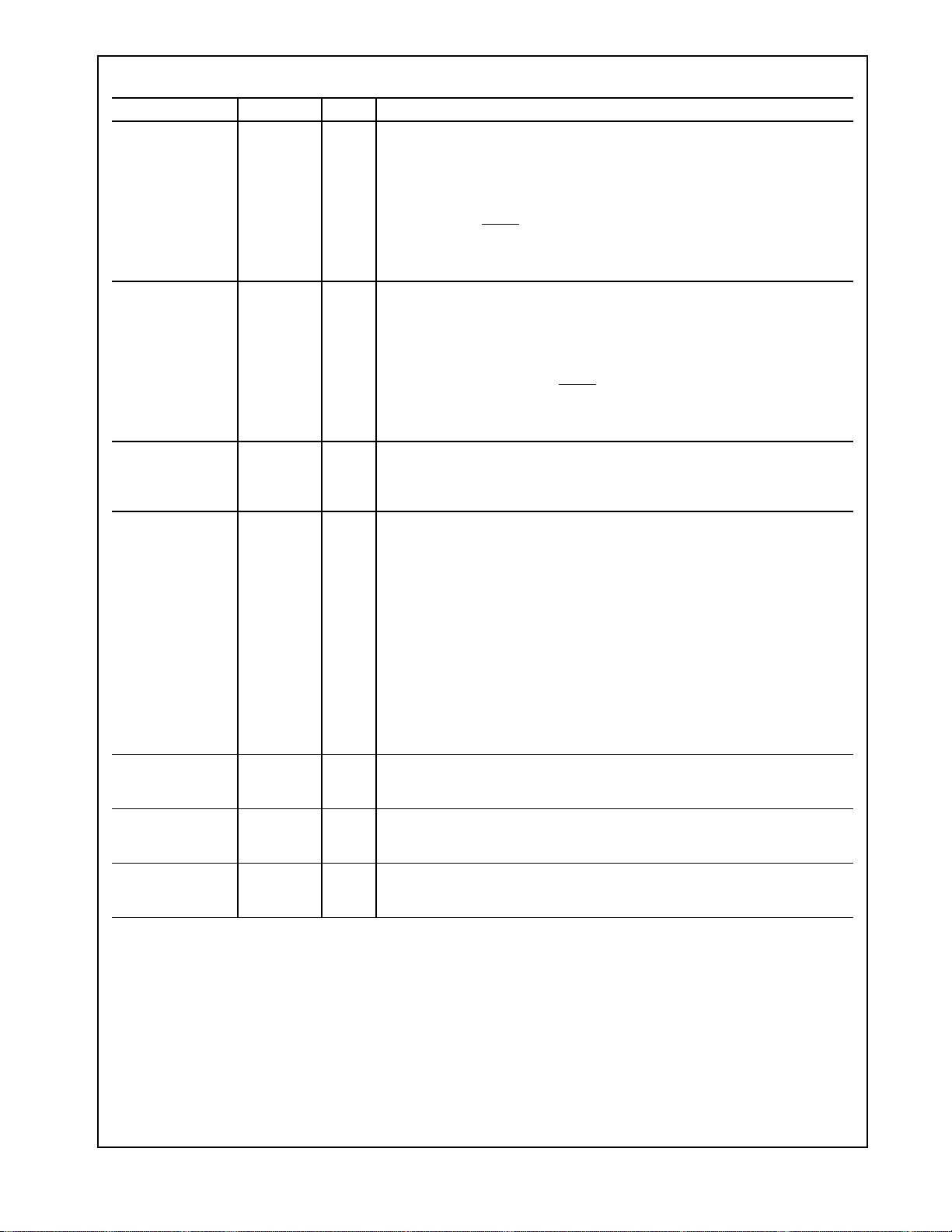

1.2 10 Mb/s and 100 Mb/s PMD Interface

Signal Name Type Pin # Description

TPTDTPTD+

TPRDTPRD+

FXTD-/AUITDFXTD+/AUITD+O(PECL

O, Z 12

13

14

15

O, Z 19 RECEIVE ERROR: Asserted high to indicate that aninvalid symbol has been detected

O

(MLT-3

or

10BASE-T)

I

(MLT-3

or

10BASE-T)

or

AUI)

RECEIVE DATA: Nibble wide receive data (synchronous to RX_CLK, 25 MHz for

100BASE-X mode, 2.5 MHz for 10BASE-T nibble mode). Data is driven on the falling

edge of RX_CLK.

In 10 Mb/s serial mode, the RXD[0] pin is used as the data output pin which is also

clocked out on the falling edgeof RX_CLK. During 10 Mb/s serial mode RXD[3:1] pins

become don't cares.

and RX_ER. A low on this input places these output pins in the TRI-STATE mode. For

normal operation in anode or switch application, this pin shouldbe pulled high. For operation in a repeater application, this pin may be connected to a repeater controller.

within a received packet in 100 Mb/s mode.

In Symbol mode (

ceive 5-bit data symbol.

for nibble mode and RXD[0] for serial mode. Data is driven on the falling edge of

RX_CLK.

This pin is not meaningful during Symbol mode.

73

74

65

67

44

43

Symbol = 0), RX_ER becomes RXD[4] which is the MSB for the re-

TRANSMIT DATA: Differential common output driver. This differential output

is configurable to either 10BASE-T or 100BASE-TX signaling:

10BASE-T: Transmissionof Manchester encoded10BASE-T packet dataas

well as Link Pulses (including Fast Link Pulses for Auto-Negotiation purposes.)

100BASE-TX: Transmission of ANSI X3T12 compliant MLT-3 data.

The DP83843 will automatically configure this common output driver for the

proper signal type as a result of either forced configuration or Auto-Negotiation.

RECEIVE DATA:Differential commoninput buffer.This differential inputcan

be configured to accept either 100BASE-TX or 10BASE-T signaling:

10BASE-T:Reception ofManchesterencoded 10BASE-T packetdataas well

as normal Link Pulses (including Fast Link Pulses for Auto-Negotiation purposes.)

100BASE-TX: Reception of ANSI X3T12 compliant scrambled MLT-3 data.

The DP83843will automaticallyconfigure this commoninput buffer to accept

the propersignal type as aresult of either forcedconfiguration or Auto-Negotiation.

100BASE-FX or 10 Mb/s AUI TRANSMIT DATA: This configurable output

driver supports either 125Mb/s PECL, for 100BASE-FX applications, or

10 Mb/s AUI signaling.

When configured as a 100BASE-FX transmitter this output sources

100BASE-FX standard compliantbinary data for directconnection to an optical transceiver. This differential output is enabled only during 100BASE-FX

device configuration (see pin definition for

When configured as an AUI driver this output sources AUI compatible

Manchester encodeddata tosupport typical10BASE2 or10BASE5 products.

FXEN.)

6 www.national.com

1.0 Pin Descriptions (Continued)

Signal Name Type Pin # Description

FXRD-/AUIRDFXRD+/AUIRD+I(PECL

or

AUI)

FXSD-/CDFXSD+/CD+

I

(PECL

or

AUI)

THIN

I/O, Z 63 THIN AUI MODE: This output allows for control of an external CTI coaxial

(REPEATER)

TXAR100 I

(current

reference)

TWREF I 60 TWISTERREFERENCE RESISTOR:External reference currentadjustment,

BGREF I

(current

reference)

VCM_CAP I 66 COMMON MODE BYPASS CAPACITOR: External capacitor to improve

49

50

100BASE-FX or 10 Mb/s AUI RECEIVE DATA: This configurable inputbuffer supportseither 125 Mb/sPECL, for 100BASE-FXapplications, or 10Mb/s

AUI signaling.

When configured as a 100BASE-FX receiver this input accepts100BASE-FX

standard compliant binary data direct from an opticaltransceiver. This differentialinput isenabled onlyduring 100BASE-FXdevice configuration(see the

pin definition for

FXEN).

When configured as an AUI buffer this input receives AUI compatible

Manchester data to support typical 10BASE2 or 10BASE5 products.

47

48

SIGNAL DETECT orAUI COLLISIONDETECT: Thisconfigurable inputbuffer supportseither 125 Mb/sPECL, for 100BASE-FXapplications, or 10Mb/s

AUI signaling.

When configured as a 100BASE-FX receiver this input accepts indication

from the 100BASE-FX PMD transceiver upon detection of a receive signal

from the fiber media. This pin is only active during 100BASE-FX operation(see the pin definition for

FXEN).

When configured as an AUI buffer this input receives AUI compatible

Manchester data to support typical 10BASE2 or 10BASE5 products.

transceiver connected throughthe AUI. This pin is controlled by writing tobit

3 ofthe 10BTSCRregister (address 18h).The THINpin may also be usedas

a user configurable output control pin.

78 100 Mb/s TRANSMIT AMPLITUDE REFERENCE CONTROL: Reference

current allowing adjustment of the TPTD+/− output amplitude during

100BASE-TX operation.

By placinga resistorbetween thispin and groundor V

, areference current

CC

is set up which dictates the output amplitude of the 100BASE-TX MLT-3

transmit signal. Connectinga resistor to V

will increase thetransmit ampli-

CC

tude while connecting a resistor to ground will decrease the transmit amplitude. While the value of the resistor should be evaluated on a case by case

bases, the DP83843 was designed to produce an amplitude close to the required range of 2V pk-pk differential ± 5% as measured across TD+/−while

driving a typical100Ω differentialload withouta resistorconnected tothis pin.

Therefore this pin is allowed to float in typical applications.

This currentreference is only recognized during 100BASE-TX operationand

has no effect during100BASE-FX,10BASE-T, or AUI modes of operation.

viaa resistorto TW_AGND,which controlstheTP-PMD receiverequalization

levels. The value of this resistor is 70k ± 1%.

61 BANDGAP REFERENCE: External current reference resistor for internal

bandgap circuitry. The value of this resistor is 4.87k ± 1%.

common mode filtering for the receive signal. It is recommended that a

.0033µF in parallel with a .10µF capacitor be used, see Figure 23.

7 www.national.com

1.0 Pin Descriptions (Continued)

1.3 Clock Interface

Signal Name Type Pin # Description

X1 I 9 CRYSTAL/OSCILLATOR INPUT: This pin is the primary clock reference input for

X2 O 8 CRYSTAL/OSCILLATOR OUTPUT PIN: Thispin isused in conjunction with the X1

1.4 Device Configuration Interface

Signal Name Type Pin # Description

AN0 I

(3-level)

4 AN0: This is a three level input pin (1, M, 0) that works in conjunction with the AN1

the DP83843 and must be connected to a 25 MHz 0.005% (50 ppm) clock source.

TheDP83843 devicesupportseither anexternalcrystal resonatorconnectedacross

pins X1 and X2, or an external CMOS-level oscillator source connected to pin X1

only. For100 Mb/s repeater applications,X1 should be tied to the common25 MHz

transmit clock reference. Refer to section 4.4 for further detail relating to the clock

requirements of the DP83843. Refer to section 4.0 for clock source specifications.

pin to connectto an external 25 MHz crystal resonator device. Thispin must be left

unconnected if an external CMOS oscillator clock source is utilized. For more information see the definition for pin X1. Refer to section 2.8 for further detail.

pin to control the forced or advertised operatingmode of the DP83843 according to

the following table. The value on this pin is set by connecting the input pin to GND

(0), VCC(1), or leaving it unconnected (M.) The unconnected state, M, refers to the

mid-level (V

the DP83843 at power-up/reset.

AN1 AN0 Forced Mode

0 M 10BASE-T, Half-Duplex without Auto-Negotiation

1 M 10BASE-T, Full Duplex without Auto-Negotiation

M 0 100BASE-X, Half-Duplex without Auto-Negotiation

M 1 100BASE-X, Full Duplex without Auto-Negotiation

/2) set by internal resistors. The valueset at this input is latched into

CC

AN1 I

(3-level)

AN1 AN0 Advertised Mode

M M Allcapable(i.e. Half-Duplex&Full Duplexfor10BASE-T and

0 0 10BASE-T, Half-Duplex & Full Duplex advertised via Auto-

0 1 100BASE-TX, Half-Duplex & Full Duplex advertised via

1 0 10BASE-T& 100BASE-TX,Half-Duplex advertisedvia Auto-

1 1 10 BASE-T, Half-Duplex advertised via Auto-Negotiation

3 AN1: This is a three-level input pin (i.e., 1, M, 0) that works in conjunction with the

AN0 pin to control the forcedor advertised operating modeof the DP83843 according to the table given in the AN0 pin description above. The value on this pin is set

by connecting the input pin to GND (0), V

value at this input is latched into the DP83843 at power-up, hardware or software

reset.

100BASE-TX) advertised via Auto-Negotiation

Negotiation

Auto-Negotiation

Negotiation

(1), or leaving it unconnected (M.) The

CC

8 www.national.com

1.0 Pin Descriptions (Continued)

Signal Name Type Pin # Description

REPEATER

(THIN)

SYMBOL/

(CRS)

SERIAL10 I 69 10BASE-T SERIAL/NIBBLE SELECT: With this activelow input selected, transmit

FXEN/

(COL)

I/O 63 REPEATER/NODE MODE: Selects 100 Mb/s Repeater mode when set high and

node mode when set low. When set in Repeater mode the DP83843 only supports

100 Mb/s data rates. In Repeater mode (or Node mode with Full Duplex configured), the Carrier Sense (CRS) output from the DP83843 is asserted due to

receive activity only. In Half Duplex Node mode, CRS is asserted due to either

receive or transmit activity. During repeater mode the heartbeat function(SQE) is

forced off.

The Carrier Integrity Monitor (CIM) function is automatically enabled when this pin

is set high (repeater mode) and disabled when this pin is set low (node mode) in

order to facilitate 802.3u CIM requirements.

There is an internal pullup resistor for this pin which is active during the powerup/reset period. If this pin is left floating externally, then the device will configure to

100 Mb/s Repeater mode as a result of power-up/reset.This pin must be externally

pulled low (typically 10 kΩ) in order to configure the DP83843 for Node operation.

The value of this input is latched into the DP83843 at power-up, hardware or software reset.

I/O, Z 22 SYMBOL MODE: This active low input allows 100 Mb/s transmit and receive data

streams to bypass all of the transmit and receive operations when set low. Note

that the PCS signals (CRS, RX_DV, RX_ER, and COL) have no meaning during

this mode. During Symbol operation, pins RX_ER/RXD[4] and TX_ER/TXD[4] are

used as the MSB of the 5 bit RX and TX data symbols.

There is an internal pullup resistor for this pin which is active during the powerup/reset period. If this pin is left floating externally, then the device will configure to

normal mode as a result of power-up/reset. This pin must be externally pulled low

(typically 10 kΩ) in order to configure the DP83843 for Symbol mode operation.

In Symbol mode this pin will indicate the signal detect status of the TP-PMD (active

high).

This mode hasno effect on 10Mb/soperation. The value atthis input is latched into

the DP83843 at power-up, hardware or software reset.

and receive data are exchanged serially at a 10 MHz clock rate on the least significant bits of the nibble-wide MII data buses, pins TXD[0] and RXD[0] respectively.

This mode is intended for use with the DP83843 connected to a MAC using a 10

Mb/s serial interface. Serial operation is not supportedin 100 Mb/s mode, therefore

this input is ignored during 100 Mb/s operation.

There is an internal pullup resistor for this pin which is active during the powerup/reset period. If this pin is left floating externally, then the device will configure to

normal mode as a result of power-up/reset. This pin must be externally pulled low

(typically 10 kΩ) in order to configure the DP83843 for Serial MII operation when

running at 10 Mb/s.

The value at this input is latched into the DP83843 at power-up, hardware or software reset.

I/O, Z 21 FIBER ENABLE: This active low input allows 100 Mb/s transmit and receive data

streams to bypass the scrambler and descrambler circuits when selected. All PCS

signaling remains active and unaffected during this mode. During this mode, the

internal 100 Mb/s transceiver is disabled, and NRZI data is transmitted and

received via the FXTD/AUITD+/− and FXRD/AUIRD+/−pins.

There is an internal pullup resistor for this pin which is active during the powerup/reset period. If this pin is left floating externally, then the device will configure to

normal mode as a result of power-up/reset. This pin must be externally pulled low

(typically 10 kΩ) in order to configure the DP83843 for 100BASE-FX operation.

The value at this input is latched into the DP83843 at power-up, hardware or software reset.

9 www.national.com

1.0 Pin Descriptions (Continued)

1.5 LED Interface

These outputs can be used to drive LEDs directly, or can

be used to provide status information to a network management device. Refer to section 2.2 for a description of

how to generate LED indication of 100 Mb/s mode. The

active state of each LED output driver is dependent on the

logic level sampled by the corresponding PHY address

input upon power-up/reset. For example, if a given PHYAD

Signal Name Type Pin # Description

LED_COL

(PHYAD[0])

LED_TX

(PHYAD[1])

LED_RX

(PHYAD[2])

LED_LINK

(PHYAD[3])

LED_FDPOL

(PHYAD[4])

SPEED10 O 5 SPEED 10 Mb/s: Indicates 10 Mb/soperation when high. Indicates100 Mb/s oper-

I/O 42 COLLISION LED: Indicates the presence of collision activity for 10 Mb/s and 100

Mb/s HalfDuplex operation.This LEDhas nomeaning for10 Mb/sor 100Mb/s Full

Duplex operation andwill remaindeasserted. During10 Mb/shalf duplexmode this

pin will be asserted after data transmission due to the heartbeat function.

The DP83843 incorporates a“monostable” function on the LED_COL output. This

ensures that even collisions generate adequate LED ON time (approximately 50

ms) for visibility.

I/O 41 TRANSMIT LED: Indicates the presence of transmit activity for 10 Mb/s and 100

Mb/s operation.

If bit 7 (LED_Trans_MODE) of the PHYCTRL register (address 19h) is set high,

then the LED_TX pin function is changed to indicate the status of the Disconnect

function as defined by the state of bit 4 (CIM_STATUS) in the 100 Mb/s PCS configuration & status register (address 16h). See register definition for complete description of alternative operation.

TheDP83843 incorporatesa “monostable”function onthe LED_TX output.This ensures that even minimum size packets generate adequate LED ON time (approximately 50 ms) for visibility.

I/O 40 RECEIVE LED: Indicates the presence ofany receive activity for10 Mb/s and 100

Mb/s operation.See register definitions(PHYCTRLregister and PCSR register) for

complete descriptions of alternative operation.

TheDP83843 incorporatesa“monostable” functionon theLED_RXoutput. Thisensures that even minimumsize packetsgenerate adequateLED activetime (approximately 50 ms) for visibility.

I/O 39 LINK LED: Indicates good link status for 10 Mb/s and 100 Mb/s operation.

In 100BASE-Tmode, link is establishedas a result ofinput receive amplitude compliant with TP-PMD specifications which will result in internal generation of Signal

Detect as well as an internal signal from the Clock Recovery Module (cypher &

sync). LED_LINK will assert after these internal signals have remainedasserted for

a minimum of 500µs. Once Link is established, then cipher & sync are no longer

sampled andthe Linkwill remainvalid as longas SignalDetect isvalid. LED_LINK

will deassert immediately following the deassertion of the internal Signal Detect.

10 Mb/slink isestablished asa resultof the receptionof atleast sevenconsecutive

normal Link Pulses or the reception of a valid 10BASE-T packet which will cause

the assertion of LED_LINK. LED_LINK will deassert in accordance with the Link

Loss Timer as specified in IEEE 802.3.

In 100BASE-FX mode, link is established as a result of the assertion of the Signal

detectinput totheDP83843.LED_LINK willassertafter SignalDetecthasremained

asserted for a minimum of 500µS. LED_LINK will deassert immediately following

the deassertion of signal detect.

The link function is disabled during AUI operation and LED_LINK is asserted.

I/O 38 FULL DUPLEX LED: Indicates Full Duplex mode status for 10 Mb/s or 100 Mb/s

operation. This pin can be configured to indicate Polarity status for 10 Mb/s operation. If bit 6 (LED_DUP_MODE) in the PHYCTRL Register (address 19h) is deasserted, the LED_FDPOL pin function is changed to indicate Polarity status for 10

Mb/s operation.

The DP83843 automatically compensates for 10BASE-T polarity inversion.

10BASE-T polarity inversion is indicated by the assertion of LED_FDPOL.

ation when low. This pin can be used to drive peripheral circuitry such as an LED

indicator.

input is resistively pulled low then the corresponding LED

output will be configured as an active high driver. Conversely, if a given PHYAD input is resistively pulled high

then the corresponding LED output will beconfigured as an

active low driver (refer to section 5.0.1 for further details).

Note that these outputs are standard CMOS voltage

drivers and not open-drain.

10 www.national.com

1.0 Pin Descriptions (Continued)

1.6 PHY Address Interface

The DP83843 PHYAD[4:0] inputs provide up to 32 unique

PHY address options. An address selection of all zeros

Signal Name Type Pin # Description

PHYAD[0]

(LED_COL)

PHYAD[1]

(LED_TX)

PHYAD[2]

(LED_RX)

PHYAD[3]

(LED_LINK)

PHYAD[4]

(LED_FDPOL)

I/O 42 PHY ADDRESS[0]: PHYaddress sensingpin for multiplePHY applications.PHY

address sensing is achieved by strapping a pull-up/pull-down resistor (typically 10

kΩ) to this pin as required.

The pull-up/pull-down status of this pin is latched into the PHYCTRL register (address 19h, bit 0) during power up/reset.

I/O 41 PHY ADDRESS[1]: PHYaddress sensingpin formultiple PHYapplications. PHY

address sensing is achieved by strapping a pull-up/pull-down resistor (typically 10

kΩ) to this pin as required.

The pull-up/pull-down status of this pin is latched into the PHYCTRL register (address 19h, bit 1) during power up/reset.

I/O 40 PHY ADDRESS[2]: PHYaddress sensingpin for multiplePHY applications.PHY

address sensing is achieved by strapping a pull-up/pull-down resistor (typically 10

kΩ) to this pin as required.

The pull-up/pull-down status of this pin is latched into the PHYCTRL register (address 19h, bit 2) during power up/reset.

I/O 39 PHY ADDRESS[3]: PHYaddress sensingpin for multiplePHY applications.PHY

address sensing is achieved by strapping a pull-up/pull-down resistor (typically 10

kΩ) to this pin as required.

The pull-up/pull-down status of this pin is latched into the PHYCTRL register (address 19h, bit 3) during power up/reset.

I/O 38 PHY ADDRESS[4]: PHYaddress sensingpin for multiplePHY applications.PHY

address sensing is achieved by strapping a pull-up/pull-down resistor (typically 10

kΩ) to this pin as required.

The pull-up/pull-down status of this pin is latched into the PHYCTRL register (address 19h, bit 4) during power up/reset.

(00000) will result in a PHY isolation condition as a

result of power-on/reset, as specified in IEEE 802.3u.

1.7 Reset

Signal Name Type Pin # Description

RESET I 1 RESET:Active high input thatinitializes or reinitializes the DP83843. Asserting this

pin will force a reset process to occur which will result in all internal registers reinitializing to their default states as specified for each bit in section 7.0, and all strapping options are reinitialized. Refer to section 5.0 for further detail regarding reset.

11 www.national.com

1.0 Pin Descriptions (Continued)

1.8 Power And Ground Pins

The power (VCC) and ground (GND) pins of the DP83843

are grouped in pairs into three categories--TTL/CMOS

Input pairs, Transmit/Receive supply pairs, and Internal

Signal Name Pin # Description

TTL/CMOS INPUT/OUTPUT SUPPLY PAIRS

IO_VDD1

IO_VSS1

IO_VDD2

IO_VSS2

IO_VDD3

IO_VSS3

IO_VSS4 32 TTL Input/Output Supply #4

IO_VDD5

IO_VSS5

PCS_VDD

PCS_VSS

TRANSMIT/RECEIVE SUPPLY PAIRS

AUIFX_VDD

AUIFX_GND

TR_AVDD

TR_AGND

TW_AVDD

TW_AGND

CD_VDD0

CD_GND0

CD_VDD1

CD_GND1

INTERNAL SUPPLY PAIRS

CP_AVDD

CP_AGND

CPTW_DVDD

CPTW_DVSS

ATP_GND 57 100BASE-T PMD Supply

SUB_GND1,

SUB_GND2

6

7

16

17

26

27

36

37

10

11

46

45

79

80

68

64

72

71

76

75

52

51

54

53

70

77

TTL Input/Output Supply #1

TTL Input/Output Supply #2

TTL Input /Output Supply #3

TTL Input/ Output Supply #5

Physical Coding Sublayer Supply

AUI Power Supply

10 Mb/s Supply

100 Mb/s Power Supply

Common Driver Supply

Common Driver Supply

CRM/CGM Supply

CRM/CGM Supply

100BASE-T PMD Supply

supply pairs. This grouping allows for optimizing the layout

and filtering of the power and ground supplies to this

device.

1.9 Special Connect Pins

Signal Name Type Pin # Description

NC 2,55,56,

58,59,

62

NO CONNECT: These pins are reserved for future use. Leave them unconnected

(floating).

12 www.national.com

2.0 Functional Description

2.1 802.3u MII

The DP83843 incorporates the Media Independent Interface (MII) as specified in clause 22 of the IEEE 802.3u

standard. This interface may be used to connect PHY

devices toa 10/100 Mb/s MAC ora 100 Mb/s repeater controller. This section describes both the serial MII management interface as well as the nibble wide MII data interface.

The management interface of the MII allows the configuration and control of multiple PHY devices, the gathering of

status and error information, and the determination of the

type and abilities of the attached PHY(s).

The nibble wide MII data interface consists of a receive bus

and a transmit bus each with control signals to facilitate

data transfer between the PHY and the upper layer (MAC

or repeater).

The DP83843 supports the TI ThunderLAN® MII interrupt

function. For further information please contact your local

National sales representative.

2.1.1 Serial Management Register Access

The serial MII specification defines a set of thirty-two 16-bit

status and control registers that are accessible through the

serial management data interface pins MDC and MDIO.

The DP83843 implements all the required MII registers as

well as several optional registers. These registers are fully

described in Section 7. A description of the serial management access protocol follows.

2.1.2 Serial Management Access Protocol

The serial control interface consists of two pins, Management Data Clock (MDC) and Management Data Input/Out-

and no minimum rate. The MDIO line is bi-directional and

may be shared by up to 32 devices. The MDIO frame format is shown in Table 1.

The MDIO pin requires a pull-up resistor (1.5 kΩ) which,

during IDLE and turnaround, will pull MDIO high. In order

to initialize the MDIO interface, the Station Management

Entity (SME) sends a sequence of 32 contiguous logic

ones on MDIO to provide the DP83843 with a sequence

that can be used to establish synchronization. This preamble may be generated either by driving MDIO high for 32

consecutive MDC clock cycles, or by simply allowing the

MDIO pull-up resistor to pull the MDIO pin high during

which time 32 MDC clock cycles are provided. In addition

32 MDC clock cycles should be used if an invalid start, op

code, or turnaround bit is detected.

The DP83843 waits until it has received this preamble

sequence before responding to any other transaction.

Once the DP83843 serial management port has initialized

no further preamble sequencing is required until after a

power-on/reset has occurred.

The Start code isindicated by a <01>pattern.This assures

the MDIO line transitions from the default idle line state.

Turnaround is an idle bit time inserted between the Register Address field andthe Data field. To avoid contention, no

device actively drives the MDIO signal during the first bit of

Turnaround during a read transaction. The addressed

DP83843 drives the MDIO with a zero for the second bit of

turnaround and follows thiswith the required data. Figure 2

shows the timing relationship between MDC and the MDIO

as driven/received by the Station Management Entity and

the DP83843 (PHY) for a typical register read access.

put (MDIO). MDC has a maximum clock rate of 2.5 MHz

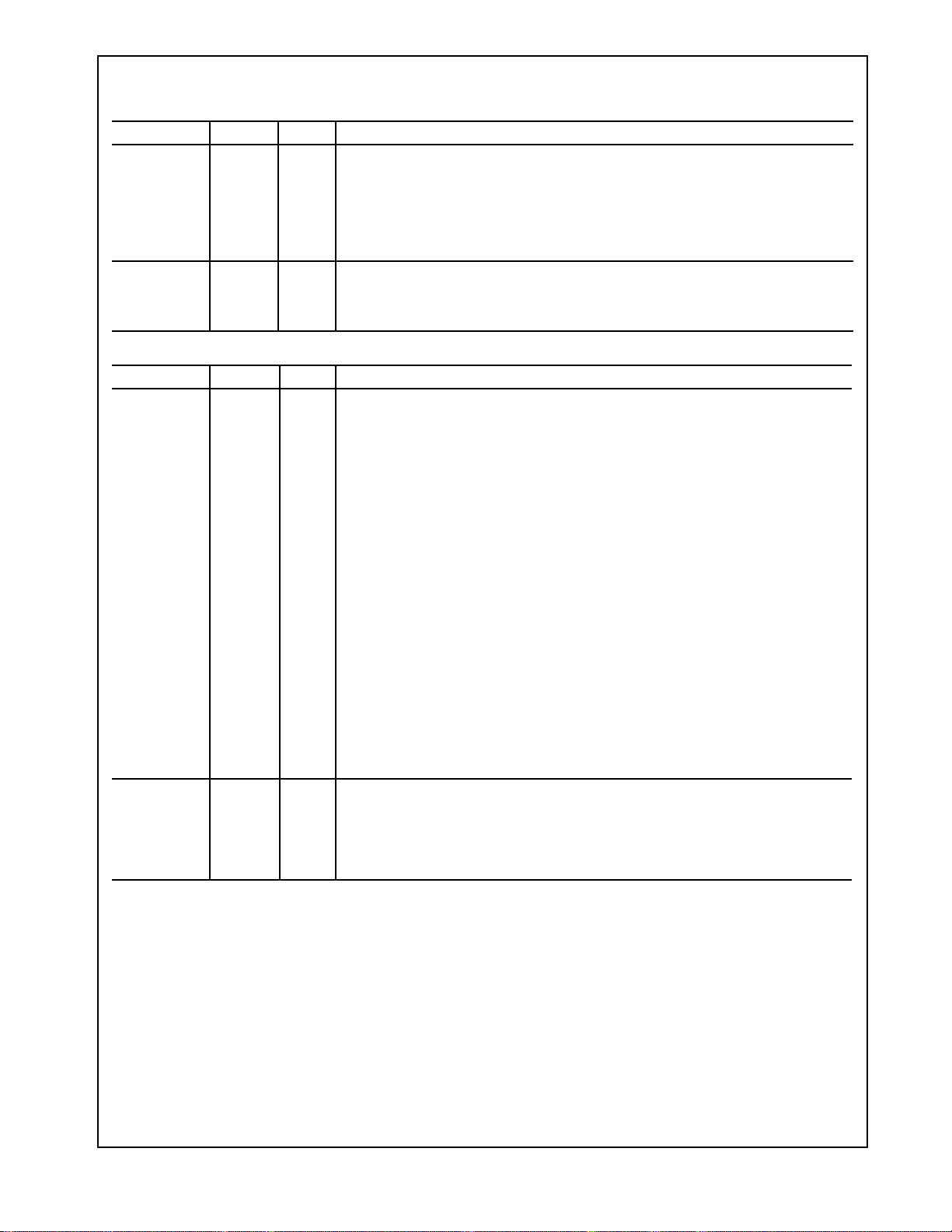

Table 1. Typical MDIO Frame Format

MII Management

<idle><start><op code><device addr> <reg addr><turnaround><data><idle>

Serial Protocol

Read Operation <idle><01><10><AAAAA> <RRRRR><Z0><xxxx xxxx xxxx xxxx><idle>

Write Operation <idle><01><01><AAAAA> <RRRRR><10><xxxx xxxx xxxx xxxx><idle>

MDC

MDIO

(SME)

MDC

MDIO

(SME)

MDIO

(PHY)

00011110000000

Z

Idle Start

Opcode

(Write)

PHY Address

(PHYAD = 0Ch)

Register Address

(00h = BMCR)

Figure 1. Typical MDC/MDIO Write Operation

Z

Z

00011 110000000

Idle Start

Opcode

(Read)

PHY Address

(PHYAD = 0Ch)

Register Address

Figure 2. Typical MDC/MDIO Read Operation

(00h = BMCR)

ZZ

0 0 0 000 00000000

1000

TA

Z

Z

Z

0 0 011000100000000

TA

Register Data

Register Data

Z

Idle

Z

Z

Idle

13 www.national.com

2.0 Functional Description (Continued)

For write transactions, the Station Management Entity

writes data to an addressed DP83843 eliminating the

requirement for MDIO Turnaround. The Turnaround time is

filled by the management entity inserting <10> for these

two bits. Figure 1shows the timing relationship for a typical

MII register write access.

2.1.3 Preamble Suppression

The DP83843 supports a Preamble Suppression mode as

indicated by a one in bit 6 of the Basic Mode Status Register (BMSR, address 01h). If the Station Management Entity

(i.e. MAC or other management controller) determines that

all PHYs in the system support Preamble Suppression by

returning a one in this bit, then the Station Management

Entity need not generate preamble for each management

transaction.

The DP83843 requires a single initialization sequence of

32 bits of preamble following power-up/hardware reset.

This requirement is generallymet by the mandatory pull-up

resistor on MDIO in conjunction with a continuous MDC, or

the management access made to determine whether Preamble Suppression is supported.

While the DP83843 requires an initial preamble sequence

of 32 bits for management initialization, it does not require

a full 32 bit sequence between each subsequent transaction. A

transactions is required

2.1.4 PHY Address Sensing

The DP83843 can be set to respond to any of the possible

32 PHY addresses. Each DP83843 connected to a common serial MII must have a unique address. It should be

noted that while an address selection of all zeros <00000>

will result in PHY Isolate mode, this will not effect serial

management access.

The DP83843 provides five PHY address pins, the state of

which are latched into the PHYCTRL register (address

19h) at system power-up/reset. These pins are described

in Section 2.8. For further detail relating to the latch-in timing requirements of the PHY address pins, as well as the

other hardware configuration pins, refer to Section 3.10.

2.1.5 Nibble-wide MII Data Interface

Clause 22 of the IEEE 802.3u specification defines the

Media Independent Interface. This interface includes a

dedicated receive bus and a dedicated transmitbus. These

two data buses, along with various control and indicate signals, allow for the simultaneous exchange of data between

the DP83843and the upper layer agent(MAC or repeater).

The receive interface consists of a nibble wide data bus

RXD[3:0], a receive error signal RX_ER, a receive data

valid flag RX_DV, anda receive clock RX_CLK for synchronous transfer of the data. The receive clock can operate at

either 2.5 MHz to support 10 Mb/s operation modes or at

25 MHz to support 100 Mb/s operational modes.

The transmit interface consists of a nibble wide data bus

TXD[3:0], a transmit error flag TX_ER, a transmit enable

control signal TX_EN, and a transmit clock TX_CLK which

runs at either 2.5 MHz or 25 MHz.

Additionally, the MII includes the carrier sense signal CRS,

as well as a collision detect signal COL. The CRS signal

asserts to indicate the reception of data from the network

or as a function of transmit data in Half Duplex mode. The

COL signal asserts asan indication of a collisionwhich can

minimum of one idle bit between management

as specified in IEEE 802.3u.

occur during half-duplex operation when both a transmit

and receive operation occur simultaneously.

2.1.6 Collision Detect

For Half Duplex, a 10BASE-T or 100BASE-X collision is

detected when the receive and transmit channels are

active simultaneously. Collisions are reported by the COL

signal on the MII.

If the DP83843 is transmitting in 10 Mb/s modewhen a collision is detected, the collision is not reported until seven

bits have been received while in the collision state. This

prevents a collision being reported incorrectly due to noise

on the network. The COL signal remains set for the duration of the collision.

If a collision occurs during a receive operation, it is immediately reported by the COL signal.

When heartbeat is enabled (only applicable to 10 Mb/s

operation), approximately 1 µs after the transmission of

each packet,a Signal Quality Error (SQE) signal ofapproximately 10 bit times is generated (internally) to indicate

successful transmission. SQEis reported as a pulse on the

COL signal of the MII.

2.1.7 Carrier Sense

Carrier Sense (CRS) may be asserted due to receiveactivity, once valid data is detected via the Smart Squelch function during 10 Mb/s operation.

For 10 Mb/s Half Duplex operation, CRS is asserted during

either packet transmission or reception.

For 10 Mb/s Full Duplex operation, CRS is asserted only

due to receive activity.

CRS is deasserted following an end of packet.

In Repeater mode(pin 63/bit 9, register address19h), CRS

is only asserted due to receive activity.

2.1.8 MII Isolate Mode

A 100BASE-X PHY connected to the mechanical MII interface specified in IEEE 802.3u is required to have a default

value of one in bit 10 of the Basic Mode Control Register

(BMCR, address 00h). The DP83843 will set this bit to one

if the PHY Address is set to 00000 upon power-up/hardware reset. Otherwise, the DP83843 will set this bit to zero

upon power-up/hardware reset.

With bit 10 in the BMCR set to one, the DP83843 does not

respond to packet data present at TXD[3:0], TX_EN, and

TX_ER inputs and presents a high impedance on the

TX_CLK, RX_CLK, RX_DV, RX_ER, RXD[3:0], COL, and

CRS outputs. The DP83843 will continue to respond to all

serial management transactions over the MII.

While in Isolate mode, the TPTD+/− and FXTD/AUITD+/−

outputs are dependent on the current state of Auto-Negotiation. The DP83843 can Auto-Negotiate or parallel detect

to a specific technology depending on the receive signal at

the TPRD+/− inputs. A valid link can be established for

either TPRD or FXRD/AUI even when the DP83843 is in

Isolate mode.

It is recommended that the user have a basic understanding of clause 22 of the 802.3u standard.

14 www.national.com

2.0 Functional Description (Continued)

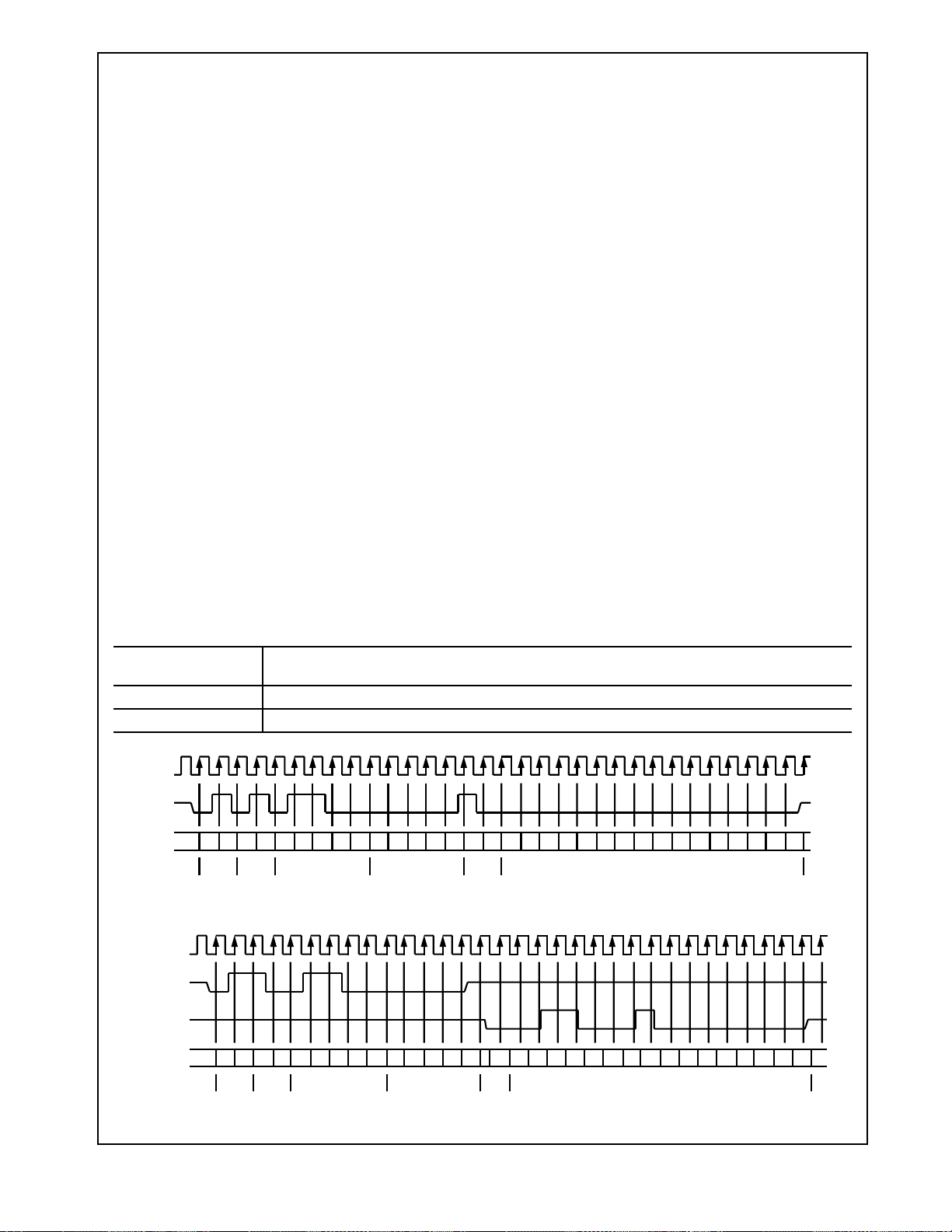

2.2 100BASE-TX TRANSMITTER

The 100BASE-TX transmitter consists of several functional

blocks which convert synchronous 4-bit nibbledata, as provided bythe MII, to a scrambled MLT-3 125 Mb/s serial data

stream. Because the 100BASE-TX TP-PMD is integrated,

the differential outputpins, TPTD+/−, can be directly routed

to the AC coupling magnetics.

The block diagram in Figure 3 provides an overview of

each functional block within the 100BASE-TX transmit section.

The Transmitter section consists of the following functional

blocks:

CODE-GROUP

ENCODER &

INJECTOR

— Code-group EncoderandInjection block(bypass option)

— Scrambler block (bypass option)

— NRZ to NRZI encoder block

— Binary to MLT-3 converter / Common Driver

The bypass option for the functional blocks within the

100BASE-X transmitter provides flexibility for applications

such as 100 Mb/s repeaters where data conversion is not

always required. The DP83843 implements the 100BASEX transmit state machine diagram as specified in the IEEE

802.3u Standard, Clause 24.

SCRAMBLER

PARALLEL

TO SERIAL

NRZ TO NRZI

ENCODER

Figure 1. 100BASE-TX Transmit Block Diagram

– Code-group Encoding and Injection

15 www.national.com

2.0 Functional Description (Continued)

The code-group encoder converts 4 bit (4B) nibble data

generated bythe MAC into5 bit (5B) code-groups for transmission. This conversion is required to allow control data to

be combined with packet data code-groups. Refer to Table

2 for 4B to 5B code-group mapping details.

The code-group encoder substitutes the first 8 bits of the

MAC preamble with a J/K code-group pair (11000 10001)

upon transmit. The code-group encoder continues to

replace subsequent 4B preamble and data nibbles with

corresponding 5B code-groups. At the end of the transmit

packet, upon the deassertion of Transmit Enable signal

from the MAC or Repeater, the code-group encoder injects

the T/R code-group pair (01101 00111) indicating the end

of frame.

After the T/R code-group pair, the code-group encoder

continuously injects IDLEs into the transmit data stream

until the next transmit packet is detected (reassertion of

Transmit Enable).

The DP83843 also incorporates a special injection function

which allowsfor fixed transmission of special repeating patterns for testing purposes. These special patterns are not

delimited with Start of Stream Delimiter (SSD) or End of

Stream Delimiter (ESD) code-groups and should not be

enabled during normal network connectivity.

These patterns, selectable via bits [8:7] of PCRS (address

16h), include:

8=0, 7=0: Normal operation (injection disabled)

8=0, 7=1: Transmit repeating FEFI pattern

8=1, 7=0: Transmit repeating 1.28 µs period squarewave

8=1, 7=1: Transmit repeating 160 ns period squarewave

Note that these patterns will be routed through thetransmit

scrambler and become scrambled (and therefore potentially less useful) unless the scrambler is bypassed via bit

12 of LBR (address 17h). It should be noted that if the

scrambler isbypassed by forcing the

quently resetting the device) the TPTD+/− outputs will

become disabled and the test pattern data will be routed to

the FXTD/AUITD+/− outputs. Additionally, the test patterns

will not be generated if the DP83843 is in symbol mode.

FXEN pin (and subse-

2.2.1 Scrambler

The scrambler is required to control the radiatedemissions

at the media connector and on the twisted pair cable (for

100BASE-TX applications). By scrambling the data, the

total energy launched onto the cable is randomly distributed over a wide frequency range. Without the scrambler,

energy levels at the PMD and on the cable could peak

beyond FCC limitations at frequencies related to repeating

5B sequences (i.e., continuous transmission of IDLEs).

The scrambler is configured as a closed loop linear feedback shift register (LFSR) with an 11-bit polynomial. The

output of the closed loop LFSR is combined with the NRZ

5B data from the code-group encoder via an X-OR logic

function. The result is a scrambled data stream with sufficient randomization to decrease radiated emissions at certain frequencies by as much as 20 dB. The DP83843 uses

the PHYID as determined by the PHYAD [4:0] pins to set a

unique seed value for thescrambler so thatthe total energy

produced by a multi-PHY application (i.e. repeater) distributes the energy out of phase across the spectrum and

helps to reduce overall electro-magnetic radiation.

The scrambler is automatically bypassed when the

DP83843 is placed in

tively, controlled by bit 12 of LBR (address 17h) via software.

2.2.2 NRZ to NRZI Encoder

After the transmit data stream has been scrambled and

serialized, the datamust be NRZI encodedin order to comply with the TP-PMD standard for 100BASE-TX transmission over Category-5 unshielded twisted pair cable. There

is no ability to bypass this block within the DP83843.

2.2.3 Binary to MLT-3 Convertor / Common Driver

The Binary to MLT-3 conversion is accomplished by converting the serial binary datastream output from the NRZI

encoder into two binary data streams with alternately

phased logic one events. These two binary streams are

then fed to the twisted pair output driver which converts

these streams to current sources and alternately drives

either side of the transmit transformer primary winding

resulting in a minimal current (20 mA max) MLT-3 signal.

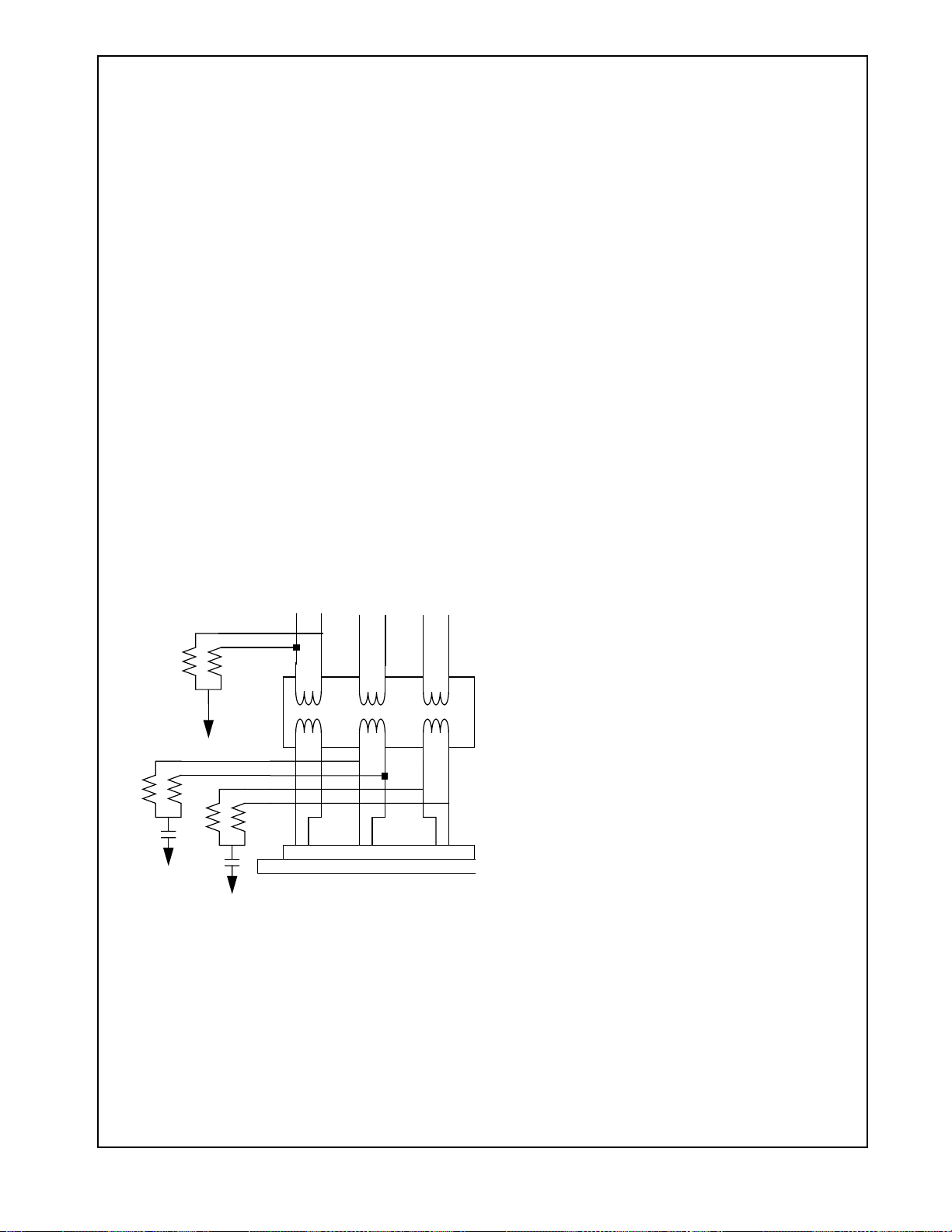

Refer to Figure 4 .

FXEN mode via hardware or,alterna-

binary_in

binary_in

D

Q

Q

CP

Figure 1. Binary to MLT-3 conversion

binary_plus

binary_minus

differential MLT-3

binary_plus

COMMON

DRIVER

binary_minus

16 www.national.com

MLT-3

2.0 Functional Description (Continued)

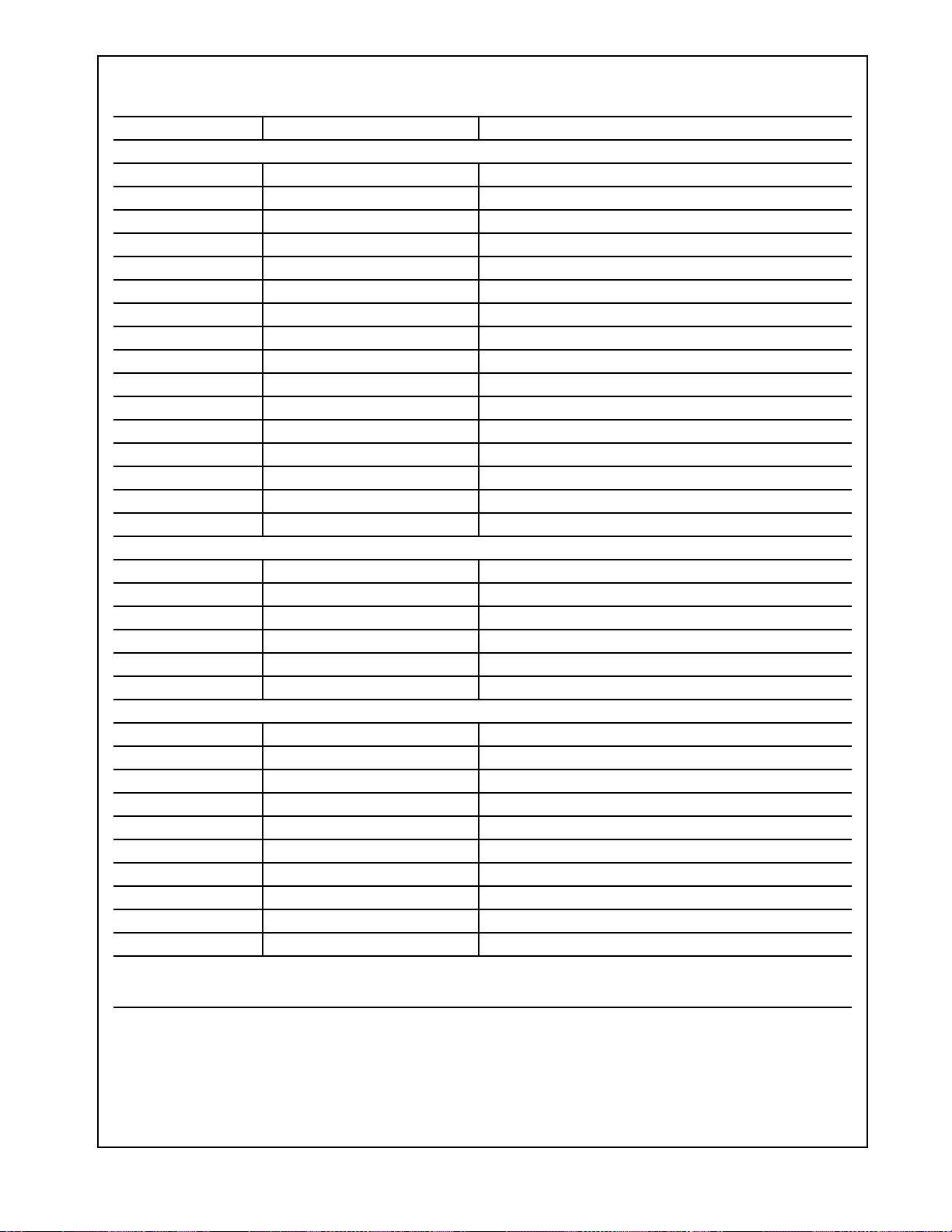

Table 2. 4B5B Code-Group Encoding/Decoding

Name PCS 5B Code-group MII 4B Nibble Code

DATA CODES

0 11110 0000

1 01001 0001

2 10100 0010

3 10101 0011

4 01010 0100

5 01011 0101

6 01110 0110

7 01111 0111

8 10010 1000

9 10011 1001

A 10110 1010

B 10111 1011

C 11010 1100

D 11011 1101

E 11100 1110

F 11101 1111

IDLE AND CONTROL CODES

H 00100 Halt code-group - Error code

I 11111 Inter-Packet Idle - 0000 (

J 11000 First Start of Packet - 0101 (Note 1)

K 10001 Second Start of Packet - 0101 (Note 1)

T 01101 First End of Packet - 0000 (Note 1)

R 00111 Second End of Packet - 0000 (Note 1)

INVALID CODES

V 00000 0110 or 0101 (

Note 2)

V 00001 0110 or 0101 (Note 2)

V 00010 0110 or 0101 (Note 2)

V 00011 0110 or 0101 (Note 2)

V 00101 0110 or 0101 (Note 2)

V 00110 0110 or 0101 (Note 2)

V 01000 0110 or 0101 (Note 2)

V 01100 0110 or 0101 (Note 2)

V 10000 0110 or 0101 (Note 2)

V 11001 0110 or 0101 (Note 2)

Note 1: Control code-groups I, J, K, T and R in data fields will be mapped as invalid codes, together with RX_ER asserted.

Note 2: Normally, invalidcodes (V)are mappedto 6hon RXD[3:0]with RX_ERasserted. Ifthe CODE_ERRbit inthe PCS (bit 3, register address 16h)

is set, the invalid codes are mapped to 5h on RXD[3:0] with RX_ER asserted. Refer to Section 4.14 for further detail.

Note 1)

17 www.national.com

2.0 Functional Description (Continued)

The 100BASE-TX MLT-3 signal sourced by the TPTD+/−

common driver output pins is slow rate controlled. This

should be considered when selecting AC coupling magnetics to ensure TP-PMD compliant transition times (3 ns < Tr

< 5ns).

The 100BASE-TX transmit TP-PMD function within the

DP83843 is capable of sourcing only MLT-3 encoded data.

Binary output from the TPTD+/− outputs is not possible in

100 Mb/s mode.

2.2.4 TX_ER

Assertion of the TX_ERinput while the TX_EN inputis also

asserted will cause the DP83843 to substitute HALT codegroups for the 5B data present at TXD[3:0]. However, the

SSD (/J/K/) and ESD (/T/R/) will not be substituted with

Halt code-groups. As a result, the assertion of TX_ER

while TX_EN is asserted will result in a frame properly

encapsulated with the /J/K/ and /T/R/ delimiters which contains HALT code-groups in place of the data code-groups.

2.2.5 TXAR100

The transmit amplitude of the signal presented at the

TPTD+/− outputpins can be controlled byvarying the value

of resistance between TXAR100 and system GND. This

TXAR100 resistor sets up a reference current that determines the final output current at TPTD+/−.

For 100Ω Category-5 UTP cable implementations, the

TXAR100 resistor may be omitted as the DP83843 was

designed to source a nominal 2V pk-pk differential transmit

amplitude with this pin left floating. Setting the transmit

amplitude to 2V pk-pk differential (MLT-3) as measured

across the RJ45-8 transmit pins is critical for complying

with the IEEE/ANSI TP-PMD specification of 2.0V pk-pk

differential ±5%.

2.3 100BASE-TX RECEIVER

The 100BASE-TX receiver consists of several functional

blocks which convert the scrambled MLT-3 125 Mb/s serial

data stream to synchronous 4-bit nibble data that is provided to the MII. Because the 100BASE-TX TP-PMD is

integrated, the differential input pins, TPRD+/−, can be

directly routed to the AC coupling magnetics.

See Figure 5 for a block diagram of the 100BASE-TX

receive function. This provides an overview of each functional block within the 100BASE-TX receive section.

The Receive section consists of the following functional

blocks:

— Input and BLW Compensation

— Signal Detect

— Digital Adaptive Equalization

— MLT-3 to Binary Decoder

— Clock Recovery Module

— NRZI to NRZ Decoder

— Serial to Parallel

— DESCRAMBLER (bypass option)

— Code Group Alignment

— 4B/5B Decoder (bypass option)

— Link Integrity Monitor

— Bad SSD Detection

The bypass option for the functional blocks within the

100BASE-X receiver provides flexibility for applications

such as 100 Mb/s repeaters where data conversion is not

always required.

2.3.1 Input and Base Line Wander Compensation

Unlike the DP83223V TWISTER™, the DP83843 requires

no external attenuation circuitry at its receive inputs,

TPRD+/−. The DP83843accepts TP-PMD compliant waveforms directly, requiring only a 100Ω termination plus a

simple 1:1 transformer. The DP83843 also requires external capacitance to V

ure 23). This establishes a solid common mode voltage

that is needed since the TPRD pins are used in both 10

Mb/s and 100 Mb/s modes.

The DP83843 is completely ANSI TP-PMD compliant

because it compensates for baseline wander. The BLW

compensation block can successfully recover the TP-PMD

defined “killer” pattern and pass it to the digital adaptive

equalization block.

Baseline wander cangenerally be defined as thechange in

the average DC content, over time, of an AC coupled digital

transmission over a given transmission medium. (i.e. copper wire).

Baseline wander results from the interaction between the

low frequency components of a bit stream being transmitted and the frequency response of the AC coupling component(s) within thetransmission system. If the low frequency

content of the digital bit stream goes below the low frequency pole of the AC coupling transformers then the

droop characteristics of the transformers will dominate

resulting in potentially serious baseline wander.

It is interesting to note that the probability of a baseline wander event serious enough to corrupt data is very low. In fact,

it is reasonable to virtually bound the occurrence of a baseline wander event serious enough to cause bit errors to a

legal but premeditated, artificially constructed bit sequence

loaded into the original MAC frame. Several studies have

been conducted to evaluate the probability of various baseline wander events for FDDI transmission over copper. Contact the X3.263 ANSI group for further information.

2.3.2 Signal Detect

The signal detect function of the DP83843 is incorporated

to meet the specificationsmandated by the ANSI FDDI TPPMD Standard as well as the IEEE 802.3 100BASE-TX

Standard for both voltage thresholds and timing parameters.

Note that the reception of Normal 10BASE-T link pulses

and fast link pulses per IEEE 802.3u Auto-Negotiation by

the 100BASE-X receiver do not cause the DP83843 to

assert signal detect.

While signal detect is normally generated and processed

entirely within the DP83843, it can be observed directly on

the CRS pin (pin 22) while the DP83843 is configured for

Symbol mode.Refer to Section3.4 for further detailregarding Symbol mode operation.

2.3.3 Digital Adaptive Equalization

When transmitting data at high speeds over copper twisted

pair cable, frequency dependent attenuation becomes a

concern. In high speed twisted pair signalling, the frequency content of the transmitted signal can vary greatly

during normal operation based primarily on the randomness of the scrambled data stream. This variation in signal

at the VCM_CAP pin (refer to Fig-

CC

18 www.national.com

2.0 Functional Description (Continued)

CARRIER

INTEGRITY

MONITOR

LINK INTEG-

RITY MONITOR

RX_DATA

VALID SSD

DETECT

RX_CLK RXD[3:0] / RX_ER

BP_RX

BP_4B5B

BP_SCR

MUX

MUX

4B/5B

DECODER

CODE GROUP

ALIGNMENT

MUX

DESCRAMBLER

SD

CLOCK

CLOCK

RECOVERY

MODULE

DAT A

SERIAL TO

PARALLEL

NRZI TO NRZ

DECODER

MLT-3 TO

BINARY

DECODER

DIGITAL

ADAPTIVE

EQUALIZATION

INPUT

&BLW

COMPEN-

SATION

SIGNAL

DETECT

TPRD +/−

Figure 1. Receive Block Diagram

19 www.national.com

2.0 Functional Description (Continued)

t

attenuation caused by frequency variations must be compensated for to ensure the integrity of the transmission.

In order to ensure quality transmission when employing

MLT-3 encoding, the compensation must be able to adapt

to various cable lengths and cable types depending on the

installed environment. The selection of long cable lengths

for a given implementation, requires significant compensation which will over-compensate for shorter, less attenuating lengths. Conversely, the selection of short or

intermediate cable lengths requiring less compensation will

cause serious under-compensation for longer length

cables. Therefore, the compensation or equalization must

be adaptive to ensure proper conditioning of the received

signal independent of the cable length.

The DP83843 utilizes an extremely robust equalization

scheme referred to herein as ‘Digital Adaptive Equalization.’ Existing designs use an adaptive equalization scheme

that determines the approximate cable length by monitoring signal attenuation at certain frequencies. This attenuation value was compared to the internal receive input

reference voltage. This comparison would indicate that

amount of equalization to use. Although this scheme is

used successfully on the DP83223V TWISTER, it is sensitive totransformer mismatch, resistor variation and process

induced offset. The DP83223V also required an external

attenuation network to help match the incoming signal

amplitude to the internal reference.

Digital Adaptive Equalization is based on an advanced digitally controlled signal tracking technique. This method

uses peak tracking with digital over-sampling and digitally

controlled feedback loops to regenerate the receive signal.

This technique does not depend on input amplitude variations to set the equalization factor. As a result it maintains

constant jitter performance for any cable length up to 150

meters of CAT-5. Digital Adaptive Equalization allows for

very high tolerance to signal amplitude variations.

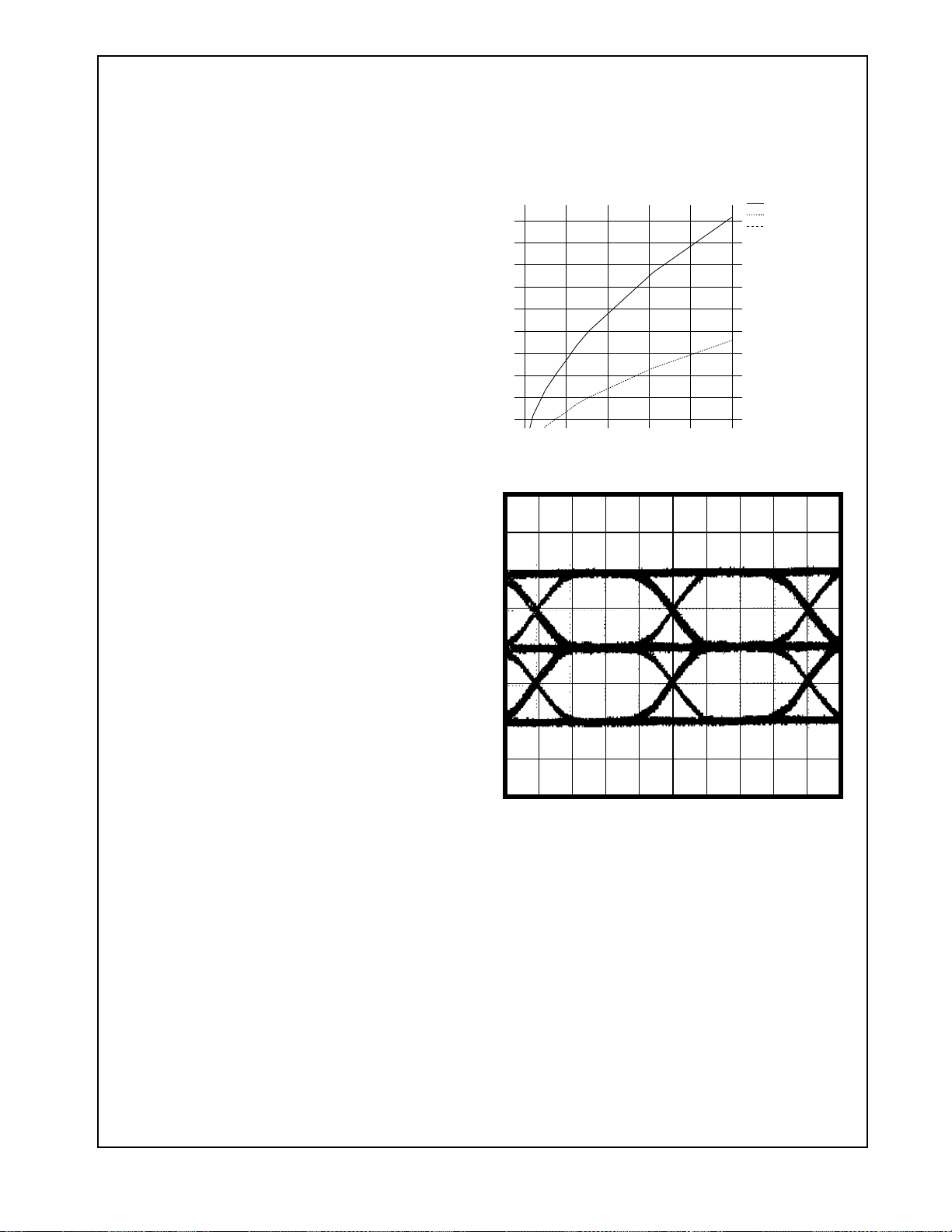

The curves given in Figure 6illustrate attenuation at certain

frequencies forgiven cablelengths. This isderived from the

worst case frequency vs. attenuation figures as specified in

the EIA/TIA BulletinTSB-36. These curves indicate the significant variations in signal attenuation that must be compensated for by the receive adaptive equalization circuit.

Figure 7 represents a scrambled IDLE transmitted over

zero meters of cable as measured at the AII (Active Input

Interface) of the receiver. Figure 8 and Figure 9 represent

the signal degradation over 50 and 100 Meters of CAT-5

cable respectively, also measured at the AII. These plots

show the extreme degradation of signal integrity and indicate the requirement for a robust adaptive equalizer.

The DP83843 provides the added flexibility of controlling

the type of receive equalization required for a given implementation. This is done through TW_EQSEL (bits [13:12]

of the PHYCTRLregister, address 19h).While digital adaptive equalization is the preferred method of cable compensation for 100BASE-TX, the ability to switch the equalizer

completely off or to a fixed maximum is provided. This feature is intended as a test mode only and, if enabled, will

inhibit normal performance of the DP83843.

2.3.4 MLT-3 to NRZI Decoder

The DP83843 decodes theMLT-3 information from the Digital Adaptive Equalizer block to binary NRZI data. The relationship of binary to MLT-3 data is shown in Figure 4.

enuation (dB)

22.00

20.00

18.00

16.00

14.00

12.00

10.00

8.00

6.00

4.00

100M

50M

0M

Figure 1. EIA/TIA Attenuation vs Frequency for 0, 50,

100 meters of CAT-5 cable

2ns/div

Figure 2. MLT-3 SignalMeasured atAII after0 metersof

2.3.5 Clock Recovery Module

The Clock Recovery Module (CRM) accepts 125 Mb/s

NRZI datafrom the MLT-3 to NRZI decoder. TheCRM locks

onto the 125 Mb/sdata stream and extracts a 125 MHz reference clock. The extracted and synchronized clock and

data are used as required by the synchronous receive

operations as generally depicted in Figure 5.

The CRM is implemented using an advanced digital Phase

Locked Loop (PLL) architecture that replaces sensitive

analog circuits. Using digital PLL circuitry allows the

DP83843 to be manufactured and specified to tighter tolerances.

For further information relating to the 100BASE-X clock

recovery module, refer to Section 4.3.

CAT-5 cable

20 www.national.com

2.0 Functional Description (Continued)

2ns/div

Figure 1. MLT-3 Signal Measured at AII after 50 meters

of CAT-5 cable

2ns/div

Figure 2. MLT-3 Signal Measured at AII after 100 meters

of CAT-5 cable

2.3.6 NRZI to NRZ

In a typical application, the NRZI to NRZ decoder is

required in order to present NRZ formatted data to the

descrambler (or to the code-group alignment block, if the

descrambler is bypassed, or directly to the PCS, if the

receiver is bypassed).

The receive data stream is in NRZI format, therefore, the data

must be decoded to NRZ before further processing.

2.3.7 Serial to Parallel

The 100BASE-X receiver includes a Serial to Parallel converter which supplies 5 bit wide data symbols to the

Descrambler. Converting to parallel helps to decrease

latency through the device, as well as performing the

required function for ultimately providing data to the nibblewide interface of the MII.

2.3.8 Descrambler

A 5-bit parallel (code-group wide) descrambler is used to

descramble the receive NRZ data. To reverse the data

scrambling process, the descrambler has to generate an

identical data scrambling sequence (N) in order to recover

the original unscrambled data (UD) from the scrambled

data (SD) as represented in the equations:

SD UD N⊕()=

UD SD N⊕()=

Synchronization of the descrambler to the original scrambling sequence (N) is achieved based on the knowledge

that the incoming scrambled data stream consists of

scrambled IDLE data. After the descrambler has recognized 12 consecutive IDLE code-groups, where an IDLE

code-group in 5B NRZ is equal to five consecutive ones

(11111), it will synchronize to the receive data stream and

generate unscrambled data in the form of unaligned 5B

code-groups.

In order to maintain synchronization, the descrambler must

continuously monitor the validity of the unscrambled data

that it generates. To ensure this, a line state monitor and a

hold timer are used to constantly monitor the synchronization status. Upon synchronization of the descrambler the

hold timer starts a 722 µs countdown. Upon detection of

sufficient IDLE code-groups within the 722 µs period, the

hold timer will reset and begin anew countdown. Thismonitoring operation will continue indefinitely given a properly

operating network connection with good signal integrity. If

the line state monitor does not recognize sufficient

unscrambled IDLE code-groups within the 722 µs period,

the entire descrambler will be forced out of the current state

of synchronization andreset in order to re-acquire synchronization.

The value of the time-out for this timer may be modified

from 722 sto 2 ms by setting bit 12 of the PCSR (address

16h) to one.The 2 ms option allows applications with Maximum Transmission Units (packet sizes) larger than IEEE

802.3 specifications to maintain descrambler synchronization (i.e. switch or router applications).

Additionally, this timer may be disabled entirely by setting

bit 11 of the PCSR (address 16h) to one. The disabling of

the time-out timer is not recommended as this will eventually result in a lackof synchronization between the transmit

scrambler and the receive descrambler which will corrupt

data. The descrambler time-out counter may be reset bybit

13 of the PCSR.

2.3.9 Code-group Alignment

The code-group alignment module operates on unaligned

5-bit data from the descrambler (or, if the descrambler is

bypassed, directly from the NRZI/NRZ decoder) and converts it into 5B code-group data (5 bits). Code-group alignment occurs after the J/K code-group pair is detected.

Once the J/K code-group pair (11000 10001) is detected,

subsequent data is aligned on a fixed boundary.

2.3.10 4B/5B Decoder

The code-group decoder functions as a look up table that

translates incoming 5B code-groups into 4B nibbles. The

code-group decoder first detects the J/K code-group pair

preceded by IDLE code-groups and replaces the J/K with

21 www.national.com

2.0 Functional Description (Continued)

the MAC preamble. Specifically, the J/K 10-bit code-group

pair is replaced by the nibble pair (0101 0101). All subsequent 5B code-groups are converted to the corresponding

4B nibbles for the duration of the entire packet. This conversion ceases upon the detection of the T/R code-group

pair denoting theEnd of Stream Delimiter(ESD) or with the

reception of a minimum of two IDLE code-groups.

2.3.11 100BASE-X Link Integrity Monitor

The 100BASE-X Link Integrity Monitor function (LIM)

allows the receiver to ensure that reliable data is being

received. Without reliable data reception, the LIM will halt

both transmit and receive operations until such time that a

valid link is detected (i.e. good link).

If Auto-Negotiation is not enabled, then a valid link will be

indicated once SD+/− is asserted continuously for 500 µs.

If Auto-Negotiation is enabled, then Auto-Negotiation will

further qualify a valid link as follows:

— The descrambler must receive a minimum of 12 IDLE

code groups for proper link initialization.

— The Auto-Negotiation must determine that the

100BASE-X function should be enabled.

A valid link for a non-Auto-Negotiating application is indicated by either the Link LED output or by reading bit 2 of

the Basic Mode Status Register BMSR (address 01h). For

a truly qualified valid link indication as a result of AutoNegotiation, bit 2 of the BMSR register (address 01h) must

be read.

2.3.12 Bad SSD Detection

A Bad Start ofStream Delimiter (Bad SSD)is any transition

from consecutive idle code-groups to non-idle code-groups

which is not prefixed by the code-group pair /J/K.

If this condition is detected, the DP83843 will assert

RX_ER and present RXD[3:0] = 1110 to the MII for the

cycles that correspond to received 5B code-groups. In

order to exit this state the PHYTER must receive at least

two IDLE code groups and the PHYTER cannot receive a

single IDLE code group at any time. In addition, the False

Carrier Event Counter (address 14h) will be incremented

by one. Once the PHYTER exits this state, RX_ER and

CRS become de-asserted.

When bit 11 of the LBR register is one (BP_RX), RXD[3:0]

and RX_ER/RXD[4] are not modified.

2.3.13 Carrier Integrity Monitor

The Carrier Integrity Monitor function (CIM) protects the

repeater from transient conditions that would otherwise

cause spurious transmission due to a faulty link. This function is required for repeater applications and is not specified for node applications.

The REPEATER pin (pin63) determines the defaultstate of

bit 5 of the PCS register (Carrier Integrity Monitor Disable,

address 16h) to automatically enable or disable the CIM

function as required for IEEE 802.3 compliant applications.

After power-up/reset, software may enable or disable this

function independent of Repeater or Node mode.

If the CIM determines that the link is unstable, the

DP83843 will not propagate the received data or control

signaling to the MII and will ignore data transmitted via the

MII. The DP83843 will continue to monitor the receive

stream for valid carrier events.

Detection of an unstable link condition will cause bit 4 of

the PCS register (address 16h) to be set to one. This bit is

cleared to zero upon a read operation once a stable link

condition is detected by the CIM. Upon detection of a stable link, the DP83843 will resume normal operations.

The Disconnect Counter (address 13h) increments each

time the CIM determines that the link is unstable.

2.4 10BASE-T TRANSCEIVER MODULE

The 10BASE-T Transceiver Module is IEEE 802.3 compliant. It includes the receiver, transmitter, collision, heartbeat, loopback, jabber, and link integrity functions, as

defined in the standard. An external filter is not required on

the 10BASE-T interface since this is integrated inside the

DP83843. Due to the complexity and scope of the

10BASE-T Transceiver block and various sub-blocks, this

section focuses on the general system level operation.

2.4.1 Operational Modes

The DP83843 has 2 basic 10BASE-T operational modes:

Half Duplex mode

Full Duplex mode

Half Duplex Mode

In Half Duplex mode the DP83843 functions as a standard

IEEE 802.3 10BASE-T transceiver supporting the

CSMA/CD protocol.

Full Duplex Mode