National Semiconductor DAC1020, DAC1021, DAC1022 Technical data

查询AD7521JD供应商

DAC1020/DAC1021/DAC1022

10-Bit Binary Multiplying D/A Converter

DAC1220/DAC1222

12-Bit Binary Multiplying D/A Converter

General Description

The DAC1020 and the DAC1220 are, respectively, 10 and

12-bit binary multiplying digital-to-analog converters. A deposited thin film R-2R resistor ladder divides the reference

current and provides the circuit with excellent temperature

tracking characteristics (0.0002%/

ature coefficient maximum). The circuit uses CMOS current

switches and drive circuitry to achieve low power consumption (30 mW max) and low output leakages (200 nA max).

The digital inputs are compatible with DTL/TTL logic levels

as well as full CMOS logic level swings. This part, combined

with an external amplifier and voltage reference, can be

used as a standard D/A converter; however, it is also very

attractive for multiplying applications (such as digitally controlled gain blocks) since its linearity error is essentially independent of the voltage reference. All inputs are protected

from damage due to static discharge by diode clamps to V

and ground.

This part is available with 10-bit (0.05%), 9-bit (0.10%), and

8-bit (0.20%) non-linearity guaranteed over temperature

C linearity error temper-

§

(note 1 of electrical characteristics). The DAC1020,

DAC1021 and DAC1022 are direct replacements for the 10bit resolution AD7520 and AD7530 and equivalent to the

AD7533 family. The DAC1220 and DAC1222 are direct replacements for the 12-bit resolution AD7521 and AD7531

family.

Features

Y

Linearity specified with zero and full-scale adjust only

Y

Non-linearity guaranteed over temperature

Y

Integrated thin film on CMOS structure

Y

10-bit or 12-bit resolution

Y

Low power dissipation 10 mW@15V typ

Y

Accepts variable or fixed referenceb25VsV

a

Y

4-quadrant multiplying capability

Y

Interfaces directly with DTL, TTL and CMOS

Y

Fast settling timeÐ500 ns typ

Y

Low feedthrough errorÐ(/2 LSB@100 kHz typ

May 1996

s

25V

REF

DAC1020/DAC1021/DAC1022 10-Bit Binary Multiplying D/A Converter

DAC1220/DAC1222 12-Bit Binary Multiplying D/A Converter

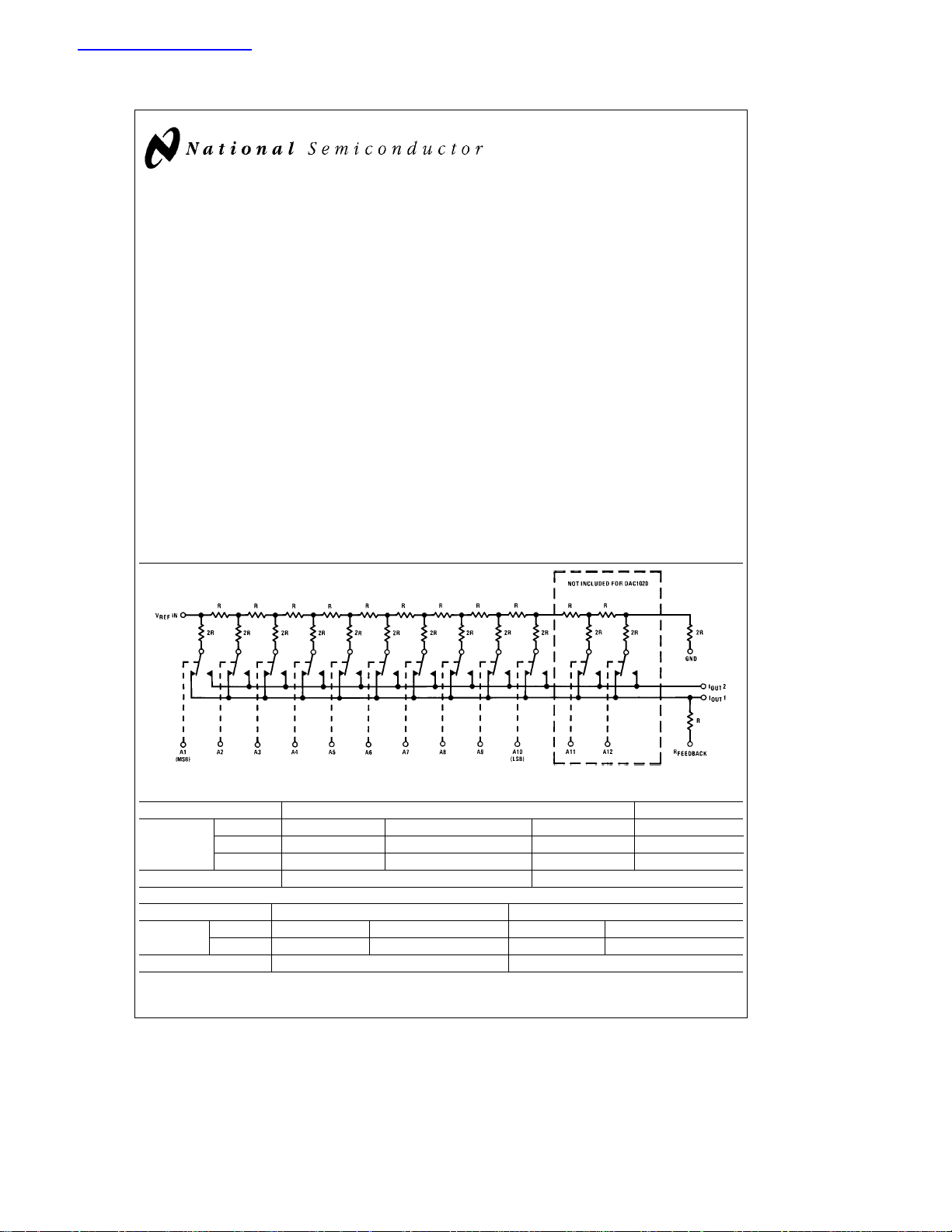

Equivalent Circuit Note. Switches shown in digital high state

Ordering Information

Temperature Range 0§Cto70§C

Non-

Linearity

Package Outline N16A V20A

Temperature Range 0§Cto70§C

Non-

Linearity

Package Outline N18A J18A

Note. Devices may be ordered by either part number.

C

1996 National Semiconductor Corporation RRD-B30M96/Printed in U. S. A.

0.05% DAC1020LCN AD7520LN,AD7530LN DAC1020LCV DAC1020LIV

0.10% DAC1021LCN AD7520KN,AD7530KN

0.20% DAC1022LCN AD7520JN,AD7530JN

0.05% DAC1220LCN AD7521LN,AD7531LN DAC1220LCJ AD7521LD,AD7531LD

0.20% DAC1222LCN AD7521JN,AD7531JN DAC1222LCJ AD7521JD,AD7531JD

TL/H/5689

10-BIT D/A CONVERTERS

12-BIT D/A CONVERTERS

b

40§Ctoa85§C

TL/H/5689– 1

b

40§Cto85§C

http://www.national.com

Absolute Maximum Ratings (Note 5)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales

Office/Distributors for availability and specifications.

a

V

to Gnd 17V

V

to Gnd

REF

Digital Input Voltage Range V

DC Voltage at Pin 1 or Pin 2 (Note 3)

Storage Temperature Range

b

b

65§Ctoa150§C

g

a

to Gnd

100 mV to V

25V

a

Operating Ratings

Temperature (T

DAC1020LIV, DAC1220LCJ,

DAC1222LCJ

DAC1020LCN, DAC1020LCV,

DAC1021LCN 0

DAC1022LCN, DAC1220LCN 0

DAC1222LCN 0

)

A

Min Max Units

b

40a85

a

a

a

§

70

§

70

§

70

§

C

C

C

C

Lead Temperature (Soldering, 10 sec.)

Dual-In-Line Package (plastic) 260

Dual-In-Line Package (ceramic) 300

C

§

C

§

ESD Susceptibility (Note 4) 800V

a

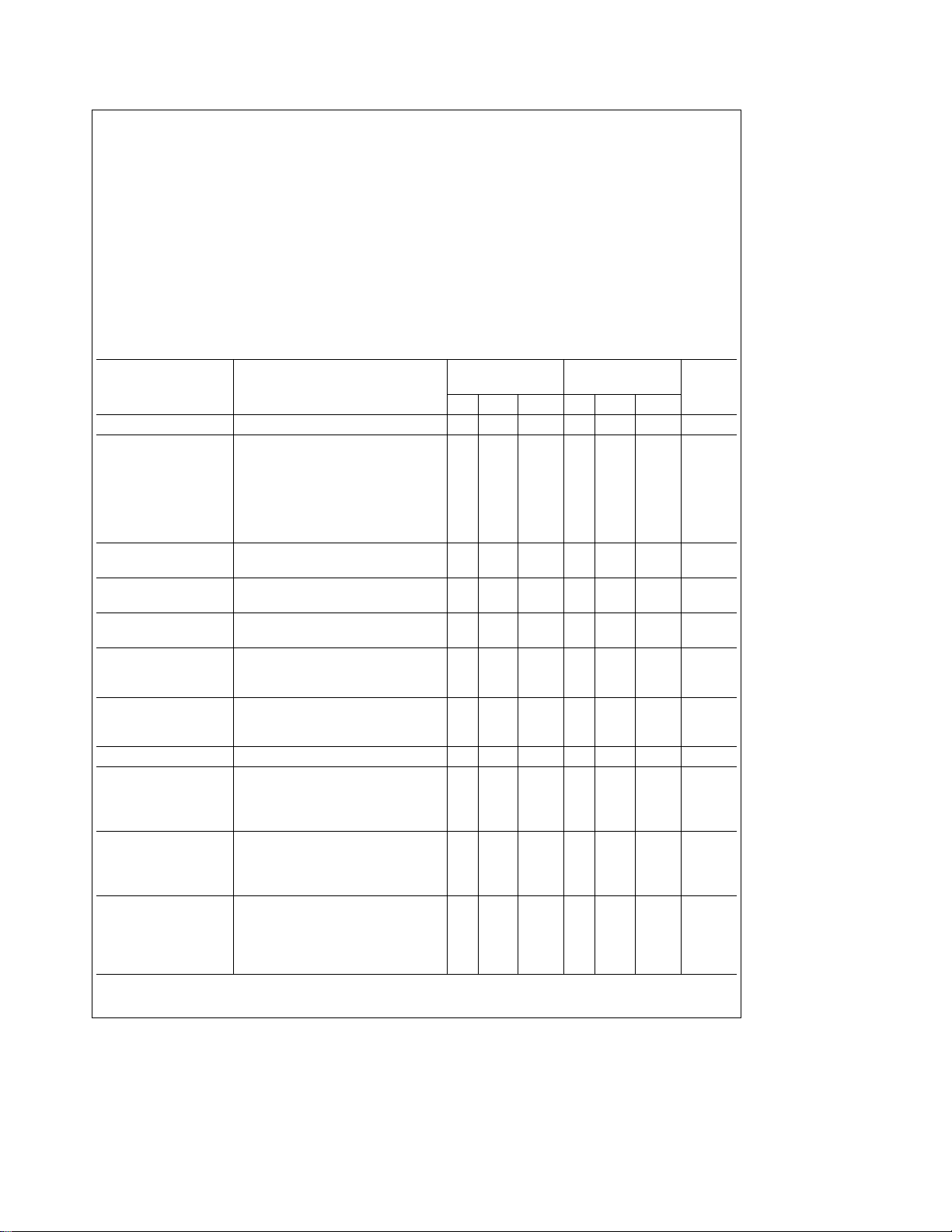

Electrical Characteristics (V

e

15V, V

Parameter Conditions DAC1022 Units

REF

e

10.000V, T

e

25§C unless otherwise specified)

A

DAC1020, DAC1021,

DAC1220, DAC1222

Min Typ Max Min Typ Max

Resolution 10 12 Bits

k

Linearity Error T

k

T

T

MIN

b

10VkV

(Note 1) End Point Adjustment Only

,

A

MAX

k

a

10V,

REF

(See Linearity Error in Definition of Terms)

10-Bit Parts DAC1020, DAC1220 0.05 0.05 % FSR

9-Bit Parts DAC1021 0.10 0.10 % FSR

8-Bit Parts DAC1022, DAC1222 0.20 0.20 % FSR

k

T

A

s

T

A

a

s

a

10V, 0.0002 0.0002 % FS/§C

REF

s

a

10V, 0.3 1.0 0.3 1.0 % FS

REF

k

T

, 0.001 0.001 % FS/§C

MAX

s

T

MAX

s

16V, (Note 2),

Linearity Error Tempco

b

10VsV

(Notes 1 and 2)

Full-Scale Error

b

10VsV

(Notes 1 and 2)

Full-Scale Error Tempco T

Output Leakage Current T

I

OUT 1

I

OUT 2

MIN

(Note 2)

MIN

All Digital Inputs Low 200 200 nA

All Digital Inputs High 200 200 nA

Power Supply Sensitivity All Digital Inputs High, 0.005 0.005 % FS/V

14VsV

(Figure 2)

V

Input Resistance 10 15 20 10 15 20 kX

REF

Full-Scale Current Settling R

Time FS

e

100X from 0 to 99. 95%

L

All Digital Inputs Switched 500 500 ns

Simultaneously

V

Feedthrough All Digital Inputs Low, 10 10 mVp-p

REF

e

V

20 Vp-p@100 kHz

REF

J Package (Note 4) 6 9 6 9 mVp-p

N Package 2 5 2 5 mVp-p

Output Capacitance

I

OUT 1

I

OUT 2

All Digital Inputs Low 40 40 pF

All Digital Inputs High 200 200 pF

All Digital Inputs Low 200 200 pF

All Digital Inputs High 40 40 pF

http://www.national.com 2

a

Electrical Characteristics (V

e

15V, V

Parameter Conditions DAC1022 Units

e

10.000V, T

REF

DAC1020, DAC1021,

e

25§C unless otherwise specified) (Continued)

A

DAC1220, DAC1222

Min Typ Max Min Typ Max

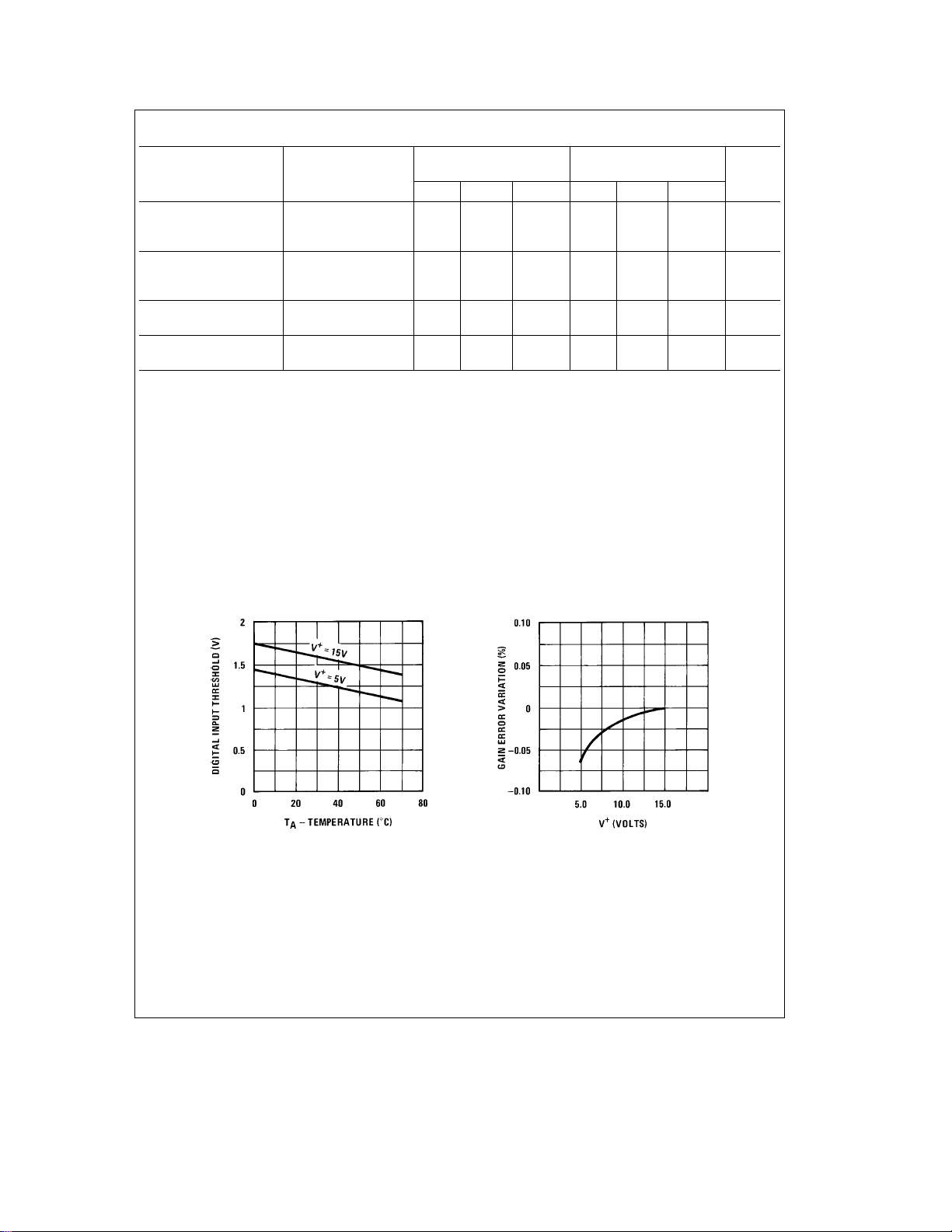

Digital Input

Low Threshold T

High Threshold T

Digital Input Current T

(Figure 1)

k

k

T

MIN

MIN

MIN

Digital Input High 1 100 1 100 mA

Digital Input Low

T

A

MAX

k

k

T

T

A

MAX

s

s

T

T

A

MAX

2.4 2.4 V

b

50

0.8 0.8 V

b

200

b

b

50

200 mA

Supply Current All Digital Inputs High 0.2 1.6 0.2 1.6 mA

All Digital Inputs Low 0.6 2 0.6 2 mA

Operating Power Supply

(Figures 1 and 2)

5 15 5 15 V

Range

e

Note 1: V

linearity error. For instance, if the linearity error at 25

however, that the linearity error is specified over the device full temperature range which is a more stringent specification since

temperature coefficient.

Note 2: Using internal feedback resistor as shown in

Note 3: Both I

0.005% linearity error will be introduced.

Note 4: Human body model, 100 pF discharged through a 1.5 kX resistor.

Note 5: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating

the device beyond its specified operating conditions.

Note 6: The maximum power dissipation must be derated at elevated temperatures and is dictated by T

allowable power dissipation at any temperature is P

device, T

120

§

g

10V and V

REF

and I

OUT 1

e

125§C, and the typical junction-to-ambient thermal resistance of the J18 package when board mounted is 85§C/W. For the N18 package, iJAis

JMAX

C/W, for the N16 this number is 125§C/W, and for the V20 this number is 95§C/W.

e

g

1V. A linearity error temperature coefficient of 0.0002% FS for a 45§C rise only guarantees 0.009% maximum change in

REF

must go to ground or the virtual ground of an operational amplifier. If V

OUT 2

C is 0.045% FS it could increase to 0.054% at 70§C and the DAC will be no longer a 10-bit part. Note,

§

Figure 3

e

D

.

b

(T

TA)/iJAor the number given in the Absolute Maximum Ratings, whichever is lower. For this

JMAX

e

10V, every millivolt offset between I

REF

, iJA, and the ambient temepature, TA. The maximum

JMAX

it includes

the linearity error

or I

OUT 1

OUT 2

,

Typical Performance Characteristics

FIGURE 1. Digital Input Threshold vs

Ambient Temperature

FIGURE 2. Gain Error Variation vs V

http://www.national.com3

a

TL/H/5689– 2

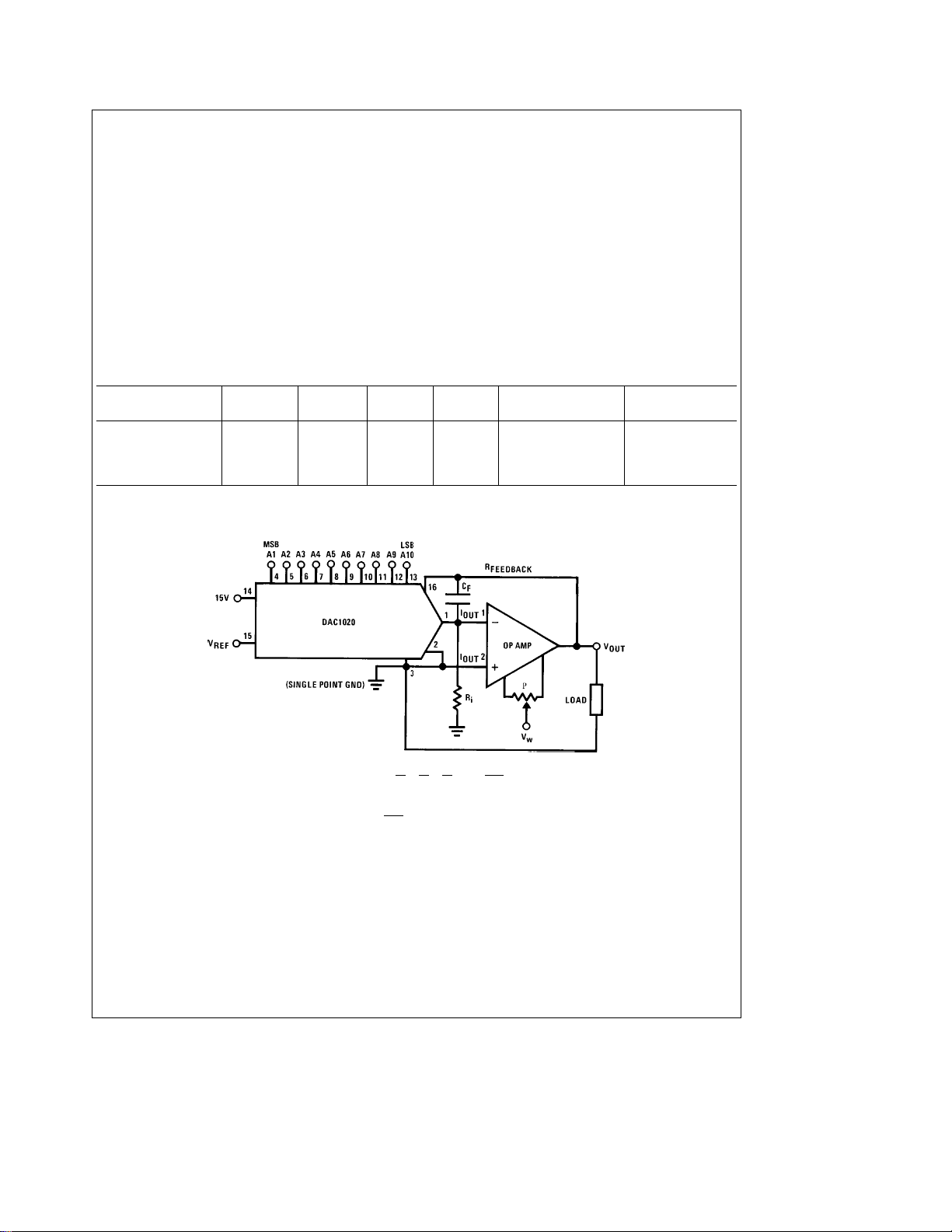

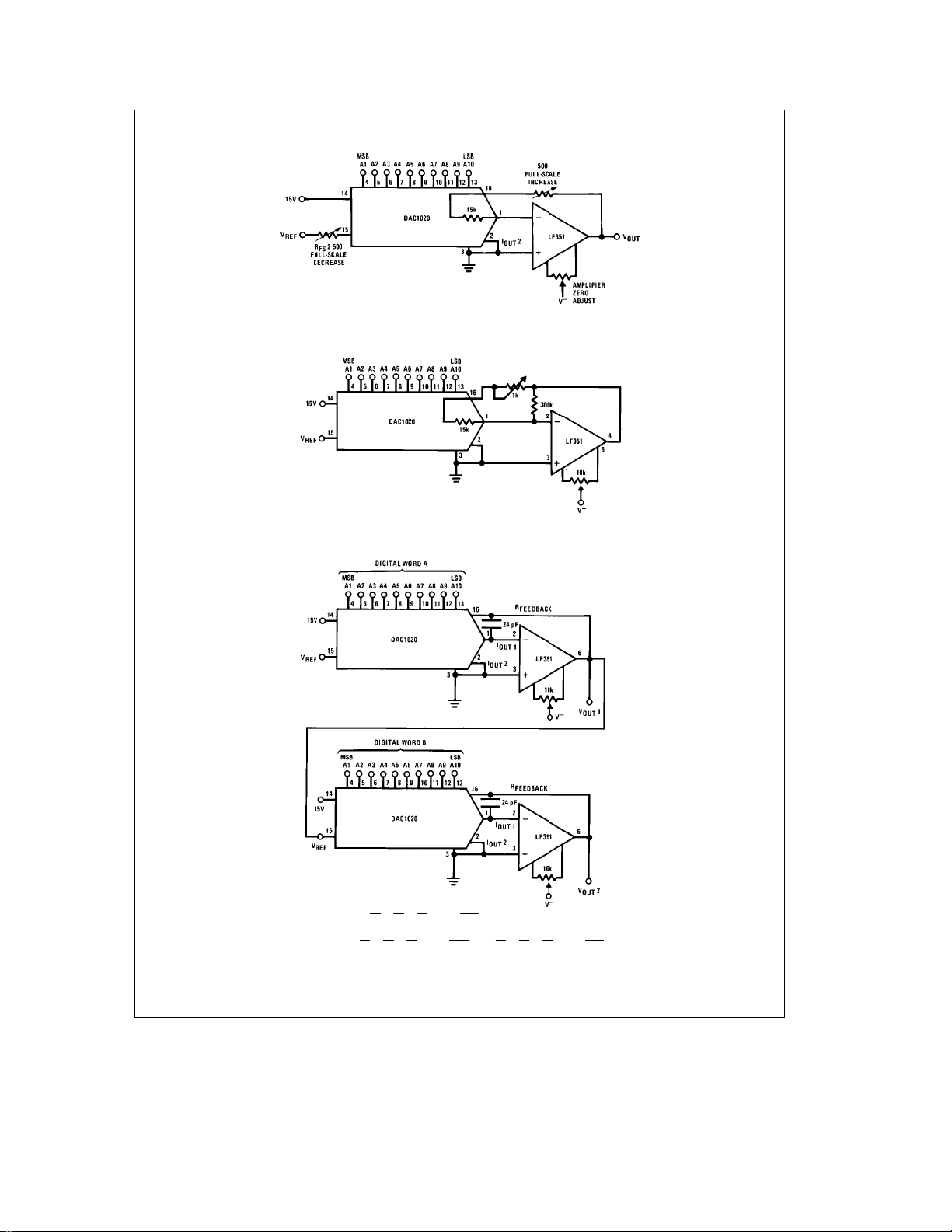

Typical Applications

The following applications are also valid for 12-bit systems

using the DAC1220 and 2 additional digital inputs.

Operational Amplifier Bias Current (

The op amp bias current, Ib, flows through the 15k internal

feedback resistor. BI-FET op amps have low I

fore, the 15k

c

Iberror they introduce is negligible; they are

strongly recommended for the DAC1020 applications.

V

Considerations

OS

The output impedance, R

the digital input code which causes a modulation of the op-

OUT

erational amplifier output offset. It is therefore recommended to adjust the op amp V

digital inputs are high; R

is high, and R

OUT

OS.ROUT

OUT

approaches infinity if all inputs are low.

SELECTING AND COMPENSATING THE OPERATIONAL AMPLIFIER

Op Amp Family C

LF357 10 pF 2.4k 25k V

LF356 22 pF

LF351 24 pF

LM741 0

Figure 3

)

and, there-

b

, of the DAC is modulated by

isE15k if more than 4

isE45k if a single digital input

F

R

i

%

%

%

Operational Amplifier V

OS

Adjust (

Figure 3

Connect all digital inputs, A1 –A10, to ground and adjust the

potentiometer to bring the op amp V

mV from ground potential. If V

V

adjustment is required. It is helpful to increase the reso-

OS

lution of the V

resistor between the inverting input of the op amp to

ground. After V

Full-Scale Adjust (

adjust procedure by connectinga1kX

OS

has been adjusted, remove the 1 kX.

OS

Figure 4

)

OUT

is less than 10V, a finer

REF

Switch high all the digital inputs, A1 –A10, and measure the

op amp output voltage. Use a 500X potentiometer, as

shown, to bring

1023/1024.

PV

25k V

10k V

10k V

W

a

a

b

b

V

to a voltage equal to V

ll

ll

OUT

Circuit Settling Circuit Small

Time, t

s

1.5 ms1M

3 ms 0.5M

4 ms 0.5M

40 ms 200 kHz

)

pin to withing1

REF

Signal BW

c

V

OUT

b

10VsV

s

0

V

where A

eb

OUT

A1

V

REF

2

#

s

10V

REF

1023

s

b

V

1024

e

1 if the ANdigital input is high

N

e

A

0 if the ANdigital input is low

N

FIGURE 3. Basic Connection: Unipolar or 2-Quadrant Multiplying

Configuration (Digital Attenuator)

http://www.national.com 4

A2

A3

a

a

4

REF

A10

a

###

8

1024

J

TL/H/5689– 3

Typical Applications (Continued)

FIGURE 5. Alternate Full-Scale Adjust: (Allows Increasing or Decreasing the Gain)

FIGURE 4. Full-Scale Adjust

A1

A2

A3

V

OUT 1

V

OUT2

where V

eb

V

REF

#

A1

e

V

REF

2

#

can be an AC signal

REF

a

a

2

4

A2

A3

a

a

4

8

A10

a

###

8

1024

A10

a

###

1024

Jc#

FIGURE 6. Precision Analog-to-Digital Multiplier

J

B1

B2

B3

a

a

2

4

B10

a

###

8

1024

J

TL/H/5689– 4

http://www.national.com5

Loading...

Loading...