CR16HCS5/CR16HCS9/CR16MAR5/CR16MAS5

CR16MAS9/CR16MBR5/CR16MCS5/CR16MCS9

Family of 16-bit CAN-enabled CompactRISC

Microcontrollers

1.0 General Description

The family of 16-bit CompactRISC™ microcontroller is

based on a Reduced Instruction Set Computer (RISC) architecture. The device operates as a complete microcomputer with all system timing, interrupt logic, flash program

memory or ROM memory, RAM, EEPROM data memory,

and I/O ports included on-chip. It is ideally suited to a wide

range of embedded controller applications because of its

high performance, on-chip integrated features and low

power consumption resulting in decreased system cost.

The device offers the high performance of a RISC architecture while retaining the advantages of a traditional Com-

plex Instruction Set Computer (CISC): compact code, onchip memory and I/O, and reduced cost. The CPU uses a

three-stage instruction pipeline that allows execution of up

to one instruction per clock cycle, or up to 25 million instructions per second (MIPS) at a clock rate of 24 MHz.

The device contains a FullCAN class, CAN serial interface

for low/high speed applications with 15 orthogonal message buffers, each supporting standard as well as extended message identifiers.

January 2002

CR16HCS5/CR16HCS9/CR16MAR5/CR16MAS5 CR16MAS9/CR16MBR5/CR16MCS5/CR16MCS9 Family of 16-bit CAN-en-

abled CompactRISC Microcontrollers

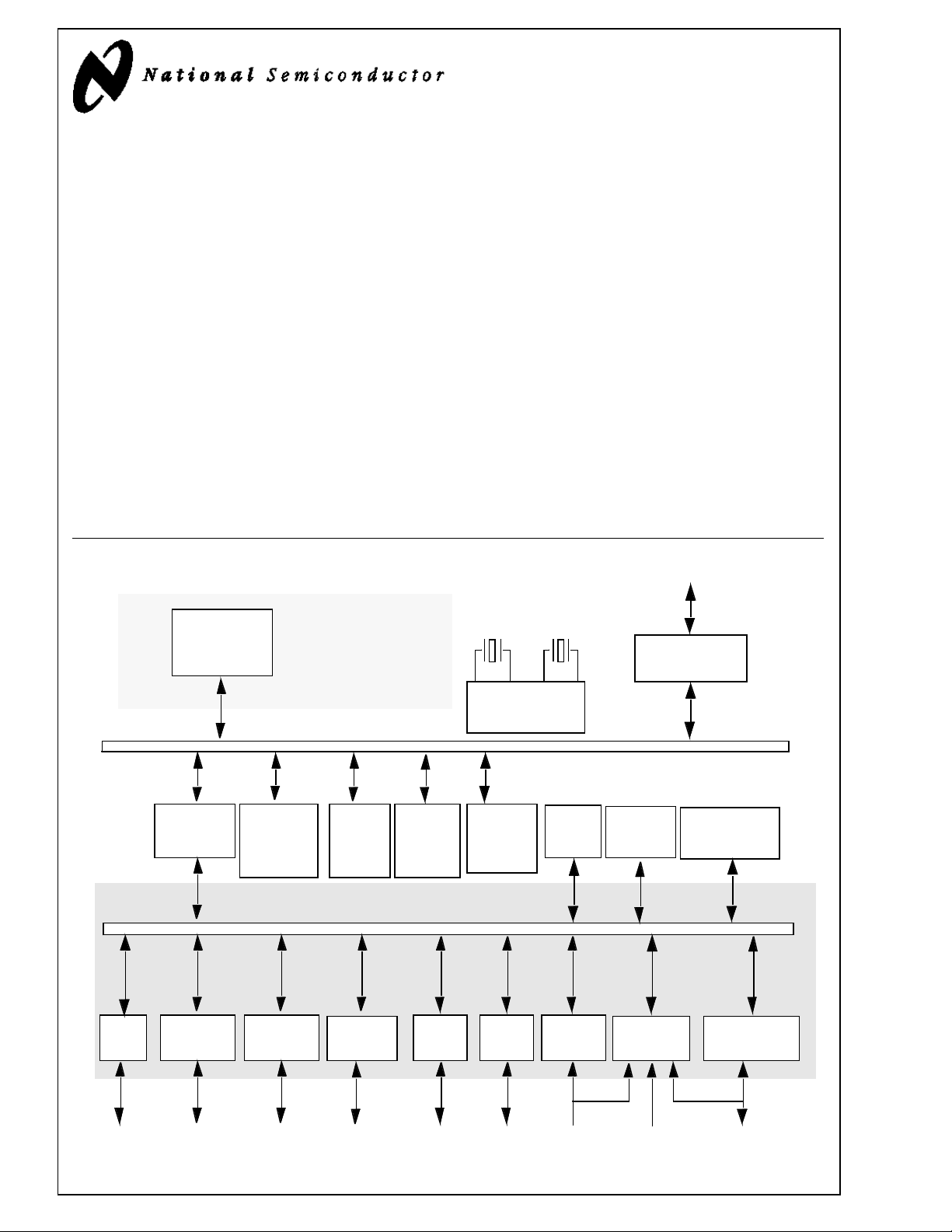

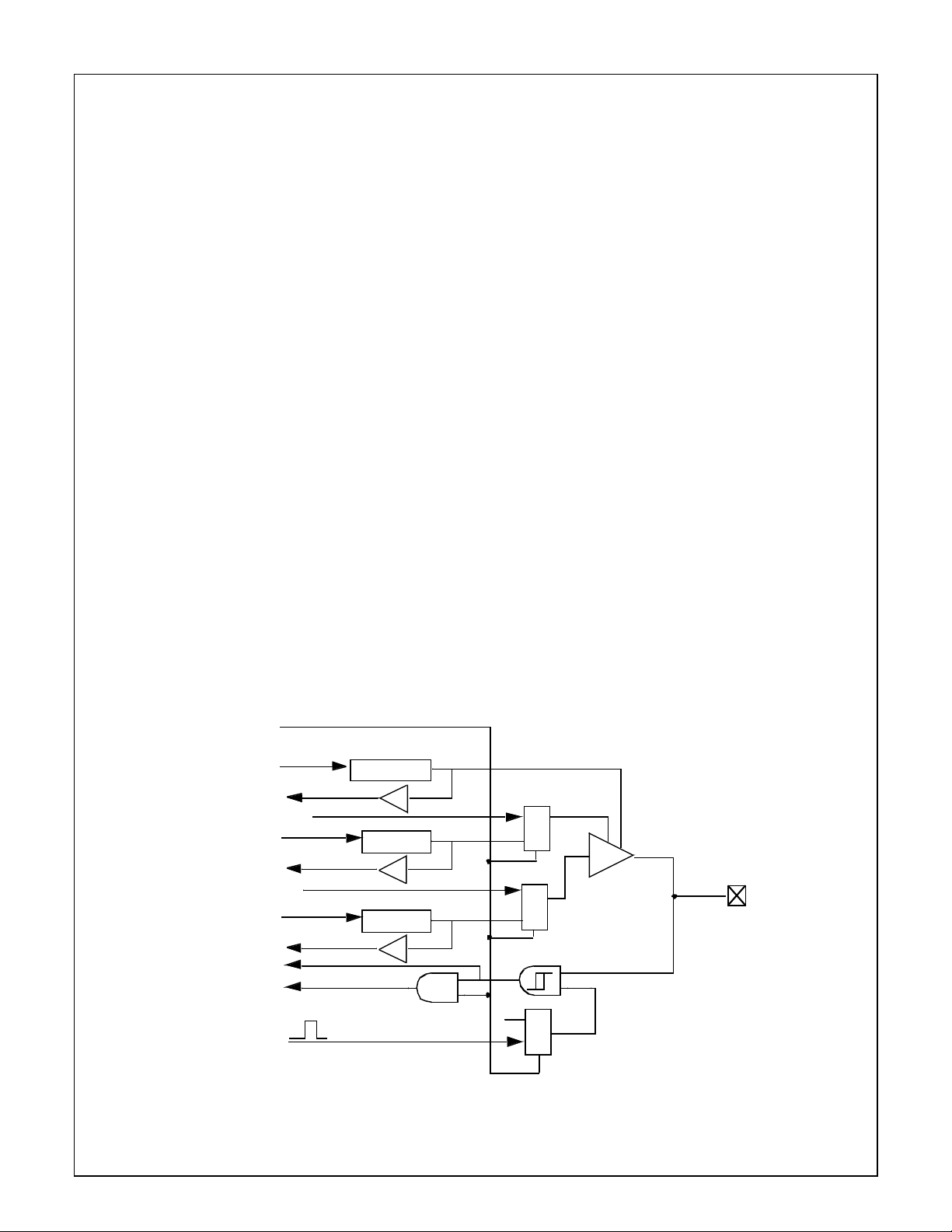

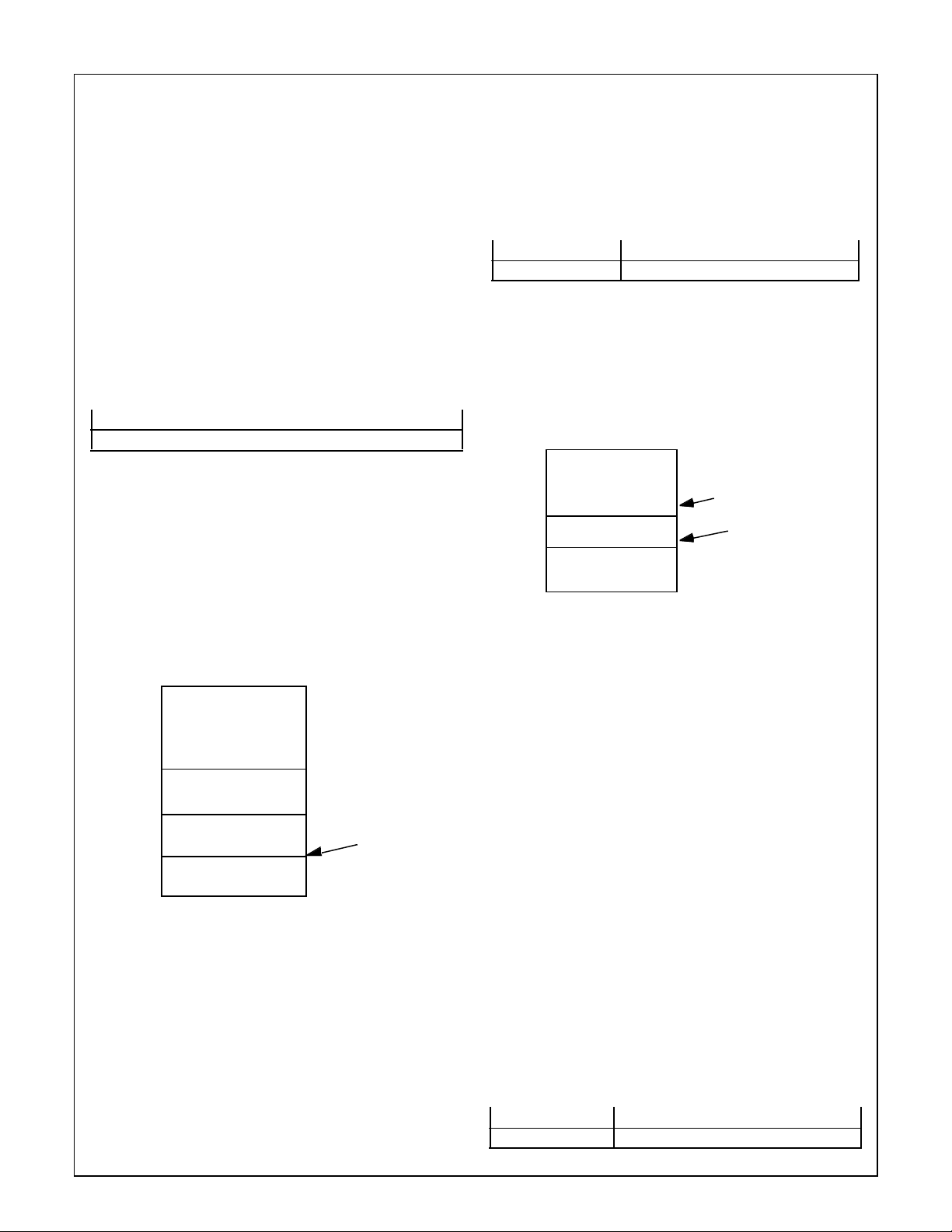

Block Diagram

CR16B

RISC Core

Peripheral

Bus

Controller

64k-Byte

Flash

Program

Memory

Processing

Unit

Core Bus

3k-Byte

RAM

2176-Byte

EEPROM

Data

Memory

Peripheral Bus

Fast Clk

Clock Generator

Power-on-Reset

1.5k-Byte

ISP

Memory

Slow Clk*

Interrupt

Control

CR16CAN

FullCAN 2.0B

Power

Manage-

ment

Timing and

Watchdog

I/O

Please note that not all family members contain same peripheral modules and features.

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

µWire/SPI

2x

USART

ACCESS

bus

4x

VTU

2x

MFT

12-ch

8-bit A/D

MIWU

2 Analog

Comparators

Table of Contents

1.0 General Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2.0 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

3.0 Device Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.1 CR16B CPU Core . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.2 Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

3.3 Input/Output Ports . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.4 Bus Interface Unit . . . . . . . . . . . . . . . . . . . . . . . . . .5

3.5 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.6 Multi-Input Wake-up . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.7 Dual Clock and Reset . . . . . . . . . . . . . . . . . . . . . . .6

3.8 Power Management . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.9 Multi-Function Timer . . . . . . . . . . . . . . . . . . . . . . . .6

3.10 Versatile timer unit. . . . . . . . . . . . . . . . . . . . . . . . . .6

3.11 Real-Time TIMER and Watchdog . . . . . . . . . . . . . . 6

3.12 USART. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.13 MICROWIRE/SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.14 CR16CAN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.15 ACCESS.bus Interface . . . . . . . . . . . . . . . . . . . . . .7

3.16 A/D Converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.17 Analog Comparators . . . . . . . . . . . . . . . . . . . . . . . .7

3.18 Development Support . . . . . . . . . . . . . . . . . . . . . . .7

4.0 Device Pinouts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

4.1 Pin Description. . . . . . . . . . . . . . . . . . . . . . . . . . . .10

5.0 System Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

5.1 ENV0 and ENV1 Pins . . . . . . . . . . . . . . . . . . . . . . 12

5.2 Module Configuration (MCFG) Register . . . . . . . .12

5.3 Module Status (MSTAT) Register . . . . . . . . . . . . . 12

6.0 Input/Output Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

6.1 Port Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

6.2 Open-Drain Operation . . . . . . . . . . . . . . . . . . . . . .14

7.0 CPU and Core Registers . . . . . . . . . . . . . . . . . . . . . . . . . 15

7.1 General-Purpose Registers. . . . . . . . . . . . . . . . . . 15

7.2 Dedicated Address Registers . . . . . . . . . . . . . . . .15

7.3 Processor Status Register. . . . . . . . . . . . . . . . . . . 15

7.4 Configuration Register. . . . . . . . . . . . . . . . . . . . . .16

7.5 Addressing Modes. . . . . . . . . . . . . . . . . . . . . . . . .16

7.6 Stacks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

7.7 Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

8.0 Bus Interface Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

8.1 Bus Cycles. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

8.2 BIU Control Registers . . . . . . . . . . . . . . . . . . . . . .18

8.3 Wait and Hold States Used . . . . . . . . . . . . . . . . . .20

9.0 Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

9.1 Flash EEPROM Program Memory. . . . . . . . . . . . .22

9.2 RAM Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

9.3 Flash EEPROM Data Memory. . . . . . . . . . . . . . . .25

9.4 ISP Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

10.0 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

10.1 Interrupt Operation . . . . . . . . . . . . . . . . . . . . . . . . . 31

10.2 Non-Maskable Interrupt . . . . . . . . . . . . . . . . . . . . .32

10.3 Maskable Interrupts . . . . . . . . . . . . . . . . . . . . . . . .32

10.4 Interrupt Registers . . . . . . . . . . . . . . . . . . . . . . . . .33

10.5 Interrupt Programming Procedures . . . . . . . . . . . .35

11.0 Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

11.1 Active Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

11.2 Power Save Mode . . . . . . . . . . . . . . . . . . . . . . . . .36

11.3 Idle Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

11.4 Halt Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

11.5 Clock Inputs and Reset Configuration . . . . . . . . . .36

11.6 Switching Between Power Modes . . . . . . . . . . . . .36

12.0 Dual Clock and Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

12.1 External Crystal Network. . . . . . . . . . . . . . . . . . . . 39

12.2 Main System Clock . . . . . . . . . . . . . . . . . . . . . . . . 40

12.3 Slow System Clock . . . . . . . . . . . . . . . . . . . . . . . . 40

12.4 Power-On Reset . . . . . . . . . . . . . . . . . . . . . . . . . .41

12.5 External Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . .41

12.6 Dual Clock and Reset Registers . . . . . . . . . . . . . .41

12.7 Slow Clock Prescaler Register (PRSSC). . . . . . . .41

12.8 Slow Clock Prescaler 1 Register (PRSSC1) . . . . .41

13.0 Multi-Input Wake-Up . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

13.1 Wake-Up Edge Detection Register (WKEDG) . . . .42

13.2 Wake-Up Enable Register (WKENA). . . . . . . . . . .42

13.3 Wake-Up Interrupt Control Register 1 (WKCTRL1) 43

13.4 Wake-Up Interrupt Control Register 1 (WKCTRL2) 43

13.5 Wake-Up Pending Register (WKPND) . . . . . . . . . .43

13.6 Wake-Up Pending Clear Register (WKPCL) . . . . .43

13.7 Programming Procedures . . . . . . . . . . . . . . . . . . .44

14.0 Real-Time Timer and WATCHDOG . . . . . . . . . . . . . . . . .45

14.1 TWM Structure. . . . . . . . . . . . . . . . . . . . . . . . . . . .45

14.2 Timer T0 Operation . . . . . . . . . . . . . . . . . . . . . . . .45

14.3 WATCHDOG Operation . . . . . . . . . . . . . . . . . . . . .46

14.4 TWM Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

14.5 WATCHDOG Programming Procedure . . . . . . . . .47

15.0 Multi-Function Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

15.1 Timer Structure. . . . . . . . . . . . . . . . . . . . . . . . . . . .49

15.2 Timer Operating Modes . . . . . . . . . . . . . . . . . . . . .51

15.3 Timer Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . .54

15.4 Timer I/O Functions . . . . . . . . . . . . . . . . . . . . . . . .54

15.5 Timer Registers . . . . . . . . . . . . . . . . . . . . . . . . . . .56

16.0 Versatile-Timer-Unit (VTU) . . . . . . . . . . . . . . . . . . . . . . .58

16.1 VTU Functional Description . . . . . . . . . . . . . . . . . .58

16.2 VTU Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

17.0 MICROWIRE/SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

17.1 MICROWIRE Operation . . . . . . . . . . . . . . . . . . . . .65

17.2 Master Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

17.3 Slave Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

17.4 Interrupt Generation. . . . . . . . . . . . . . . . . . . . . . . .68

17.5 MICROWIRE Interface Registers. . . . . . . . . . . . . .68

18.0 USART . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

18.1 Functional Overview . . . . . . . . . . . . . . . . . . . . . . . .71

18.2 USART Operation . . . . . . . . . . . . . . . . . . . . . . . . .71

18.3 USART Registers . . . . . . . . . . . . . . . . . . . . . . . . . .75

18.4 Baud Rate Calculations . . . . . . . . . . . . . . . . . . . . .77

19.0 ACCESS.bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . .78

19.1 ACB Protocol Overview . . . . . . . . . . . . . . . . . . . . .78

19.2 ACB Functional Description . . . . . . . . . . . . . . . . . .79

19.3 ACB Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . .82

19.4 Usage Hints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .84

20.0 CR16CAN Module. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .85

20.1 Functional Description . . . . . . . . . . . . . . . . . . . . . .85

20.2 Basic CAN Concepts . . . . . . . . . . . . . . . . . . . . . . .87

20.3 Message Transfer . . . . . . . . . . . . . . . . . . . . . . . . .95

20.4 Acceptance Filtering . . . . . . . . . . . . . . . . . . . . . . . .96

20.5 Receive Structure . . . . . . . . . . . . . . . . . . . . . . . . . .97

20.6 Transmit Structure . . . . . . . . . . . . . . . . . . . . . . . . 100

20.7 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

20.8 Time Stamp Counter . . . . . . . . . . . . . . . . . . . . . . 105

20.9 Memory Organization. . . . . . . . . . . . . . . . . . . . . .105

20.10 System Start-Up and Multi-Input Wake-Up . . . . .116

21.0 Analog Comparators . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

21.1 Analog Comparator Control/Status Register

(CMPCTRL). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

21.2 Analog Comparator Usage . . . . . . . . . . . . . . . . . .118

22.0 A/D Converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .119

22.1 Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . 119

22.2 A/D Converter Registers . . . . . . . . . . . . . . . . . . .120

22.3 A/D Converter Programming . . . . . . . . . . . . . . . .122

23.0 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123

24.0 Register Layouts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .129

24.1 Register layout . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

25.0 ELECTRICAL AND THERMAL CHARACTERISTICS . . 136

26.0 Appendix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .152

26.1 CR16CAN. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

26.2 8/16-bit microwire/spi (MWSPI16) . . . . . . . . . . . .154

26.3 Timing and watchdog module . . . . . . . . . . . . . . . 154

www.national.com 2

1.0 General Description (Continued)

The device has up to 64K bytes of reprogrammable flash EEPROM program memory or ROM memory, 1.5K bytes of

flash EEPROM In-System-Programming memory, 3K bytes

of static RAM, 2K bytes of non-volatile EEPROM data memory and 128 bytes with high endurance, two USARTs, two 16bit multi-function timers, one SPI/MICROWIRE-PLUS™ serial interface, a 12-channel A/D converter, two analog comparators, WATCHDOG™ protection mechanism, and up to 56

general-purpose I/O pins.

The device operates with a high-frequency crystal as the

main clock source and either the prescaled main clock

source or with a low frequency (32.768 kHz) oscillator in

Power Save mode. The device supports several Power Save

modes which are combined with multi-source interrupt and

wake-up capabilities.

This device also has a Versatile Timer Unit (VTU) with four

timer sub-systems, a CAN interface, and ACCESS.bus synchronous serial bus interface.

Powerful cross-development tools are available from National Semiconductor and third party suppliers to support the development and debugging of application software for the

device. These tools let you program the application software

in C and are designed to take full advantage of the CompactRISC architecture.

In the following text, device is always referred to the family of

16-bit CAN-enabled CompactRISC Microtroller.

— FullCAN interface with 15 message buffers complaint

to CAN specification 2.0B active

— Versatile Timer Unit with four subsystems (VTU)

— Two analog comparators

— Integrated WATCHDOG logic

• I/O Features

— Up to 56 general-purpose I/O pins (shared with on-chip

peripheral I/O pins)

— Programmable I/O pin characteristics: TRI-STATE out-

put, push-pull output, weak pull-up input, high-impedance input

— Schmitt triggers on general purpose inputs

• Power Supply

— 4.5V to 5.5V single-supply operation

• Temperature Range

— –40°C to +85°C

— –40°C to +125°C

• Development Support

— Real-time emulation and full program debug capabili-

ties available

— CompactRISC tools provide C programming and de-

bugging support

2.0 Features

• CPU Features

— Fully static core, capable of operating at any rate from

0 to 24 MHz (4 MHz minimum in active mode)

— 50 ns instruction cycle time with a 20 MHz external

clock frequency

— Multi-source vectored interrupts (internal, external,

and on-chip peripheral)

— Dual clock and reset

• On-chip power-on reset

• On-Chip Memory

— Up to 64K bytes flash EEPROM program memory; can

be programmed, erased, and reprogrammed by soft-

ware (100K cycles)

— 3K bytes of static RAM data memory

— For flash program memory devices, 1.5k bytes flash

EEPROM memory is available to store boot loader

code (100K cycles)

— 2K bytes of non-volatile EEPROM data memory with

low endurance (25K cycles) and 128 bytes with high

endurance (100K cycles)

• On-Chip Peripherals

— Two Universal Synchronous/Asynchronous Receiver/

Transmitter (USART) devices

— Programmable Idle Timer and real-time clock (T0)

— Two dual 16-bit multi-function timers (MFT1 and MFT2)

— 8/16-bit SPI/MICROWIRE-PLUS serial interface

— 12-channel, 8-bit Analog-to-Digital (A/D) converter

with external voltage reference, programmable sam-

ple-and-hold delay, and programmable conversion fre-

quency

— ACCESS.bus synchronous serial bus

3 www.national.com

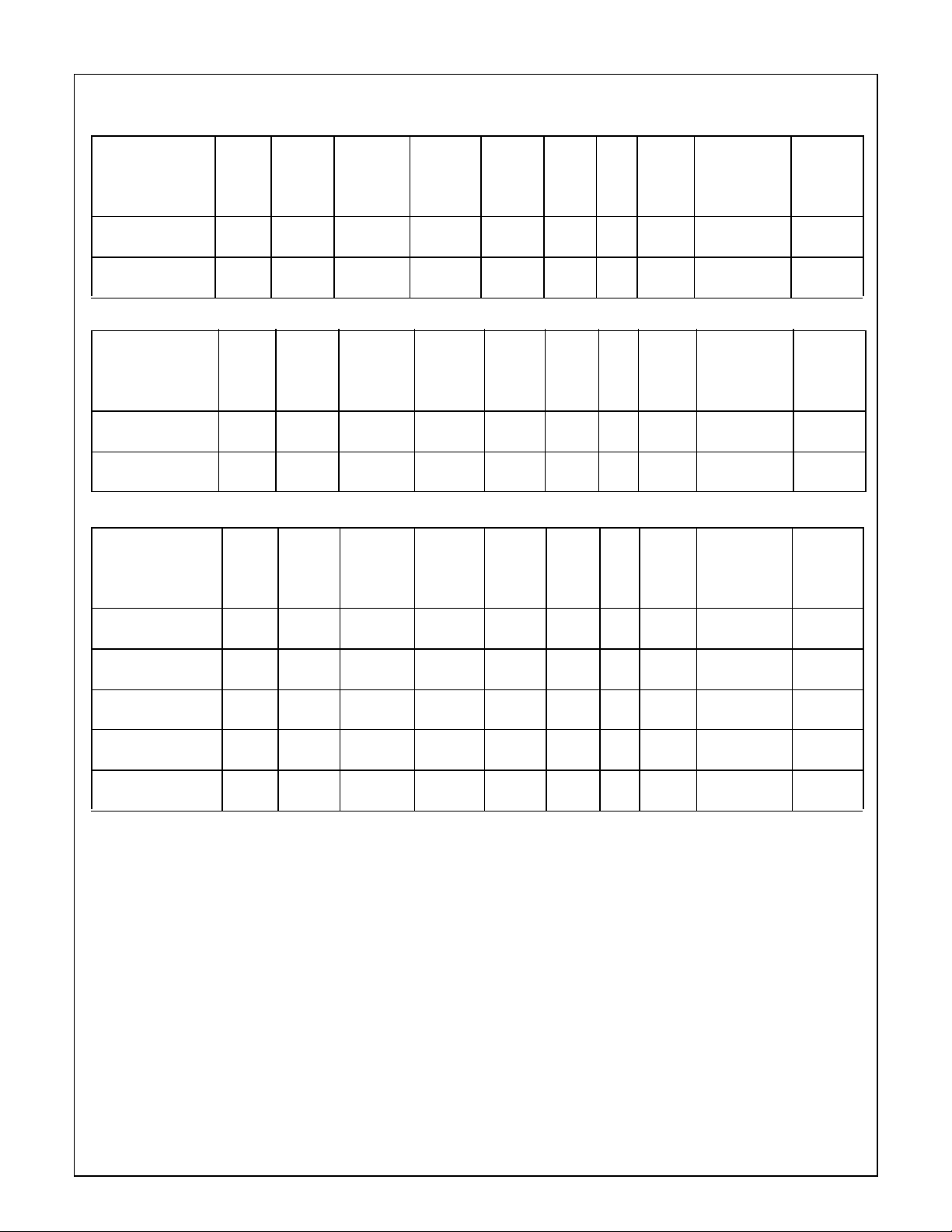

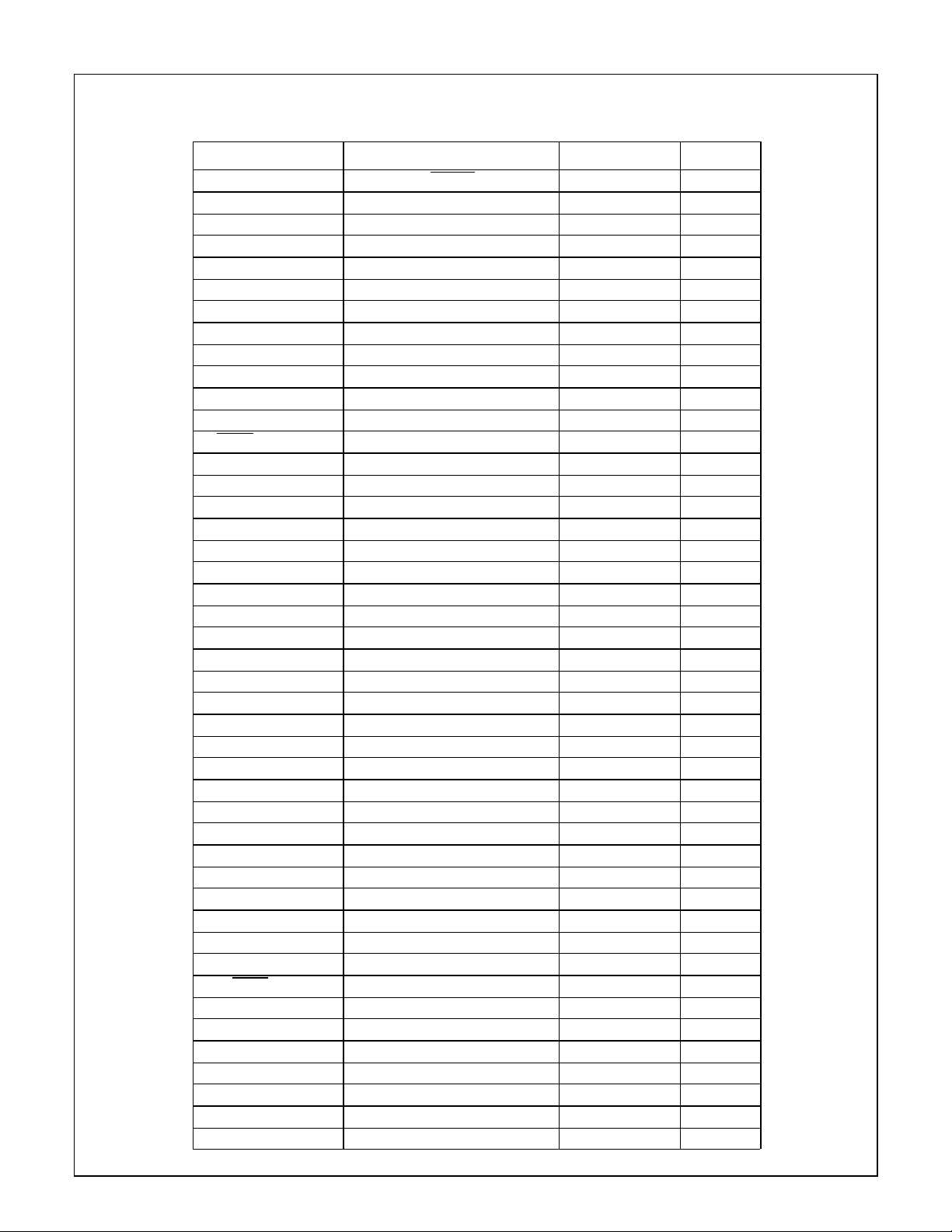

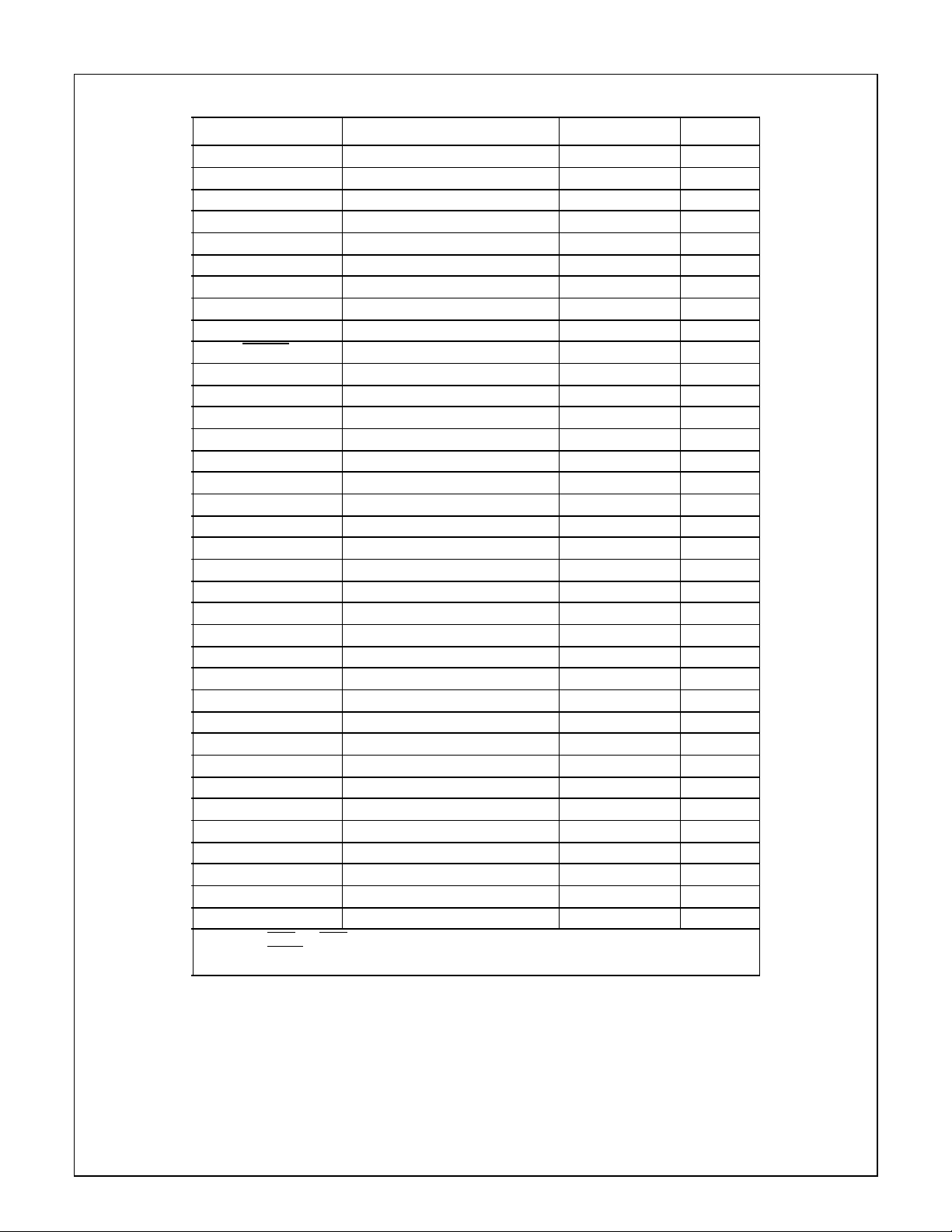

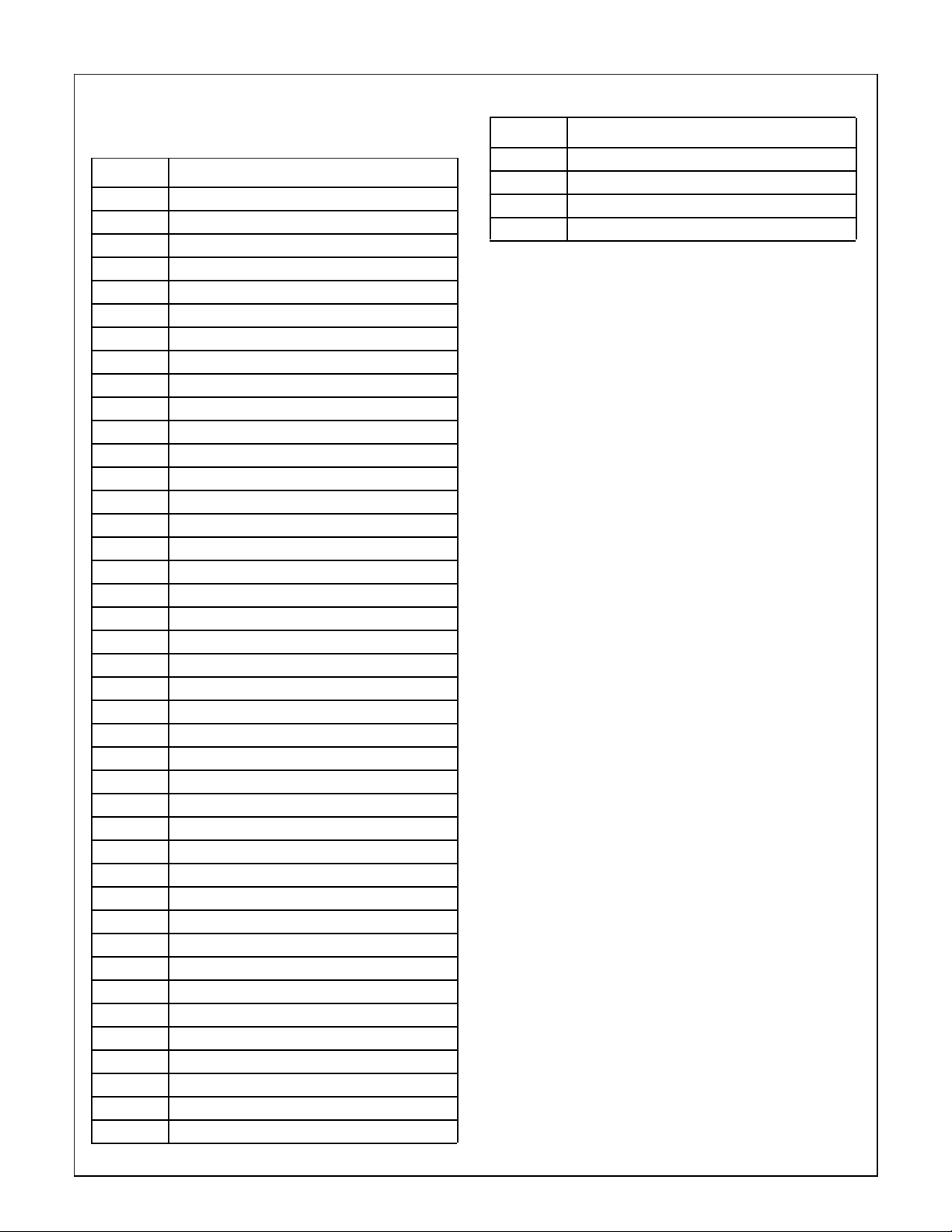

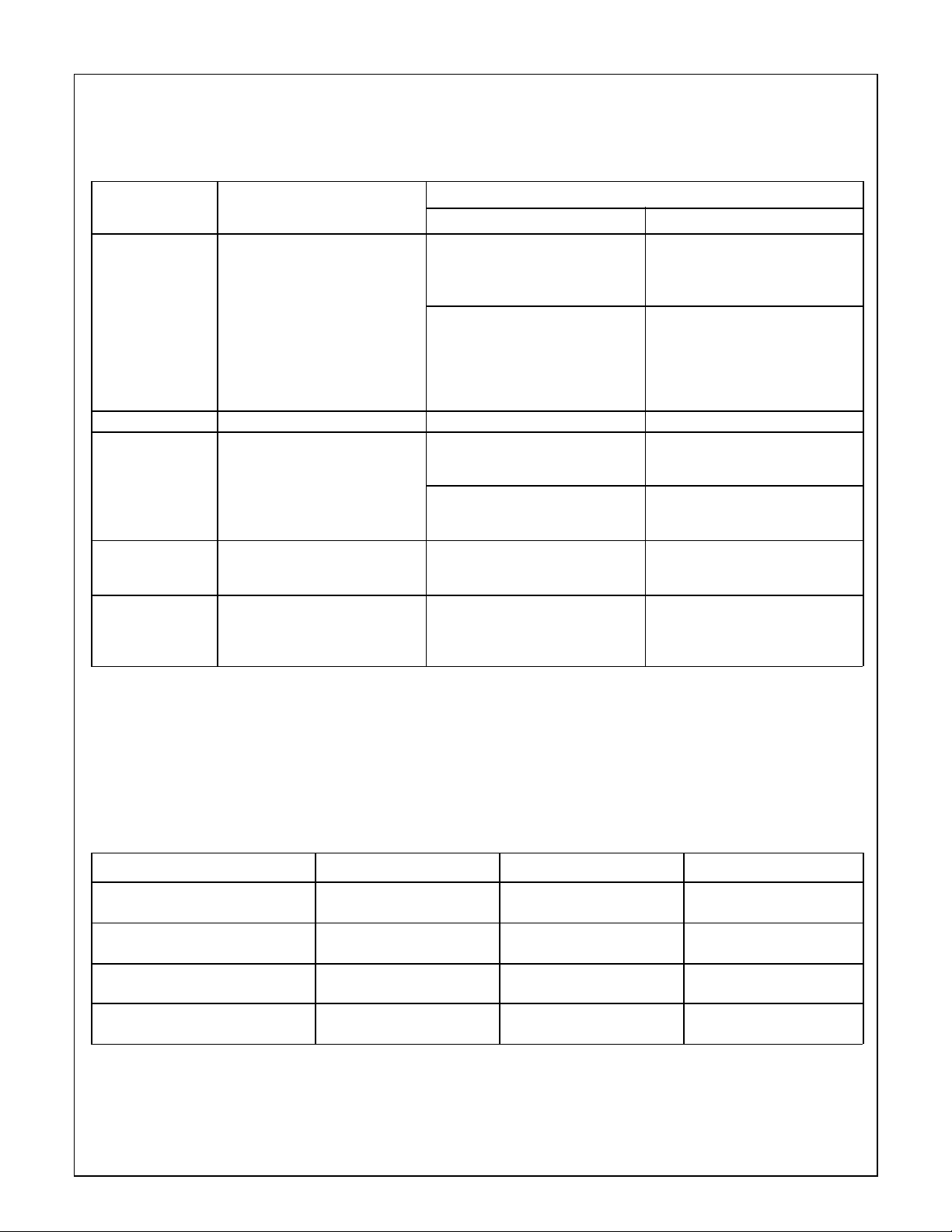

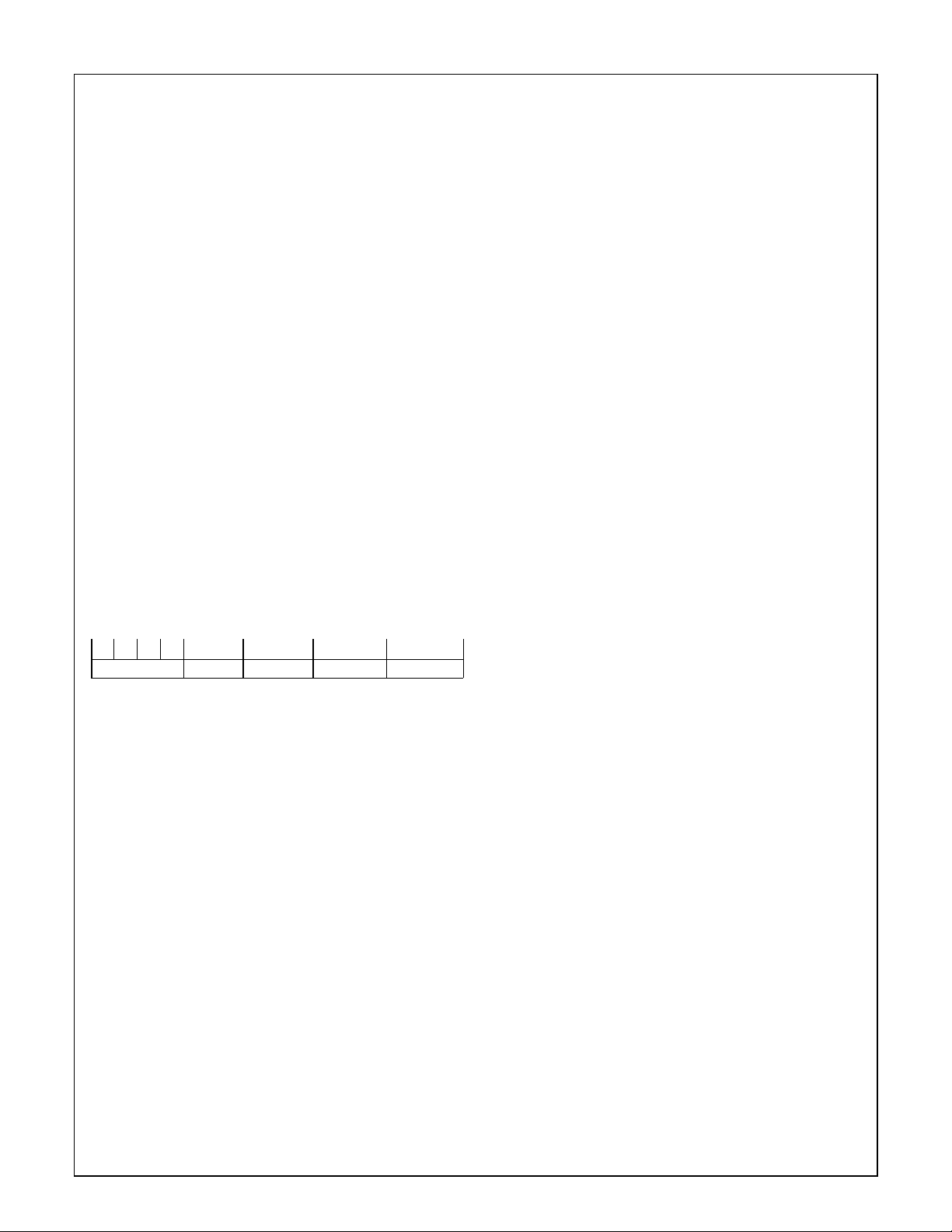

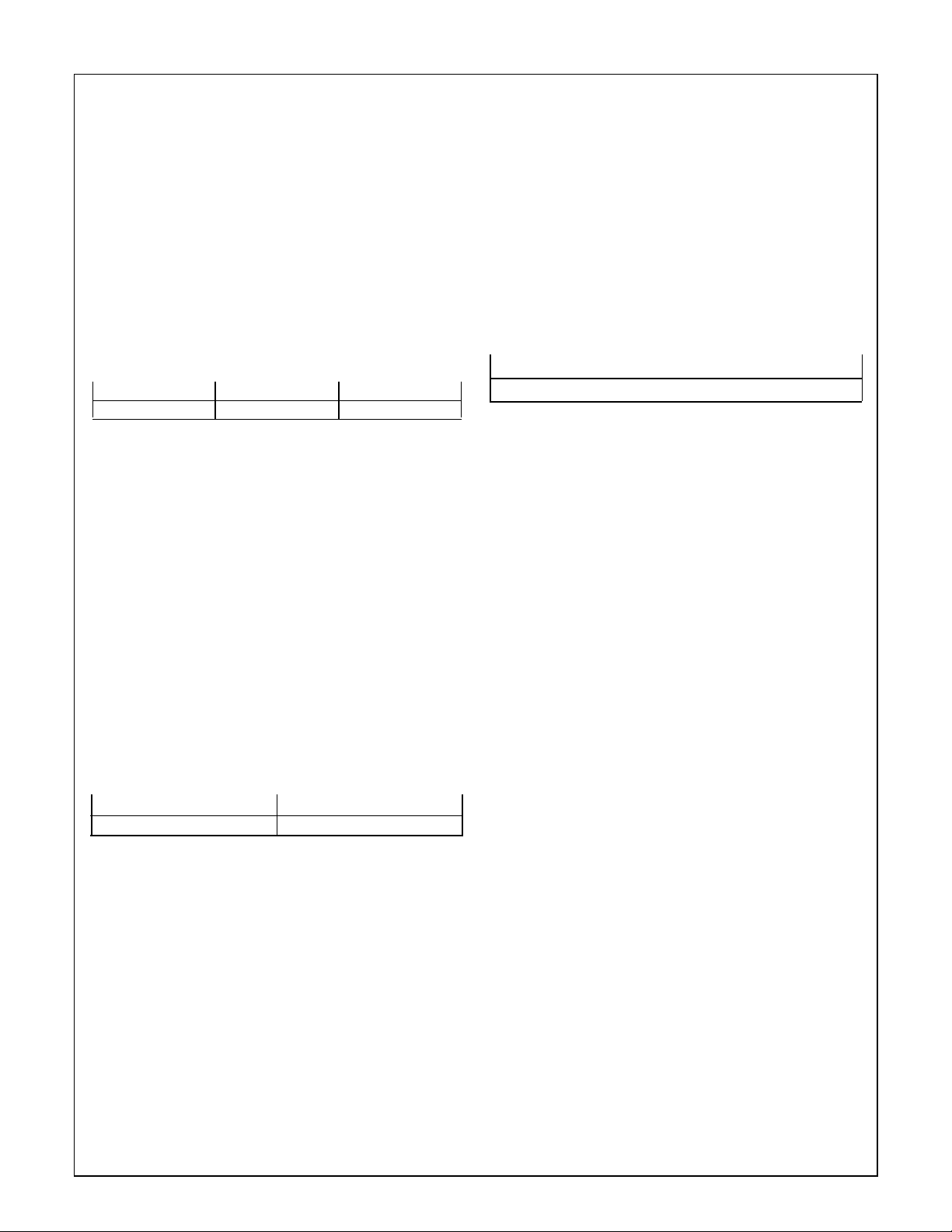

CR16 CompactRISC Microcontroller with CAN Interface Family Selection Guide

Programmable devices

EEPROM

NSID

Speed

(MHz)

Flash/

(kByte)

Data

Memory

SRAM

(kBytes)

USART Timer I/Os

(Bytes)

Temp.

Range

Peripherals

Package

Type

CR16MCS9VJEx 16 64 2176 3 2

CR16MAS9VJEx 24 64 3 2

Factory Programmed devices

EEPROM

NSID

Speed

(MHz)

Flash/

(KByte)

Data

Memory

SRAM

(kBytes)

USART Timer I/Os

(Bytes)

CR16MCS9VJExy 16 64 2176 3 2

CR16MCS9VJExy 24 64 2176 3 2

ROM devices

EEPROM

Data

Memory

(Bytes)

SRAM

(kBytes)

USART Timer I/Os

NSID

Speed

(MHz)

Flash/

ROM

(KByte)

CR16HCS9VJEx 24 64 2176 3 2

CR16MCS5VJEx 24 64 2176 3 2

CR16MBR5VJEx 24 32 2176 3 2

CR16MAR5VJEx 24 32 3 2

CR16MAS5VJEx 24 64 3 2

Note:

• Suffix x in the NSID is defined below:

Temperature Ranges:

I = Industrial

E = Extended

• Suffix y in the NSID defines the ROM code.

Note: All devices contains Access.bus (ACB), Clock and Reset, MICROWIRE/API, Multi-Input Wake-Up (MIWU), Power

Management (PMM), and the Real-Time Timer and Watchdog (TWM) modules. Access.bus is compatible with I2C bus

offered by Philips Semiconductor.

-40°C to +85°C is represented when x is 8

-40°C to +125°C is represented when x is 7

CR16 CompactRISC Microcontroller with CAN Interface

Family Devices

National Semiconductor currently offers a variety of the

CR16 CompactRISC Microcontrollers with CAN interface.

The CR16MCS offer complete functionality in an 80-pin

PQFP package.

2MFT,

VTU

2MFT,

VTU

2MFT,

VTU

2MFT,

VTU

2MFT,

VTU

2MFT,

VTU

2MFT,

VTU

2MFT,

VTU

2MFT,

VTU

56 E, I

56 E, I

Temp.

Range

56 E, I

56 E, I

Temp.

Range

56 E, I

56 E, I

56 E, I

ADC, CAN,

Comparators

ADC, CAN,

Comparators

Peripherals

ADC, CAN,

Comparators

ADC, CAN,

Comparators

Peripherals

ADC, CAN,

Comparators

ADC, CAN,

Comparators

ADC, CAN,

Comparators

80 PQFP

80 PQFP

Package

Type

80 PQFP

80 PQFP

Package

Type

80 PQFP

80 PQFP

80 PQFP

56 E, I CAN, 80 PQFP

56 E, I CAN, 80 PQFP

www.national.com 4

3.0 Device Overview

The devices are complete microcomputers with all system

timing, interrupt logic, program memory, data memory, and I/

O ports included on-chip, making it well-suited to a wide

range of embedded controller applications.

3.1 CR16B CPU CORE

The device uses a CR16B CPU core module. This is the

same core used in other CompactRISC family member designs, like DECT or GSM chipsets.

The high performance of the CPU core results from the implementation of a pipelined architecture with a two-bytes-percycle pipelined system bus. As a result, the CPU can support

a peak execution rate of one instruction per clock cycle.

Compared with conventional RISC processors, the device

differs in the following ways:

— The CPU core can use on-chip rather than external

memory. This eliminates the need for large and com-

plex bus interface units.

— Most instructions are 16 bits, so all basic instructions

are just two bytes long. Additional bytes are sometimes

required for immediate values, so instructions can be

two or four bytes long.

— Non-aligned word access is allowed. Each instruction

can operate on 8-bit or 16-bit data.

— The device is designed to operate with a clock rate in

the 10 to 24 MHz range rather than 100 MHz or more.

Most embedded systems face EMI and noise con-

straints that limit clock speed to these lower ranges. A

lower clock speed means a simpler, less costly silicon

implementation.

— The instruction pipeline uses three stages. A smaller

pipeline eliminates the need for costly branch predic-

tion mechanisms and bypass registers, while maintain-

ing adequate performance for typical embedded

controller applications.

For more information, please refer to the CR16B Programmer’s Reference Manual, Literature #: 633150.

3.2 MEMORY

The CompactRISC architecture supports a uniform linear address space of 2 megabytes. The device implementation of

this architecture uses only the lowest 128K bytes of address

space. Four types of on-chip memory occupy specific intervals within this address space:

• 64K bytes of flash EEPROM program memory (100K cycles)

• 48K bytes ROM programm memory version available also

(100K cycles)

• 3K bytes of static RAM

• 2K bytes of EEPROM data memory with low endurance

(25K cycles)

• 128 bytes with high endurance (100K cycles)

• 1.5K bytes flash EEPROM memory for ISP code

The 3K bytes of static RAM are used for temporary storage

of data and for the program stack and interrupt stack. Read

and write operations can be byte-wide or word-wide, depending on the instruction executed by the CPU. Each memory

access requires one clock cycle; no wait cycles or hold cycles

are required.

There are two types of flash EEPROM data memory storage.

The 2K bytes of EEPROM data memory with low endurance

(25K cycles) and 128 bytes of flash EEPROM data memory

with high endurance (100K cycles) are used for non-volatile

storage of data, such as configuration settings entered by the

end-user.

The 64K bytes of flash EEPROM program memory are used

to store the application program. It has security features to

prevent unintentional programming and to prevent unauthorized access to the program code. This memory can be programmed with a device external programming unit or with the

device installed in the application system (in-system programming).

There is a factory programmed boot memory used to store

In-System-Programming (ISP) code. (This code allows programming of the program memory via one of the USART interfaces in the final application.)

For flash EEPROM program and data memory, the device internally generates the necessary voltages for programming.

No additional power supply is required.

3.3 INPUT/OUTPUT PORTS

The device has 56 software-configurable I/O pins, organized

into seven 8-pin ports called Port B, Port C, Port F, Port G,

Port H, Port I, and Port L. Each pin can be configured to operate as a general-purpose input or general-purpose output.

In addition, many I/O pins can be configured to operate as a

designated input or output for an on-chip peripheral module

such as the USART, timer, A/D converter, or MICROWIRE/

SPI interface.

The I/O pin characteristics are fully programmable. Each pin

can be configured to operate as a TRI-STATE output, pushpull output, weak pull-up input, or high-impedance input.

3.4 BUS INTERFACE UNIT

The Bus Interface Unit (BIU) controls the interface between

the on-chip modules to the internal core bus. It determines

the configured parameters for bus access (such as the number of wait states for memory access) and issues the appropriate bus signals for each requested access.

The BIU uses a set of control registers to determine how

many wait states and hold states are to be used when accessing flash EEPROM program memory, ISP memory and

the I/O area (Port B and Port C). Upon start-up the configuration registers are set for slowest possible memory access.

To achieve fastest possible program execution, appropriate

values should be programmed. These settings vary with the

clock frequency and the type of on-chip device being accessed.

5 www.national.com

3.5 INTERRUPTS

The Interrupt Control Unit (ICU31L) receives interrupt requests from internal and external sources and generates interrupts to the CPU. An interrupt is an event that temporarily

stops the normal flow of program execution and causes a

separate interrupt service routine to be executed. After the interrupt is serviced, CPU execution continues with the next instruction in the program following the point of interruption.

Interrupts from the timers, USARTs, MICROWIRE/SPI interface, multi-input wake-up, and A/D converter are all

maskable interrupts; they can be enabled or disabled by the

software. There are 32 of these maskable interrupts, organized into 32 predetermined levels of priority.

The highest-priority interrupt is the Non-Maskable Interrupt

(NMI), which is generated by a signal received on the NMI input pin.

3.6 MULTI-INPUT WAKE-UP

The Multi-Input Wake-Up (MIWU16) module can be used for

either of two purposes: to provide inputs for waking up (exiting) from the HALT, IDLE, or Power Save mode; or to provide

general-purpose edge-triggered maskable interrupts from

external sources. This 16-channel module generates four

programmable interrupts to the CPU based on the signals received on its 16 input channels. Channels can be individually

enabled or disabled, and programmed to respond to positive

or negative edges.

3.7 DUAL CLOCK AND RESET

The Dual Clock and Reset (CLK2RES) module generates a

high-speed main system clock from an external crystal network. It also provides the main system reset signal and a

power-on reset function.

This module also generates a slow system clock (32.768

kHz) from another external crystal network. The slow clock is

used for operating the device in power-save mode. Without a

32.768kHz external crystal network, the low speed system

clock can be derived from the high speed clock by a prescaler.

Also, two independent clocks divided down from the high

speed clock are available on output pins.

3.8 POWER MANAGEMENT

The Power Management Module (PMM) improves the efficiency of the device by changing the operating mode and

therefore the power consumption according to the required

level of activity.

The device can operate in any of four power modes:

— Active: The device operates at full speed using the

high-frequency clock. All device functions are fully operational.

— Power Save: The device operates at reduced speed

using the slow clock. The CPU and some modules can

continue to operate at this low speed.

— IDLE: The device is inactive except for the Power Man-

agement Module and Timing and Watchdog Module,

which continue to operate using the slow clock.

— HALT: The device is inactive but still retains its internal

state (RAM and register contents).

3.9 MULTI-FUNCTION TIMER

The Multi-Function Timer (MFT16) module contains two independent timer/counter units called MFT1 and MFT2, each

containing a pair of 16-bit timer/counter registers. Each timer/

counter unit can be configured to operate in any of the following modes:

— Processor-Independent Pulse Width Modulation

(PWM) mode, which generates pulses of a specified

width and duty cycle, and which also provides a general-purpose timer/counter.

— Dual Input Capture mode, which measures the

elapsed time between occurrences of external events,

and which also provides a general-purpose timer/

counter.

— Dual Independent Timer mode, which generates sys-

tem timing signals or counts occurrences of external

events.

— Single Input Capture and Single Timer mode, which

provides one external event counter and one system

timer.

3.10 VERSATILE TIMER UNIT

The Versatile Timer Unit (VTU) module contains four independent timer subsystems, each operating in either dual 8-bit

PWM configuration, as a single 16-bit PWM timer, or a 16-bit

counter with two input capture channels. Each of the four timer subsystems offer an 8-bit clock prescaler to accommodate

a wide range of frequencies.

3.11 REAL-TIME TIMER AND WATCHDOG

The Timing and Watchdog Module (TWM) generates the

clocks and interrupts used for timing periodic functions in the

system. It also provides Watchdog protection against software errors. The module operates on the slow system clock.

The real-time timer can generate a periodic interrupt to the

CPU at a software-programmed interval. This can be used

for real-time functions such as a time-of-day clock. The realtime timer can trigger a wake-up condition from power-save

mode via the Multi-Input Wake-Up module.

The Watchdog is designed to detect program execution errors such as an infinite loop or a “runaway” program. Once

Watchdog operation is initiated, the application program

must periodically write a specific value to a Watchdog register, within specific time intervals. If the software fails to do so,

a Watchdog error is triggered, which resets the device.

3.12 USART

The USART supports a wide range of programmable baud

rates and data formats, and handles parity generation and

several error detection schemes. The baud rate is generated

on-chip, under software control.

There are two independent USARTs in the device and they

offer a wake-up condition from the power-save mode via the

Multi-Input Wake-Up module.

3.13 MICROWIRE/SPI

The MICROWIRE/SPI (MWSPI) interface module supports

synchronous serial communications with other devices that

conform to MICROWIRE or Serial Peripheral Interface (SPI)

specifications. It supports 8-bit and 16-bit data transfers.

www.national.com 6

The MICROWIRE interface allows several devices to communicate over a single system consisting of four wires: serial

in, serial out, shift clock, and slave enable. At any given time,

the MICROWIRE interface operates as the master or a slave.

The support supports the full set of slave select for multislave implementation.

In master mode, the shift clock is generated on chip under

software control. In slave mode, a wake-up out of powersave mode is triggered via the Multi-Input Wake-Up module.

3.14 CR16CAN

The CR16CAN device contains a FullCAN class, CAN serial

bus interface for applications that require a high speed (up to

1MBits per second) or a low speed interface with CAN bus

master capability. The data transfer between CAN and the

CPU is established by 15 memory mapped message buffers,

which can be individually configured as receive or transmit

buffers. An incoming message is filtered by two masks, one

for the first 14 message buffers and another one for the 15th

message buffer to provide a basic CAN path. A priority decoder allows any buffer to have the highest or lowest transmit

priority. Remote transmission requests can be processed automatically by automatic reconfiguration to a receiver after

transmission or by automated transmit scheduling upon reception. In addition, a time stamp counter (16-bits wide) is

provided to support real time applications.

The CR16CAN device is a fast core bus peripheral, which allows single cycle byte or word read/write access. A set of diagnostic features (such as loopback, listen only, and error

identification) support the development with the CR16CAN

module and provide a sophisticated error management tool.

The CR16CAN receiver can trigger a wake-up condition out

of the power-save modes via the Multi-Input Wake-Up module.

3.17 ANALOG COMPARATORS

The Dual Analog Comparator (ACMP2) module contains two

independent analog comparators with all necessary control

logic. Each comparator unit compares the analog input voltages applied to two input pins and determines which voltage

is higher. The CPU uses a memory-mapped register to control the comparator and to obtain the comparison results. The

comparison result can also be applied to comparator output

pins.

3.18 DEVELOPMENT SUPPORT

A powerful cross-development tool set is available from National Semiconductor and third parties to support the development and debugging of application software for the

CR16MCS9. The tool set lets you program the application

software in C and is designed to take full advantage of the

CompactRISC architecture.

There are In-System Emulation (ISE) devices available for

the device from iSYSTEM™, as well as lower-cost evaluation

boards. See your National Semiconductor sales representative for current information on availability and features of emulation equipment and evaluation boards.

3.15 ACCESS.BUS INTERFACE

The ACCESS.bus interface module (ACB) is a two-wire serial interface with the ACCESS.bus physical layer. It is also

compatible with Intel’s System Management Bus (SMBus)

and Philips’ I2C bus. The ACB module can be configured as

a bus master or slave, and can maintain bi-directional communications with both multiple master and slave devices.

The ACCESS.bus receiver can trigger a wake-up condition

out of the power-save modes via the Multi-Input Wake-Up

module.

3.16 A/D CONVERTER

The A/D Converter (ADC) module is a 12-channel multiplexed-input analog-to-digital converter. The A/D Converter

receives an analog voltage signal on an input pin and converts the analog signal into an 8-bit digital value using successive approximation. The CPU can then read the result

from a memory-mapped register. The module supports four

automated operating modes, providing single-channel or 4channel operation in single or continuous mode.

The device has a separate pin, Vref, for the A/D reference

voltage.

7 www.national.com

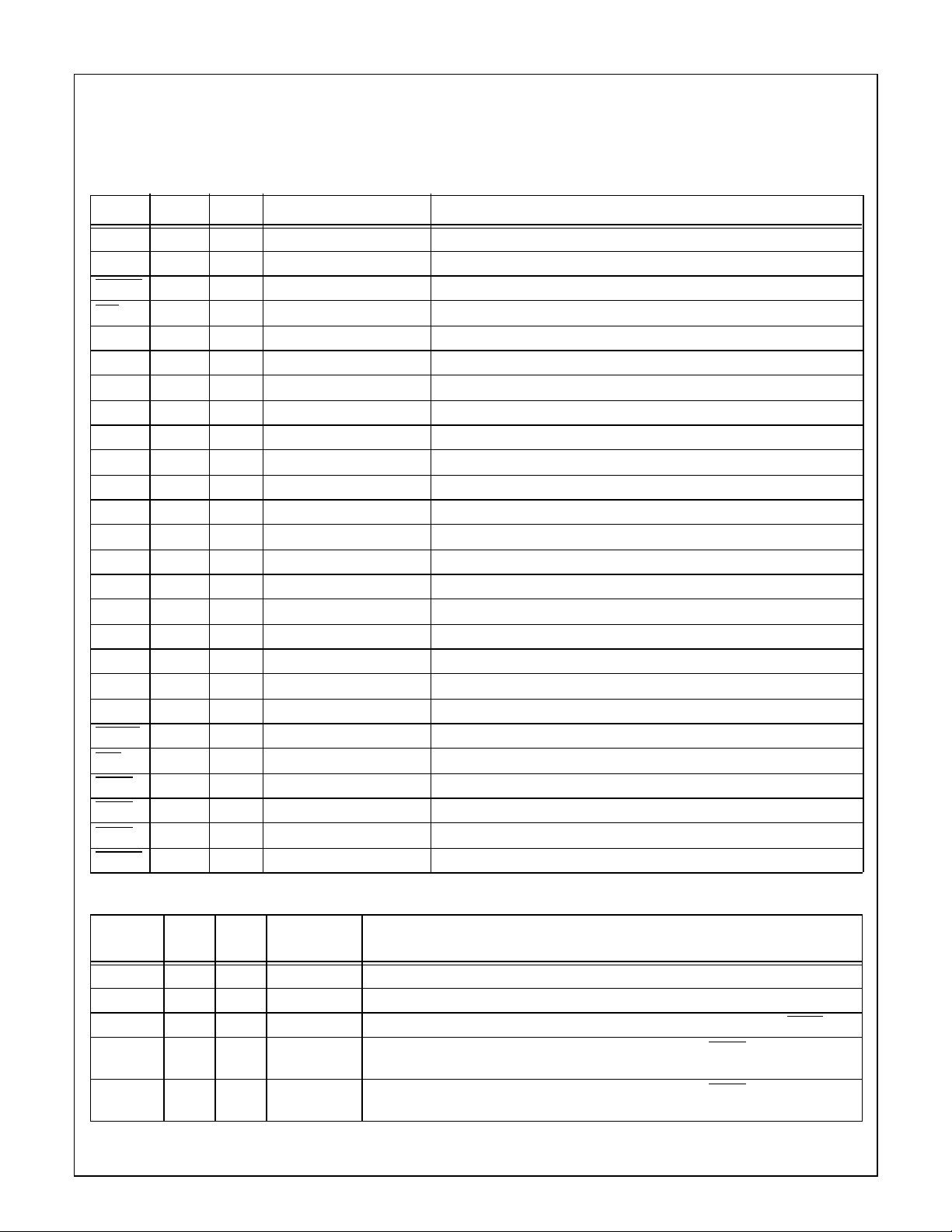

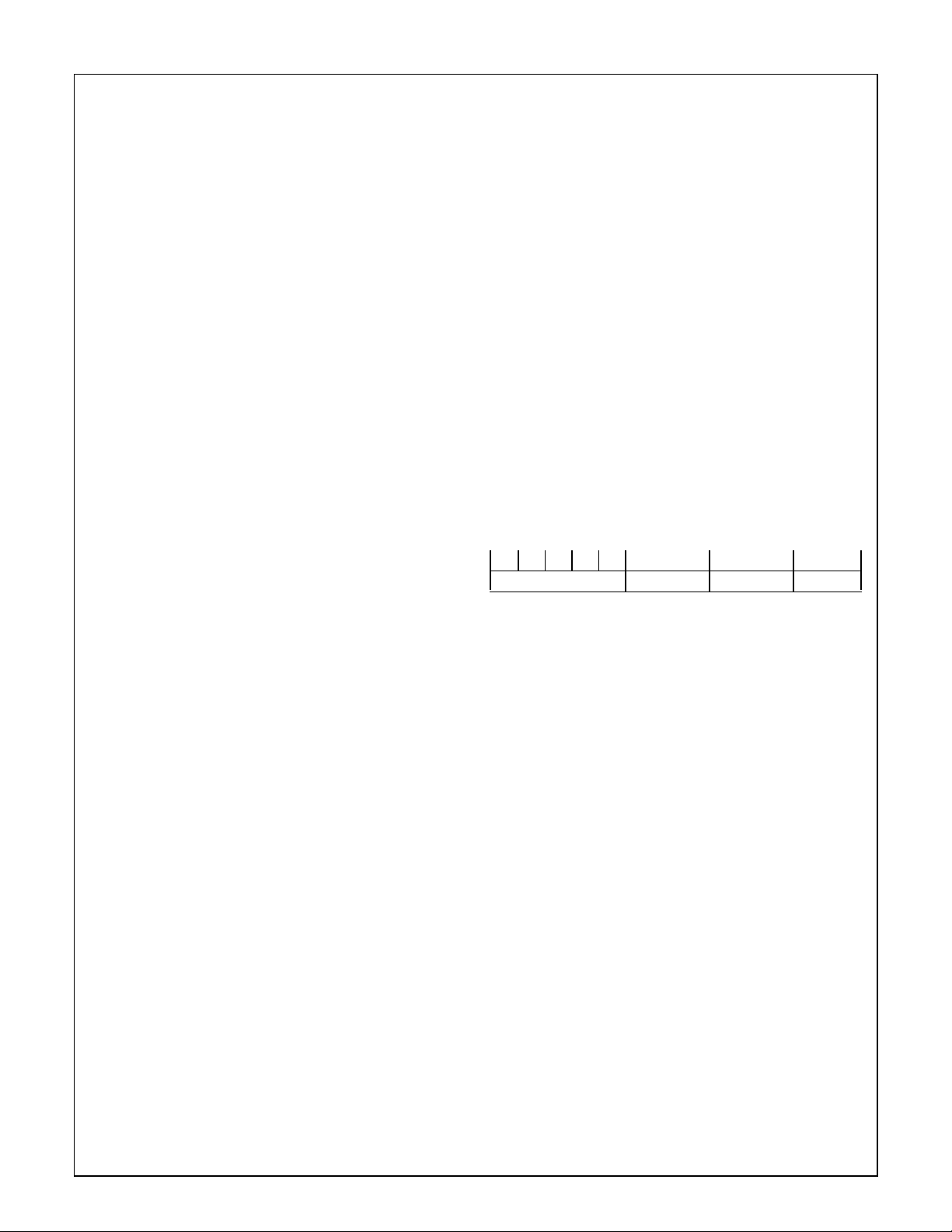

4.0 Device Pinouts

Pin Name Alternate Function(s) Pin Number Type

PH4 MWCS 1 I/O

PH5 MD1D0 2 I/O

PH6 MD0D1 3 I/O

PH7 MSK 4 I/O

PB0 D0 5 I/O

PB1 D1 6 I/O

PB2 D2 7 I/O

PB3 D3 8 I/O

PB4 D4 9 I/O

PB5 D5 10 I/O

PB6 D6 11 I/O

PB7 D7 12 I/O

ENV0/CLKOUT1 13 I/O

SDA 14 I/O

SCL 15 I/O

GND 16 PWR

Vcc 17 PWR

GND 18 PWR

CANTx 19 O

CANRx 20 I

PC0 D8 21 I/O

PC1 D9 22 I/O

PC2 D10 23 I/O

PC3 D11 24 I/O

PC4 D12 25 I/O

PC5 D13 26 I/O

PC6 D14 27 I/O

PC7 D15 28 I/O

PG7 CKX1 29 I/O

PG6 TDX1 30 I/O

PG5 RDX1 31 I/O

PG4 TIO6 32 I/O

PG3 TIO5 33 I/O

PG2 CKX2 34 I/O

PG1 TDX2 35 I/O

PG0 RDX2 36 I/O

CLKOUT2 37 O

ENV1/CLK

PF7 TIO4 38 I/O

PF6 TIO3 39 I/O

PF5 T2B 40 I/O

PF4 T2A 41 I/O

PF3 TIO2 42 I/O

PF2 TIO1 43 I/O

PF1 TIB 44 I/O

Table 1Package Pin Assignments

1

37 I/O

www.national.com 8

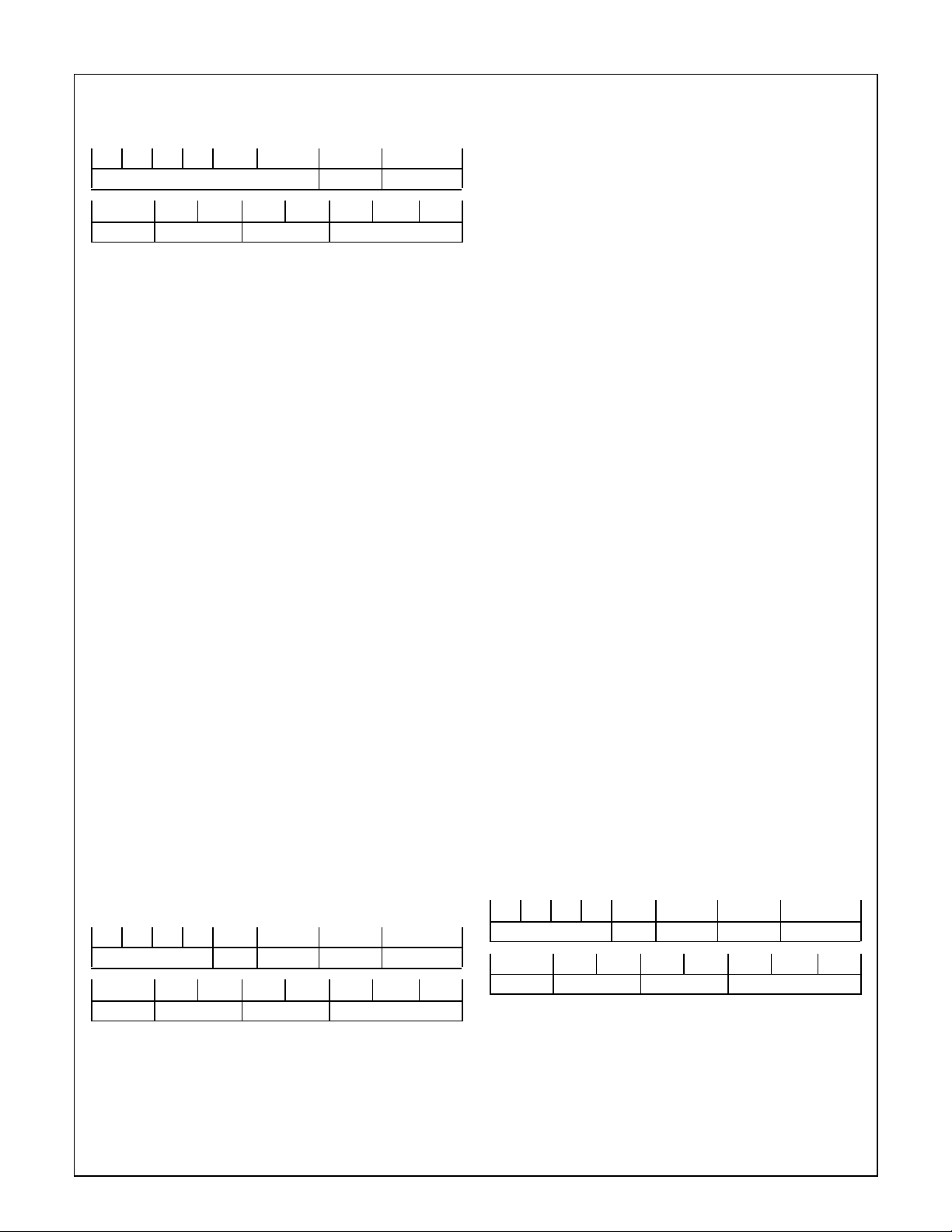

Table 1Package Pin Assignments

Pin Name Alternate Function(s) Pin Number Type

PF0 TIA 45 I/O

NMI 46 I

X1CKO 47 O

X1CKI 48 I

GND 49 PWR

Vcc 50 PWR

GND 51 PWR

X2CKO 52 O

X2CKI 53 I

2

RESET

PI0 ACH0

PI1 ACH1

PI2 ACN2

PI3 ACH3

PI4 ACH4

PI5 ACH5

PI6 ACH6

PI7 ACH7

3

3

3

3

3

3

3

3

54 I

55 I/O

56 I/O

57 I/O

58 I/O

59 I/O

60 I/O

61 I/O

62 I/O

Vref 63 PWR

AGND 64 PWR

AVcc 65 PWR

PH0 ACH83, WUI4 66 I/O

PH1 ACH93, WUI5 67 I/O

PH2 ACH103, WUI6 68 I/O

PH3 ACH113, WUI7 69 I/O

GND 70 PWR

Vcc 71 PWR

GND 72 PWR

PL0 COMP1N3, WUI0 73 I/O

PL1 COMP1P3, WUI1 74 I/O

PL2 COMP1O, WUI2 75 I/O

PL3 COMP2O, WUI3 76 I/O

PL4 COMP2P

PL5 COMP2N

3

3

77 I/O

78 I/O

PL6 TIO7 79 I/O

PL7 TIO8 80 I/O

Note 1: The ENV0 and ENV1 pins each have a weak pull-up to keep the input from floating.

Note 2: The RESET input has a weak pulldown.

Note 3: These functions are always enabled, due to the direct low-impedance path to these pins.

9 www.national.com

4.1 PIN DESCRIPTION

The following is a brief description of all device pins.

Some pins have alternate functions which may be enabled.

These pins can be individually configured as general purpose pins, even when the module they belong to is enabled.

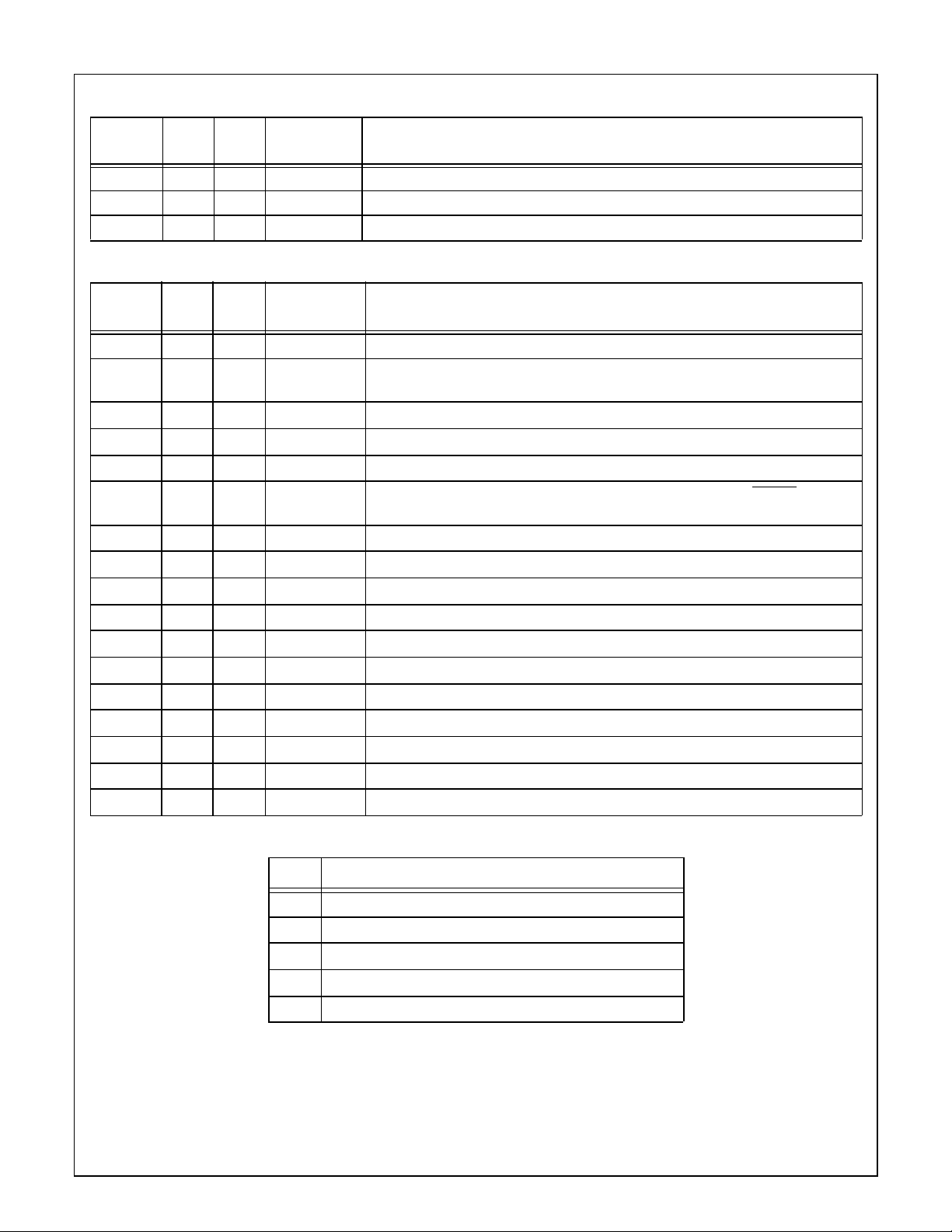

Table 2Input Pins

Signal Type Active Pin (* for a shared pin) Function

X1CKI OSC High Main oscillator clock input.

X2CKI OSC High 32kHz oscillator clock input.

RESET CMOS Low Chip general reset pin. Schmitt trigger input, asynchronous.

ISE CMOS Low Interrupt input for development system.

T1B CMOS Prog. * Timer 1 input B. Shares pin with I/O port pin PF1.

T2B CMOS Prog. * Timer 2 input B. Shares pin with I/O port pin PF5.

RDX1 CMOS High * USART 1 receive data input. Shares pin with I/O port pin PG5.

RDX2 CMOS High * USART 2 receive data input. Shares pin with I/O port pin PG0.

ACH0 Analog * A2D converter channel 0. Shares pin with I/O port pin PI0

ACH1 Analog * A2D converter channel 1. Shares pin with I/O port pin PI1

ACH2 Analog * A2D converter channel 2. Shares pin with I/O port pin PI2

ACH3 Analog * A2D converter channel 3. Shares pin with I/O port pin PI3

ACH4 Analog * A2D converter channel 4. Shares pin with I/O port pin PI4

ACH5 Analog * A2D converter channel 5. Shares pin with I/O port pin PI5

ACH6 Analog * A2D converter channel 6. Shares pin with I/O port pin PI6

ACH7 Analog * A2D converter channel 7. Shares pin with I/O port pin PI7

ACH8 Analog * A2D converter channel 8. Shares pin with I/O port pin PH0

ACH9 Analog * A2D converter channel 9. Shares pin with I/O port pin PH1

ACH10 Analog * A2D converter channel 10. Shares pin with I/O port pin PH2

ACH11 Analog * A2D converter channel 11. Shares pin with I/O port pin PH3

MWCS CMOS Low * SPI/MICROWIRE slave select. Shares pin with I/O port pin PH4.

NMI CMOS Low External non-maskable interrupt.

ENV0 CMOS Low * Strap to select operating environment.

ENV1 CMOS Low * Strap pin to select operating environment.

ENV2 CMOS Low Strap pin to select operating environment.

CANRx CMOS High CAN receive data input.

Table 3Output Pins

Signal Type Active

Pin (* for

a shared pin)

Function

X1CKO OSC High Main oscillator clock output.

X2CKO OSC High 32kHz oscillator clock output.

CLK CMOS High * External reference clock for development environment (shared with ENV1).

CLKOUT1CMOS High * Clock output generated through prescaler (shared with ENV0).

CLKOUT2CMOS High * Clock output generated through prescaler (shared with ENV1).

www.national.com 10

Table 3Output Pins

Signal Type Active

TDX1 CMOS High * USART 1 transmit data output (shared with PG6).

TDX2 CMOS High * USART 2 transmit data output (shared with PG1).

CANTx CMOS High CAN output.

Signal Type Active

PF[0:7] CMOS High * Generic I/O port. Shared with T1A, T1B, TIO1, TIO2, T2A, T2B, TIO3, TIO4.

PG[0:7] CMOS High * Generic I/O port. Shared with RDX2, TDX2, CKX2, TIO5, TIO6, RDX1, TDX1,

PB[0:7] CMOS High * Generic I/O port.

PC[0:7] CMOS High * Generic I/O port.

PL[0:7] CMOS High * Generic I/O port. Shared with 6 comparator pins, MIWU16 on PL0:3.

PH[0:7] CMOS High * Generic I/O port. Shared with ADC input channels 8-11, MWCS, MDIDO,

PI[0:7] CMOS High * Generic I/O port. Shared with ADC input channels 0-7.

T1A CMOS Prog * Timer 1 input A. Shared with I/O port pin PF0.

Pin (* for

a shared pin)

Pin (* for a

shared pin)

Function

Table 4Input/Output Pins

Function

CKX1.

MDODI, MSK; MIWU16 on PH4:7.

T2A CMOS Prog * Timer 2 input A. Shared with I/O port pin PF4.

TIO[0:7] CMOS Prog * Versatile timer unit I/Os. Shared with PF2:3, PF6:7, PG3:4, PL6:7.

MDIDO CMOS High * Master In/Slave Out port: SPI/Microwire. Shared with I/O pin PH5,

MDODI CMOS High * Master Out/Slave In port: SPI/Microwire. Shared with I/O pin PH6.

MSK CMOS Prog * SPI/Microwire clock. Shared with I/O pin PH7.

CKX1 CMOS High * USART 1 clock. Shared with I/O pin PG7.

CKX2 CMOS High * USART 2 clock. Shared with I/O pin PG2

SCL CMOS High ACCESS.bus clock I/O.

SDA CMOS High ACCESS.bus data I/O.

Table 5Power Supply

Signal Function

Vcc Main digital power supply (4 total).

Vref Voltage reference supply for analog to digital converter.

AVcc Analog power supply for analog/digital converter.

AGND Analog reference ground supply.

GND Main digital reference ground (8 total).

11 www.national.com

5.0 System Configuration

The device has two input pins, ENV0 and ENV1, which are

used to specify the operating environment of the device upon

reset. There are also two system configuration registers,

called the Module Configuration (MCFG) register and the

Module Status (MSTAT) register.

5.1 ENV0 AND ENV1 PINS

Upon reset, the operating mode of the device is determined

by the state of the ENV0 and ENV1 input pins, as indicated

in Table6.

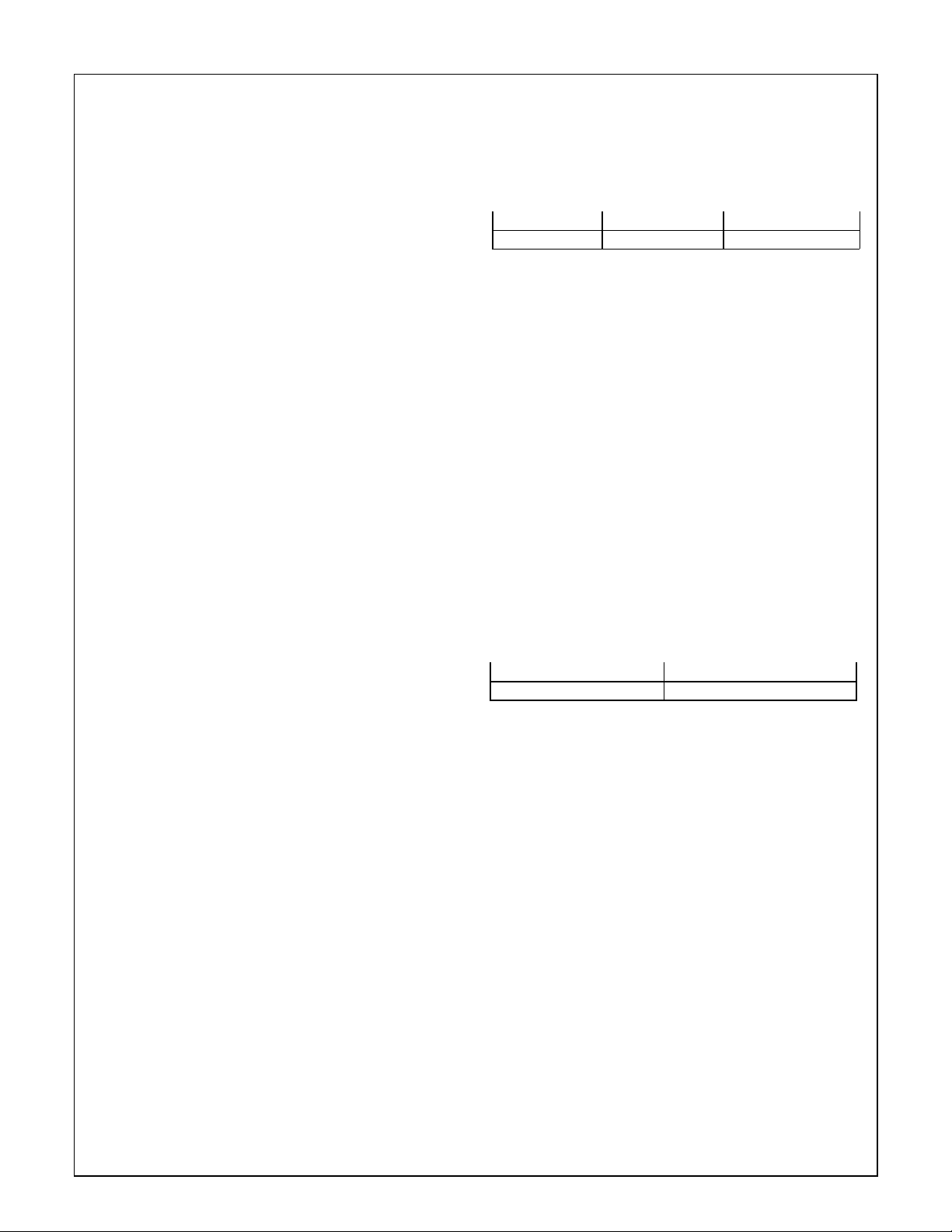

Table 6Operating Environment Selection

ENV1 ENV0 Operating Environment

0 0 Test Mode Flash Memory

0 1 Test Mode

1 0 In-System-Programming mode (ISP)

Internal ROM enabled Mode (IRE), if

1 1

program memory is not empty; or ISPMode, if program memory is empty

normal operating mode, the CLK pin operates

as a CPU clock output.

CLK1OE Generated Clock Output 1 Enable. When

cleared (0), the CLKOUT1 pin (ENV0) stays in

high impedance state. When set (1), the pin

outputs the clock from the prescaler controlled

by PRSSC1.SCDIV1.

CLK2OE Generated Clock Output 2 Enable. When this

bit is set (1) and CLKOE is cleared, the

CLKOUT2 pin (ENV1) outputs the clock from

the prescaler controlled by PRSSC1.SCDIV2.

Otherwise, the CLKOUT2 pin is in high impedance state.

5.3 MODULE STATUS (MSTAT) REGISTER

The MSTAT register is a byte-wide, read-only register that indicates the general status of the device.

The MCFG register format is shown below.

74 3 2 1 0

Reserved PGMBUSY Reserved OENV1 OENV0

In the case where the ENV1 and ENV0 pins are both high,

the reset algorithm looks at the FLCTRL2.EMPTY bit to determine whether the program memory is empty, and sets the

operating mode accordingly.

The ENV0 and ENV1 pins have on-chip pull-up devices that

are enabled during reset while the pins are being sampled.

Therefore, if they are left unconnected, the inputs are considered high and the normal operating mode (IRE-Mode) is selected and the CPU starts to execute code at address 0. To

enter any other operating mode, the external hardware must

drive the appropriate input low.

In the case where the ISP-Mode is selected, the chip starts

executing the ISP code residing in the on-chip ISP-Memory

area.

The test modes are Reserved for factory testing and for external programming of the flash EEPROM program memory.

They should not be invoked otherwise.

5.2 MODULE CONFIGURATION (MCFG)

REGISTER

The MCFG register is a byte-wide, read/write register that

sets the clock output features of the device.

Upon reset, the non-reserved bits of this register are cleared

to zero. The start-up software must write a specific value to

this register in order to configure the CLK output pin function.

When the software writes to this register, it must write a zero

to each reserved bit for the device to operate properly. The

register should be written in active mode only, not in power

save, HALT, or IDLE mode. However, the register contents

are preserved during all power modes.

The MCFG register format is shown below.

7 6 5 4 3 2 1 0

Reserved CLK2OE Reserved CLK1OE CLKOE Reserved

OENV(1:0) Operating Environment. These two bits contain

the values applied to the ENV1 and ENV0 pins

upon reset. These bit values are controlled by

the external hardware upon reset and are held

constant in the register until the next reset.

PGMBUSY Flash EEPROM Programming Busy. This bit is

automatically set to 1 when either the program

memory or the data memory is busy being programmed or erased. It is cleared to 0 when neither of the two flash EEPROM memories is

busy being programmed or erased. When this

bit is set, the software should not attempt any

write access to either of these two memories.

CLKOE CPU Clock Output Enable. When this bit is

cleared (0), the CLK pin (ENV1) remains in the

high-impedance state. When this bit is set (1) in

www.national.com 12

6.0 Input/Output Ports

Each device has up to 56 software-configurable I/O pins, organized into seven ports of up to eight pins per port. The

ports are named Port B, Port C, Port F, Port G, Port H, Port

I, and Port L.

Each pin can be configured to operate as a general-purpose

input or general-purpose output. In addition, many I/O pins

can be configured to operate as a designated input or output

for an on-chip peripheral module such as the USART or the

Multi-Input Wakeup. This is called the pin's “alternate function.” The alternate functions of all I/O pins are shown in the

pinout diagrams in Table1.

The I/O pin characteristics are fully programmable. Each pin

can be configured to operate as a TRI-STATE output, pushpull output, weak pull-up input, or high-impedance input. Different pins within the same port can be individually configured to operate in different modes.

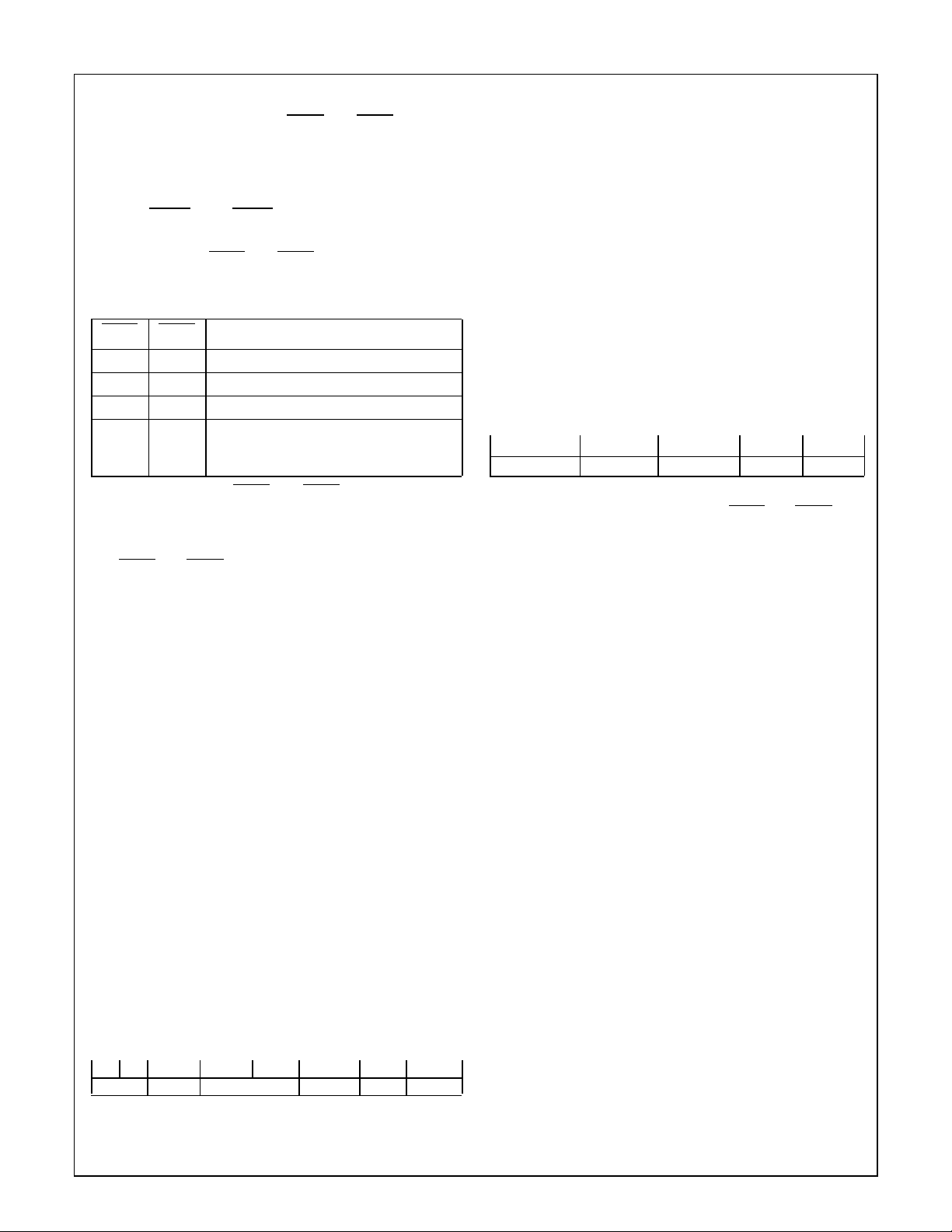

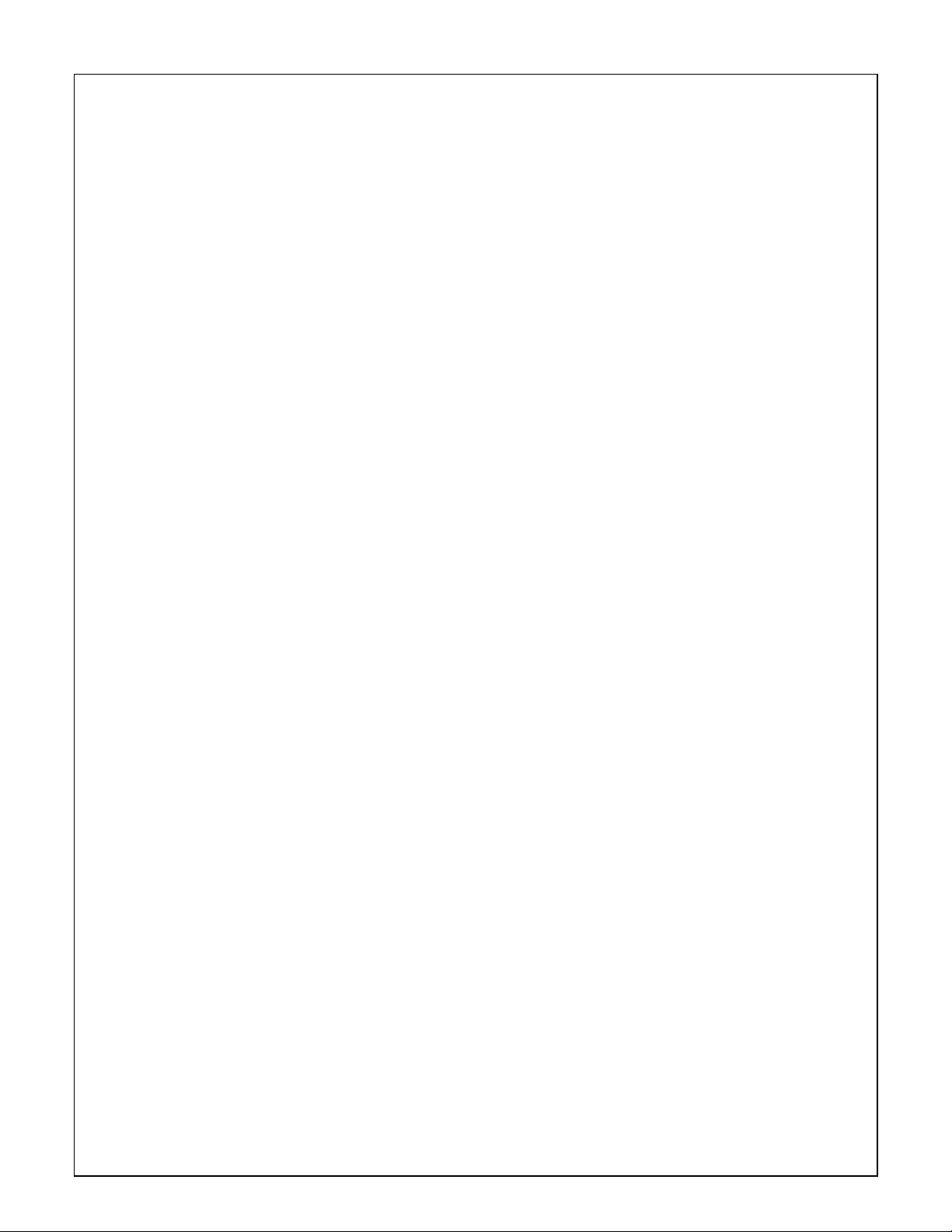

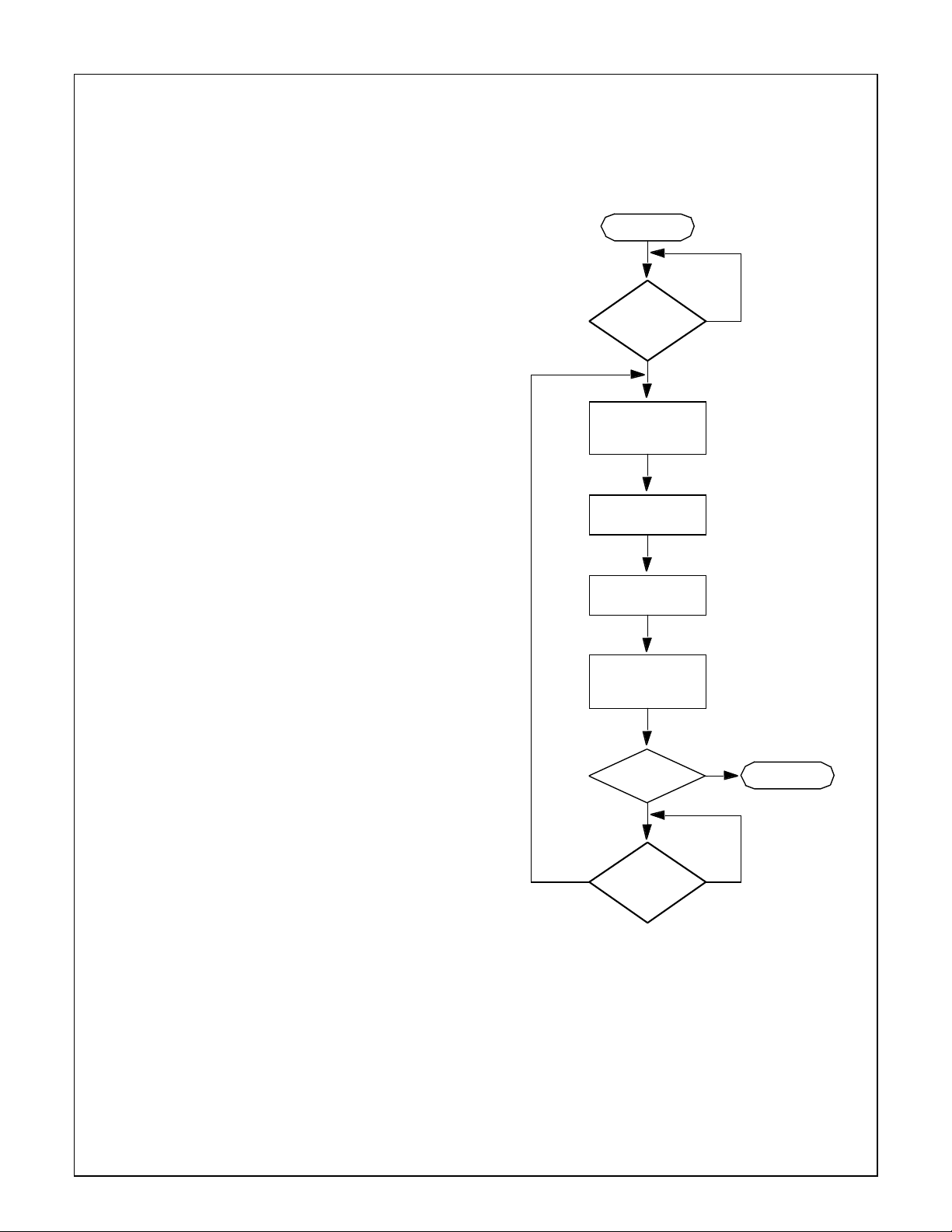

Figure1 is a diagram showing the functional features of an I/

O port pin. The register bits, multiplexers, and buffers allow

the port pin to be configured into the various operating

modes.The output buffer is a TRI-STATE buffer with weak

pull-up capability. The weak pull-up, if used, prevents the port

pin from going to an undefined state when it operates as an

input.

The input buffer is disabled when it is not needed to prevent

leakage current caused by an input signal’s level between

Vcc-0.2 and Vss+0.2 [Volts]. When enabled, it buffers the input signal and sends the pin's logic level to the appropriate

on-chip module where it is latched. A Schmitt-Trigger minimizes the effects of electrical noise.

The electrical characteristics and drive capabilities of the input and output buffers are described in Section25.0.

For some pins, a direct low-impedance path is provided between the pin and an internal analog function. These are the

input pins to the A/D converter and the analog comparators.

6.1 PORT REGISTERS

Each port has an associated set of memory-mapped registers used for controlling the port and for holding the port data.

In general, there are five such registers:

— PxALT: Port alternate function register

— PxDIR: Port direction register

— PxDIN: Port data input register

— PxDOUT: Port data output register

— PxWKPU: Port weak pull-up register

In the descriptions of the ports and port registers, the lowercase letter “x” represents the port designation, either B, C, F,

G, H, I, or L. For example, “PxDIR register” means any one

of the port direction registers: PBDIR, PCDIR, PFDIR, and so

on.

All of the port registers are byte-wide read/write registers, except for the port data input registers, which are read-only registers. Each register bit controls the function of the

corresponding port pin. For example, PFDIR.2 (bit 2 of the

PFDIR register) controls the operation of port pin PF2.

Alternate Function

enable

Weak pull-up

Register

Alt Device Direction

Direction

Register

Alt Device Data Output

Data Out

Register

Data Input

Alternate Data Input

Data In Read Strobe

{

{

{

Weak pull-up

Direction

Data Out

Alt

Figure 1.I/O Pin Functional Diagram

MUX1

Alt

MUX2

Alt

*

1

MUX3

Alt

PIN

13 www.national.com

6.1.1 Port Alternate Function Register

Each port that supports an alternate function (any port other

than Port B or Port C) has an alternate function register (PxALT). This register determines whether the port pins are used

for general-purpose I/O or for the predetermined alternate

function. Each port pin can be controlled independently.

A bit cleared to 0 in the alternate function register causes the

corresponding pin to be used for general-purpose I/O. In this

configuration, the output buffer is controlled by the direction

register and the data output register. The input buffer is routed to the data input register. The input buffer is blocked except when the buffer is actually being read.

A bit set to 1 in the alternate function register causes the corresponding pin to be used for its predetermined peripheral I/

O function. The output buffer data and TRI-STATE configuration are controlled by signals coming from the on-chip peripheral device. The input buffer is enabled continuously in this

case. To minimize power consumption, the input signal

should be held within 0.2 volts of the VCC or GND voltage.

A reset operation clears the port alternate function registers

to 0, which programs the pins to operate as general-purpose

I/O ports. This register must be enabled before the corresponding alternate function is enabled.

6.1.2 Port Direction Register

The port direction register (PxDIR) determines whether each

port pin is used for input or for output. A bit cleared to 0 causes the pin to operate as an input, which puts the output buffer

in the high-impedance state. A bit set to 1 causes the pin to

operate as an output, which enables the output buffer.

A reset operation clears the port direction registers to 0,

which programs the pins to operate as inputs.

6.2 OPEN-DRAIN OPERATION

A port pin can be configured to operate as an inverting opendrain output buffer. To do this, the CPU should clear the bit in

the data output register (PxDOUT) and then use the port direction register (PxDIR) to set the value of the port pin. With

the direction register bit set to 1 (direction=out), the value

zero is forced on the pin. With the direction register bit

cleared to 0 (direction=in), the pin is placed in the TRI-STATE

mode. If desired, the internal weak pull-up can be enabled to

pull the signal high when the output buffer is in the TRISTATE mode.

6.1.3 Port Data Input Register

The data input register (PxDIN) is a read-only register that returns the current state of each port pin. The CPU can read

this register at any time even when the pin is configured as

an output.

6.1.4 Port Data Output Register

The data output register (PxDOUT) holds the data to be driven onto each port pin configured to operate as a general-purpose output. In this configuration, writing to the register

changes the output value. Reading the register returns the

last value written to the register.

A reset operation leaves the register contents unchanged.

Upon power-up, the registers contain unknown values.

6.1.5 Port Weak Pull-Up Register

The weak pull-up register (PxWKPU) determines whether

each port pin uses a weak pull-up on the output buffer. A bit

set to 1 causes the weak pull-up to be used, while a bit

cleared to 0 causes the causes the weak pull-up not to be

used.

The pull-up device, if enabled by the register bit, operates in

the general-purpose I/O mode whenever the port output buffer is in the TRI-STATE mode. In the alternate function mode,

the pull-ups are always disabled.

A reset operation clears the port weak pull-up registers to 0,

which disables all pull-ups.

www.national.com 14

7.0 CPU and Core Registers

The device uses the same CR16B CPU core as other CompactRISC family members. The core's Reduced Instruction

Set Computer (RISC) architecture allows a processing rate

of up to one instruction per clock cycle.

The CPU core uses a set of internal registers:

— General-purpose registers (R0-R13, RA, and SP)

— Dedicated address registers (PC, ISP, and INTBASE)

— Processor Status Register (PSR)

— Configuration Register (CFG)

All of these registers are 16 bits wide except for the three address registers, which are 21 bits wide.

Some register bits are designated as “reserved.” The CPU

must write a zero to each of these bit locations when it writes

to the register. Read operations from reserved bit locations

return undefined values.

7.1 GENERAL-PURPOSE REGISTERS

There are 16 general-purpose registers, designated R0

through R13, RA, and SP. Registers R0 through R13 can be

used for any purpose such as holding variables, addresses,

or index values. The RA register is usually used to store the

return address upon entry into a subroutine. The SP register

is usually used as the pointer to the program run-time stack.

If a general-purpose register is used for a byte-wide operation, only the low-order byte is referenced or modified. The

high-order byte is not used or affected by a byte-wide operation.

7.2 DEDICATED ADDRESS REGISTERS

There are three dedicated address registers: the Program

Counter (PC), the Interrupt Stack Pointer (ISP), and the Interrupt Base Register (INTBASE). Each of these registers is

21 bits wide.

7.2.1 Program Counter

The PC register contains the address of the least significant

word currently being fetched. It is automatically incremented

or changed by the appropriate amount each time an instruction is executed.

The least significant bit of the PC is always zero, thus instructions must always be aligned to an even address in the range

of 0000 to 1FFFE hex.

Upon reset, the PC register is initialized to zero and program

execution starts at that address (if in IRE-Mode). When a reset signal is received, bits 1 through 16 of the PC register

(prior to initialization) are stored in register R0. This allows

the software to determine the point in the program at which

the reset occurred.

7.2.2 Interrupt Stack Pointer

The ISP register points to the lowest address of the last item

stored on the interrupt stack. This stack is used by the hardware when an interrupt or trap service procedure is invoked.

7.2.3 Interrupt Base Register

The INTBASE register holds the address of the Dispatch Table for interrupts and traps. The least significant bit of the register is always zero. Thus, the Dispatch Table starts at an

even address in the range of 0000 to FFFE.

7.3 PROCESSOR STATUS REGISTER

The Processor Status Register (PSR) holds status information and selects the operating modes for the CPU core. The

format of the register is shown below.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved I P E 0 N Z F 0 0 L T C

C bit The Carry (C) bit indicates whether a carry or

borrow occurred after addition or subtraction. It

is set to 1 if a carry or borrow occurred, or

cleared to 0 otherwise.

T bit The Trace (T) bit, when set, causes a Trace

(TRC) trap to be executed after every instruction. This bit is automatically cleared to 0 when

a trap or interrupt occurs.

L bit The Low (L) bit is set by comparison opera-

tions. In a comparison of unsigned integers, the

bit is set to 1 if the second operand (Rdest) is

less than the first operand (Rsrc). Otherwise, it

is cleared to 0.

F bit The Flag (F) bit is a general condition flag that

is set by various instructions. It may be used to

signal exception conditions or to distinguish the

results of an instruction. For example, integer

arithmetic instructions use this bit to indicate an

overflow condition after an addition or subtraction operation.

Z bit The Zero (Z) bit is set by comparison opera-

tions. In a comparison of integers, the bit is set

to 1 if the two operands are equal. Otherwise,

it is cleared to 0.

N bit The Negative (N) bit is set by comparison oper-

ations. In a comparison of signed integers, the

bit is set to 1 if the second operand (Rdest) is

less than the first operand (Rsrc). Otherwise, it

is cleared to 0.

E bit The Local Maskable Interrupt Enable (E) bit is

used to enable or disable maskable interrupts.

If this bit and the Global Maskable Interrupt Enable (I) bit are both set to 1, all maskable interrupts are accepted. Otherwise, only the nonmaskable interrupt is accepted. The E bit is set

to 1 by the Enable Interrupts (EI) instruction

and cleared to 0 by the Disable Interrupts (DI)

instruction.

P bit The Trace Trap Pending (P) bit is used togeth-

er with the Trace (T) bit to prevent a Trace

(TRC) trap from occurring more than once for

any instruction. The P bit may be cleared to 0

(no TRC trap pending) or set to 1 (TRC trap

pending).

15 www.national.com

I bit The Global Maskable Interrupt Enable (I) bit is

used to enable or disable maskable interrupts.

If this bit and the Local Maskable Interrupt Enable (E) bit are both set to 1, all maskable interrupts are accepted. Otherwise, only the nonmaskable interrupt is accepted. This bit is automatically cleared to 0 when an interrupt occurs

and automatically set to 1 upon completion of

an interrupt service routine.

Upon reset, all non-reserved bits of the register are cleared

to 0 except for the E bit (bit 9), which is set to 1. When a device reset occurs, the PSR contents prior to the reset are

stored into register R1, allowing the initialization software to

determine the state of the device prior to the reset operation.

7.4 CONFIGURATION REGISTER

The Configuration (CFG) register is a 16-bit core register that

determines the size of the INTBASE register. For the device,

the CFG register should always be left in its default state

(cleared to zero), resulting in a 16-bit INTBASE register.

7.5 ADDRESSING MODES

Each instruction operates on one or more operands. An operand can be a register or a memory location.

Most instructions use one, two, or three device registers as

operands. The instruction opcode specifies the registers to

be operated on. Some instructions may use an immediate

value (a value provided in the instruction itself) instead of a

register.

Memory locations are accessed only by the Load and Store

commands. The memory location to use for a particular instruction can be specified as an absolute, relative, or far-relative address.

The instruction set supports the following addressing modes:

Register Mode The operand is a general-purpose regis-

ter: R0 through R13, RA, or SP. For example:

ADDB R1, R2

Immediate

Mode

Relative Mode The operand is located in memory. Its ad-

Far-Relative

Mode

A constant operand value is specified within the instruction. In a branch instruction,

the immediate operand is a displacement

from the program counter (PC). In the assembly language syntax, a dollar sign indicates an immediate value. For example:

MULW $4, R4

dress is obtained by adding the contents of

a general purpose register to the constant

value encoded into the displacement field

of the instruction. For example:

LOADW 12(R5), R6

The operand is located in memory. Its ad-

dress is obtained by concatenating a pair

of adjacent general-purpose registers to

form a 21-bit value, and adding this value

to the constant value encoded into the displacement field of the instruction.

Absolute Mode The operand is located in memory. Its ad-

dress is specified within the instruction.

For example:

LOADB 4000, R6

For additional information on the instruction set and instruction encoding, see the CompactRISC CR16B Programmer's

Reference manual.

7.6 STACKS

A stack is a one-dimensional data buffer in which values are

entered and removed one at a time. The last valued entered

is the first one removed. A register called the stack pointer

contains the current address of the last item entered on the

stack. In the device, when an item is entered or “pushed”

onto the stack, the stack expands downward in memory (the

stack pointer is decremented). When an item is removed or

“popped” from the stack, the stack shrinks upward in memory

(the stack pointer is incremented).

The device uses two type of stacks: the program stack and

the interrupt stack.

The program stack is used by the software to save and restore register values upon entry into and exit from a subroutine. The software can also use the program stack to store

local and temporary variables. The stack pointer for this stack

is the SP register.

The interrupt stack is used to save and restore the program

state when an exception occurs (an interrupt or software

trap). The on-chip hardware automatically pushes the program state information onto the stack before the exception

service procedure is executed. Upon exit from the exception

service procedure, the hardware pops this information from

the stack and restores the program state. The stack pointer

for this stack is the ISP register.

7.7 INSTRUCTION SET

Table7 is a summary list of all instructions in the device instruction set. For each instruction, the table shows the mnemonic and a brief description of the operation performed.

In the Mnemonic column, the lower-case letter “i” is used to

indicate the type of integer that the instruction operates on,

either “B” for byte or “W” for word. For example, the notation

ADDi for the “add” instruction means that there are two forms

of this instruction, ADDB and ADDW, which operate on bytes

and words, respectively.

Similarly, the lower-case string “cond” is used to indicate the

type of condition tested by the instruction. For example, the

notation Jcond represents a class of conditional jump instructions: JEQ for Jump on Equal, JNE for Jump on Not Equal,

and so on.

www.national.com 16

For detailed information on all instructions, see the

CompactRISC CR16B Programmer's Reference manual.

Table 7Device Instruction Set Summary

Mnemonic Description

ADDi Add Integer

ADDUi Add Unsigned Integer

ADDCi Add Integer with Carry

ANDi Bitwise Logical AND

ASHUi Arithmetic Shift Unsigned

Bcond Conditional Branch

Bcond0i Compare Register to 0 and Branch

Bcond1i Compare Register to 1and Branch

BAL Branch and Link

BR Unconditional Branch

CBITi Clear Bit in Integer

CMPi Compare Integer

DI Disable Maskable Interrupts

EI Enable Maskable Interrupts

EIWAIT Enable Interrupts and Wait for Interrupt

EXCP Exception

Jcond Conditional Jump

JAL Jump and Link

JUMP Jump

LOADi Load Integer

LOADM Load Multiple Registers

LPR Load Processor Register

LSHi Logical Shift Integer

MOVi Move Integer

MOVXB Move with Sign-Extension

MOVZB Move with Zero-Extension

MULi Multiply Integer

MULSi Multiply Signed

MULUW Multiply Unsigned

NOP No Operation

ORi Bitwise Logical OR

POP Pop Registers from Stack

POPRET Pop and jump RA

PUSH Push Registers on Stack

RETX Return from Exception

Scond Save Condition as Boolean

MULi Multiply Integer

SBITi Set Bit in Integer

STORi Store Integer

STORM Store Registers to Memory

SUBi Subtract Integer

Table 7Device Instruction Set Summary

Mnemonic Description

SUBCi Subtract Integer with Carry

TBIT Test Bit

WAIT Wait for Interrupt

XORi Bitwise Logical Exclusive OR

17 www.national.com

8.0 Bus Interface Unit

The Bus Interface Unit (BIU) controls the interface between

the internal core bus and those on-chip modules which are

mapped into BIU zones. These on-chip modules are the flash

EEPROM program memory, the ISP-memory and the I/Ozone. It determines the configured parameters for bus access (such as the number of wait states for memory access)

and issues the appropriate bus signals for the requested access.

Note: The device is manufactured in a 224-pin version which

is used in emulation equipment. In the 224-pin device, the

BIU controls access to both on-chip and off-chip memory and

peripherals. Operation of the 224-pin device and the use of

chip-external memory is beyond the scope of this data sheet.

8.1 BUS CYCLES

There are four types of data transfer bus cycles:

— Normal read

— Fast read

— Early write

— Late write

The type of data cycle used in a particular transaction depends on the type of CPU operation (a write or a read), the

type of memory or I/O being accessed, and the access type

programmed into the BIU control registers (early/late write or

normal/fast read).

For read operations, a basic normal read takes two clock cycles, whereas a fast read bus cycle takes one clock cycle.

Upon reset of the device, normal read bus cycles are enabled

by default.

For write operations, a basic late write bus cycle takes two

clock cycles, whereas a basic early write bus cycle takes

three clock cycles. Upon reset of the device, early write bus

cycles are enabled by default. However, late write bus cycles

are needed for ordinary write operations, so this configuration should be changed by the application software (see

Section8.2.1).

In certain cases, one or more additional clock cycles are added to a bus access cycle. There are two types of additional

clock cycles for ordinary memory accesses, called internal

wait cycles (TIW) and hold (T

A wait cycle is inserted in a bus cycle just after the memory

address has been placed on the address bus. This gives the

accessed memory more time to respond to the transaction

request. A hold cycle is inserted at the end of a bus cycle.

This holds the data on the data bus for an extended number

of clock cycles.

hold

) cycles.

8.2 BIU CONTROL REGISTERS

The BIU has a set of control registers that determine how

many wait cycles and hold cycles are to be used for accessing memory. Upon start-up of the device, these registers

should be programmed with appropriate values so that the

minimum allowable number of cycles is used. This number

varies with the clock frequency used.

There are four applicable BIU registers: the BIU Configuration (BCFG) register, the I/O Configuration (IOCFG) register,

the Static Zone 0 Configuration (SZCFG0) register and the

Static Zone 1Configuration (SZCFG1) register. These registers control the bus cycle configuration used for accessing

the various on-chip memory types.

Note: A system configuration register called the Module

Configuration (MCFG) register controls the number of wait

cycles used for accessing the EEPROM data memory. This

register is described in Section5.1.

8.2.1 BIU Configuration (BCFG) Register

The BIU Configuration (BCFG) Register is a byte-wide, read/

write register that selects either early write or late write bus

cycles. The register address is F900 hex. Upon reset, the

register is initialized to 07 hex. The register format is shown

below.

7 6 5 4 3 2 1 0

Reserved Note 1 Note 1 EWR

EWR Early Write. This bit is cleared to 0 for late write

operation (two clock cycles to write) or set to 1

for early write operation.

Note 1: These bits (bit 1 or bit 2) control the configuration of

the 224-pin device used in emulation equipment. The CPU

should set this bit to 1 when it writes to the register.

Upon reset, the BCFG register is initialized to 07 hex, which

selects early write operation. However, late write operation is

required for normal device operation, so the software should

change the register value to 06 hex.

8.2.2 I/O Zone Configuration (IOCFG) Register

The I/O Zone Configuration (IOCFG) register is a word-wide,

read/write register that sets the timing and bus characteristics of I/O Zone memory accesses. In the device implementation, the registers associated to Port B and Port C reside in

the I/O memory array. (These ports are used as a 16-bit data

port, if the device operates in development mode.)

www.national.com 18

The IOCFG register address is F902 hex. Upon reset, the

register is initialized to 069F hex. The register format is

shown below.

15 14 13 12 11 10 9 8

Reserved IPST Reserved

7 6 5 4 3 2 1 0

BW Reserved HOLD WAIT

WAIT Memory Wait cycles

This field specifies the number of TIW (internal

wait state) clock cycles added for each memory

access, ranging from 000 binary for no additional TIW wait cycles to 111 binary for seven

additional TIW wait cycles.

HOLD Memory Hold cycles

This field specifies the number of T

cycles used for each memory access, ranging

from 00 binary for no T

for three T

BW Bus Width.

This bit defines the bus width of the zone.

If cleared to 0, a bus width of 8-bit is used.

if set to 1, a bus width of 16-bit is used.

For the device, a bus width of 16-bit needs to

be set.

IPST Post Idle.

An idle cycle follows the current bus cycle,

when the next bus cycle accesses a different

zone.

If cleared to 0, no idle cycle is inserted.

If set to 1, one idle cycle is inserted.

The IPST bit can be cleared to 0, as no idle cycles are required for on-chip accesses.

Note: Reserved bits must be cleared to 0 when the CPU

writes to the register.

8.2.3 Static Zone 0 Configuration (SZCFG0) Register

The Static Zone 0 Configuration (SZCFG0) register is a

word-wide, read/write register that sets the timing and bus

characteristics of Zone 0 memory accesses. In the device implementation of the CompactRISC architecture, Zone 0 is occupied by the flash EEPROM program memory.

The SCCFG0 register address is F904 hex. Upon reset, the

register is initialized to 069F hex. The register format is

shown below.

15 14 13 12 11 10 9 8

Reserved FRE IPRE IPST Reserved

7 6 5 4 3 2 1 0

BW Reserved HOLD WAIT

WAIT Memory Wait cycles

This field specifies the number of TIW (internal

wait state) clock cycles added for each memory

access, ranging from 000 binary for no additional TIW wait cycles to 111 binary for seven

additional TIW wait cycles. These bits are ignored if the SZCFG0.FRE bit is set to 1.

clock cycles.

hold

cycles to 11 binary

hold

hold

clock

HOLD Memory Hold cycles

This field specifies the number of T

cycles used for each memory access, ranging

from 00 binary for no T

for three T

nored if the SZCFG0.FRE bit is set to 1.

BW Bus Width.

This bit defines the bus width of the zone.

If cleared to 0, a bus width of 8-bit is used.

if set to 1, a bus width of 16-bit is used.

For the devicedevice a bus width of 16-bit

needs to be set.

FRE Fast Read Enable

This bit enables (1) or disables (0) fast read

bus cycles. A fast read operation takes one

clock cycle. A normal read operation takes at

least two clock cycles.

IPST Post Idle.

An idle cycle follows the current bus cycle,

when the next bus cycle accesses a different

zone.

If cleared to 0, no idle cycle is inserted.

If set to 1, one idle cycle is inserted.

The IPST bit can be cleared to 0, as no idle cycles are required for on-chip accesses.

IPRE Preliminary Idle.

An idle cycle is inserted prior to the current bus

cycle, when the new bus cycle accesses a different zone.

If cleared to 0, no idle cycle is inserted.

If set to 1, one idle cycle is inserted.

The IPRE bit can be cleared to 0, as no idle cycles are required for on-chip accesses.

Note: Reserved bits must be cleared to 0 when the CPU

writes to the register.

8.2.4 Static Zone 1 Configuration (SZCFG1) Register

The Static Zone 1 Configuration (SZCFG1) register is a

word-wide, read/write register that sets the timing and bus

characteristics of Zone 1 memory accesses. In the device implementation of the CompactRISC architecture, Zone 1 is occupied by the boot ROM memory (ISP-Memory).

The SCCFG1 register address is F906 hex. Upon reset, the

register is initialized to 069F hex. The register format is

shown below.

15 14 13 12 11 10 9 8

Reserved FRE IPRE IPST Reserved

7 6 5 4 3 2 1 0

BW Reserved HOLD WAIT

WAIT Memory Wait cycles

This field specifies the number of TIW (internal

wait state) clock cycles added for each memory

access, ranging from 000 binary for no additional TIW wait cycles to 111 binary for seven

additional TIW wait cycles. These bits are ignored if the SZCFG0.FRE bit is set to 1.

HOLD Memory Hold cycles

This field specifies the number of T

clock cycles. These bits are ig-

hold

cycles to 11 binary

hold

hold

hold

clock

clock

19 www.national.com

cycles used for each memory access, ranging

from 00 binary for no T

for three T

clock cycles. These bits are ig-

hold

cycles to 11 binary

hold

nored if the SZCFG0.FRE bit is set to 1.

BW Bus Width.

This bit defines the bus width of the zone.

If cleared to 0, a bus width of 8-bit is used.

if set to 1, a bus width of 16-bit is used.

For the device a bus width of 16-bit needs to be

set.

FRE Fast Read Enable

This bit enables (1) or disables (0) fast read bus

cycles. A fast read operation takes one clock

cycle. A normal read operation takes at least

two clock cycles.

IPST Post Idle.

An idle cycle follows the current bus cycle,

when the next bus cycle accesses a different

zone.

If cleared to 0, no idle cycle is inserted.

If set to 1, one idle cycle is inserted.

The IPST bit can be cleared to 0, as no idle cycles are required for on-chip accesses.

IPRE Preliminary Idle.

An idle cycle is inserted prior to the current bus

cycle, when the new bus cycle accesses a different zone.

If cleared to 0, no idle cycle is inserted.

If set to 1, one idle cycle is inserted.

The IPRE bit can be cleared to 0, as no idle cycles are required for on-chip accesses.

Note: Reserved bits must be cleared to 0 when the CPU

writes to the register.

For a write operation normal read mode (SZCFG0.FRE=0),

the number of wait cycles is equal to the value written to the

SZCFG0. WAIT field plus one (in the late write mode) or two

(in the early write mode). The number of inserted hold cycles

is equal to the value written to the SCCFG0.HOLD field,

which can range from zero to three.

Writing to the flash EEPROM program memory is a Flash

programming operation that requires some additional steps,

as explained in Section9.3.

8.3.2 RAM Memory

Read and write accesses to on-chip RAM is performed within

a single cycle, regardless of the BIU settings.

8.3.3 EEPROM Data Memory

There is either no wait state or one wait state used when the

CPU accesses the EEPROM data memory (address F000F27F hex). The number of required wait states (zero or one)

depends on the CPU clock frequency and operating mode,

and is controlled by programming of the DMCSR.ZEROWS

bit in the MCFG register, as explained in Section9.3. No hold

cycles are used.

8.3.4 Accesses to Peripheral

When the CPU accesses on-chip peripherals in the range of

F800-FAFF hex and FC00-FFFF hex, one wait cycle and one

preliminary idle cycle is used. No hold cycles are used.

The IOCFG register determines the access timing for the address range FB00-FB16 hex (Ports B and Port C).

8.3 WAIT AND HOLD STATES USED