National Semiconductor ADC0819 Technical data

查询ADC0819供应商查询ADC0819供应商

ADC0819 8-Bit Serial I/O A/D Converter

with 19-Channel Multiplexer

General Description

The ADC0819 is an 8-Bit successive approximation A/D

converter with simultaneous serial I/O. The serial input controls an analog multiplexer which selects from 19 input

channels or an internal half scale test voltage.

An input sample-and-hold is implemented by a capacitive

reference ladder and sampled data comparator. This allows

the input signal to vary during the conversion cycle.

Separate serial I/O and conversion clock inputs are provided to facilitate the interface to various microprocessors.

Features

Y

Separate asynchronous converter clock and serial data

I/O clock.

Y

19-Channel multiplexer with 5-Bit serial address logic.

Y

Built-in sample and hold function.

December 1994

Y

Ratiometric or absolute voltage referencing.

Y

No zero or full-scale adjust required.

Y

Internally addressable test voltage.

Y

0V to 5V input range with single 5V power supply.

Y

TTL/MOS input/output compatible.

Y

28-pin molded chip carrier or 28-pin molded DIP

Key Specifications

Y

Resolution 8-Bits

Y

Total unadjusted error

Y

Single supply 5V

Y

Low Power 15 mW

Y

Conversion Time 16 ms

g

(/2LSB andg1LSB

ADC0819 8-Bit Serial I/O A/D Converter with 19-Channel Multiplexer

DC

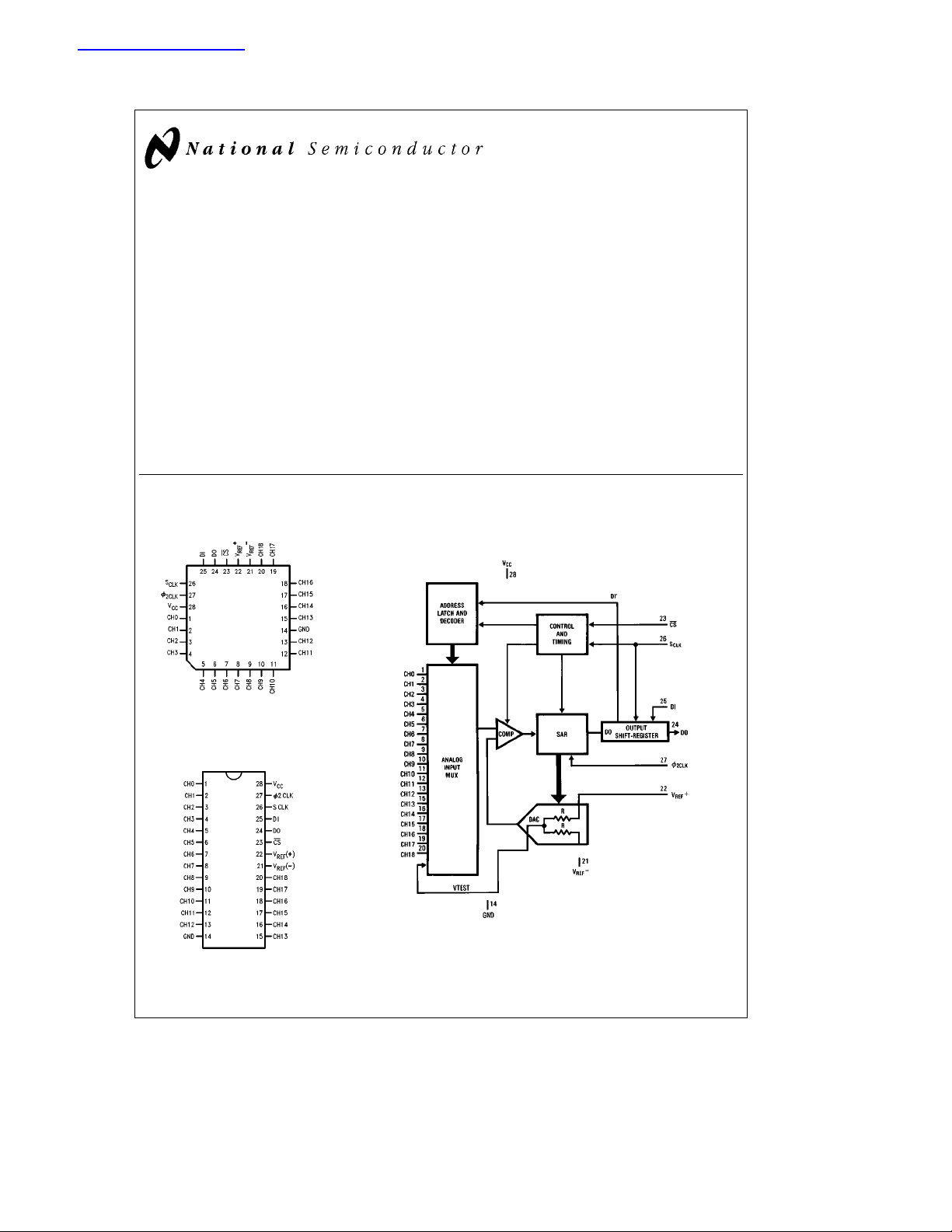

Connection Diagrams

Molded Chip Carrier (PCC) Package

TL/H/9287– 1

Top View

Order Number ADC0819BCV, CCV

See NS Package Number V28A

Dual-In-Line Package

TL/H/9287– 20

Top View

Order Number ADC0819BCN, CIN

See NS Package Number N28B

Functional Diagram

TL/H/9287– 2

C

1995 National Semiconductor Corporation RRD-B30M115/Printed in U. S. A.

TL/H/9287

Absolute Maximum Ratings (Notes1&2)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales

Office/Distributors for availability and specifications.

Supply Voltage (V

Voltage

Inputs and Outputs

Input Current Per Pin (Note 3)

Total Package Input Current (Note 3)

Storage Temperature

Package Dissipation at T

) 6.5V

CC

b

0.3V to V

CC

b

e

25§C 875 mW

A

65§Ctoa150§C

a

g

g

0.3V

5mA

20mA

Lead Temperature (Soldering, 10 sec.)

Dual-In-Line Package (Plastic) 260

Surface Mount Package

Vapor Phase (60 sec.) 215

Infrared (15 sec.) 220

ESD Susceptibility (Note 11) 2000V

Operating Ratings (Notes1&2)

Supply Voltage (VCC) 4.5 VDCto 6.0 V

Temperature Range T

ADC0819BCV, ADC0819CCV

b

40§CsT

MIN

s

ADC0819BCN 0§CsT

ADC0819CIN

b

40§CsT

DC

s

T

T

A

MAX

s

a

85§C

A

s

a

70§C

A

s

a

85§C

A

C

§

C

§

C

§

Electrical Characteristics

The following specifications apply for V

apply from T

to T

MIN

; all other limits T

MAX

Parameter Conditions

CC

e

5V, V

A

e

5V, w

REF

e

e

T

25§C.

J

2 CLK

Typical

(Note 6)

e

2.097 MHz unless otherwise specified. Boldface limits

Tested Design

Limit Limit Units

(Note 7) (Note 8)

CONVERTER AND MULTIPLEXER CHARACTERISTICS

Maximum Total V

Unadjusted Error (Note 4)

ADC0819BCV, BCN

ADC0819CCV, CIN

Minimum Reference

Input Resistance

Maximum Reference

Input Resistance

Maximum Analog Input Range (Note 5) V

REF

e

5.00 V

DC

g

(/2

g

1

g

(/2 LSB

g

1 LSB

8 5 kX

811 11 kX

a

0.05 V

CC

a

0.05 V

CC

Minimum Analog Input Range GNDb0.05 GNDb0.05 V

On Channel Leakage Current (Note 9)

Off Channel Leakage Current (Note 9)

Minimum V

Internal Test Voltage CH 19 Selected 125 125 Counts

Maximum V

Internal Test Voltage CH 19 Selected 130 130 Counts

TEST

TEST

On Channel

Off Channel

On Channele0V

Off Channel

(Note 9)

On Channel

Off Channel

On Channele0V 400 1000 nA

Off Channel

(Note 9)

V

REF

V

REF

e

5V 400 1000 nA

e

0V

b

e

5V

e

5V

e

0V

e

5V

e

VCC, (Note 10)

e

VCC, (Note 10)

400

b

400

b

1000 nA

b

1000 nA

DIGITAL AND DC CHARACTERISTICS

V

, Logical ‘‘1’’ Input V

IN(1)

Voltage (Min)

V

, Logical ‘‘0’’ Input V

IN(0)

Voltage (Max)

I

, Logical ‘‘1’’ Input V

IN(1)

Current (Max)

I

, Logical ‘‘0’’ Input V

IN(0)

Current (Max)

e

5.25V

CC

e

4.75V

CC

e

5.0V 0.005

IN

e

0V

IN

b

0.005

2.0 2.0 V

0.8 0.8 V

2.5 2.5 mA

b

2.5

b

2.5 mA

2

Electrical Characteristics (Continued)

The following specifications apply for V

apply from T

to T

MIN

; all other limits T

MAX

Parameter Conditions

CC

e

5V, V

A

e

5V, w

REF

e

e

T

25§C.

J

e

2.097 MHz unless otherwise specified. Boldface limits

2 CLK

Typical

(Note 6)

Tested Design

Limit Limit Units

(Note 7) (Note 8)

DIGITAL AND DC CHARACTERISTICS (Continued)

V

, Logical ‘‘1’’ V

OUT(1)

Output Voltage (Min) I

V

, Logical ‘‘0’’ V

OUT(0)

Output Voltage (Max) I

I

, TRI-STATE Output V

OUT

Current (Max) V

I

, Output Source V

SOURCE

Current (Min)

I

, Output Sink Current (Min) V

SINK

ICC, Supply Current (Max) CSe1, V

I

(Max) V

REF

e

4.75V

CC

eb

360 mA 2.4 2.4 V

OUT

eb

10 mA 4.5 4.5 V

I

OUT

e

5.25V

CC

e

1.6 mA

OUT

e

0V

OUT

e

5V 0.01 3 3 mA

OUT

e

0V

OUT

e

V

OUT

CC

Open 1 2.5 2.5 mA

REF

e

5V 0.7 1 1 mA

REF

b

0.01

b

14

16 8.0 8.0 mA

0.4 0.4 V

b

3

b

6.5

b

b

6.5 mA

3 mA

AC CHARACTERISTICS

Tested Design

Parameter Conditions Typical Limit Limit Units

(Note 6) (Note 7) (Note 8)

w

, w2Clock Frequency MIN 0.70 1.0

2 CLK

MAX 4.0 2.0 2.1

S

, Serial Data Clock MIN 5.0

CLK

Frequency

MAX 1000 525 525

MHz

KHz

TC, Conversion Process Time MIN Not Including MUX 26 26 w2cycles

Addressing and

Analog Input

MAX

Sampling Times

t

, Access Time Delay From CS MIN 1 w2cycles

ACC

32 32

Falling Edge to DO Data Valid MAX 3

t

, Minimum Set-up Time of CS Falling

SET-UP

Edge to S

t

,CSHold Time After the Falling

HCS

Edge of S

CLK

Rising Edge

CLK

tCS, Total CS Low Time MIN t

MAX tCS(min)a26/w

t

, Minimum DI Hold Time from

HDI

t

HDO

t

SDI

t

DDO

t

TRI

Rising Edge

S

CLK

, Minimum DO Hold Time from S

Falling Edge C

, Minimum DI Set-up Time to S

Rising Edge

, Maximum Delay From S

Falling Edge to DO Data Valid C

CLK

CLK

CLK

, Maximum DO Hold Time, R

Rising edge to DO TRI-STATE) C

(CS

e

R

30k,

L

e

100 pF

L

e

R

30k,

L

e

100 pF

L

e

3k,

L

e

100 pF

L

0 0 ns

200 400 ns

180 200 250 ns

90 150 150 ns

4/w

set-up

2CLK

1

a

2S

CLK

sec

0 ns

a

8/S

CLK

2CLK

sec

sec

10 ns

3

Electrical Characteristics The following specifications apply for V

otherwise specified. Boldface limits apply from T

Parameter Conditions

MIN

to T

MAX

; all other limits T

Typical

(Note 6)

5V, t

CC

e

A

r

e

T

25§C.

J

Tested Design

Limit Limit Units

(Note 7) (Note 8)

e

t

f

20 ns, V

REF

e

5V, unless

e

e

AC CHARACTERISTICS (Continued)

tCA, Analog After Address Is Latched

e

Sampling Time CS

t

, Maximum DO R

RDO

Rise Time C

t

, Maximum DO R

FDO

Fall Time C

Low

e

30 kX, ‘‘TRI-STATE’’ to ‘‘HIGH’’ State 75 150 150

L

e

100 pf ‘‘LOW’’ to ‘‘HIGH’’ State 150 300 300

L

e

30 kX, ‘‘TRI-STATE’’ to ‘‘LOW’’ State 75 150 150

L

e

100 pf ‘‘HIGH’’ to ‘‘LOW’’ State 150 300 300

L

CIN, Maximum Input Analog Inputs, ANO–AN10 and V

REF

11 55

3/S

CLK

a

1 ms sec

Capacitance All Others 5 15

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating

the device beyond its specified operating conditions.

Note 2: All voltages are measured with respect to ground.

Note 3: Under over voltage conditions (V

a

.3V the total package current must be limited to 20 mA. For example the maximum number of pins that can be over driven at the maximum current level of

V

CC

g

5 mA is four.

Note 4: Total unadjusted error includes offset, full-scale, linearity, multiplexer, and hold step errors.

Note 5: Two on-chip diodes are tied to each analog input, which will forward-conduct for analog input voltages one diode drop below ground or one diode drop

greater than V

elevated temperatures, and cause errors for analog inputs near full-scale. The spec allows 50 mV forward bias of either diode. This means that as long as the

analog V

therefore require a minimum supply voltage of 4.950 V

Note 6: Typicals are at 25

Note 7: Tested Limits are guaranteed to National’s AOQL (Average Outgoing Quality Level).

Note 8: Design Limits are guaranteed, but not 100% production tested. These limits are not used to calculate outgoing quality levels.

Note 9: Channel leakage current is measured after the channel selection.

Note 10: 1 count

Note 11: Human body model; 100 pF discharged through a 1.5 kX resistor.

supply. Be careful during testing at low VCClevels (4.5V), as high level analog inputs (5V) can cause this input diode to conduct, especially at

CC

does not exceed the supply voltage by more than 50 mV, the output code will be correct. To achieve an absolute 0 VDCto5VDCinput voltage range will

IN

C and represent most likely parametric norm.

§

e

V

/256.

REF

k

IN

0V and V

l

VCC) the maximum input current at any one pin isg5 mA. If the voltage at more than one pin exceeds

IN

over temperature variations, initial tolerance and loading.

DC

ns

ns

pF

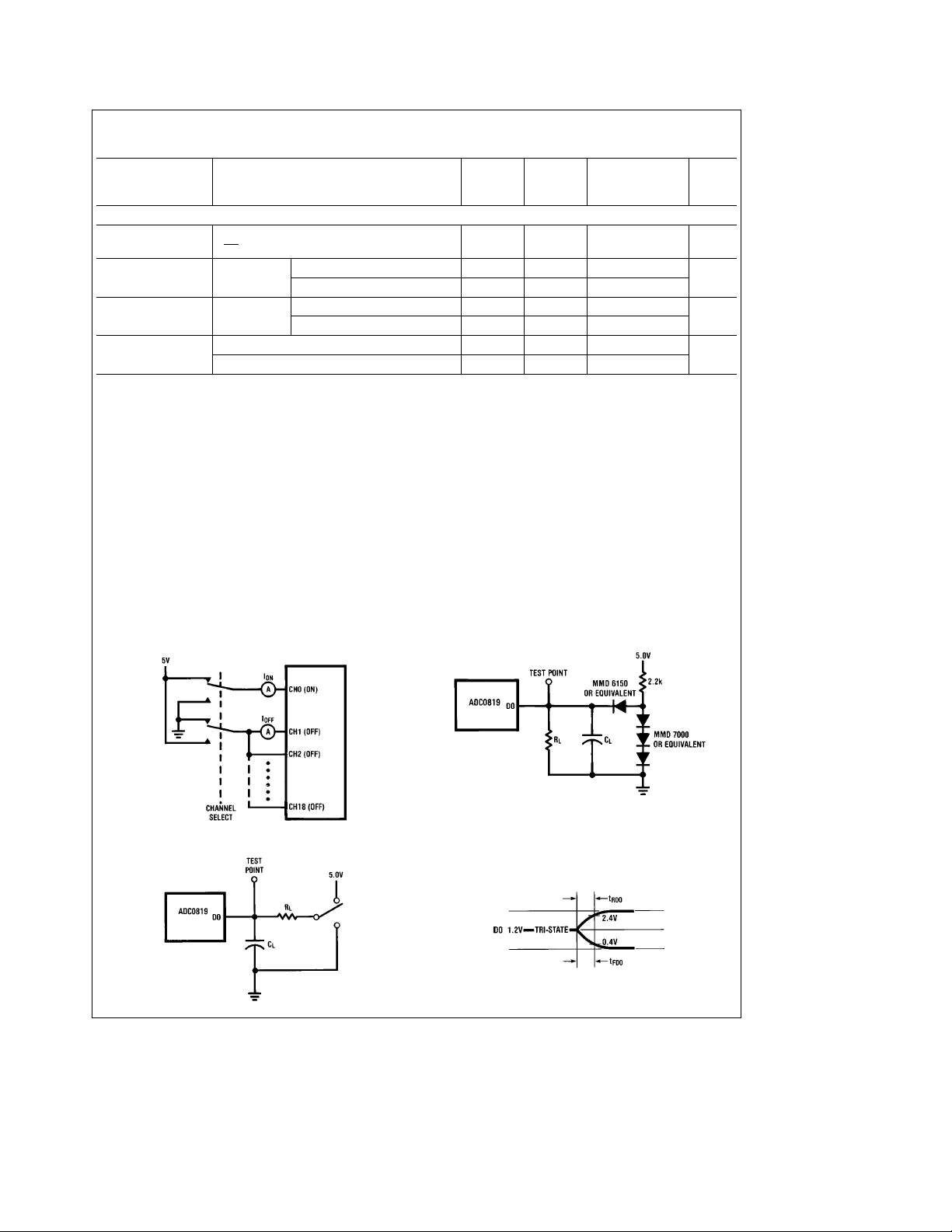

Test Circuits

Leakage Current

t

‘‘TRI-STATE’’

TRI

D0 Except ‘‘TRI-STATE’’

TL/H/9287– 4

TL/H/9287– 3

Timing Diagrams

D0 ‘‘TRI-STATE’’ Rise & Fall Times

TL/H/9287– 6

TL/H/9287– 5

4

Loading...

Loading...