查询ADC0816供应商查询ADC0816供应商

ADC0816/ADC0817

8-Bit µP Compatible A/D Converters

with 16-Channel Multiplexer

ADC0816/ADC0817 8-Bit µP Compatible A/D Converters with 16-Channel Multiplexer

June 1999

General Description

The ADC0816, ADC0817 data acquisition component is a

monolithic CMOS device with an 8-bit analog-to-digital converter, 16-channel multiplexer and microprocessor compatible control logic. The 8-bit A/D converter uses successive

approximation as the conversion technique. The converter

features a high impedance chopper stabilized comparator, a

256R voltage divider with analog switch tree and a successive approximation register. The 16-channel multiplexer can

directly access any one of 16-single-ended analog signals,

and provides the logic for additional channel expansion. Signal conditioning of any analog input signal is eased by direct

access to the multiplexer output, and to the input of the 8-bit

A/D converter.

The device eliminates the need for external zero and

full-scale adjustments. Easy interfacing to microprocessors

is provided by the latched and decoded multiplexer address

inputs and latched TTL TRI-STATE

The design of the ADC0816, ADC0817 has been optimized

by incorporating the most desirable aspects of several A/D

conversion techniques. The ADC0816, ADC0817 offers high

speed, high accuracy, minimal temperaturedependence,excellent long-term accuracy and repeatability, and consumes

minimal power. These features make this device ideally

suited to applications from process and machine control to

consumer and automotive applications. For similar performance in an 8-channel, 28-pin, 8-bit A/D converter, see the

ADC0808, ADC0809 data sheet. (See AN-258 for more information.)

®

outputs.

Block Diagram

Features

n Easy interface to all microprocessors

n Operates ratiometrically or with 5 V

adjusted voltage reference

n 16-channel multiplexer with latched control logic

n Outputs meet TTL voltage level specifications

n 0V to 5V analog input voltage range with single 5V

supply

n No zero or full-scale adjust required

n Standard hermetic or molded 40-pin DIP package

n Temperature range −40˚C to +85˚C or −55˚C to +125˚C

n Latched TRI-STATE output

n Direct access to “comparator in” and “multiplexer out” for

signal conditioning

n ADC0816 equivalent to MM74C948

n ADC0817 equivalent to MM74C948-1

or analog span

DC

Key Specifications

n Resolution 8 Bits

n Total Unadjusted Error

n Single Supply 5 V

n Low Power 15 mW

n Conversion Time 100 µs

1

±

⁄2LSB and±1 LSB

DC

DS005277-1

TRI-STATE®is a registered trademark of National Semiconductor Corporation.

© 1999 National Semiconductor Corporation DS005277 www.national.com

Connection Diagram

Ordering Information

TEMPERATURE RANGE −40˚C to +85˚C

1

Error

±

⁄2Bit Unadjusted ADC0816CCN ADC0816CCJ

±

1 Bit Unadjusted ADC0817CCN

Package Outline N40A Molded DIP J40A Hermetic DIP

Dual-In-Line Package

DS005277-6

Order Number ADC0816CCN or ADC0817CCN

See NS Package Number N40A

www.national.com 2

Absolute Maximum Ratings (Notes 1, 2)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Supply Voltage (V

Voltage at Any Pin −0.3V to (V

Except Control Inputs

Voltage at Control Inputs −0.3V to 15V

(START, OE, CLOCK, ALE, EXPANSION CONTROL,

ADD A, ADD B, ADD C, ADD D)

Storage Temperature Range −65˚C to + 150˚C

Package Dissipation at T

) (Note 3) 6.5V

CC

=

25˚C 875 mW

A

CC

+0.3V)

Lead Temp. (Soldering, 10 seconds)

Dual-In-Line Package (Plastic) 260˚C

Molded Chip Carrier Package

Vapor Phase (60 seconds) 215˚C

Infrared (15 seconds) 220˚C

ESD Susceptibility (Note 9) 400V

Operating Conditions (Notes 1, 2)

Temperature Range (Note 1) T

ADC0816CCN, ADC0817CCN −40˚C≤TA≤+85˚C

Range of V

Voltage at Any Pin 0V to V

(Note 1) 4.5 VDCto 6.0 V

CC

Except Control Inputs

Voltage at Control Inputs 0V to 15V

(START, OE, CLOCK, ALE, EXPANSION CONTROL,

ADD A, ADD B, ADD C, ADD D)

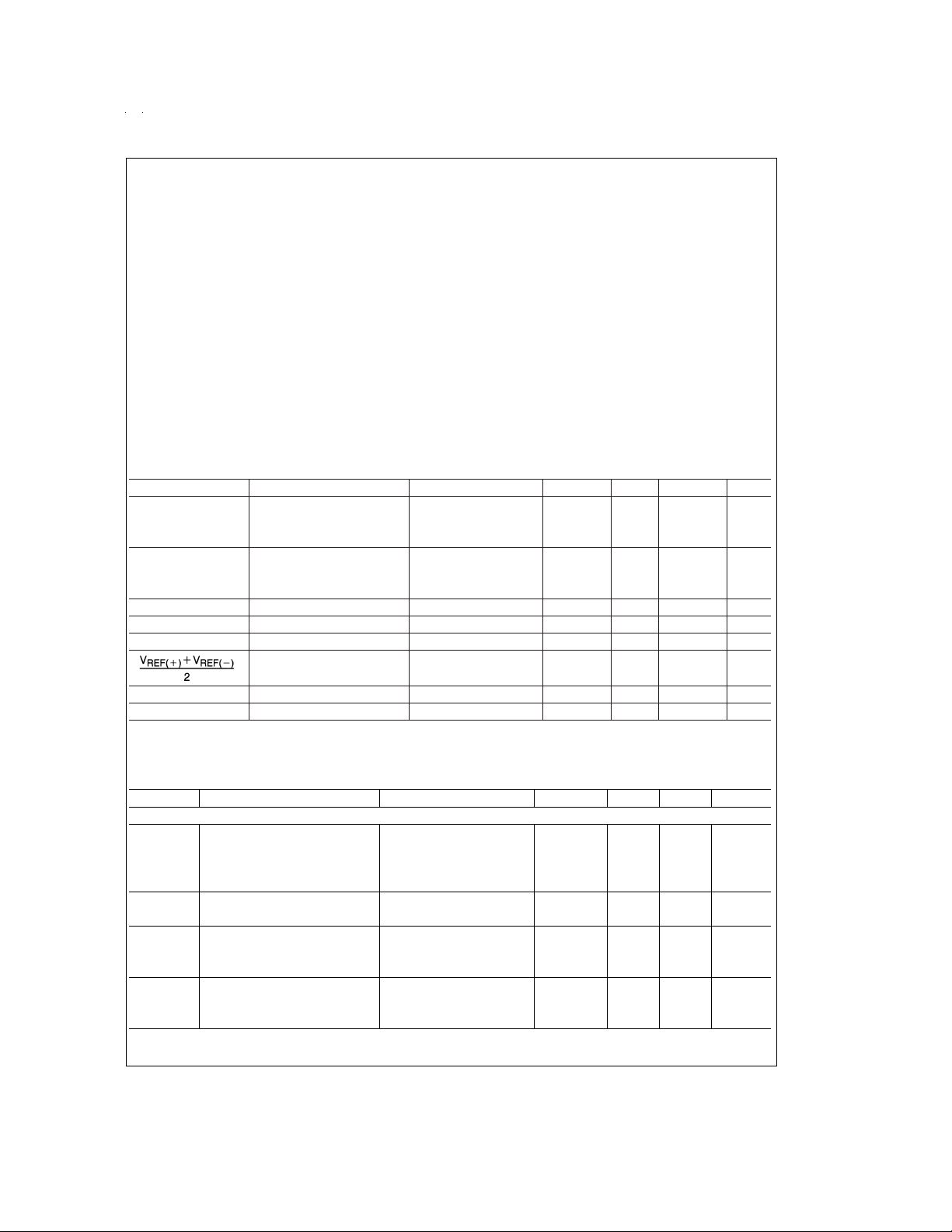

Electrical Characteristics

=

Converter Specifications: V

otherwise stated.

CC

5V

=

DC

V

REF(+),VREF(−)

Symbol Parameter Conditions Min Typ Max Units

ADC0816

Total Unadjusted Error 25˚C

(Note 5) T

ADC0817

Total Unadjusted Error 0˚C to 70˚C

(Note 5) T

Input Resistance From Ref(+) to Ref(−) 1.0 4.5 kΩ

Analog Input Voltage Range (Note 4) V(+) or V(−) GND−0.10 V

V

REF(+)

Voltage, Top of Ladder Measured at Ref(+) V

Voltage, Center of Ladder VCC/2−0.1 VCC/2 VCC/2+0.1 V

=

GND, V

MIN

MIN

=

V

IN

COMPARATOR IN,TMIN≤TMAX

to T

MAX

to T

MAX

and f

CLK

CC

=

640 kHz unless

±

CC

VCC+0.1 V

MIN≤TA≤TMAX

1

±

⁄

2

3

±

⁄

4

±

1 LSB

11⁄

4

+0.10 V

DC

CC

LSB

LSB

LSB

DC

V

REF(−)

Voltage, Bottom of Ladder Measured at Ref(−) −0.1 0 V

Comparator Input Current f

=

640 kHz, (Note 6) −2

c

±

0.5 2 µA

Electrical Characteristics

Digital Levels and DC Specifications: ADC0816CCN, ADC0817CCN— 4.75V≤VCC≤5.25V, −40˚C≤TA≤+85˚C unless other-

wise noted.

Symbol Parameter Conditions Min Typ Max Units

ANALOG MULTIPLEXER

R

∆R

I

OFF+

I

OFF(−)

ON

ON

Analog Multiplexer ON (Any Selected Channel)

Resistance T

=

A

=

T

A

=

T

A

=

25˚C, R

10k 1.5 3 kΩ

L

85˚C 6 kΩ

125˚C 9 kΩ

∆ON Resistance Between Any (Any Selected Channel) 75 Ω

2 Channels R

OFF Channel Leakage Current V

OFF Channel Leakage Current V

=

10k

L

=

=

5V, V

to T

5V, V

to T

MAX

Max

5V,

IN

1.0 µA

=

0,

IN

−1.0 µA

CC

=

T

25˚C 10 200 nA

A

T

MIN

=

CC

=

T

25˚C −200 nA

A

T

MIN

www.national.com3

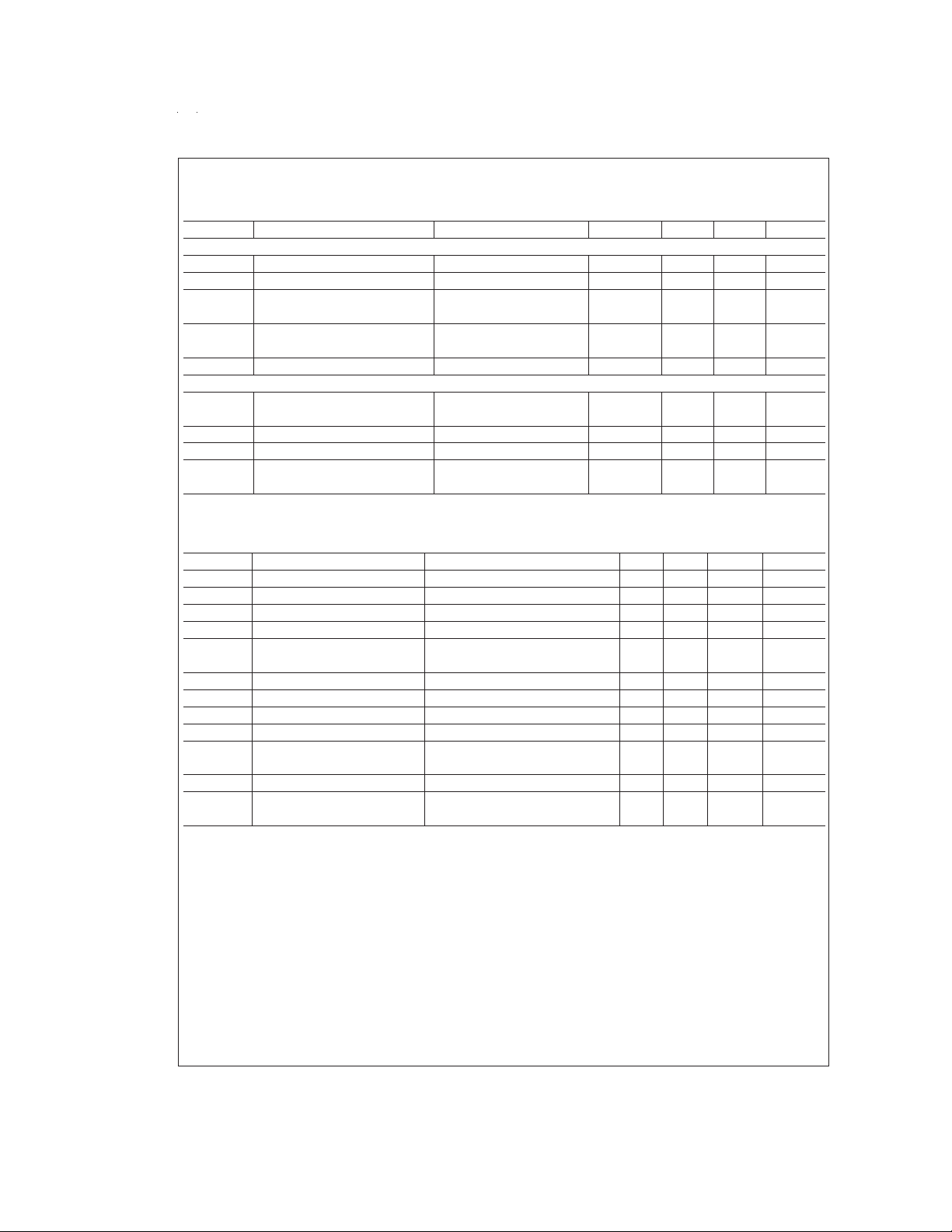

Electrical Characteristics (Continued)

Digital Levels and DC Specifications: ADC0816CCN, ADC0817CCN— 4.75V≤VCC≤5.25V, −40˚C≤TA≤+85˚C unless other-

wise noted.

Symbol Parameter Conditions Min Typ Max Units

CONTROL INPUTS

V

IN(1)

V

IN(0)

I

IN(1)

I

IN(0)

I

CC

DATA OUTPUTS AND EOC (INTERRUPT)

V

OUT(1)

V

OUT(0)

V

OUT(0)

I

OUT

Logical “1” Input Voltage VCC−1.5 V

Logical “0” Input Voltage 1.5 V

Logical “1” Input Current V

=

15V 1.0 µA

IN

(The Control Inputs)

Logical “0” Input Current V

=

0 −1.0 µA

IN

(The Control Inputs)

Supply Current f

Logical “1” Output Voltage I

Logical “0” Output Voltage I

Logical “0” Output Voltage EOC I

TRI-STATE Output Current V

=

640 kHz 0.3 3.0 mA

CLK

=

−360 µA, T

O

=

I

−300 µA, T

O

=

1.6 mA 0.45 V

O

=

1.2 mA 0.45 V

O

=

V

O

CC

=

V

0 −3.0 µA

O

=

85˚C V

A

=

125˚C

A

−0.4 V

CC

3.0 µA

Electrical Characteristics

=

Timing Specifications: V

CC

V

REF(+)

=

5V, V

Symbol Parameter Conditions Min Typ Max Units

t

WS

t

WALE

t

s

T

H

t

D

Minimum Start Pulse Width (

Minimum ALE Pulse Width (

Minimum Address Set-Up Time (

Minimum Address Hold Time (

Analog MUX Delay Time R

from ALE

t

H1,tH0

t

1H,t0H

t

C

f

c

t

EOC

C

IN

C

OUT

OE Control to Q Logic State C

OE Control to Hi-Z C

Conversion Time f

Clock Frequency 10 640 1280 kHz

EOC Delay Time (

Input Capacitance At Control Inputs 10 15 pF

TRI-STATE Output At TRI-STATE Outputs (Note 8) 10 15 pF

Capacitance

Note 1: AbsoluteMaximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating

the device beyond its specified operating conditions.

Note 2: All voltages are measured with respect to GND, unless otherwise specified.

Note 3: Azener diode exists, internally, from V

Note 4: Two on-chip diodes are tied to each analog input which will forward conduct for analog input voltages one diode drop below ground or one diode drop greater

than the V

than 100 mV, the output code will be correct. To achieve an absolute 0 V

V

Note 5: Total unadjusted error includes offset, full-scale, and linearity errors. See

all zero code is desired for an analog input other than 0.0V, or if a narrow full-scale span exists (for example: 0.5V to 4.5V full-scale) the reference voltages can be

adjusted to achieve this. See

Note 6: Comparatorinput current is a bias current into or out of the chopper stabilized comparator.The bias current varies directly with clock frequency and has little

temperature dependence (

Note 7: Ifstart pulse is asynchronous with converter clock or if f

at f

Note 8: The outputs of the data register are updated one clock cycle before the rising edge of EOC.

Note 9: Human body model, 100 pF discharged through a 1.5 kΩ resistor.

supply.The spec allows 100 mV forward bias of either diode. This means that as long as the analog VINdoes not exceed the supply voltage by more

CC

over temperature variations, initial tolerance and loading.

DC

Figure 13

Figure 6

). See paragraph 4.0.

≤ 640 kHz take start high within 100 ns of clock going low.

c

to GND and has a typical breakdown voltage of 7 VDC.

CC

.

=

=

REF(−)

GND, t

Figure 5

Figure 5

Figure 5

Figure 5

=

S

=

L

=

L

=

640 kHz, (

c

Figure 5

>

c

=

t

20 ns and T

r

f

) (Note 7) 100 200 ns

) 100 200 ns

)2550ns

)2550ns

Figure 5

OΩ (

50 pF, R

10 pF, R

) 1 2.5 µs

=

10k (

L

=

10k (

L

Figure 5

) 0 8+2µs Clock

to5VDCinput voltage range will therefore require a minimum supply voltage of 4.900

DC

Figure 3

640 kHz, the minimum start pulse width is 8 clock periods plus 2 µs. For synchronous operation

=

25˚C unless otherwise noted.

A

Figure 8

) 125 250 ns

Figure 8

) 125 250 ns

) (Note 8) 90 100 116 µs

. None of these A/Ds requires a zero or full-scale adjust. However, if an

Periods

www.national.com 4

Loading...

Loading...