54ABT16373

16-Bit Transparent Latch with TRI-STATE

®

Outputs

54ABT16373 16-Bit Transparent Latch with TRI-STATE Outputs

July 1998

General Description

The ABT16373 contains sixteen non-inverting latches with

TRI-STATE outputs and is intended for bus oriented applications. The device is byte controlled. The flip-flops appear

transparent to the data when the Latch Enable (LE) is HIGH.

When LE is low, the data that meets the setup time is

latched. Data appears on the bus when the Output Enable

(OE) is LOW. When OE is HIGH, the outputs are in high Z

state.

Features

n Separate control logic for each byte

n 16-bit version of the ABT373

n High impedance glitch free bus loading during entire

n Non-destructive hot insertion capability

n Guaranteed latch-up protection

n Standard Microcircuit Drawing (SMD) 5962-9320001

Ordering Code:

Military Package Package Description

Number

54ABT16373W-QML WA48A 48-Lead Cerpack

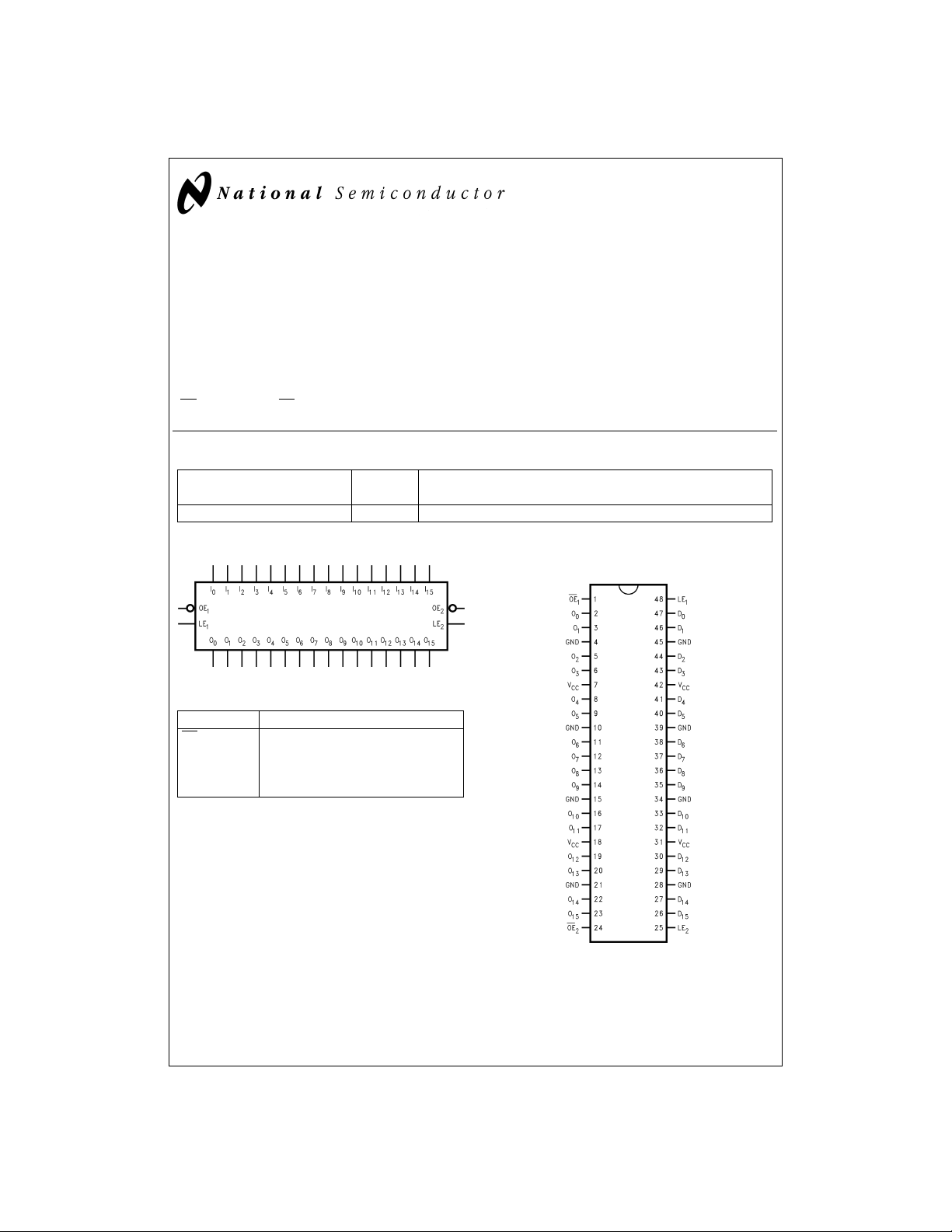

Logic Symbol

DS100201-1

Connection Diagram

Pin Description

Pin Names Description

OE

LE

D

0–D15

O

n

n

0–O15

Output Enable Input (Active Low)

Latch Enable Input

Data Inputs

Outputs

power up and power down cycle

Pin Assignment for Cerpack

DS100201-2

TRI-STATE®is a registered trademark of NationalSemiconductor Corporation.

© 1998 National Semiconductor Corporation DS100201 www.national.com

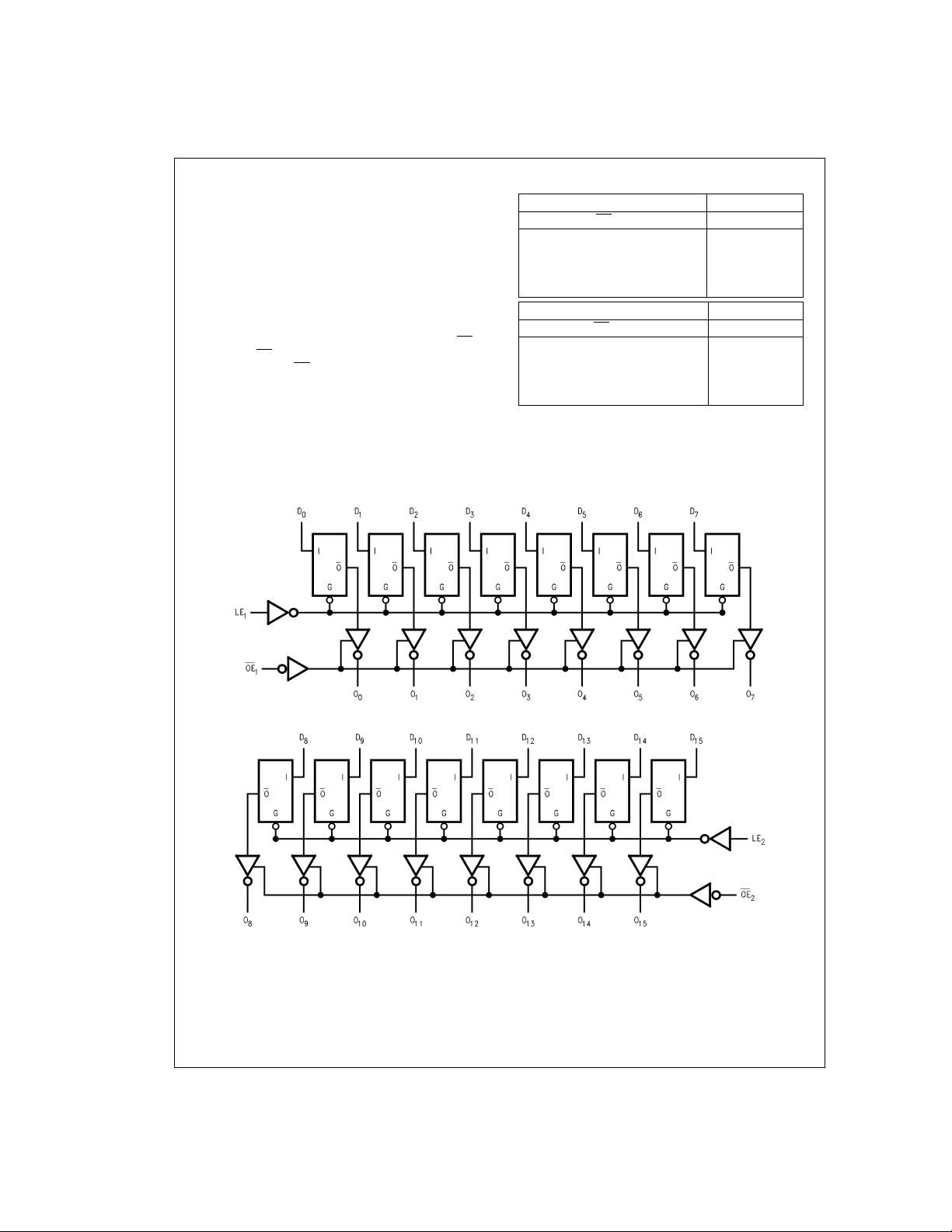

Functional Description

The ABT16373 contains sixteen D-type latches with

TRI-STATE standard outputs. The device is byte controlled

with each byte functioning identically, but independent of the

other. Control pins can be shorted together to obtain full

16-bit operation. The following description applies to each

byte. When the Latch Enable (LE

the D

enters the latches. In this condition the latches are

n

transparent, i.e., a latch output will change states each time

its D input changes. When LE

formation that was present on the D inputs a setup time preceding the HIGH-to-LOW transition of LE

standard outputs are controlled by the Output Enable (OE

) input is HIGH, data on

n

is LOW, the latches store in-

n

. The TRI-STATE

n

input. When OEnis LOW, the standard outputs are in the

2-state mode. When OEnis HIGH, the standard outputs are

in the high impedance mode but this does not interfere with

entering new data into the latches.

Logic Diagrams

Truth Tables

Inputs Outputs

LE

XH X Z

HL L L

HL H H

L L X (Previous)

LE

)

n

XH X Z

HL L L

HL H H

L L X (Previous)

H=High Voltage Level

L=Low Voltage Level

X=Immaterial

Z=High Impedance

Previous=previous output prior to HIGH to LOW transition of LE

OE

1

D0–D

1

Inputs Outputs

OE

2

D8–D

2

7

15

O0–O

O8–O

7

15

www.national.com 2

DS100201-3

DS100201-4

Loading...

Loading...