查询54165供应商

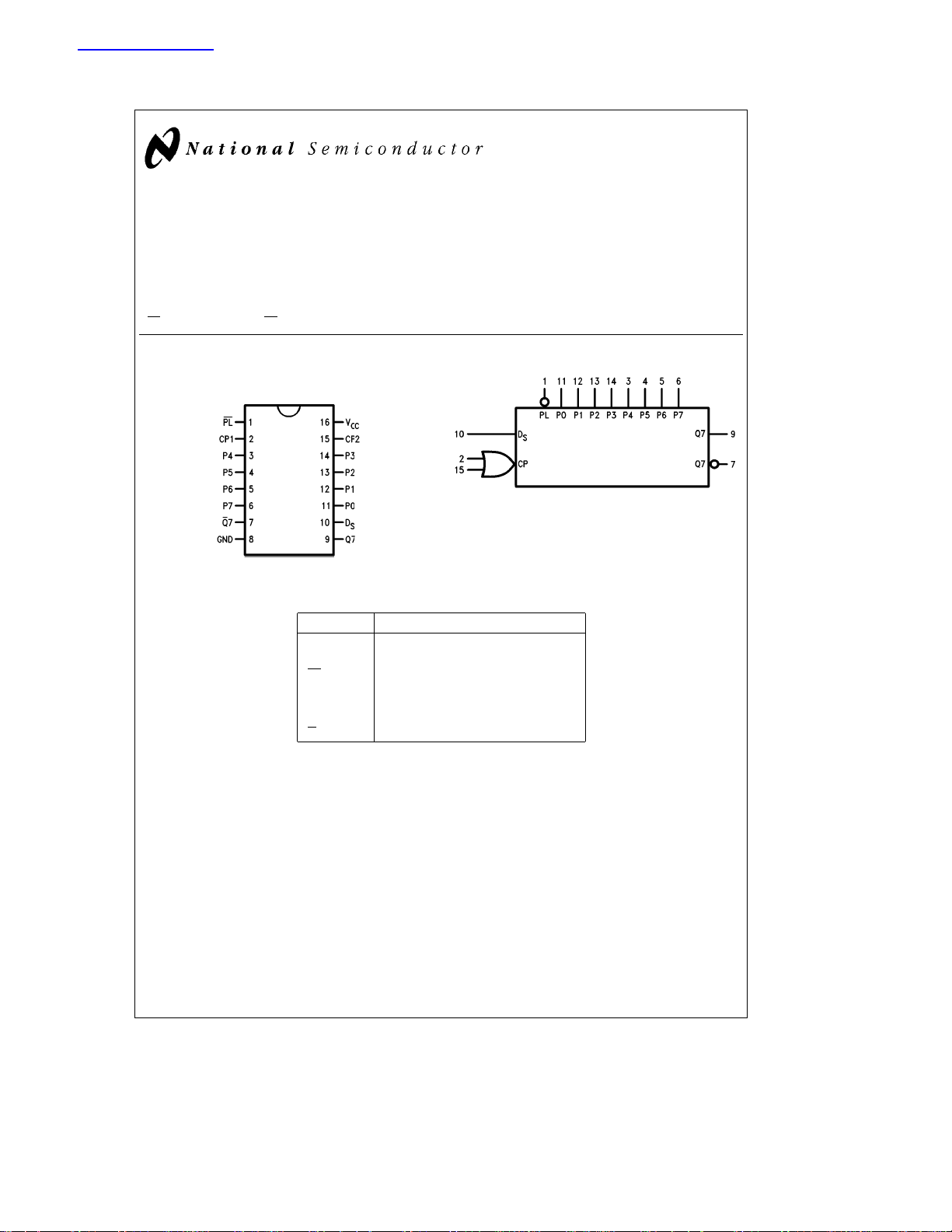

54165/DM74165

8-Bit Parallel-to-Serial Converter

General Description

The ’165 is an 8-bit parallel load or serial-in register with

complementary outputs available from the last stage. Parallel inputting occurs asynchronously when the Parallel Load

(PL

) input is LOW. With PL HIGH, serial shifting occurs on

August 1989

the rising edge of the clock; new data enters via the Serial

Data (D

) input. The 2-input OR clock can be used to com-

S

bine two independent clock sources, or one input can act as

an active LOW clock enable.

54165/DM74165 8-Bit Parallel-to-Serial Converter

Connection Diagram

Dual-In-Line-Package

Order Number 54165DMQB, 54165FMQB or DM74165N

See NS Package Number J16A, N16E or W16A

Pin Names Description

CP1, CP2 Clock Pulse Inputs (Active Rising Edge)

D

S

PL

P0–P7 Parallel Data Inputs

Q7 Serial Output from Last Stage

Q7 Complementary Output

TL/F/9782– 1

Serial Data Input

Asynchronous Parallel Load Input

(Active LOW)

Logic Symbol

V

CC

GND

e

e

Pin 16

Pin 8

TL/F/9782– 2

C

1995 National Semiconductor Corporation RRD-B30M115/Printed in U. S. A.

TL/F/9782

Absolute Maximum Ratings (Note)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales

Office/Distributors for availability and specifications.

Supply Voltage 7V

Input Voltage 5.5V

Operating Free Air Temperature Range

54

DM74 0

Storage Temperature Range

b

55§Ctoa125§C

Ctoa70§C

§

b

65§Ctoa150§C

Note:

The ‘‘Absolute Maximum Ratings’’ are those values

beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The

parametric values defined in the ‘‘Electrical Characteristics’’

table are not guaranteed at the absolute maximum ratings.

The ‘‘Recommended Operating Conditions’’ table will define

the conditions for actual device operation.

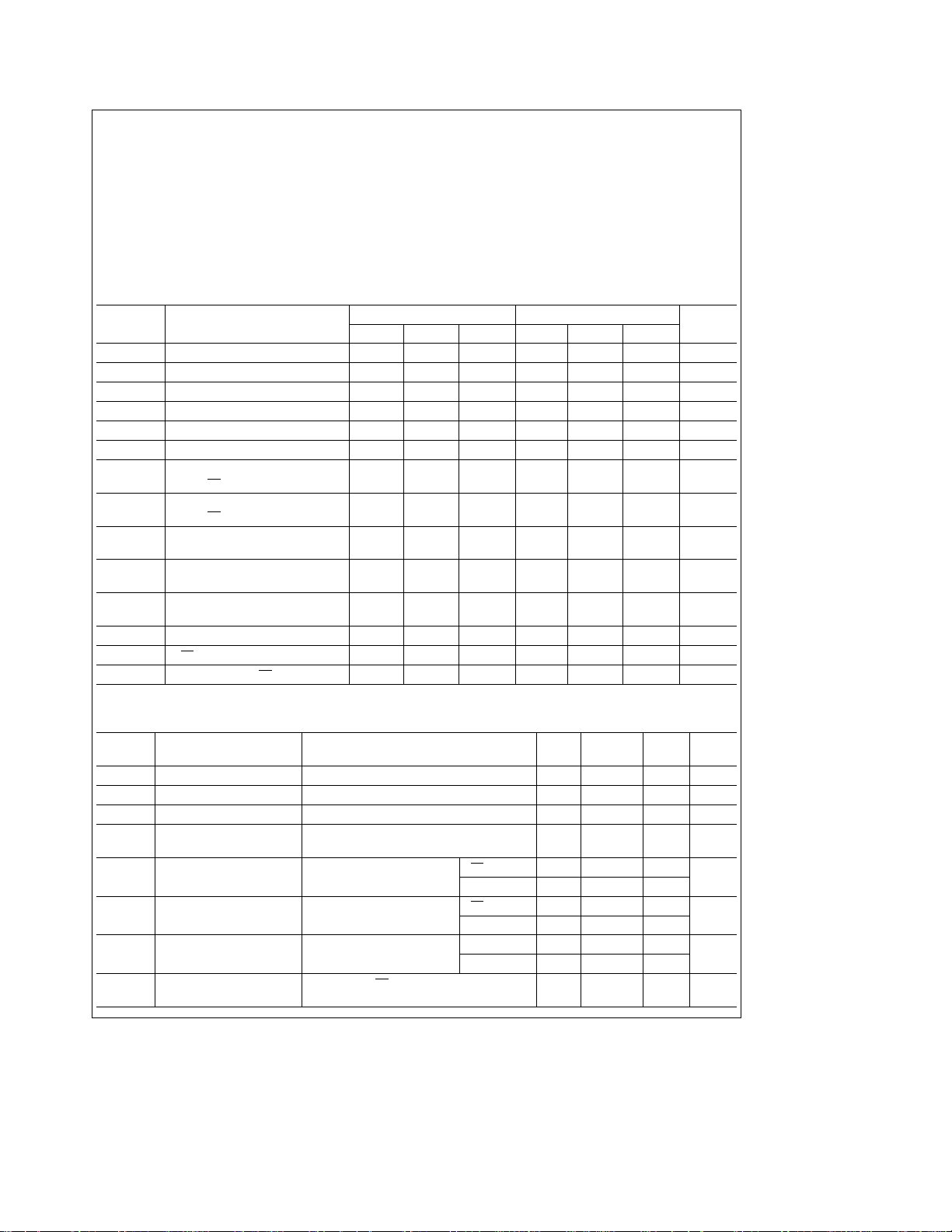

Recommended Operating Conditions

Symbol Parameter

V

CC

V

IH

V

IL

I

OH

I

OL

T

A

Supply Voltage 4.5 5 5.5 4.75 5 5.25 V

High Level Input Voltage 2 2 V

Low Level Input Voltage 0.8 0.8 V

High Level Output Current

Low Level Output Current 16 16 mA

Free Air Operating Temperature

Min Nom Max Min Nom Max

b

ts(H) Setup Time HIGH or LOW 10 10

(L) Pnto PL 10 10

t

s

th(H) Hold Time HIGH or LOW 10 0

(L) Pnto PL 10 0

t

h

ts(H) Setup Time HIGH or LOW 20 20

ts(L) DSto CP

n

20 20

th(H) Hold Time HIGH or LOW 0 0

(L) DSto CP

t

h

t

(H) Setup Time HIGH

s

n

CP1 to CP2 or CP2 to CP1

30 30 ns

tw(H) CPnPulse Width HIGH 25 25 ns

tw(L) PL Pulse Width LOW 15 15 ns

t

rec

Recovery Time, PL to CP

n

45 45 ns

54165 DM74165

b

0.8

b

0.8 mA

55 125 0 70

00

Units

C

§

ns

ns

ns

ns

Electrical Characteristics

Over recommended operating free air temperature range (unless otherwise noted)

Symbol Parameter Conditions Min

eb

V

I

V

OH

V

OL

I

I

I

IH

I

IL

I

OS

I

CC

Input Clamp Voltage V

High Level Output Voltage V

Low Level Output Voltage V

Input Current@Max V

Input Voltage

High Level Input Current V

Low Level Input Current V

Short Circuit V

Output Current (Note 2)

Supply Current V

e

Min, I

CC

CC

CC

CC

CC

CC

CC

CC

P

n

I

e

e

e

e

e

e

e

e

K,CP1,CP

e

Min, I

OH

e

Min, V

IH

e

Max, V

I

e

Max, V

I

e

Max, V

I

Max 54

e

Max, PL

12 mA

e

Max, V

Max 2.4 3.4 V

IL

Min 0.2 0.4 V

5.5V

2.4V PL 80

Inputs 40

0.4V PL

Inputs

b

DM74

b

ß

e

4.5V

2

2

Typ

(Note 1)

Max Units

b

1.5 V

1mA

mA

b

3.2

1.6

55

55

mA

mA

b

20

18

b

b

63 mA

Switching Characteristics

ea

V

CC

Symbol Parameter R

5.0V, T

ea

25§C (See Section 1 for waveforms and load configurations)

A

e

C

15 pF

L

e

400X Units

L

Min Max

f

max

t

PLH

t

PHL

t

PLH

t

PHL

t

PLH

t

PHL

t

PLH

t

PHL

Note 1: All typicals are at V

Note 2: Not more than one output should be shorted at a time.

Maximum Clock Frequency 20 MHz

Propagation Delay 31

PL to Q7 or Q740

Propagation Delay 24

CP1 to Q7 or Q731

Propagation Delay 17

P7 to Q7 36

Propagation Delay 27

P7 to Q727

e

e

5V, T

CC

25§C.

A

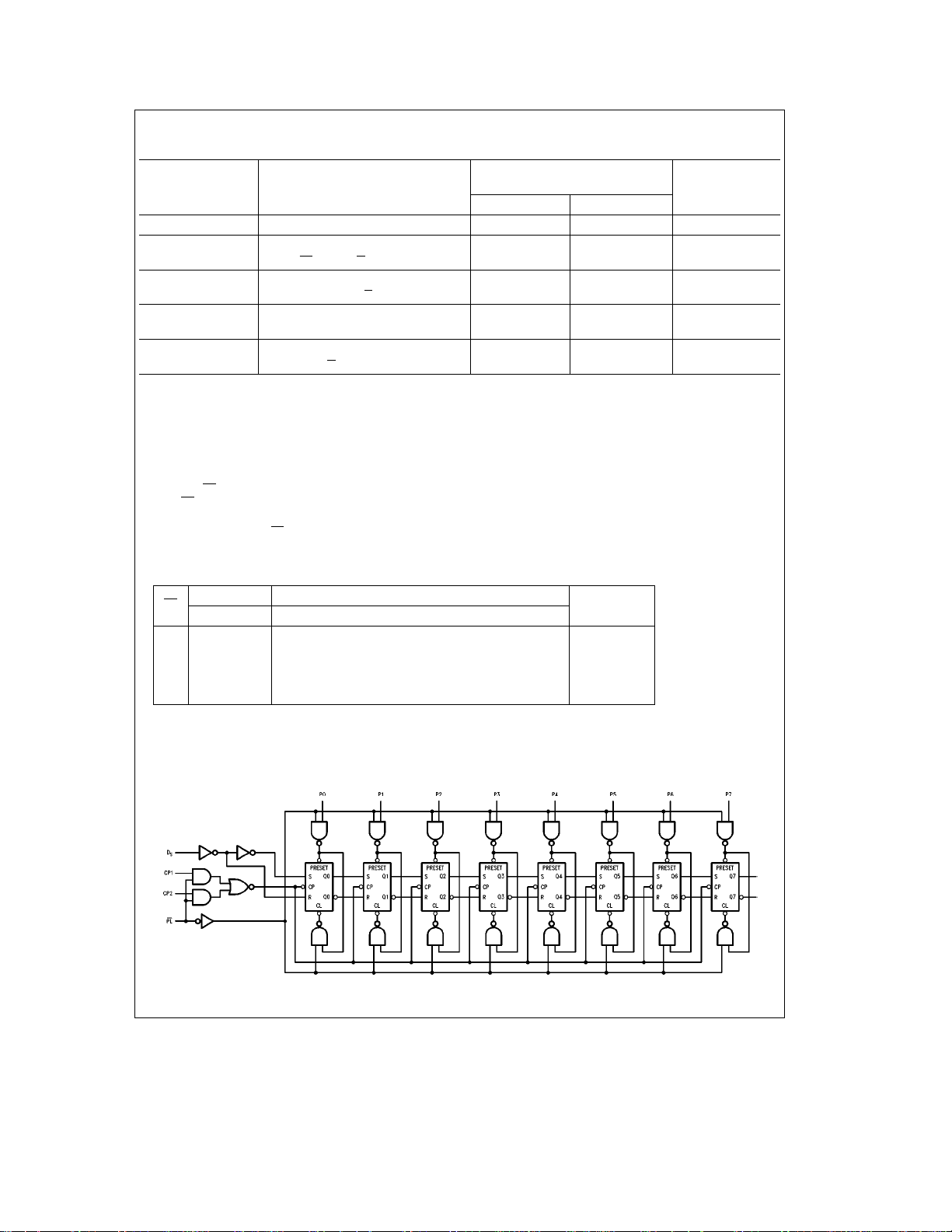

Functional Description

The ’165 contains eight clocked master/slave RS flip-flops

connected as a shift register with auxiliary gating to provide

overriding asynchronous parallel entry. Parallel data enters

when the PL

while PL

signal is LOW. The parallel data can change

is LOW provided that the recommended setup and

hold times are observed.

For clocked operation, PL

must be HIGH. The two clock

inputs perform identically; one can be used as a clock inhibit

by applying a HIGH signal. To avoid double clocking, however, the inhibit signal should only go HIGH while the clock

is HIGH. Otherwise, the rising inhibit signal will cause the

same response as a rising clock edge. The flip-flops are

edge-triggered for serial operations. The serial input data

can change at any time, provided only that the recommended setup and hold times are observed, with respect to the

rising edge of the clock.

Truth Table

PL

CP Contents

1 2 Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

L X X P0 P1 P2 P3 P4 P5 P6 P7 Parallel Entry

HLLD

HHLQ0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 No Change

H L LD

H L H Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 No Change

HeHIGH Voltage Level

e

LOW Voltage Level

L

e

Immaterial

X

e

Positive Rising Edge

L

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Right Shift

S

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Right Shift

S

Response

ns

ns

ns

ns

Logic Diagram

TL/F/9782– 3

3

Loading...

Loading...