Page 1

DAQ

NI 6115/6120 User Manual

Multifunction I/O Devices for

PCI/PXI/CompactPCI Bus Computers

NI 6115/6120 User Manual

August 2002 Edition

Part Number 322812B-01

Page 2

Support

Worldwide Technical Support and Product Information

ni.com

National Instruments Corporate Headquarters

11500 North Mopac Expressway Austin, Texas 78759-3504 USA Tel: 512 683 0100

Worldwide Offices

Australia 03 9879 5166, Austria 0662 45 79 90 0, Belgium 02 757 00 20, Brazil 55 11 3262 3599,

Canada (Calgary) 403 274 9391, Canada (Montreal) 514 288 5722, Canada (Ottawa) 613 233 5949,

Canada (Québec) 514 694 8521, Canada (Toronto) 905 785 0085, China 86 21 6555 7838,

Czech Republic 02 2423 5774, Denmark 45 76 26 00, Finland 09 725 725 11, France 01 48 14 24 24,

Germany 089 741 31 30, Greece 01 42 96 427, Hong Kong 2645 3186, India 91 80 4190000,

Israel 03 6393737, Italy 02 413091, Japan 03 5472 2970, Korea 02 3451 3400, Malaysia 603 9596711,

Mexico 001 800 010 0793, Netherlands 0348 433466, New Zealand 09 914 0488, Norway 32 27 73 00,

Poland 22 3390 150, Portugal 210 311 210, Russia 095 238 7139, Singapore 65 6 226 5886,

Slovenia 3 425 4200, South Africa 11 805 8197, Spain 91 640 0085, Sweden 08 587 895 00,

Switzerland 056 200 51 51, Taiwan 02 2528 7227, United Kingdom 01635 523545

For further support information, see the Technical Support and Professional Services appendix. To comment on

the documentation, send email to techpubs@ni.com.

© 2001–2002 National Instruments Corporation. All rights reserved.

Page 3

Important Information

Warranty

The NI PCI-6115, NI PXI-6115, NI PCI-6120, and NI PXI-6120 devices are warranted against defects in materials and workmanship for a

period of one year from the date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair

or replace equipment that proves to be defective during the warranty period. This warranty includes parts and labor.

The media on which you receive National Instruments software are warranted not to fail to execute programming instructions, due to defects

in materials and workmanship, for a period of 90 days from date of shipment, as evidenced by receipts or other documentation. National

Instruments will, at its option, repair or replace software media that do not execute programming instructions if National Instruments receives

notice of such defects during the warranty period. National Instruments does not warrant that the operation of the software shall be

uninterrupted or error free.

A Return Material Authorization (RMA) number must be obtained from the factory and clearly marked on the outside of the package before

any equipment will be accepted for warranty work. National Instruments will pay the shipping costs of returning to the owner parts which are

covered by warranty.

National Instruments believes that the information in this document is accurate. The document has been carefully reviewed for technical

accuracy. In the event that technical or typographical errors exist, National Instruments reserves the right to make changes to subsequent

editions of this document without prior notice to holders of this edition. The reader should consult National Instruments if errors are suspected.

In no event shall National Instruments be liable for any damages arising out of or related to this document or the information contained in it.

E

XCEPT AS SPECIFIED HEREIN, NATIONAL INSTRUMENTS MAKES NO WARRANTIES, EXPRESS OR IMPLIED, AND SPECIFICALLY DISCLAIMS ANY WARRANTY OF

MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. CUSTOMER’S RIGHT TO RECOVER DAMAGES CAUSED BY FAULT OR NEGLIGENCE ON THE PART OF

N

ATIONAL INSTRUMENTS SHALL BE LIMITED TO THE AMOUNT THERETOFORE PAID BY THE CUSTO MER. NATIONAL INSTRUMENTS WILL NOT BE LIA BLE FOR

DAMAGES RESULTIN G FROM LOSS OF DATA, PROFITS, USE OF PRODUCTS, OR INCIDENTAL OR CONSEQUENTIAL DAMAGES, EVEN IF ADVISED OF THE POSSIBILITY

THEREOF. This limitation of the liability of National Instruments will apply regardless of the form of action, whether in contract or tort, including

negligence. Any action against National Instruments must be brought within one year after the cause of action accrues. National Instruments

shall not be liable for any delay in performance due to causes beyond its reasonable control. The warranty provided herein does not cover

damages, defects, malfunctions, or service failures caused by owner’s failure to follow the National Instruments installation, operation, or

maintenance instructions; owner’s modification of the product; owner’s abuse, misuse, or negligent acts; and power failure or surges, fire,

flood, accident, actions of third parties, or other events outside reasonable control.

Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying,

recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National

Instruments Corporation.

Trademarks

CVI™, DAQ-STC™, LabVIEW™, Measurement Studio™, MITE™, MXI™, National Instruments™, NI™, ni.com™, NI-DAQ™, NI Developer

™

, and RTSI™ are trademarks of National Instruments Corporation.

Zone

Product and company names mentioned herein are trademarks or trade names of their respective companies.

Patents

For patents covering National Instruments products, refer to the appropriate location: Help»Patents in your software, the patents.txt file

on your CD, or

ni.com/paten ts.

WARNING REGARDING USE OF NATIONAL INSTRUMENTS PRODUCTS

(1) NATIONAL INSTRUMENTS PRODUCTS ARE NOT DESIGNED WITH COMPONENTS AND TESTING FOR A LEVEL OF

RELIABILITY SUITABLE FOR USE IN OR IN CONNECTION WITH SURGICAL IMPLANTS OR AS CRITICAL COMPONENT S IN

ANY LIFE SUPPORT SYSTEMS WHOSE FAILURE TO PERFORM CAN REASONABLY BE EXPECTED TO CAUSE SIGNIFICANT

INJURY TO A HUMAN.

(2) IN ANY APPLICATION, INCLUDING THE ABOVE, RELIABILITY OF OPERATION OF THE SOFTWARE PRODUCTS CAN BE

IMPAIRED BY ADVERSE FACTORS, INCLUDING BUT NOT LIMITED TO FLUCTUATIONS IN ELECTRICAL POWER SUPPLY,

COMPUTER HARDWARE MALFUNCTIONS, COMPUTER OPERATING SYSTEM SOFTWARE FIT NESS, FITNESS OF COMPILERS

AND DEVELOPMENT SOFTWARE USED TO DEVELOP AN APPLICATION, INSTALLATION ERRORS, SOFTWARE AND

HARDWARE COMPATIBILITY PROBLEMS, MALFUNCTIONS OR FAILURES OF ELECTRONIC MONITORING OR CONTROL

DEVICES, TRANSIENT FAILURES OF ELECTRONIC SYSTEMS (HARDWARE AND/OR SOFTWARE), UNANTICIPATED USES OR

MISUSES, OR ERRORS ON THE PART OF THE USER OR APPLICATIONS DESIGNER (ADVERSE FACTORS SUCH AS THESE ARE

HEREAFTER COLLECTIVELY TERMED “SYSTEM FAILURES”). ANY APPLICATION WHERE A SYSTEM FAILURE WOULD

CREATE A RISK OF HARM TO PROPERTY OR PERSONS (INCLUDING THE RISK OF BODILY INJURY AND DEATH) SHOULD

NOT BE RELIANT SOLELY UPON ONE FORM OF ELECTRONIC SYSTEM DUE TO THE RISK OF SYSTEM FAILURE. TO AVOID

DAMAGE, INJURY, OR DEATH, THE USER OR APPLICATION DESIGNER MUST TAKE REASONABLY PRUDENT STEPS TO

PROTECT AGAINST SYSTEM FAILURES, INCLUDING BUT NOT LIMITED TO BACK-UP OR SHUT DOWN MECHANISMS.

BECAUSE EACH END-USER SYSTEM IS CUSTOMIZED AND DIFFERS FROM NATIONAL INSTRUMENTS' TESTING

PLATFORMS AND BECAUSE A USER OR APPLICATION DESIGNER MAY USE NATIONAL INSTRUMENTS PRODUCTS IN

COMBINATION WITH OTHER PRODUCTS IN A MANNER NOT EVALUATED OR CONTEMPLATED BY NATIONAL

INSTRUMENTS, THE USER OR APPLICATION DESIGNER IS ULTIMATELY RESPONSIBLE FOR VERIFYING AND VALIDATING

THE SUITABILITY OF NATIONAL INSTRUMENTS PRODUCTS WHENEVER NATIONAL INSTRUMENTS PRODUCTS ARE

INCORPORATED IN A SYSTEM OR APPLICATION, INCLUDING, WITHOUT LIMITATION, THE APPROPRIATE DESIGN,

PROCESS AND SAFETY LEVEL OF SUCH SYSTEM OR APPLICATION.

Page 4

Compliance

FCC/Canada Radio Frequency Interference Compliance

Determining FCC Class

The Federal Communications Commission (FCC) has rules to protect wireless communications from interference. The FCC

places digital electronics into two classes. These classes are known as Class A (for use in industrial-commercial locations only)

or Class B (for use in residential or commercial locations). Depending on where it is operated, this product could be subject to

restrictions in the FCC rules. (In Canada, the Department of Communications (DOC), of Industry Canada, regulates wireless

interference in much the same way.)

Digital electronics emit weak signals during normal operation that can affect radio, television, or other wireless products. By

examining the product you purchased, you can determine the FCC Class and therefore which of the two FCC/DOC Warnings

apply in the following sections. (Some products may not be labeled at all for FCC; if so, the reader should then assume these are

Class A devices.)

FCC Class A products only display a simple warning statement of one paragraph in length regarding interference and undesired

operation. Most of our products are FCC Class A. The FCC rules have restrictions regarding the locations where FCC Class A

products can be operated.

FCC Class B products display either a FCC ID code, starting with the letters EXN,

or the FCC Class B compliance mark that appears as shown here on the right.

Consult the FCC Web site at

FCC/DOC Warnings

This equipment generates and uses radio frequency energy and, if not installed and used in strict accordance with the instructions

in this manual and the CE Mark Declaration of Conformity*, may cause interference to radio and television reception.

Classification requirements are the same for the Federal Communications Commission (FCC) and the Canadian Department

of Communications (DOC).

Changes or modifications not expressly approved by National Instruments could void the user’s authority to operate the

equipment under the FCC Rules.

http://www.fcc.gov for more information.

Class A

Federal Communications Commission

This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to part 15 of the FCC

Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated

in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and

used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this

equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct

the interference at his own expense.

Canadian Department of Communications

This Class A digital apparatus meets all requirements of the Canadian Interference-Causing Equipment Regulations.

Cet appareil numérique de la classe A respecte toutes les exigences du Règlement sur le matériel brouilleur du Canada.

Class B

Federal Communications Commission

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the

FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation.

This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the

instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not

occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can

be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of

the following measures:

• Reorient or relocate the receiving antenna.

• Increase the separation between the equipment and receiver.

• Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

• Consult the dealer or an experienced radio/TV technician for help.

Page 5

Canadian Department of Communications

This Class B digital apparatus meets all requirements of the Canadian Interference-Causing Equipment Regulations.

Cet appareil numérique de la classe B respecte toutes les exigences du Règlement sur le matériel brouilleur du Canada.

Compliance to EU Directives

Readers in the European Union (EU) must refer to the Manufacturer’s Declaration of Conformity (DoC) for information*

pertaining to the CE Mark compliance scheme. The Manufacturer includes a DoC for most every hardware product except for

those bought for OEMs, if also available from an original manufacturer that also markets in the EU, or where compliance is not

required as for electrically benign apparatus or cables.

To obtain the DoC for this product, click Declaration of Conformity at

by product family. Select the appropriate product family, followed by your product, and a link to the DoC appears in Adobe

Acrobat format. Click the Acrobat icon to download or read the DoC.

* The CE Mark Declaration of Conformity will contain important supplementary information and instructions for the user or

installer.

ni.com/hardref.nsf/. This Web site lists the DoCs

Page 6

Contents

About This Manual

Conventions ...................................................................................................................xi

National Instruments Documentation ............................................................................xii

Related Documentation..................................................................................................xiii

Chapter 1

Introduction

About the NI 6115/6120 ...............................................................................................1-1

Using PXI with CompactPCI.........................................................................................1-2

What You Need to Get Started ......................................................................................1-3

Software Programming Choices ....................................................................................1-4

NI-DAQ...........................................................................................................1-4

National Instruments ADE Software...............................................................1-5

Optional Equipment.......................................................................................................1-6

Custom Cabling .............................................................................................................1-6

Unpacking......................................................................................................................1-7

Safety Information .........................................................................................................1-8

Chapter 2

Installing and Configuring the NI 6115/6120

Installing the Software ...................................................................................................2-1

Installing the Hardware..................................................................................................2-1

Configuring the Device..................................................................................................2-3

Chapter 3

Hardware Overview

Analog Input ..................................................................................................................3-2

Input Mode ......................................................................................................3-2

Input Polarity and Input Range........................................................................3-3

Considerations for Selecting Input Ranges.......................................3-4

Input Coupling.................................................................................................3-4

Analog Output................................................................................................................3-5

Analog Trigger...............................................................................................................3-5

Antialiasing Filters.........................................................................................................3-8

Phase-Locked Loop Circuit ...........................................................................................3-9

Correlated Digital I/O ....................................................................................................3-10

© National Instruments Corporation vii NI 6115/6120 User Manual

Page 7

Contents

Timing Signal Routing .................................................................................................. 3-10

Programmable Function Inputs....................................................................... 3-12

Device and RTSI Clocks................................................................................. 3-12

RTSI Triggers ................................................................................................. 3-12

Chapter 4

Connecting Signals

I/O Connector ................................................................................................................ 4-1

I/O Connector Signal Descriptions .................................................................4-3

Types of Signal Sources................................................................................................ 4-7

Floating Signal Sources .................................................................................. 4-7

Ground-Referenced Signal Sources................................................................ 4-8

Connecting Analog Input Signals.................................................................................. 4-8

Connections for Ground-Referenced Signal Sources ..................................... 4-9

Connections for Nonreferenced or Floating Signal Sources........................... 4-11

Common-Mode Signal Rejection Considerations........................................... 4-12

Working Voltage Range................................................................................................ 4-13

Connecting Analog Output Signals............................................................................... 4-14

Connecting Digital I/O Signals ..................................................................................... 4-15

Correlating DIO Signal Connections............................................................................. 4-16

Power Connections........................................................................................................4-18

Connecting Timing Signals ........................................................................................... 4-18

Programmable Function Input Connections ................................................... 4-20

DAQ Timing Connections .............................................................................. 4-20

Waveform Generation Timing Connections................................................... 4-29

General-Purpose Timing Signal Connections................................................. 4-32

TRIG1 Signal.................................................................................... 4-21

TRIG2 Signal.................................................................................... 4-22

STARTSCAN Signal........................................................................ 4-24

CONVERT* Signal .......................................................................... 4-26

AIGATE Signal ................................................................................ 4-27

SISOURCE Signal............................................................................ 4-27

SCANCLK Signal ............................................................................ 4-28

EXTSTROBE* Signal...................................................................... 4-29

WFTRIG Signal................................................................................ 4-29

UPDATE* Signal ............................................................................. 4-30

UISOURCE Signal ........................................................................... 4-31

GPCTR0_SOURCE Signal .............................................................. 4-32

GPCTR0_GATE Signal ................................................................... 4-33

GPCTR0_OUT Signal...................................................................... 4-34

GPCTR0_UP_DOWN Signal........................................................... 4-35

GPCTR1_SOURCE Signal .............................................................. 4-35

GPCTR1_GATE Signal ................................................................... 4-36

NI 6115/6120 User Manual viii ni.com

Page 8

GPCTR1_OUT Signal ......................................................................4-36

GPCTR1_UP_DOWN Signal ...........................................................4-37

FREQ_OUT Signal ...........................................................................4-38

Field Wiring Considerations..........................................................................................4-39

Chapter 5

Calibration

Loading Stored Calibration Constants...........................................................................5-1

Self-Calibration..............................................................................................................5-2

External Calibration.......................................................................................................5-2

Appendix A

Specifications

Appendix B

Common Questions

Appendix C

Technical Support and Professional Services

Contents

Glossary

Index

© National Instruments Corporation ix NI 6115/6120 User Manual

Page 9

About This Manual

This manual describes the electrical and mechanical aspects of the

NI 6115/6120 and contains information concerning its operation

and programming.

The NI 6115/6120 family includes the following devices:

• NI PCI-6115

• NI PXI-6115

• NI PCI-6120

• NI PXI-6120

The NI 6115/6120 is a high-performance multifunction analog, digital, and

timing I/O data acquisition (DAQ) device for PXI and PCI bus computers.

Supported functions include analog input (AI), analog output (AO),

digital I/O (DIO), and timing I/O (TIO).

Conventions

The following conventions appear in this manual:

<> Angle brackets that contain numbers separated by an ellipsis represent a

range of values associated with a bit or signal name—for example,

DIO<3..0>.

» The » symbol leads you through nested menu items and dialog box options

to a final action. The sequence File»Page Setup»Options directs you to

pull down the File menu, select the Page Setup item, and select Options

from the last dialog box.

♦ The ♦ symbol indicates that the following text applies only to a specific

product, a specific operating system, or a specific software version.

This icon denotes a note, which alerts you to important information.

This icon denotes a caution, which advises you of precautions to take to

avoid injury, data loss, or a system crash. When this symbol is marked on

the product, refer to the Safety Information section of Chapter 1,

Introduction, for precautions to take.

© National Instruments Corporation xi NI 6115/6120 User Manual

Page 10

About This Manual

bold Bold text denotes items that you must select or click on in the software,

such as menu items and dialog box options. Bold text also denotes

parameter names and hardware labels.

CompactPCI CompactPCI refers to the core specification defined by the PCI Industrial

Computer Manufacturer’s Group (PICMG).

italic Italic text denotes variables, emphasis, a cross reference, or an introduction

to a key concept. This font also denotes text that is a placeholder for a word

or value that you must supply.

monospace Monospace text denotes text or characters that you should enter from the

keyboard, sections of code, programming examples, and syntax examples.

This font is also used for the proper names of disk drives, paths, directories,

programs, subprograms, subroutines, device names, functions, operations,

variables, filenames and extensions, and code excerpts.

NI 6115/6120 This phrase refers to any device in the NI 6115/6120 family.

PCI Peripheral Component Interconnect—PCI is a high-performance

expansion bus architecture originally developed by Intel to replace ISA

and EISA.

Platform Text in this font denotes a specific platform and indicates that the text

following it applies only to that platform.

PXI A rugged, open system for modular instrumentation based on CompactPCI,

with special mechanical, electrical, and software features. The PXI bus

standard was originally developed by National Instruments in 1997, and is

now managed by the PXI bus Systems Alliance.

National Instruments Documentation

The NI 6115/6120 User Manual is one piece of the documentation set for

the DAQ system. You could have any of several types of documentation

depending on the hardware and software in the system. Use the

documentation you have as follows:

• DAQ Quick Start Guide—This guide describes how to install the DAQ

software and hardware, and confirm that the DAQ device is operating

properly. When using this guide, refer to the pinout diagram for the

NI 6110/6111. The pinouts for the NI 6110/6111 and the NI 6115/6120

are identical.

NI 6115/6120 User Manual xii ni.com

Page 11

• DAQ hardware documentation—This documentation has detailed

information about the DAQ hardware that plugs into or is connected to

the computer. Use this documentation for hardware installation and

configuration instructions, specification information about the DAQ

hardware, and application hints.

• Software documentation—You may have both application software

and NI-DAQ documentation. NI application software includes

LabVIEW and Measurement Studio. After you set up the hardware

system, use either your application software documentation or the

NI-DAQ documentation to help you write your application. If you

have a large, complicated system, it is worthwhile to look through the

software documentation before you configure the hardware.

• Accessory installation guides or manuals—If you are using accessory

products, read the terminal block and cable assembly installation

guides. They explain how to physically connect the relevant pieces

of the system. Consult these guides when you are making the

connections.

Related Documentation

The following documents contain information you may find helpful:

• DAQ Quick Start Guide, located at

• DAQ-STC Technical Reference Manual, located at ni.com/manuals

• NI Developer Zone tutorial, Field Wiring and Noise Considerations

for Analog Signals, located at

• NI-DAQ User Manual for PC Compatibles, located at

ni.com/manuals

• NI-DAQ Function Reference Help. You can access this help file by

clicking Start»Programs»National Instruments»NI-DAQ»

NI-DAQ Help.

• PCI Local Bus Specification Revision 2.2

• PICMG 2.0 R3.0, CompactPCI Core Specification

• PXI Specification Revision 2.0, available from

About This Manual

ni.com/manuals

ni.com/zone

www.pxisa.org

© National Instruments Corporation xiii NI 6115/6120 User Manual

Page 12

Introduction

This chapter describes the NI 6115/6120, lists what you need to get started,

describes the optional software and optional equipment, and explains how

to unpack the device.

About the NI 6115/6120

Thank you for buying an NI 6115/6120. The NI 6115/6120 is a Plug and

Play multifunction analog, digital, and timing I/O device for PXI and PCI

bus computers. The NI 6115 features a 12-bit A/D converter (ADC) per

channel with four simultaneously sampling analog inputs, and two 12-bit

D/A converters (DACs) with voltage outputs. The NI 6120 features a 16-bit

ADC per input channel and 16-bit DACs for output. Each device features

eight lines of TTL-compatible correlated DIO, and two 24-bit

counter/timers for TIO.

The NI 6115/6120 is a DAQ device for PXI or the PCI bus. The device

is software configured and calibrated, and completely switchless and

jumperless. This feature is made possible by the NI MITE bus interface

chip that connects the device to the PXI or PCI I/O bus. The MITE

implements the PCI Local Bus Specification so that you can configure

all the interrupts and base memory addresses with software.

1

The NI 6115/6120 uses the NI data acquisition system timing controller

(DAQ-STC) for time-related functions. The DAQ-STC consists of three

timing groups that control AI, AO, and general-purpose counter/timer

functions. These groups include a total of seven 24-bit and three 16-bit

counters and a maximum timing resolution of 50 ns. The DAQ-STC makes

possible such applications as buffered pulse generation and equivalent time

sampling.

The NI 6115/6120 uses the Real-Time System Integration (RTSI) bus to

easily synchronize several measurement devices to a common trigger or

timing event. The RTSI bus allows synchronization of the measurements.

The RTSI bus consists of the RTSI bus interface and a ribbon cable to route

timing and trigger signals between as many as five DAQ devices in the

computer. If you are using the NI PXI-6115/6120 in a PXI chassis, RTSI

lines, known as the PXI trigger bus, are part of the backplane. Therefore,

© National Instruments Corporation 1-1 NI 6115/6120 User Manual

Page 13

Chapter 1 Introduction

you do not need the RTSI cable for system triggering and timing on the

PXI. In addition, a phase-locked loop (PLL) circuit accomplishes the

synchronization of multiple NI PXI-6115/6120 devices or other PXI

devices which support PLL synchronization by allowing these devices to

all lock to the same reference clock present on the PXI backplane. Refer to

the Phase-Locked Loop Circuit section of Chapter 3, Hardware Overview,

for more information.

Detailed specifications of the NI 6115/6120 are in Appendix A,

Specifications.

Using PXI with CompactPCI

The ability to use PXI-compatible products with standard CompactPCI

products is an important feature of PXI Specification Revision 2.0. If you

use a PXI-compatible plug-in device in a standard CompactPCI chassis,

you are unable to use PXI-specific functions, but you can still use the basic

plug-in device functions. For example, the RTSI interface on the

NI PXI-6115/6120 is available in a PXI chassis, but not in a CompactPCI

chassis.

The CompactPCI specification permits vendors to develop sub-buses that

coexist with the basic PCI interface on the CompactPCI bus. Compatible

operation is not guaranteed between CompactPCI devices with different

sub-buses nor between CompactPCI devices with sub-buses and PXI

devices. The standard implementation for CompactPCI does not include

these sub-buses. The NI PXI-6115/6120 works in any standard

CompactPCI chassis adhering to PICMG CompactPCI 2.0 R3.0.

PXI-specific features are implemented on the J2 connector of the

CompactPCI bus. Table 1-1 lists the J2 pins used by the NI PXI-6115/6120.

The PXI device is compatible with any CompactPCI chassis with a sub-bus

that does not drive these lines. Even if the sub-bus is capable of driving

these lines, the PXI device is still compatible as long as those pins on the

sub-bus are disabled by default and are never enabled.

Caution Damage can result if these lines are driven by the sub-bus.

NI 6115/6120 User Manual 1-2 ni.com

Page 14

Table 1-1. NI PXI-6115/6120 J2 Pin Assignment

NI PXI-6115/6120 Signal PXI Pin Name

RTSI<0..5> PXI Trigger<0..5> B16, A16, A17,

RTSI 6 Star D17

RTSI Clock PXI Trigger 7 E16

Reserved LBL<0..12> C20, E20, A19,

Reserved LBR<0..12> A21, C21, D21,

What You Need to Get Started

To set up and use the NI 6115/6120, you need the following:

Chapter 1 Introduction

PXI J2 Pin

Number

A18, B18, C18

C19

E21, A20, B20,

E15, A3, C3, D3,

E3, A2, B2

❑ A computer or a PXI/CompactPCI chassis and controller

(hereafter referred to as the computer)

❑ At least one of the following devices:

– NI PCI-6115

– NI PXI-6115

– NI PCI-6120

– NI PXI-6120

❑ NI 6115/6120 User Manual

❑ NI-DAQ for PC compatibles

❑ (Optional) One of the following software packages and

documentation:

– LabVIEW (Windows)

– Measurement Studio (Windows)

– VI Logger (Windows)

© National Instruments Corporation 1-3 NI 6115/6120 User Manual

Page 15

Chapter 1 Introduction

Software Programming Choices

When programming National Instruments DAQ hardware, you can use an

NI application development environment (ADE) or other ADEs. In either

case, you use NI-DAQ.

NI-DAQ

NI-DAQ, which shipped with the NI 6115/6120, has an extensive library of

functions that you can call from the ADE. These functions allow you to use

all the features of the device.

NI-DAQ carries out many of the complex interactions, such as

programming interrupts, between the computer and the DAQ hardware.

NI-DAQ maintains a consistent software interface among its different

versions so that you can change platforms with minimal modifications

to the code. Whether you are using LabVIEW, LabWindows

Measurement Studio, VI Logger, or other ADEs, your application uses

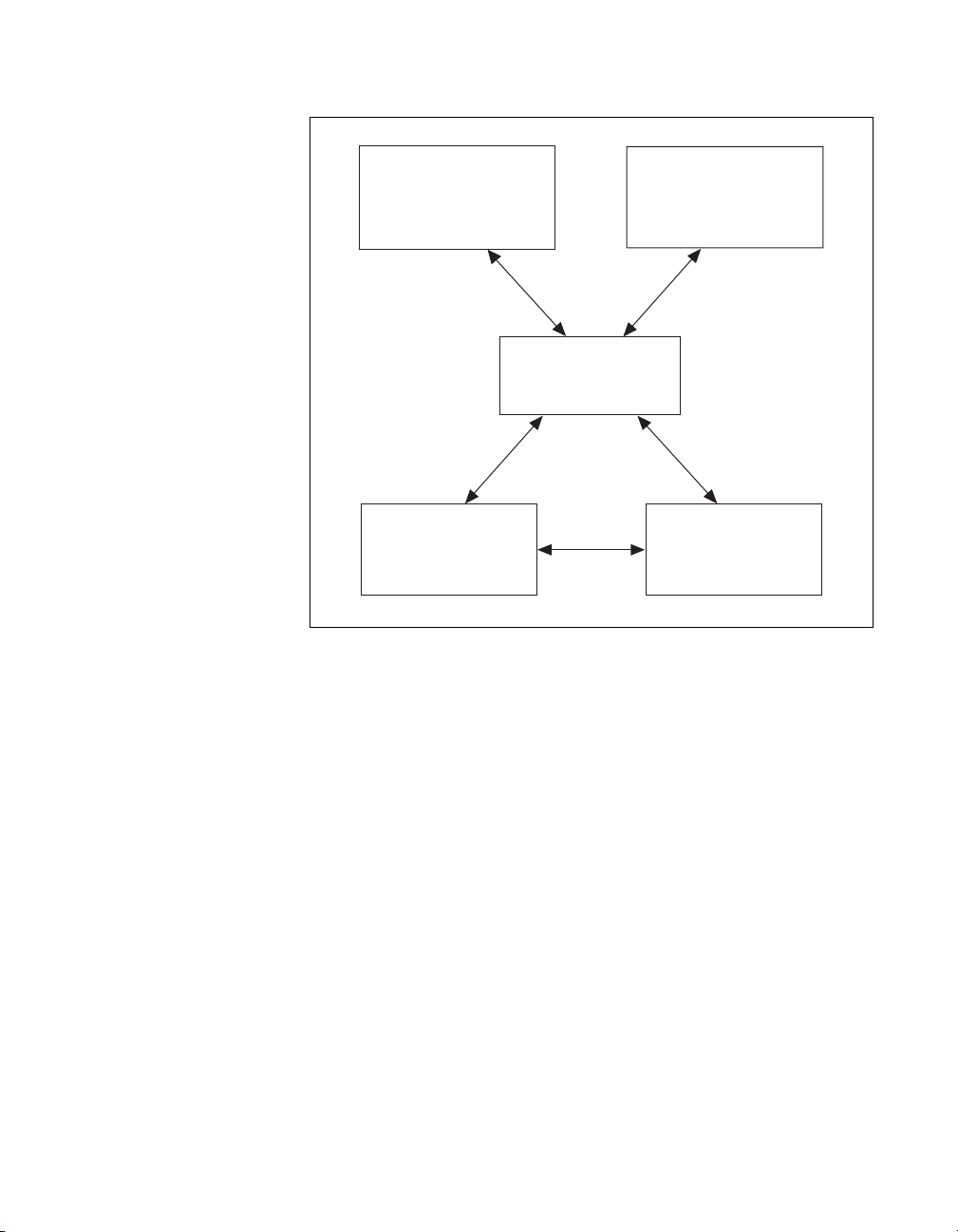

NI-DAQ, as illustrated in Figure 1-1.

™

/CVI™,

NI 6115/6120 User Manual 1-4 ni.com

Page 16

Chapter 1 Introduction

Conventional

Programming Environment

NI-DAQ

Driver Software

DAQ

Hardware

Figure 1-1. The Relationship Among the Programming Environment,

NI-DAQ, and the Hardware

LabVIEW,

LabWindows/CVI,

Measurement Studio,

or VI Logger

Personal

Computer or

Workstation

To download a free copy of the most recent version of NI-DAQ, click

Download Software at

ni.com.

National Instruments ADE Software

LabVIEW features interactive graphics, a state-of-the-art interface, and

a powerful graphical programming language. The LabVIEW Data

Acquisition VI Library, a series of virtual instruments for using LabVIEW

with National Instruments DAQ hardware, is included with LabVIEW.

LabWindows/CVI is a complete ANSI C ADE that features an interactive

user interface, code generation tools, and the LabWindows/CVI Data

Acquisition and Easy I/O libraries.

Measurement Studio, which includes tools for Visual C++ and tools for

Visual Basic, is a development suite that allows you to design test and

measurement applications. For Visual Basic developers, Measurement

Studio features a set of ActiveX controls for using National Instruments

© National Instruments Corporation 1-5 NI 6115/6120 User Manual

Page 17

Chapter 1 Introduction

DAQ hardware. These ActiveX controls provide a high-level programming

interface for building virtual instruments (VIs). For Visual C++ developers,

Measurement Studio offers a set of Visual C++ classes and tools to

integrate those classes into Visual C++ applications. The ActiveX controls

and classes are available with Measurement Studio and the NI-DAQ

software.

VI Logger is an easy-to-use yet flexible tool specifically designed for data

logging applications. Using dialog windows, you can configure data

logging tasks to easily acquire, log, view, and share your data. VI Logger

does not require any programming; it is a stand-alone, configuration-based

software program.

Using LabVIEW, LabWindows/CVI, Measurement Studio, or VI Logger

greatly reduces the development time for your data acquisition and control

application.

Optional Equipment

NI offers a variety of products to use with the NI 6115/6120, including

cables, connector blocks, and other accessories, as follows:

• Shielded cables and cable assemblies

• Connector blocks, shielded 50- and 68-pin screw terminals

• RTSI bus cables (PCI only)

• Low channel-count signal conditioning modules, devices, and

accessories, including conditioning for strain gauges, resistance

temperature detectors, and relays

For more specific information about these products, refer to the NI catalog

at

ni.com/catalog.

Custom Cabling

NI offers cables and accessories to help you prototype your application or

to use if you frequently change device interconnections.

If you want to develop your own cable, however, adhere to the following

guidelines for best results:

• For AI signals, use shielded twisted-pair wires for each AI pair for

differential inputs. Tie the shield for each signal pair to the ground

reference at the source.

NI 6115/6120 User Manual 1-6 ni.com

Page 18

Unpacking

Caution Never touch the exposed pins of connectors.

Chapter 1 Introduction

• Route the analog lines separately from the digital lines.

• When using a cable shield, use separate shields for the analog and

digital halves of the cable. Failure to do so results in noise coupling

into the analog signals from transient digital signals.

Mating connectors and a backshell kit for making custom 68-pin cables are

available from NI.

The parts in the following list are recommended for connectors that mate to

the I/O connector on the device:

• Honda 68-position, solder cup, female connector

• Honda backshell

The NI 6115/6120 is shipped in an antistatic package to prevent

electrostatic damage to the device. Electrostatic discharge (ESD) can

damage several components on the device.

To avoid such damage when handling the device, take the following

precautions:

• Ground yourself using a grounding strap or by holding a grounded

object.

• Touch the antistatic package to a metal part of the computer chassis

before removing the device from the package.

Remove the device from the package and inspect the device for

loose components or any sign of damage. Notify NI if the device appears

damaged in any way. Do not install a damaged device into the computer.

Store the NI 6115/6120 in the antistatic envelope when not in use.

© National Instruments Corporation 1-7 NI 6115/6120 User Manual

Page 19

Chapter 1 Introduction

Safety Information

The following section contains important safety information that you must

follow when installing and using the product.

Do not operate the product in a manner not specified in this document.

Misuse of the product can result in a hazard. You can compromise the

safety protection built into the product if the product is damaged in any

way. If the product is damaged, return it to National Instruments for repair.

Do not substitute parts or modify the product except as described in this

document. Use the product only with the chassis, modules, accessories, and

cables specified in the installation instructions. You must have all covers

and filler panels installed during operation of the product.

Do not operate the product in an explosive atmosphere or where there may

be flammable gases or fumes. Operate the product only at or below the

pollution degree stated in Appendix A, Specifications. Pollution is foreign

matter in a solid, liquid, or gaseous state that can reduce dielectric strength

or surface resistivity. The following is a description of pollution degrees:

• Pollution Degree 1 means no pollution or only dry, nonconductive

pollution occurs. The pollution has no influence.

• Pollution Degree 2 means that only nonconductive pollution occurs in

most cases. Occasionally, however, a temporary conductivity caused

by condensation must be expected.

• Pollution Degree 3 means that conductive pollution occurs, or dry,

nonconductive pollution occurs that becomes conductive due to

condensation.

Clean the product with a soft nonmetallic brush. Make sure that the product

is completely dry and free from contaminants before returning it to service.

Yo u must insulate signal connections for the maximum voltage for which

the product is rated. Do not exceed the maximum ratings for the product.

Remove power from signal lines before connecting them to or

disconnecting them from the product.

Clean the product with a soft nonmetallic brush. Make sure that the product

is completely dry and free from contaminants before returning it to service.

Operate this product only at or below the installation category stated in

Appendix A, Specifications.

NI 6115/6120 User Manual 1-8 ni.com

Page 20

Chapter 1 Introduction

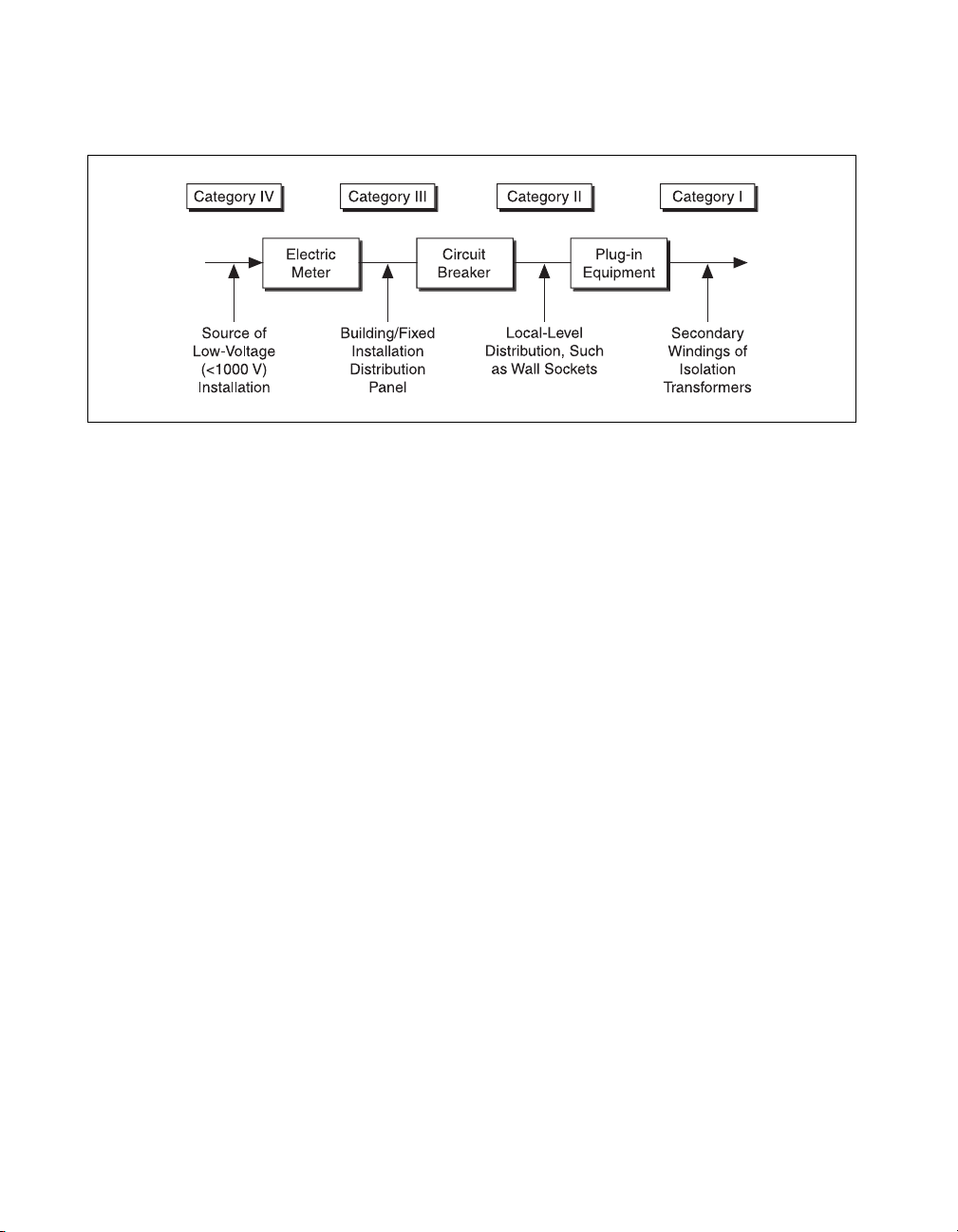

The following is a description of installation categories:

• Installation Category I is for measurements performed on circuits not

directly connected to MAINS

1

. This category is a signal level such as

voltages on a printed wire board (PWB) on the secondary of an

isolation transformer.

Examples of Installation Category I are measurements on circuits not

derived from MAINS and specially protected (internal)

MAINS-derived circuits.

• Installation Category II is for measurements performed on circuits

directly connected to the low-voltage installation. This category refers

to local-level distribution such as that provided by a standard wall

outlet.

Examples of Installation Category II are measurements on household

appliances, portable tools, and similar equipment.

• Installation Category III is for measurements performed in the building

installation. This category is a distribution level referring to hardwired

equipment that does not rely on standard building insulation.

Examples of Installation Category III include measurements on

distribution circuits and circuit breakers. Other examples of

Installation Category III are wiring including cables, bus-bars, junction

boxes, switches, socket outlets in the building/fixed installation, and

equipment for industrial use, such as stationary motors with a

permanent connection to the building/fixed installation.

• Installation Category IV is for measurements performed at the source

of the low-voltage (<1,000 V) installation.

Examples of Installation Category IV are electric meters, and

measurements on primary overcurrent protection devices and

ripple-control units.

1

MAINS is defined as the electricity supply system to which the equipment concerned is designed to be connected either for

powering the equipment or for measurement purposes.

© National Instruments Corporation 1-9 NI 6115/6120 User Manual

Page 21

Chapter 1 Introduction

Below is a diagram of a sample installation.

NI 6115/6120 User Manual 1-10 ni.com

Page 22

Installing and Configuring the

NI 6115/6120

This chapter explains how to install and configure the NI 6115/6120.

Installing the Software

Before you install the NI 6115/6120, complete the following steps to install

the software:

1. Install the ADE, such as LabVIEW or Measurement Studio, according

to the instructions on the CD and the release notes.

2. Install NI-DAQ according to the instructions on the CD and the

DAQ Quick Start Guide included with the device. When using the

DAQ Quick Start Guide, refer to the pinout for the NI 6110/6111,

which is identical to the pinout for the NI 6115/6120.

Note It is important to install NI-DAQ before installing the NI 6115/6120 to ensure that

the device is properly detected.

2

Installing the Hardware

You can install the NI 6115/6120 in any available expansion slot in the

computer. However, to achieve best noise performance, leave as much

room as possible between the NI 6115/6120 and other devices and

hardware.

The following are general installation instructions, so consult the computer

user manual or technical reference manual for specific instructions and

warnings.

♦ NI PXI-6115/6120

1. Power off and unplug the computer.

2. Choose an unused PXI slot in the system. For maximum performance,

the NI PXI-6115/6120 has an onboard DMA controller that you can

use only if the device is installed in a slot that supports bus arbitration,

© National Instruments Corporation 2-1 NI 6115/6120 User Manual

Page 23

Chapter 2 Installing and Configuring the NI 6115/6120

or bus master devices. NI recommends installing the

NI PXI-6115/6120 in such a slot.

Note The PXI specification requires all slots to support bus master devices, but the

CompactPCI specification does not. If you install in a CompactPCI non-master slot, you

must disable the onboard DMA controller using software.

3. Make sure there are no lighted LEDs on the chassis. If any are lit, wait

until they go out before continuing the installation.

4. Remove the filler panel for the slot you have chosen.

5. Ground yourself using a grounding strap or by touching a grounded

object. Follow the ESD protection precautions described in the

Unpacking section of Chapter 1, Introduction.

6. Remove the rubber front panel screw protectors.

7. Insert the NI PXI-6115/6120 into a 5 V PXI slot. Use the

injector/ejector handle to fully insert the device into the chassis.

8. Screw the front panel of the NI PXI-6115/6120 to the front

panel-mounting rail of the system.

9. Visually verify the installation. Make sure the device is not touching

other devices or components and is fully inserted in the slot.

10. Plug in and power on the computer.

The NI PXI-6115/6120 is now installed. You are now ready to configure

the hardware and software.

♦ NI PCI-6115/6120

1. Power off and unplug the computer.

2. Remove the cover.

3. Make sure there are no lighted LEDs on the motherboard. If any are lit,

wait until they go out before continuing the installation.

4. Remove the expansion slot cover on the back panel of the computer.

5. Ground yourself using a grounding strap or by touching a grounded

object. Follow the ESD protection precautions described in the

Unpacking section of Chapter 1, Introduction.

6. Insert the NI PCI-6115/6120 into a PCI system slot. Gently rock the

device to ease it into place. It may be a tight fit, but do not force the

device into place.

7. Screw the mounting bracket of the device to the back panel rail of the

computer.

NI 6115/6120 User Manual 2-2 ni.com

Page 24

8. Replace the cover.

9. Plug in and power on the computer.

The NI PCI-6115/6120 is now installed. You are now ready to configure the

hardware and software.

Configuring the Device

Because of the NI standard architecture for data acquisition and the PCI bus

specification, the NI 6115/6120 is completely software-configurable. Two

types of configuration are performed on the NI 6115/6120: bus-related and

data acquisition-related configuration.

The NI PCI-6115/6120 is fully compatible with the industry-standard

PCI Local Bus Specification Revision 2.2. This compatibility allows the

PCI system to automatically perform all bus-related configurations with no

user interaction. Bus-related configuration includes setting the device base

memory address and interrupt channel.

The NI PXI-6115/6120 is fully compatible with the industry-standard PXI

Specification Revision 2.0. This allows the PXI/CompactPCI system to

automatically perform all bus-related configurations with no user

interaction. Bus-related configuration includes setting the device base

memory address and interrupt channel.

Chapter 2 Installing and Configuring the NI 6115/6120

Data acquisition-related configuration, which you must perform, includes

such settings as analog input coupling and range, and others. You can

modify these settings using NI-DAQ or application-level software, such as

LabVIEW and Measurement Studio.

To configure the device in Measurement & Automation Explorer (MAX),

refer to either the DAQ Quick Start Guide or to the NI-DAQ User Manual

for PC Compatibles at

installation and troubleshooting instructions, refer to

ni.com/support/daq.

© National Instruments Corporation 2-3 NI 6115/6120 User Manual

ni.com/manuals. For operating system-specific

Page 25

Hardware Overview

This chapter presents an overview of the hardware functions on the

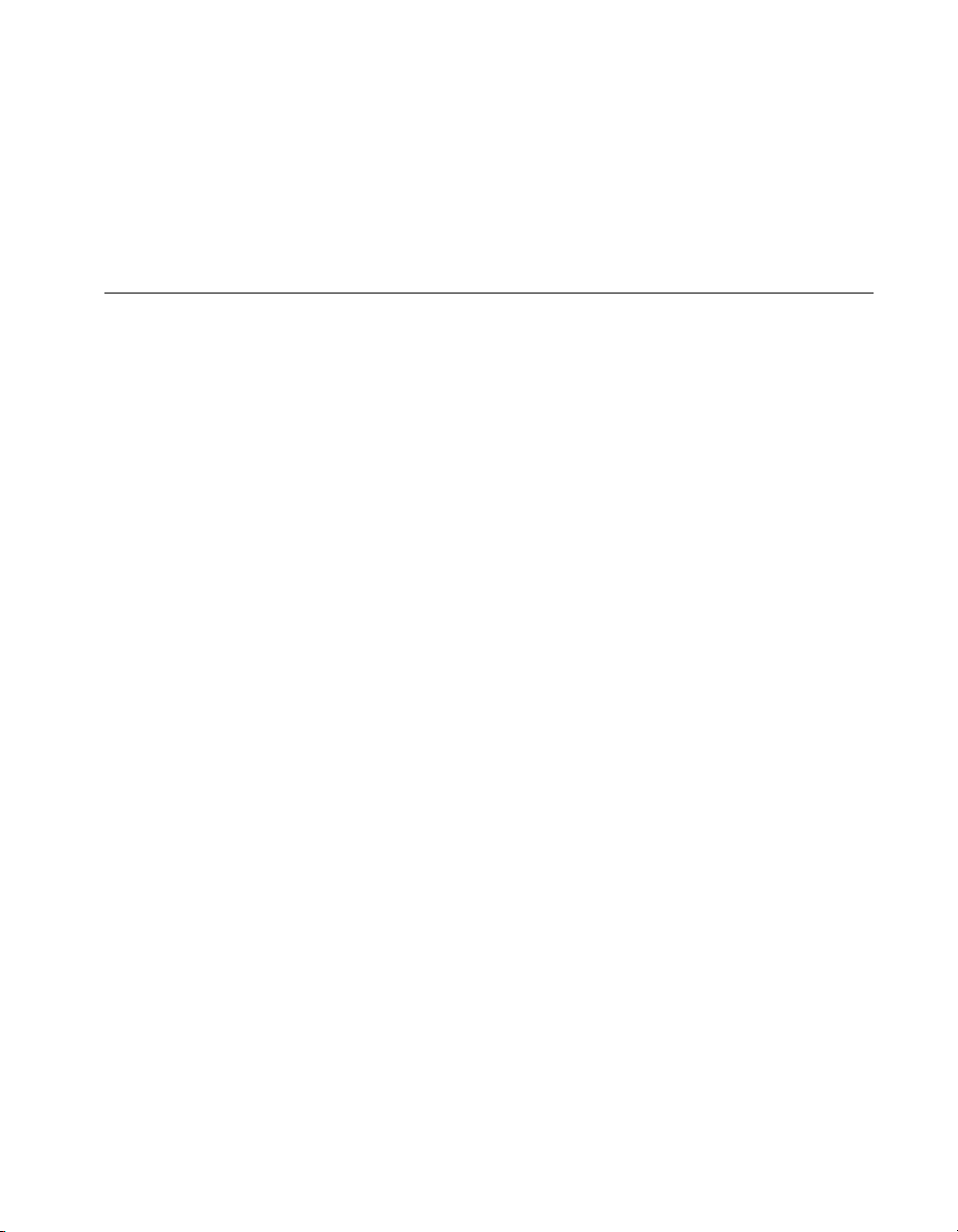

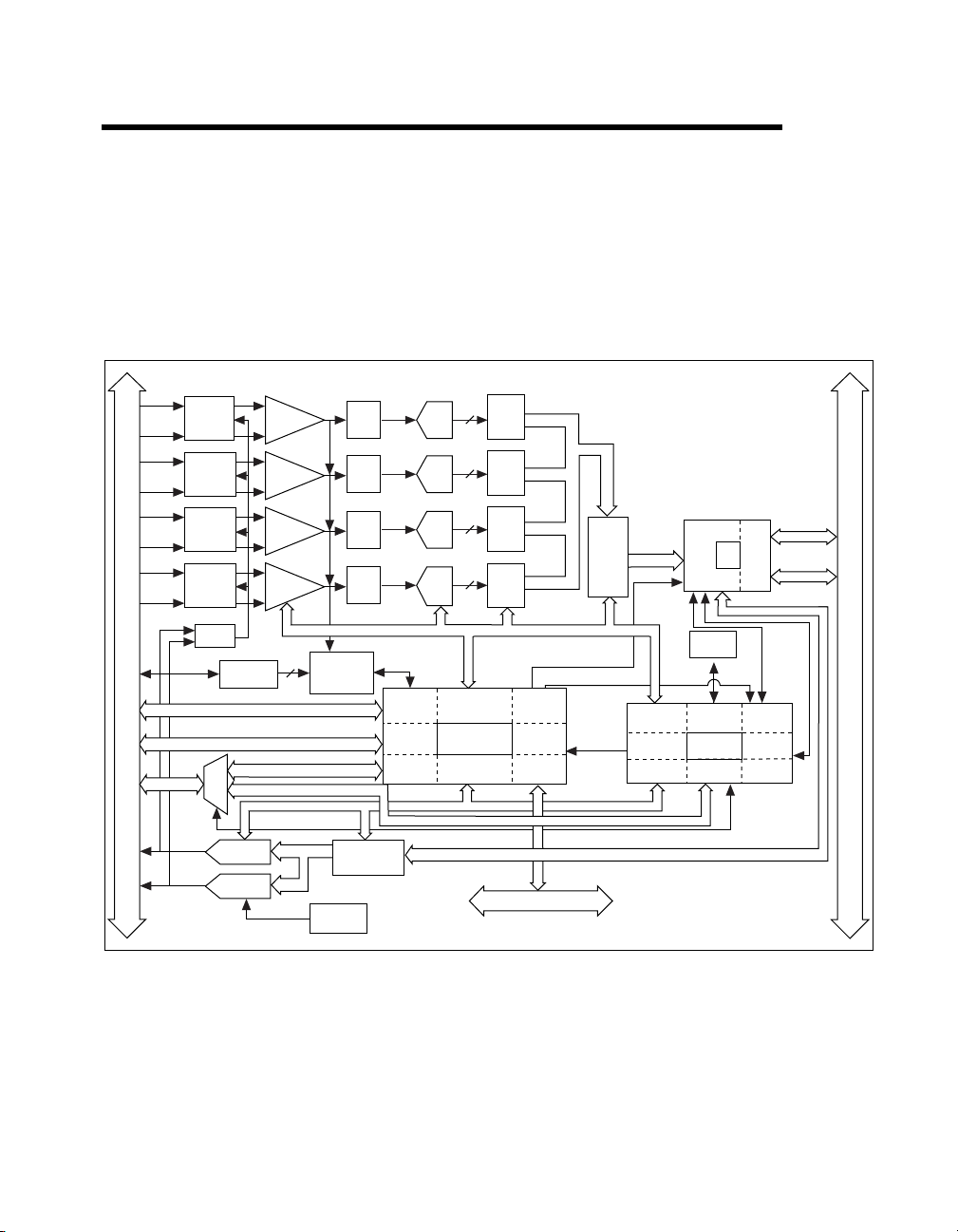

NI 6115/6120. Figures 3-1 and 3-2 provide block diagrams for the NI 6115

and NI 6120, respectively.

3

CH0+

AI CH0

Mux

CH0–

CH1+

AI CH1

Mux

CH1–

CH2+

AI CH2

Mux

CH2–

CH3+

AI CH3

Mux

CH3–

Calibration

Mux

Trigger

Trigger Level

DACs

Digital I/O (8)

PFI / Trigger

Timing

DIO

MUX

DAC0

DAC1

I/O Connector

+

CH0

Amplifier

–

+

CH1

Amplifier

–

+

CH2

Amplifier

–

+

CH3

Amplifier

–

2

STC Digital I/O (8)

FPGA Digital I/O (8)

Data (12)

Calibration

Analog

Trigger

Circuitry

DACs

Anti-

Aliasing

Filter

Anti-

Aliasing

Filter

Anti-

Aliasing

Filter

Anti-

Aliasing

Filter

DAC

FIFO

Trigger

Counter/

Timing I/O

Digital I/O

CH0

12-Bit

ADC

CH1

12-Bit

ADC

CH2

12-Bit

ADC

CH3

12-Bit

ADC

Analog Input

Timing/Control

DAQ - STC

Analog Output

Timing/Control

AO Control

Data (32)

CH0

12

12

12

12

Latch

CH1

Latch

CH2

Latch

CH3

Latch

Data (16)

Data (16)

Data (16)

Data (16)

AI Control

DMA/IRQ

Bus

Interface

RTSI Bus

Interface

IRQ

DMA

ADC

FIFO

Data (32)

Analog

Input

Control

DAQ-STC

Bus

Interface

Analog

Output

Control

Generic

Bus

Interface

EEPROM

EEPROM

Control

FPGA

Control

Control

PCI

Mini

Bus

MITE

Interface

Address/Data

DMA

Interface

DIO

FIFO

I/O

DIO

Bus

Interface

PXI/PCI Bus

RTSI Bus

Figure 3-1. NI 6115 Block Diagram

© National Instruments Corporation 3-1 NI 6115/6120 User Manual

Page 26

Chapter 3 Hardware Overview

CH0+

AI CH0

Mux

CH0–

CH1+

AI CH1

Mux

CH1–

CH2+

AI CH2

Mux

CH2–

CH3+

AI CH3

Mux

CH3–

Calibration

Mux

Trigger

Trigger Level

DACs

Digital I/O (8)

PFI / Trigger

Timing

DIO

MUX

DAC0

DAC1

I/O Connector

+

CH0

Amplifier

–

+

CH1

Amplifier

–

+

CH2

Amplifier

–

+

CH3

Amplifier

–

2

STC Digital I/O (8)

FPGA Digital I/O (8)

Data (16)

Calibration

Analog

Trigger

Circuitry

DACs

Anti-

Aliasing

Filter

Anti-

Aliasing

Filter

Anti-

Aliasing

Filter

Anti-

Aliasing

Filter

DAC

FIFO

Trigger

Counter/

Timing I/O

Digital I/O

CH0

16-Bit

ADC

CH1

16-Bit

ADC

CH2

16-Bit

ADC

CH3

16-Bit

ADC

Analog Input

Timing/Control

DAQ - STC

Analog Output

Timing/Control

AO Control

Data (32)

16

CH0

Data (16)

Latch

CH1

16

16

16

Latch

CH2

Latch

CH3

Latch

Data (16)

Data (16)

Data (16)

AI Control

IRQ

ADC

FIFO

Data (32)

Generic

Bus

Interface

EEPROM

Mini

MITE

PCI

Bus

Interface

Control

Address/Data

DMA

DMA/IRQ

Bus

Interface

RTSI Bus

Interface

Analog

Input

Control

DAQ-STC

Bus

Interface

Analog

Output

Control

EEPROM

Control

FPGA

DIO

Control

DMA

Interface

DIO

FIFO

I/O

Bus

Interface

PXI/PCI Bus

RTSI Bus

Figure 3-2. NI 6120 Block Diagram

Analog Input

The following sections describe in detail each AI category.

Input Mode

The NI 6115/6120 supports only differential (DIFF) input mode. For more

information about DIFF input, refer to the Connecting Analog Input

Signals section of Chapter 4, Connecting Signals, which contains diagrams

showing the signal paths for DIFF input mode.

Note The inputs are differential only in the sense that the ground loops are broken.

The negative input is not intended to carry signals of interest, rather it provides a DC

reference point for the positive input, which may be different than ground.

NI 6115/6120 User Manual 3-2 ni.com

Page 27

Input Polarity and Input Range

The NI 6115/6120 has bipolar inputs only. Bipolar input means that the

midpoint of the input voltage range is centered at zero volts.

You can independently configure each channel for a different input voltage

range.

The software-programmable gain on this device increases its overall

flexibility by matching the input signal ranges to those that the ADC can

accommodate. It has ranges of ±42 V, ±20 V, ±10 V, ±5 V, ±2 V, ±1 V,

±500 mV, and ±200 mV and is suited for a wide variety of signal levels.

By choosing the optimal gain setting, you can maximize usage of the

dynamic range of the ADC, which effectively increases input signal

resolution. Table 3-1 shows the overall input range and precision according

to the gain used.

Caution The NI 6115/6120 is not designed for input voltages greater than ±42 VDC.

Input voltages greater than ±42 VDC can damage the NI 6115/6120, any device connected

to it, and the host computer. Overvoltage can also cause an electric shock hazard for the

operator. NI is not liable for damage or injury resulting from such misuse.

Chapter 3 Hardware Overview

© National Instruments Corporation 3-3 NI 6115/6120 User Manual

Page 28

Chapter 3 Hardware Overview

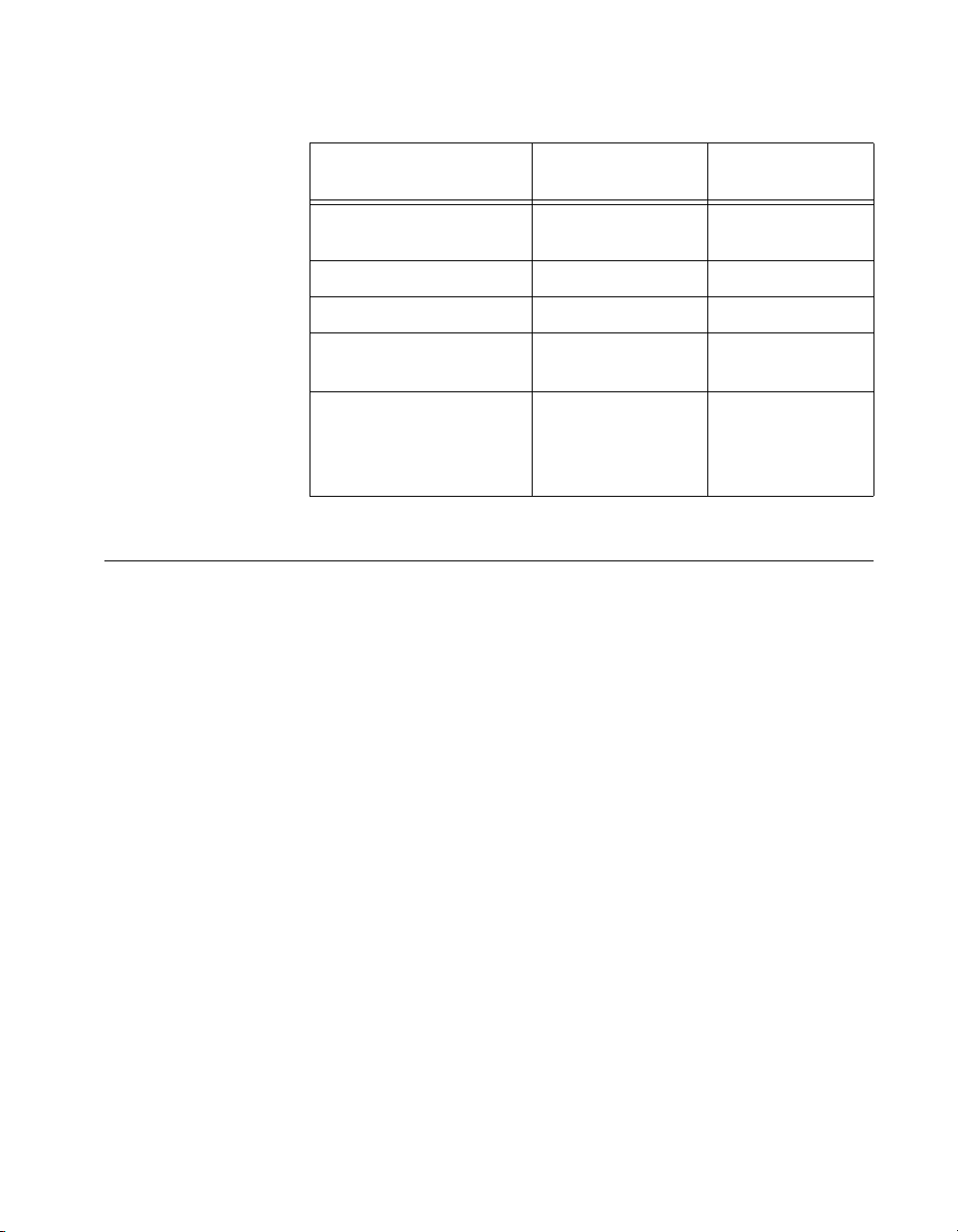

Table 3-1. Input Range and Measurement Precision

Precision

Input Range

–50 to +50 V

2

–20 to +20 V

–10 to +10 V

–5 to +5 V

–2 to +2 V

–1 to +1V

–500 to +500 mV

–200 to +200 mV

1

The value of 1 least significant bit (LSB) of the ADC; that is, the voltage increment

corresponding to a change of one count in the ADC count.

2

Do not exceed ±42 VDC maximum.

Note: Refer to Appendix A, Specifications, for absolute maximum ratings.

6115 (12-Bit) 6120 (16-Bit)

24.4 mV

9.77 mV

4.88 mV

2.44 mV

977 µV

488 µV

244 µV

97.7 µV

1

1.53 mV

610 µV

305 µV

153 µV

61.0 µV

30.5 µV

15.3 µV

6.10 µV

Considerations for Selecting Input Ranges

The range you select depends on the expected range of the incoming signal.

A large input range can accommodate a large signal variation but reduces

the voltage resolution. Choosing a smaller input range improves the voltage

resolution but may result in the input signal going out of range. For best

results, match the input range as closely as possible to the expected range

of the input signal.

Input Coupling

You can configure the NI 6115/6120 for either AC or DC input coupling

on a per channel basis. Use AC coupling when the AC signal contains a

large DC component. If you enable AC coupling, you remove the large DC

offset for the input amplifier and amplify only the AC component. This

configuration effectively uses the dynamic range of the ADC.

The input impedance for the programmable gain instrumentation amplifier

(PGIA) channels is 1 MΩ for ranges ≤ ±10 V and 10 kΩ for

ranges > ±10 V. This configuration provides an AC-coupled corner

frequency of 2.34 Hz for ranges ≤ ±10 V and 234 Hz for ranges > ±10 V.

NI 6115/6120 User Manual 3-4 ni.com

Page 29

Analog Output

Note The AO channels do not have analog or digital filtering hardware and do produce

images in the frequency domain related to the update rate.

Analog Trigger

Chapter 3 Hardware Overview

The NI 6115/6120 supplies two channels of AO voltage at the I/O

connector. The range is fixed at bipolar ±10 V.

The AO channels on the NI 6115 contain 12-bit DACs that are capable of

4 MS/s for one channel or 2.5 MS/s for each of two channels. The NI 6120

DACs are 16-bit, and they have the same AO capabilities as the NI 6115.

Refer to Appendix A, Specifications, for more detailed information about

the AO capabilities of the NI 6115/6120.

The NI 6115/6120 includes high-density memory modules allowing for

long waveform generations.

In addition to supporting internal software triggering and external digital

triggering to initiate a DAQ sequence, these devices also support analog

hardware triggering. You can configure the analog trigger circuitry to

accept either a direct analog input from the PFI0/TRIG1 pin on the

I/O connector or a post-gain signal from the output of the PGIA on any of

the channels, as shown in Figure 3-3. The trigger-level range for the direct

analog channel is ±10 V with a resolution of 78 mV for the NI 6115 and

4.88 mV for the NI 6120. The input impedance for the direct analog

channel is 10 kΩ. When this direct analog channel is configured for AC

coupling, the corner frequency is 159 Hz.

The range for the post-PGIA trigger from a selected channel is the

full-scale range of the selected channel with a resolution of that range

divided by 256 for the NI 6115 and 4,096 for the NI 6120.

Two trigger reference signals, lowValue and highValue, can then be

independently set to achieve advanced triggering modes. Refer to

Figures 3-3 through 3-8 for illustrations of these modes.

Note The PFI0/TRIG1 pin is an analog input when configured as an analog trigger.

Therefore, it is susceptible to crosstalk from adjacent pins, which can result in false

triggering when the pin is left unconnected. To avoid false triggering, make sure the

PFI0/TRIG1 pin is connected to a low-impedance signal source (less than 1 kΩ source

impedance) if you plan to enable this input using software.

© National Instruments Corporation 3-5 NI 6115/6120 User Manual

Page 30

Chapter 3 Hardware Overview

Analog

Input

CH0

Analog

Input

CH1

Analog

Input

CH2

Analog

Input

CH3

+

PGIA

–

+

PGIA

–

+

PGIA

–

+

PGIA

–

PFI0/TRIG1

ADC

ADC

ADC

ADC

AC Couple

Digital Data

Mux

10 k

highValue

Analog

Trigger

Circuit

lowValue

Trigger

DAC

DAQ-STC

Trigger

DAC

Figure 3-3. Analog Trigger Block Diagram for the NI 6115/6120

In below-low-level analog triggering mode, the trigger is generated when

the signal value is less than lowValue, as shown in Figure 3-4. HighValue

is unused.

lowValue

Trigger

Figure 3-4. Below-Low-Level Analog Triggering Mode

In above-high-level analog triggering mode, the trigger is generated when

the signal value is greater than highValue, as shown in Figure 3-5.

LowValue is unused.

NI 6115/6120 User Manual 3-6 ni.com

Page 31

Chapter 3 Hardware Overview

highValue

Trigger

Figure 3-5. Above-High-Level Analog Triggering Mode

In inside-region analog triggering mode, the trigger is generated when the

signal value is between the lowValue and the highValue, as Figure 3-6

shows.

highValue

lowValue

Trigger

Figure 3-6. Inside-Region Analog Triggering Mode

In high-hysteresis analog triggering mode, the trigger is generated when the

signal value is greater than highValue, with the hysteresis specified by

lowValue, as Figure 3-7 shows.

highValue

lowValue

Trigger

Figure 3-7. High-Hysteresis Analog Triggering Mode

© National Instruments Corporation 3-7 NI 6115/6120 User Manual

Page 32

Chapter 3 Hardware Overview

In low-hysteresis analog triggering mode, the trigger is generated when

the signal value is less than lowValue, with the hysteresis specified by

highValue, as Figure 3-8 shows.

highValue

lowValue

Trigger

Figure 3-8. Low-Hysteresis Analog Triggering Mode

The analog trigger circuit generates an internal digital trigger based on the

AI signal and the user-defined trigger levels. This digital trigger can be

used by any of the timing sections of the DAQ-STC, including the AI, AO,

and general-purpose counter/timer sections. For example, the AI section

can be configured to acquire n scans after the AI signal crosses a specific

threshold. As another example, the AO section can be configured to update

its outputs whenever the AI signal crosses a specific threshold.

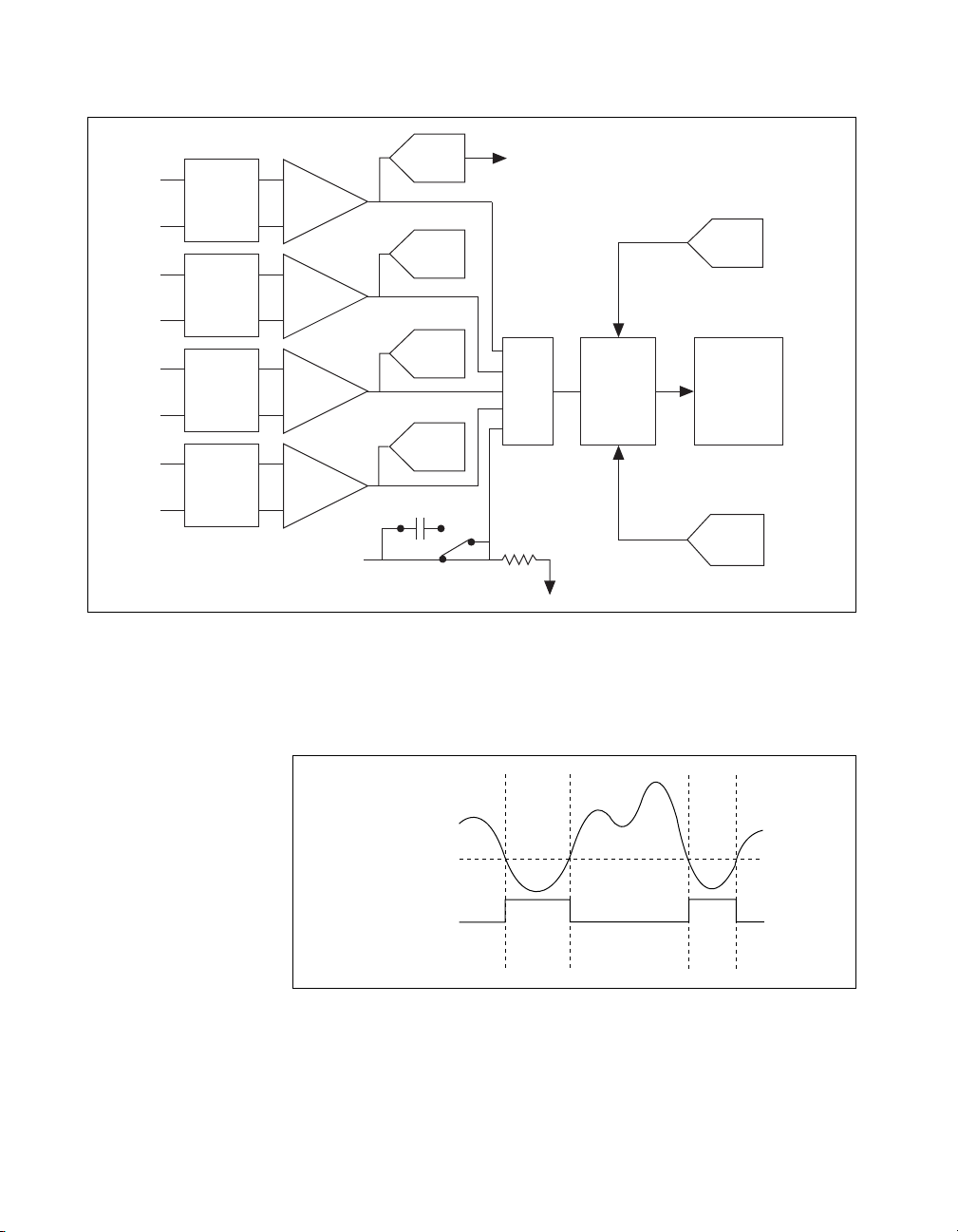

Antialiasing Filters

Each AI channel on the NI 6115/6120 is equipped with a programmable

antialaising Bessel filter. On the NI 6115, you can program the filters to

provide a third-order 50 kHz lowpass filter, a third-order 500 kHz lowpass

filter, or a pass-through mode with no filtering. On the NI 6120, you can

program the filters to provide a five-pole 100 kHz low-pass filter or

pass-through. These Bessel filters are highly effective at reducing signal

aliasing and are designed for use with software filters.

Existing software algorithms alone provide good roll-off at the cut-off

frequency as shown in Figure 3-9. However, aliasing can cause

high-frequency harmonics to make it through passbands in the filter. By

combining hardware and software filtering, it is possible to obtain both

steep roll-off and clean filtering of high-frequency aliases.

NI 6115/6120 User Manual 3-8 ni.com

Page 33

Chapter 3 Hardware Overview

Response of Analog Hardware Filters

Response of Software Filters

Figure 3-9. Effects of Hardware and Software Filtering on Antialiasing

Phase-Locked Loop Circuit

♦ NI PXI-6115/6120

A phase-locked loop (PLL) circuit accomplishes the synchronization of

multiple NI PXI-6115/6120 devices or other PXI devices which support

PLL synchronization by allowing these devices to all lock to the same

reference clock present on the PXI backplane. This circuit allows you to

trigger input or output operations on different devices and ensures that

samples occur at the same time.

The PLL circuitry consists of a voltage-controlled crystal oscillator

(VCXO) with a tuning range of ±50 ppm. The VCXO generates the

60 MHz master clock used onboard the NI PXI-6115/6120.

The PLL locks to the 10 MHz oscillator line on the PXI backplane bus.

A phase comparator running at 1 MHz compares the PXI Bus and VCXO

clock. The loop filter then processes the error signal and outputs a control

voltage for the VCXO. Figure 3-10 illustrates the block diagram for the

NI PXI-6115/6120.

f

cutoff

f

Nyquist

(2 f

cutoff

4 f

cutoff

)

Note This feature is not available on the NI PCI-6115/6120.

The PLL circuit is automatically enabled when the NI 6115/6120 is

powered up. No configuration steps are required in order to utilize PLL

synchronization.

© National Instruments Corporation 3-9 NI 6115/6120 User Manual

Page 34

Chapter 3 Hardware Overview

10 MHz

PXI Bus

Div/10

Div/60

Phase Comp

Correlated Digital I/O

The NI 6115/6120 contains eight lines of DIO for general-purpose use.

You can software-configure groups of individual lines for either input or

output. The NI 6115/6120 includes a FIFO for buffered operation. This

operation allows you to read/write an array of data, using either an internal

or external clock source, at a maximum rate of 10 MHz. In addition, you

can correlate DIO and AI/AO operations to the same clock. Refer to the

Correlating DIO Signal Connections section of Chapter 4, Connecting

Signals, for information on which signals you can use to clock DIO

operation. At system startup and reset, the DIO ports are all

high-impedance.

The hardware up/down control for general-purpose counters 0 and 1 are

connected onboard to DIO6 and DIO7, respectively. Thus, you can use

DIO6 and DIO7 to control the general-purpose counters. The up/down

control signals, GPCTR0_UP_DOWN and GPCTR1_UP_DOWN, are

input only and do not affect the operation of the DIO lines.

60 MHz out

+

–

Loop

Filter

Figure 3-10. PLL Block Diagram

synched to 10 MHZ

backplane clock

VCXO

Timing Signal Routing

The DAQ-STC provides a flexible interface for connecting timing signals

to other devices or external circuitry. The NI 6115/6120 uses the RTSI bus

to interconnect timing signals between devices, and it uses the

programmable function input (PFI) pins on the I/O connector to connect the

device to external circuitry. These connections are designed to enable the

NI 6115/6120 to both control and be controlled by other devices and

circuits.

There are 13 timing signals internal to the DAQ-STC that can be controlled

by an external source. These timing signals can also be controlled by

signals generated by the DAQ-STC, and these selections are fully software

NI 6115/6120 User Manual 3-10 ni.com

Page 35

Chapter 3 Hardware Overview

configurable. For example, Figure 3-11 shows the signal routing

multiplexer for controlling the STARTSCAN signal.

RTSI Trigger <0..6>

STARTSCAN

PFI<0..9>

Scan Interval Counter TC

GPCTR0_OUT

Figure 3-11. STARTSCAN Signal Routing

This figure shows that STARTSCAN can be generated from a number of

sources, including the external signals RTSI<0..6> and PFI<0..9> and the

internal signals Scan Interval Counter TC and GPCTR0_OUT.

Many of these timing signals are also available as outputs on the RTSI pins,

as indicated in the RTSI Triggers section later in this chapter, and on the

PFI pins, as indicated in Chapter 4, Connecting Signals.

© National Instruments Corporation 3-11 NI 6115/6120 User Manual

Page 36

Chapter 3 Hardware Overview

Programmable Function Inputs

The 10 PFIs are connected to the signal routing multiplexer for each timing

signal, and software can select one of the PFIs as the external source for a

given timing signal. It is important to note that any PFI can be used as an

input by any timing signal and that multiple timing signals can

simultaneously use the same PFI. This flexible routing scheme reduces the

need to change physical connections to the I/O connector for different

applications. You can also individually enable each PFI pin to output a

specific internal timing signal. For example, if you need the UPDATE*

signal as an output on the I/O connector, software can enable the output

driver for the PFI5/UPDATE* pin.

Device and RTSI Clocks

Many functions performed by the NI 6115/6120 require a frequency

timebase to generate the necessary timing signals for controlling A/D

conversions, updates, or general-purpose signals at the I/O connector.

The NI 6115/6120 can use either its internal 20 MHz timebase or a

timebase received over the RTSI bus. In addition, if you configure the

device to use the internal timebase, you can also program the device to drive

its internal timebase over the RTSI bus to another device that is

programmed to receive this timebase signal. This clock source, whether

local or from the RTSI bus, is used directly by the device as the primary

frequency source. The default configuration at startup is to use the internal

timebase without driving the RTSI bus timebase signal. This timebase is

software-selectable.

RTSI Triggers

The seven RTSI trigger lines on the RTSI bus provide a very flexible

interconnection scheme for any device sharing the RTSI bus. These

bidirectional lines can drive any of eight timing signals onto the RTSI bus

and can receive any of these timing signals. The RTSI trigger lines connect

to other devices through the PXI bus on the PXI backplane or through a

special ribbon cable that must be installed for PCI. Figure 3-12 shows the

PCI signal connection scheme and Figure 3-13 shows the PXI connection

scheme.

NI 6115/6120 User Manual 3-12 ni.com

Page 37

Chapter 3 Hardware Overview

In PCI, you can access all seven RTSI lines (RTSI<0..6>) through their

RTSI cable. With the NI PXI-6115/6120, RTSI<0..5> connects to PXI

Trigger <0..5>, respectively, through the NI PXI-6115/6120 backplane.

In PXI, RTSI<6> connects to the PXI Star Trigger line, allowing the

NI 6115/6120 to receive triggers from any Star Trigger controller plugged

into slot 2 of the chassis. For more information on the Star Trigger, refer to

the PXI Specification Revision 2.0.

DAQ-STC

TRIG1

TRIG2

CONVERT*

UPDATE*

WFTRIG

GPCTR0_SOURCE

GPCTR0_GATE

Trigger

RTSI Bus Connector

7

Clock

Switch

RTSI Switch

GPCTR0_OUT

STARTSCAN

AIGATE

SISOURCE

UISOURSE

GPCTR1_SOURCE

GPCTR1_GATE

RTSI_OSC (20 MHz)

Figure 3-12. PCI RTSI Bus Signal Connection

© National Instruments Corporation 3-13 NI 6115/6120 User Manual

Page 38

Chapter 3 Hardware Overview

PXI Star (6)

PXI Trigger (0..5)

PXI Bus Connector

6

PXI Trigger (7)

RTSI Switch

Switch

DAQ-STC

TRIG1

TRIG2

CONVERT*

UPDATE*

WFTRIG

GPCTR0_SOURCE

GPCTR0_GATE

GPCTR0_OUT

STARTSCAN

AIGATE

SISOURCE

UISOURSE

GPCTR1_SOURCE

GPCTR1_GATE

RTSI_OSC (20 MHz)

Figure 3-13. PXI RTSI Bus Signal Connections

Refer to the Connecting Timing Signals section of Chapter 4, Connecting

Signals, for a description of the signals shown in Figures 3-12 and 3-13.

NI 6115/6120 User Manual 3-14 ni.com

Page 39

Connecting Signals

This chapter describes how to connect input and output signals to the

NI 6115/6120 using the device I/O connector.

Table 4-1. I/O Connector Details

4

Device with I/O

Connector

NI 6115,

NI 6120

I/O Connector

Caution Connections that exceed any of the maximum ratings of input or output signals

on the NI 6115/6120 can damage the device and the computer. NI is not liable for any

damage resulting from such signal connections. The Protection column of Tables 4-3, 4-4,

and 4-5 show the maximum input ratings for each signal.

Number

of Pins

68 N/A SH6868 Shielded Cable,

Figure 4-1 shows the pin assignments for the 68-pin I/O connector on the

NI 6115/6120. A signal description follows the connector pinouts.

Cable for Connecting

to 100-pin Accessories

Cable for Connecting

to 68-pin Accessories

SH68-68-EP, R6868,

SH68-68R1-EP

© National Instruments Corporation 4-1 NI 6115/6120 User Manual

Page 40

Chapter 4 Connecting Signals

ACH0–

ACH1+

ACH1GND

ACH2–

ACH3+

ACH3GND

NC

NC

NC

NC

NC

NC

DAC0OUT

DAC1OUT

NC

DIO4

DGND

DIO1

DIO6

DGND

+5V OUTPUT

DGND

DGND

PFI0/TRIG1

PFI1/TRIG2

DGND

+5V OUTPUT

DGND

PFI5/UPDATE*

PFI6/WFTRIG

DGND

PFI9/GPCTR0_GATE

GPCTR0_OUT

FREQ_OUT

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

68

ACH0+

67

ACH0GND

66

ACH1–

65

ACH2+

64

ACH2GND

63

ACH3–

62

NC

61

NC

60

NC

59

NC

58

NC

57

NC

56

NC

55

AOGND

54

AOGND

53

DGND

52

DIO0

51

DIO5

50

DGND

49

DIO2

48

DIO7

47

DIO3

46

SCANCLK

45

EXTSTROBE*

44

DGND

43

9

8

7

6

5

4

3

2

1

PFI2/CONVERT*

42

PFI3/GPCTR1_SOURCE

41

PFI4/GPCTR1_GATE

40

GPCTR1_OUT

39

DGND

38

PFI7/STARTSCAN

37

PFI8/GPCTR0_SOURCE

36

DGND

35

DGND

NC = No Connect

Figure 4-1. I/O Connector Pin Assignment for the NI 6115/6120

NI 6115/6120 User Manual 4-2 ni.com

Page 41

Chapter 4 Connecting Signals

I/O Connector Signal Descriptions

Table 4-2. Signal Descriptions for I/O Connector Pins

Signal Name Reference Direction Description

ACH<0..3>GND — — Ground for Anal og Input Channels 0 through 3— These

pins are the bias current return point for

pseudodifferential measurements.

ACH<0..3>+ ACH<0..3>GND Input Analog Input Channels 0 through 3 (+)—These pins

ACH<0..3>– ACH<0..3>GND Input Analog Input Channels 0 through 3 (–)—These pins are

DAC0OUT AOGND Output Analog Channel 0 Output—This pin supplies the

DAC1OUT AOGND Output Analog Channel 1 Output—This pin supplies the

AOGND — — Analog Output Ground—The AO voltages are

DGND — — Digital Ground—This pin supplies the reference for the

DIO<0..7> DGND Input

Output

+5V DGND Output +5 VDC Source—These pins are fused for up to 1 A of

SCANCLK DGND Output Scan Clock—This pin pulses once for each A/D

are routed to the (+) terminal of the respective channel

amplifier and carry the input signal.

routed to the (–) terminal of the respective channel

amplifier and are the DC reference for the (+) input

signal of that channel.

voltage output of AO channel 0.

voltage output of AO channel 1.

referenced to this node.

digital signals at the I/O connector as well as the

+5 VDC supply.

Digital I/O Signals—DIO6 and 7 can control the

up/down signal of general-purpose counters 0 and 1,

respectively.

+5 V supply. The fuse is self-resetting.

conversion when enabled. The low-to-high edge

indicates when the input signal can be removed from

the input or switched to another signal.

EXTSTROBE* DGND Output External Strobe—This output can be toggled under