®

NAT4882

Programmer Reference Manual

October 1993 Edition

Part Number 320383-01

© Copyright 1991, 1994 National Instruments Corporation.

All Rights Reserved.

National Instruments Corporate Headquarters

6504 Bridge Point Parkway

Austin, TX 78730-5039

(512) 794-0100

Technical support fax: (800) 328-2203

(512) 794-5678

Branch Offices:

Australia (03) 879 9422, Austria (0662) 435986, Belgium 02/757.00.20, Canada (Ontario) (519) 622-9310,

Canada (Québec) (514) 694-8521, Denmark 45 76 26 00, Finland (90) 527 2321, France (1) 48 14 24 24,

Germany 089/741 31 30, Italy 02/48301892, Japan (03) 3788-1921, Mexico 95 800 010 0793,

Netherlands 03480-33466, Norway 32-84 84 00, Singapore 2265886, Spain (91) 640 0085, Sweden 08-730 49 70,

Switzerland 056/20 51 51, Taiwan 02 377 1200, U.K. 0635 523545

Limited Warranty

The NAT4882® integrated circuit (“equipment”) is warranted against defects in material and workmanship

under normal use and service for a period of one (1) year from the date of shipment from the National

Instruments factory. During this period of one year, National Instruments shall at its sole option either repair,

replace, or credit the Buyer for defective equipment if: (i) Buyer returns the equipment to National

Instruments, FOB the National Instruments factory in Austin, Texas; (ii) Buyer notifies National Instruments

promptly upon discovery of any defect in writing, including a detailed description of the defect; and (iii) upon

examination of the returned equipment, National Instruments is satisfied that the circuit is defective and that

the cause of such defect is not alteration or repair by someone other than National Instruments, neglect,

accident, misuse, improper installation, or use contrary to any instructions issued by National Instruments.

A Return Material Authorization (RMA) number must be obtained from the factory and clearly marked on the

outside of the package before any equipment will be accepted for warranty work. Prior to issuance of a RMA

by National Instruments, Buyer shall allow National Instruments the opportunity to inspect the equipment onsite at Buyer’s facility.

This warranty expires one year from date of original shipment regardless of any warranty performance during

that warranty period. The warranty provided herein is Buyer’s sole and exclusive remedy for nonconformity of

the equipment or for breach of any warranty. THE ABOVE IS IN LIEU OF ALL OTHER WARRANTIES

EXPRESSED OR IMPLIED. NATIONAL INSTRUMENTS SPECIFICALLY DISCLAIMS THE IMPLIED

WARRANTIES OF MERCHANTIBILITY AND FITNESS FOR A PARTICULAR PURPOSE. BUYER’S

RIGHT TO RECOVER DAMAGES CAUSED BY FAULT OR NEGLIGENCE ON THE PART OF NATIONAL

INSTRUMENTS SHALL BE LIMITED TO THE AMOUNT THERETOFORE PAID BY THE BUYER.

NATIONAL INSTRUMENTS WILL NOT BE LIABLE FOR DAMAGES RESULTING FROM LOSS OF

DATA, PROFITS, USE OF PRODUCTS, OR INCIDENTAL OR CONSEQUENTIAL DAMAGES, EVEN IF

ADVISED OF THE POSSIBILITY THEREOF. This limitation of the liability of National Instruments will

apply regardless of the form of action, whether in contract or tort, including negligence. National Instruments

recommends against the use of its products as critical components in any life support devices or systems

whose failure to perform can reasonably be expected to cause significant injury to a human. Buyer assumes

all risk for such application and agrees to indemnify National Instruments for all damages which may be

incurred due to use of the National Instruments standard devices in medical or life support applications. Any

action against National Instruments must be brought within one year after the cause of action accrues.

National Instruments believes that the information in this manual is accurate. The document has been

carefully reviewed for technical accuracy. In the event that technical or typographical errors exist, National

Instruments reserves the right to make changes to subsequent editions of this document without prior notice to

holders of this edition. The reader should consult National Instruments if errors are suspected. In no event

shall National Instruments be liable for any damages arising out of or related to this document or the

information contained in it.

Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or

mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in

whole or in part, without the prior written consent of National Instruments Corporation.

Trademarks

NAT4882® is a trademark of National Instruments Corporation.

Product and company names listed are trademarks or trade names of their respective companies.

WARNING REGARDING MEDICAL AND CLINICAL USE

OF NATIONAL INSTRUMENTS PRODUCTS

National Instruments products are not designed with components and testing intended to ensure a level of

reliability suitable for use in treatment and diagnosis of humans. Applications of National Instruments products

involving medical or clinical treatment can create a potential for accidental injury caused by product failure,

or by errors on the part of the user or application designer. Any use or application of National Instruments

products for or involving medical or clinical treatment must be performed by properly trained and qualified

medical personnel, and all traditional medical safeguards, equipment, and procedures that are appropriate in

the particular situation to prevent serious injury or death should always continue to be used when National

Instruments products are being used. National Instruments products are NOT intended to be a substitute for any

form of established process, procedure, or equipment used to monitor or safeguard human health and safety in

medical or clinical treatment.

Contents

About This Manual

Organization of This Manual...............................................................................ix

Conventions Used in This Manual.......................................................................x

Related Documents..............................................................................................x

Customer Communication...................................................................................x

Chapter 1

Introduction and General Description

NAT4882 Features...............................................................................................1-1

NAT4882 Functional Description........................................................................1-2

GPIB Capabilities ................................................................................................1-5

Interrupt Capabilities............................................................................................1-7

7210 Mode Interrupts...............................................................................1-7

9914 Mode Interrupts...............................................................................1-8

Addressing Schemes............................................................................................1-9

Chapter 2

NAT4882 Interface Registers

Register Description Format................................................................................2-1

7210 Mode Registers ...........................................................................................2-2

Data In Register (DIR).............................................................................2-5

Command/Data Out Register (CDOR)....................................................2-6

Interrupt Status Register 1 (ISR1)............................................................2-7

Interrupt Mask Register 1 (IMR1)...........................................................2-7

Interrupt Status Register 2 (ISR2)............................................................2-14

Interrupt Mask Register 2 (IMR2)...........................................................2-14

Serial Poll Status Register (SPSR)...........................................................2-19

Serial Poll Mode Register (SPMR)..........................................................2-19

Key Status Register (KSR) ......................................................................2-21

Key Control Register (KCR)....................................................................2-22

Address Status Register (ADSR).............................................................2-24

Address Mode Register (ADMR)............................................................2-27

Command Pass Through Register (CPTR)..............................................2-30

Source/Acceptor Status Register (SASR)................................................2-32

Auxiliary Mode Register (AUXMR).......................................................2-34

Hidden Registers......................................................................................2-44

Parallel Poll Register (PPR).........................................................2-44

Auxiliary Register A (AUXRA)..................................................2-47

Auxiliary Register B (AUXRB)...................................................2-49

Auxiliary Register E (AUXRE)...................................................2-51

Auxiliary Register F (AUXRF)....................................................2-53

Auxiliary Register G (AUXRG)..................................................2-55

Auxiliary Register I (AUXRI).....................................................2-57

Auxiliary Register J (AUXRJ).....................................................2-60

................................................................................2-1

..............................................................1-1

© National Instruments Corporation v NAT4882 Programmer Reference Manual

Contents

Address Register 0 (ADR0).....................................................................2-62

Address Register (ADR)..........................................................................2-63

Interrupt Status Register 0 (ISR0)............................................................2-64

Interrupt Mask Register 0 (IMR0)...........................................................2-64

Address Register 1 (ADR1).....................................................................2-68

End Of String Register (EOSR)...............................................................2-70

Bus Status Register (BSR).......................................................................2-71

Bus Control Register (BCR)....................................................................2-71

9914 Mode Registers ...........................................................................................2-74

Interrupt Status Register 0 (ISR0)............................................................2-76

Interrupt Mask Register 0 (IMR0)...........................................................2-76

Interrupt Status Register 1 (ISR1)............................................................2-81

Interrupt Mask Register 1 (IMR1)...........................................................2-81

Address Status Register (ADSR).............................................................2-87

Interrupt Mask Register 2 (IMR2)...........................................................2-90

End Of String Register (EOSR)...............................................................2-92

Bus Control Register (BCR)....................................................................2-93

Hidden Registers......................................................................................2-95

Accessory Register A (ACCRA).................................................2-95

Accessory Register B (ACCRB)..................................................2-97

Accessory Register E (ACCRE)..................................................2-99

Accessory Register F (ACCRF)...................................................2-100

Accessory Register I (ACCRI) ....................................................2-102

Accessory Register J (ACCRJ)....................................................2-104

Bus Status Register (BSR).......................................................................2-106

Auxiliary Command Register (AUXCR).................................................2-107

Interrupt Status Register 2 (ISR2)............................................................2-116

Address Register (ADR)..........................................................................2-119

Serial Poll Status Register (SPSR)...........................................................2-120

Serial Poll Mode Register (SPMR)..........................................................2-120

Command Pass Through Register (CPTR)..............................................2-122

Parallel Poll Register (PPR).....................................................................2-124

Data In Register (DIR).............................................................................2-125

Data Out Register (DOR).........................................................................2-126

Chapter 3

NAT4882 Programming Considerations

Initialization.........................................................................................................3-1

The NAT4882 as GPIB Controller......................................................................3-3

System Controller ....................................................................................3-3

Becoming Controller-In-Charge (CIC) and Active Controller................3-3

Sending Remote Multiline Messages (Commands).................................3-4

Going from Active to Standby Controller................................................3-4

Going from Standby to Active Controller................................................3-5

Going from Active to Idle Controller ......................................................3-5

The NAT4882 as GPIB Talker and Listener .......................................................3-6

Programmed Implementation of Talker and Listener..............................3-6

NAT4882 Programmer Reference Manual vi © National Instruments Corporation

..........................................................3-1

Addressed Implementation of Talker and Listener..................................3-6

Address Mode 1...........................................................................3-7

Address Mode 2...........................................................................3-7

Address Mode 3...........................................................................3-7

Sending and Receiving Messages........................................................................3-8

Sending and Receiving END or EOS ......................................................3-9

Performing an RFD Holdoff on the Last Data Byte................................3-9

Aborting a Data Transmission.................................................................3-10

Serial Polls...........................................................................................................3-10

Conducting Serial Polls............................................................................3-10

Requesting Service...................................................................................3-10

Responding to Serial Polls.......................................................................3-11

Parallel Polls ........................................................................................................3-11

Conducting a Parallel Poll........................................................................3-12

Responding to a Parallel Poll...................................................................3-13

Interrupts..............................................................................................................3-14

Direct Memory Access (DMA)............................................................................3-14

Synchronization Detection...................................................................................3-14

Timeouts...............................................................................................................3-15

Global Timeouts.......................................................................................3-15

Byte Timeouts..........................................................................................3-15

Contents

Appendix A

Multiline Interface Command Messages

..........................................................A-1

Appendix B

Mnemonics Key

.........................................................................................................B-1

Appendix C

Customer Communication

.....................................................................................C-1

Glossary.............................................................................................................Glossary-1

Index.........................................................................................................................Index-1

© National Instruments Corporation vii NAT4882 Programmer Reference Manual

Contents

Figures

Figure 1-1. NAT4882 Implementation Block Diagram..............................................1-2

Figure 1-2. NAT4882 Block Diagram........................................................................1-4

Figure 2-1. 7210 Mode Register Map.........................................................................2-3

Figure 2-2. 7210 Mode Hidden Registers...................................................................2-4

Figure 2-3. GPIB I/O Hardware Configuration for µPD7210 Mode..........................2-72

Figure 2-4. 9914 Mode Interface Registers................................................................2-74

Figure 2-5. 9914 Mode Hidden Registers...................................................................2-75

Figure 2-6. GPIB I/O Hardware Configuration for TMS9914A Mode......................2-93

Tables

Table 1-1. NAT4882 IEEE 488 Interface Capabilities.............................................1-5

Table 2-1. Clues to Understanding Mnemonics........................................................2-2

Table 2-2. Multiline GPIB Commands Recognized by the GPIB Chip in

µPD7210 Mode........................................................................................2-30

Table 2-3. Auxiliary Command Summary................................................................2-35

Table 2-4. Auxiliary Command Description.............................................................2-37

Table 2-5. Clear Conditions for SISB Bit.................................................................2-58

Table 2-6. Timeout Values in µPD7210 Mode.........................................................2-60

Table 2-7. Timeout Values in TMS9914A Mode.....................................................2-104

Table 2-8. Auxiliary Command Summary................................................................2-108

Table 2-9. Auxiliary Command Description.............................................................2-110

Table 2-10. Multiline GPIB Commands Recognized by the NAT4882 in

9914A Mode ............................................................................................2-122

NAT4882 Programmer Reference Manual viii © National Instruments Corporation

About This Manual

The NAT4882 is an application-specific integrated circuit developed by National Instruments.

The NAT4882 is an IEEE 488.2 Controller chip designed to perform all the interface functions

defined in the IEEE 488.1-1987 standard and the additional requirements of the IEEE 488.2-1987

standard. The NAT4882 performs complete IEEE 488 Talker, Listener, and Controller functions

and is software compatible with the NEC µPD7210 and TI TMS9914A GPIB controller chips.

The NAT4882 provides the core of a complete, high-speed IEEE 488.2 interface.

This manual describes the programmable features of the NAT4882 and contains information

suitable for programmers and engineers who wish to write software for the NAT4882.

Organization of This Manual

This manual is divided into the following sections and appendixes:

• Chapter 1, Introduction and General Description, contains a list of NAT4882 features, a

functional description of the NAT4882, a list of GPIB and interrupt capabilities, and a

discussion of the addressing scheme used by the NAT4882.

• Chapter 2, NAT4882 Interface Registers, contains information on the use of the NAT4882

internal program registers. It also contains NAT4882 address maps and detailed descriptions

of the NAT4882 interface registers.

• Chapter 3, NAT4882 Programming Considerations, explains important considerations for

programming the NAT4882 in 7210 mode.

• Appendix A, Multiline Interface Command Messages, lists the multiline interface messages

and describes the mnemonics and messages that correspond to the interface functions. These

functions include initializing the bus, addressing and unaddressing devices, and setting device

modes for local or remote programming. The multiline interface messages are IEEE 488defined commands that are sent and received with ATN TRUE.

• Appendix B, Mnemonics Key, is an easy reference table that defines the mnemonics

(abbreviations) used throughout this manual for functions, remote messages, local messages,

states, bits, registers, integrated circuits, and system functions.

• Appendix C, Customer Communication, contains forms you can use to request help from

National Instruments or to comment on our products and manuals.

• The Glossary contains an alphabetical list and description of terms used in this manual,

including acronyms, abbreviations, metric prefixes, mnemonics, and symbols.

• The Index contains an alphabetical list of key terms and topics used in this manual, including

the page number where you can find each one.

© National Instruments Corporation ix NAT4882 Programmer Reference Manual

About This Manual

Conventions Used in This Manual

The following conventions are used to distinguish elements of text throughout this manual:

italic Italic text denotes emphasis, a cross reference, or an introduction to a

key concept.

7210 mode 7210 mode is used throughout this manual to refer to the NEC

µPD7210 software compatibility mode.

9914 mode 9914 mode is used throughout this manual to refer to the TI

TMS9914A software compatibility mode.

IEEE 488 and IEEE 488 and IEEE 488.2 are used throughout this manual to refer to

IEEE 488.2 the ANSI/IEEE Standard 488.1-1987 and the ANSI/IEEE Standard

488.2-1987, respectively, which define the GPIB.

Abbreviations, acronyms, metric prefixes, mnemonics, symbols, and terms are listed in the

Glossary.

Related Documents

The following documents contain information that may be helpful as you read this manual:

• ANSI/IEEE Standard 488.1-1987, IEEE Standard Digital Interface for Programmable

Instrumentation.

• ANSI/IEEE Standard 488.2-1987, IEEE Standard Codes, Formats, Protocols, and Common

Commands.

• NAT4882BPL IEEE 488.2 Controller Chip data sheet, National Instruments Corporation (part

number 340495-01).

Customer Communication

National Instruments wants to receive your comments on our products and manuals. We are

interested in the applications you develop with our products, and we want to help if you have

problems with them. To make it easy for you to contact us, this manual contains comment and

configuration forms for you to complete. These forms are in Appendix C, Customer

Communication, at the end of this manual.

NAT4882 Programmer Reference Manual x © National Instruments Corporation

Chapter 1 Introduction and General Description

This chapter contains a list of NAT4882 features, a functional description of the NAT4882, a list

of GPIB and interrupt capabilities, and a discussion of the addressing scheme used by the

NAT4882.

The NAT4882 is an IEEE 488.2 Controller chip designed to perform all the interface

functions defined in the IEEE 488.1-1987 specification and the additional requirements and

recommendations of the IEEE 488.2-1987 specification. The NAT4882 manages the

IEEE 488 interface functions with a set of control and status registers that increase the

throughput of driver software and simplify hardware and software design. The NAT4882

performs complete IEEE 488 Talker, Listener, and Controller functions and is

software-compatible with the NEC µPD7210 and TI TMS9914A chips. The compatibility

mode can be determined by either hardware or software. The NAT4882 is a

surface-mountable 68-pin Plastic Leaded Chip Carrier (PLCC) part.

NAT4882 Features

The National Instruments NAT4882 has all the features necessary to provide a high-performance

IEEE 488 interface. These features include the following:

• Can use all IEEE 488.1 interface functions and IEEE 488.2 requirements

- Source Handshake (SH1)

- Acceptor Handshake (AH1)

- Talker or Extended Talker (T5 or TE5)

- Listener or Extended Listener (L3 or LE3)

- Service Request (SR1)

- Remote/Local (RL1)

- Parallel Poll

remote configuration (PP1)

local configuration (PP2)

- Device Clear (DC1)

- Device Trigger (DT1)

- Controller, all capabilities (C1-C5)

- Busline Monitoring

- Preferred Implementation of requesting service

© National Instruments Corporation 1-1 NAT4882 Programmer Reference Manual

Introduction and General Description Chapter 1

• Can use six addressing modes

- Automatic single or dual primary addressing detection

- Automatic single primary with single secondary address detection

- Single or dual primary with multiple secondary addressing

- Multiple primary addressing

• Software-compatible with NEC µPD7210 and TI TMS9914A Controller chips

• Automatic EOS and/or NL message detection

• DMA support with automatic END message generation or automatic holdoff on terminal count

• Ability to detect bus synchronization

• Programmable T1 delay (2 µsec, 500 nsec, or 350 nsec)

• Automatic IEEE 488 command processing and undefined command read capability

• Programmable bus transceiver support (Texas Instruments, National Semiconductor,

Motorola, Intel)

NAT4882 Functional Description

The NAT4882 can be characterized as a bus translator, converting messages and signals

from the CPU into appropriate GPIB messages and signals. In GPIB terminology, the

NAT4882 implements GPIB board and device functions to communicate with the central

processor and memory. For the computer, the NAT4882 is an interface to the outside world.

Figure 1-1 shows a block diagram of a typical application using the NAT4882 to implement

an IEEE 488.2 interface.

NAT4882 Programmer Reference Manual 1-2 © National Instruments Corporation

Chapter 1 Introduction and General Description

CPU Bus

Control

Address

Decode

GPIB

XCVR

GPIB

NAT4882

Data

GPIB

Interrupt

XCVR

Figure 1-1. NAT4882 Implementation Block Diagram

In all applications, the NAT4882 must be connected to the GPIB via special transceivers. The

NAT4882 supplies the control signals necessary to interface to the IEEE 488 bus using several

different types of transceivers, such as the 75160 and 75162 from National Semiconductor or

Texas Instruments.

The NAT4882 interfaces to a CPU or local bus. Data is transferred to and from the registers

of NAT4882 from the local bus to perform configuration, check status, or transfer data

across the IEEE 488 bus. The NAT4882 can interrupt the CPU on many conditions. The

NAT4882 also can use a Direct Memory Access (DMA) Controller for enhanced transfer

speed.

Figure 1-2 shows a block diagram of the NAT4882.

© National Instruments Corporation 1-3 NAT4882 Programmer Reference Manual

Introduction and General Description Chapter 1

D(7-0)

CS*

RS2-0

RD*

Accen

WR*

Paged

DRQ

Swap

Dack*

T/C

INT

CLK

Read/

Write

Control

Data-In

Command Pass Through

Command/Data Out

Address Status

Address Mode

Address 0/1

End-Of-String

Interrupt Mask 0, 1, 2

Interrupt Status 0, 1, 2

Timer

Serial Poll

CompareCompare

Message

Decoder

Interface

Functions

SH1

AH1

T5/TE5

L3/LE3

SR1

RL1

PP1/PP2

DC1

DT1

C1-C5

DIO(8-1)*

T/R3

T/R2*

TE

MA

TA

LA

REM

LOK

TRIG

CIC

SC

Reset*

Mode

Parallel Poll

Aux A, B, E, F, G, I

SASR

Auxiliary

Command Decoder

KEY/CSR

Figure 1-2. NAT4882 Block Diagram

RSV Gen

EOI Gen

STB Out

SYNC

Bus Status

and Control

GPIB

Control

Keyrst*

KeyDQ

Keyclk

NAT4882 Programmer Reference Manual 1-4 © National Instruments Corporation

Chapter 1 Introduction and General Description

The interface includes the following major components:

• Read/Write Control converts the CPU signals presented to the NAT4882 to read and write

signals for each internal register.

• Internal NAT4882 Registers configure and control the operation of the NAT4882. They

transfer data between the NAT4882 and the GPIB bus, report status information, and set the

operating modes. Each register is described in detail in Chapter 2, NAT4882 Interface

Registers.

• Interface Functions implement the interface functions described in the IEEE 488.1-1978

specification. The interface functions are controlled by some of the internal registers, and you

can use other internal registers to monitor their status. The interface functions drive and

receive the GPIB control signals and generate the signals to control the GPIB transceivers.

• Message Decoding receives the GPIB data lines and decodes the GPIB commands that affect

the operation of the interface functions.

GPIB Capabilities

Table 1-1 lists the capabilities of the NAT4882 in terms of the IEEE 488 standard codes.

Table 1-1. NAT4882 IEEE 488 Interface Capabilities

Capability Code Description

SH1 Complete Source Handshake capability

AH1 Complete Acceptor Handshake capability, DAC and RFD

Holdoff on certain events

T5 Complete Talker capability

Basic Talker

Serial Poll

Talk Only mode

Unaddressed on MLA

Send END or EOS

Dual primary addressing

TE5 Complete Extended Talker capability

Basic Extended Talker

Serial Poll

Talk Only mode

Unaddressed on MSA*LPAS

Send END or EOS

Dual extended addressing with software assist

(continues)

© National Instruments Corporation 1-5 NAT4882 Programmer Reference Manual

Introduction and General Description Chapter 1

Table 1-1. NAT4882 IEEE 488 Interface Capabilities (continued)

Capability Code Description

L3 Complete Listener capability

Basic Listener

Listen Only mode

Unaddressed on MTA

Detect END or EOS

Dual primary addressing

LE3 Complete Extended Listener capability

Basic Extended Listener

Listen Only mode

Unaddressed on MSA*TPAS

Detect END or EOS

Dual extended addressing with software assist

SR1 Complete Service Request capability

RL1 Complete Remote/Local capability with software

interpretation

PP1 Remote Parallel Poll configuration

PP2 Local Parallel Poll configuration with software assist

DC1 Complete Device Clear capability with software interpretation

DT1 Complete Device Trigger capability with software

interpretation

C1 through C5 Complete Controller capability

System Controller

Send IFC and take charge

Send REN

Respond to SRQ

Send interface messages

Received control

Parallel Poll

Take control synchronously or asynchronously

E1, E2 Provides an output signal (T/R3) that can be used to switch

the GPIB transceivers from Three-state drivers to open

Collector drivers during Parallel Polls

The NAT4882 has complete Source and Acceptor Handshake capability. It can operate as a basic

Talker or Extended Talker and can respond to a Serial Poll. If you place it in a talk-only mode, it

is unaddressed to talk when it receives its listen address. The NAT4882 GPIB interface can also

operate as a basic Listener or Extended Listener. If you place it in a listen-only mode, it is

unaddressed to listen when it receives its talk address. The NAT4882 can request service from

another Controller. The ability to place the NAT4882 in local mode is software-dependent. The

interface can conduct a Parallel Poll, although local configuration requires software assistance.

NAT4882 Programmer Reference Manual 1-6 © National Instruments Corporation

Chapter 1 Introduction and General Description

Device Clear and Trigger capability is included in the interface, but the interpretation is softwaredependent.

The NAT4882 includes all Controller functions, as specified by the IEEE 488 standard. These

functions include the capability to do the following:

• Act as System Controller

• Initialize the interface

• Send Remote Enable

• Respond to Service Request

• Send multiline command messages

• Receive control

• Pass control

• Conduct a Parallel Poll

• Take control synchronously or asynchronously

Interrupt Capabilities

You can enable and disable NAT4882 interrupt sources individually by using the three Interrupt

Mask Registers (IMR0, IMR1, and IMR2). All unmasked interrupt conditions in the NAT4882

are logically combined (ORed) before being driven on the NAT4882 IRQ line.

7210 Mode Interrupts

The interrupt conditions in 7210 mode are as follows:

• GPIB Data In (DI)

• GPIB Data Out (DO)

• END received (END RX)

• GPIB Command Out (CO)

• Remote Mode Change (REMC)

• GPIB Handshake Errors (ERR)

• Lockout Change (LOKC)

© National Instruments Corporation 1-7 NAT4882 Programmer Reference Manual

Introduction and General Description Chapter 1

• Address Status Change (ADSC)

• Secondary Address received (APT)

• Service Request received (SRQI)

• Trigger command received (DET)

• Device Clear received (DEC)

• Unrecognized command received (CPT)

• Status Byte Out (STBO)

• Interface Clear (IFC)

• Attention (ATN)

• Time Out (TO)

• GPIB Synchronized (SYNC)

For more information on the 7210 mode interrupt conditions, refer to Interrupt Status Register 0,

1, and 2 in the 7210 Mode Registers section of Chapter 2, NAT4882 Interface Registers.

9914 Mode Interrupts

The interrupt conditions in 9914 mode are as follows:

• GPIB Byte In (BI)

• GPIB Byte Out (BO)

• END message received (END)

• Serial Poll Active State (SPAS)

• Remote/Local Change (RLC)

• My Address Change (MAC)

• Group Execute Trigger (GET)

• Transmit Error (ERR)

• Unrecognized Command (UNC)

• Secondary Address received (APT)

• Device Clear Active State (DCAS)

NAT4882 Programmer Reference Manual 1-8 © National Instruments Corporation

Chapter 1 Introduction and General Description

• My Address (MA)

• Service Request received (SRQ)

• Interface Clear (IFC)

• Status Byte Out (STBO)

• Local Lockout Change (LLOC)

• Attention (ATN)

• Time Out (TO)

• Controller-in-Charge (CIC)

For more information on the 9914 mode interrupt conditions, refer to Interrupt Status

Register 0, 1, and 2 in the 9914 Mode Registers section of Chapter 2, NAT4882 Interface

Registers.

Addressing Schemes

Because the NAT4882 was designed to be completely compatible with the NEC µPD7210 or

TI TMS9914A, only three register select lines are available, providing access to eight

register locations. To include the additional features of the NAT4882, there are two methods

of accessing additional registers: the hidden registers method and the paged registers

method. The NAT4882 comes out of reset with a completely compatible register map so that

existing software for either chip can run with no modification. By accessing these additional

registers, features can be invoked under software control.

Hidden registers have always been a part of the µPD7210 chip, but their number has

increased in the NAT4882, and their use has been expanded to the TMS9914A chip. Hidden

registers provide additional write-only registers by using part of the data byte being written

as an address. The upper three or four bits of a write to the Auxiliary Mode Register

(AUXMR) in 7210 mode or the Accessory Register (ACCR) in 9914 mode select the register

to be written. The lower four or five bits contain the data written to the register.

You can add additional readable and writeable registers to the 7210 mode by using one of

two methods to page them into the locations of existing registers. If you issue the page-in

auxiliary command, the additional registers are paged in until after the next CPU access to

the NAT4882. If you use this method, you must issue the page-in command before every

access to a paged register. Alternately, you can page in the registers by asserting the Page-In

pin during an access. If you use this method, you can connect the Page-In pin to an additional

address line, so that the paged registers appear at a different offset, and the NAT4882

occupies sixteen register locations. This method is the more efficient of the two, and is

recommended unless it is necessary that the NAT4882 only occupy eight register locations.

© National Instruments Corporation 1-9 NAT4882 Programmer Reference Manual

Introduction and General Description Chapter 1

The TMS9914A chip has two unused readable locations and one unused writeable location

that are used to add additional registers. Four additional write-only registers, located at the

same offset, are added to the 9914 mode, and are made available by issuing a page-in

command. Each register has its own page-in command, and unlike in the 7210 mode, a CPU

access does not page out a register. You can only page out a register by issuing the page-in

command of another register or by issuing the clear page-in command. The two unused

readable locations are used for two new read-only registers after any page-in command has

been issued. If no page-in command is issued, the NAT4882 does not drive the data bus

when an unused location is accessed. The ACCEN pin indicates when registers have been

paged in.

NAT4882 Programmer Reference Manual 1-10 © National Instruments Corporation

Chapter 2 NAT4882 Interface Registers

This chapter contains information on the use of the NAT4882 internal program registers. It also

contains NAT4882 address maps and detailed descriptions of the NAT4882 interface registers.

Software written for the NAT4882 controls the GPIB interface through a set of hardware registers.

The internal registers of the NAT4882 IEEE 488.2 Controller are mapped between offsets 0 and 7

hex. Many of the registers are read-only or write-only. Some registers are not storage registers at

all, but buffers through which status signals can be read or through which control signals can be sent.

Two special register types are also located in the NAT4882: multiple hidden registers are accessed

through a single register space by using the upper data bits to distinguish the registers; Paged

registers are made accessible by writing a command to the NAT4882 before accessing the register.

The NAT4882 operates in two different compatibility modes: NEC µPD7210 mode and TI 9914A

mode. The registers are mapped differently for the two modes and some registers exist in only one

of the modes.

Note: Throughout this manual, 7210 mode is used to refer to the NEC µPD7210 software

compatibility mode, and 9914 mode is used to refer to the TI TMS9914A software

compatibility mode.

Register Description Format

The remainder of this chapter describes each register in the 7210 and 9914 compatibility modes.

Each register description gives the address, type, word size, and bit map of the register, followed by

a detailed description of each bit.

The bit map of each register shows a diagram of the register with the most significant bit (bit 7 for an

8-bit register) shown on the left, and the least significant bit (bit 0) shown on the right. A square is

used to represent each bit. Each bit is labeled with a name inside its square. An asterisk (*) after the

bit name indicates that the signal is active low. An asterisk is equivalent to an overbar.

In many of the registers, several bits are labeled with an X, indicating don't care bits. When one of

these registers is read, the don't care bits may appear set or cleared but should be ignored, as they

have no significance. When a register is written to, these bits should be written as zeros.

The terms set, set true, and set to one are synonymous. The terms clear, set false, set to zero, and

clear to zero are synonymous. The meanings of preset and reset are determined by the context in

which they are used. Bit signatures are written in uppercase letters.

The term addressed indicates that the interface has been configured to perform a function from the

GPIB side, while the term programmed means that it has been configured from the CPU interface

side. This distinction is important to make, because many functions, such as making the interface a

Talker or Listener, can be activated from either side.

© National Instruments Corporation 2-1 NAT4882 Programmer Reference Manual

NAT4882 Interface Registers Chapter 2

Where it is necessary to specify a particular bit of a register, the bit position appears as a decimal

number in square brackets after the mnemonic. For example, ISR1[1] indicates the DI bit of

Interrupt Status Register 1.

A minus sign (-) indicates logical negation. An ampersand (&) represents AND, and a plus sign (+)

represents OR in logical expressions.

All numbers, except register offsets, are decimal unless specified otherwise. Register offsets are

given in hexadecimal notation.

Uppercase mnemonics are used for control, status, data registers, register contents, and interface

functions, as well as GPIB remote messages, commands, and logic states as defined in the IEEE 488

standard.

After a mnemonic of a name is defined, the mnemonic is used thereafter. Appendix B, Mnemonics

Key, contains a list of all mnemonics used in this manual, along with their type and name.

Mnemonics are assigned to messages, states, registers, bits, functions, and integrated circuits. Most

mnemonics contain some clue to their meaning. Table 2-1 contains a list of clues to look for.

Table 2-1. Clues to Understanding Mnemonics

Clue Mnemonic Probably Stands For:

Ends in IE Interrupt enable bit

Ends in EN Enable bit

4 letters,

ends in S

Ends in R,

R0, R1, R2

3 letters,

uppercase

3 letters,

lowercase

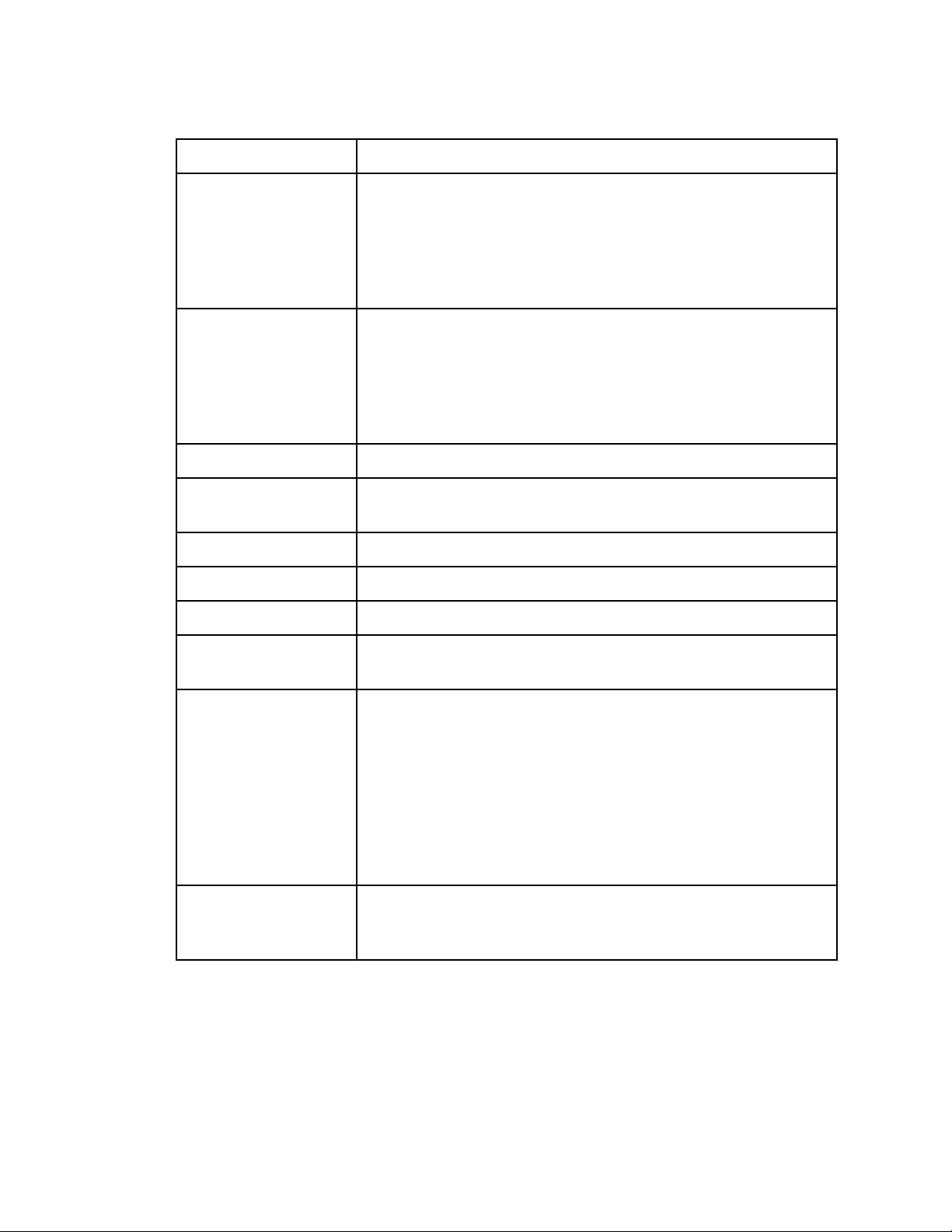

7210 Mode Registers

Interface function as defined in the

IEEE 488 standard

GPIB program register

Remote GPIB message

Local GPIB message

The 7210 mode register group consists of 31 registers.

Figure 2-1 shows the register map for the 7210 mode registers, and Figure 2-2 shows the 7210 mode

hidden registers. The 7210 hidden registers are accessed by writing to the auxiliary mode register

(AUXMR). The upper three or four bits written to the AUXMR determine which hidden register

will be accessed, and the lower four or five bits are written to that hidden register as shown in Figure

2-2. The non-shaded registers in Figure 2-1 are normally available in 7210 mode.

NAT4882 Programmer Reference Manual 2-2 © National Instruments Corporation

Chapter 2 NAT4882 Interface Registers

The paged registers in 7210 mode, which are shaded in Figure 2-1, can be accessed using two

methods. You can issue the Page-In auxiliary command, which makes the paged registers available

during the next CPU access to the NAT4882. After this paged access, the registers are paged out.

Alternately, you can assert the Page-In pin of the NAT4882 during the access to make the paged

registers available. The Page-In pin would commonly be connected as an additional address line so

that the paged registers would appear at an address different from the standard 7210 registers, unless

address space was limited.

The sections following Figures 2-1 and 2-2 contain detailed function descriptions of all 31 7210

mode registers.

Key

= 7210 Mode Paged Registers

R = Read Register

W = Write Register

7 6 5 4 3 2 1 0

DIR

CDOR

ISR1

IMR1

ISR2

IMR2

SPSR

KSR

KCR

SPMR

ADSR

ADMR

CPTR

SASR

AUXMR

ADR0

ISR0

IMR0

ADR

+0

+1

+2

+3

+4

+5

+6

DI7

CDO7

CPT

CPT IE

INT

0

S8

V3

0

S8

CIC

ton

CPT7

cdba

CNT2

X

cdba

GLINT

ARS

DI6

CDO6

APT

APT IE

SRQI

SRQI IE

PEND

V2

SWAP

rsv/RQS

ATN*

lon

CPT6

AEHS

CNT1

DT0

STBO

STBO IE

DT

DI5

CDO5

DET

DET IE

LOK

DMAO

S6

V1

MSTD

S6

SPMS

TRM1

CPT5

ANHS1

CNT0

DL0

NL

NLEE

DL

DI4

CDO4

END RX

END IE

REM

DMAI

S5

V0

NO T1

S5

LP AS

TRM0

CPT4

ANHS2

COM4

AD5-0

EOS

BTO

AD5

DI3

CDO3

DEC

DEC IE

CO

CO IE

S4

KEYDQ

KEYCLK

S4

TPAS

0

CPT3

ADHS

COM3

AD4-0

IFCI

IFCI IE

AD4

DI2

CDO2

ERR

ERR IE

LOKC

LOKC IE

S3

MODE

KEYDATEN

S3

LA

0

CPT2

ACRDY

COM2

AD3-0

ATNI

ATNI IE

AD3

DI1

CDO1

DO

DO IE

REMC

REMC IE

S2

0

KEYDATA

S2

TA

ADM1

CPT1

SH1A

COM1

AD2-0

TO

TO IE

AD2

DI0

CDO0

DI

DI IE

ADSC

ADSC IE

S1

0

KEYRST*

S1

MJMN

ADM0

CPT0

SH1B

COM0

AD1-0

SYNC

SYNC IE

AD1

R

W

R

W

R

W

R

R

W

W

R

W

R

R

W

R

R

W

W

ADR1

BSR

BCR

EOSR

+7

EOI

ATN S

ATN C

EOS7

DT1

DAV S

DAV C

EOS6

DL1

NDAC S

NDAC C

EOS5

AD5-1

NRFD S

NRFD C

EOS4

AD4-1

EOI S

EOI C

EOS3

AD3-1

SRQ S

SRQ C

EOS2

AD2-1

IFC S

IFC C

EOS1

AD1-1

REN S

REN C

EOS0

Figure 2-1. 7210 Mode Register Map

© National Instruments Corporation 2-3 NAT4882 Programmer Reference Manual

R

R

W

W

NAT4882 Interface Registers Chapter 2

Key

W = Write Register

7 6 5 4 3 2 1 0

AUXMR CNT2 CNT1 CNT0 COM4 COM3 COM2 COM1

PPR 0 1 1 U S P3 P2 P1

AUXRA 1 0 0 BIN XEOS REOS HLDE HLDA

AUXRB 1 0 1 ISS INV TRI SPEOI CPT EN

AUXRE 1 1 0 0 DHADT DHADC DHDT DHDC

AUXRF 1 1 0 1 DHATA DHALA DHUNTL DHALL

+5

COM0

W

W

W

W

W

W

AUXRG 0 1 0 0 NTNL RPP2 DISTCT CHES

AUXRI 1 1 1 0 USTD PP2 ACC SISB

AUXRJ 1 1 1 1 TM3 TM2 TM1 TM0

W

W

W

Figure 2-2. 7210 Mode Hidden Registers

NAT4882 Programmer Reference Manual 2-4 © National Instruments Corporation

Chapter 2 NAT4882 Interface Registers

Data In Register (DIR)

Access: location 0 (not affected by the page-in auxiliary command or the Page-In pin)

Mode: µPD7210

Attributes: Read-Only

76543210R

DI7 DI6 DI5 DI4 DI3 DI2 DI1 DI0

The Data In Register (DIR) moves data from the GPIB to the computer when the interface is a

Listener. Incoming information is separately latched by this register when a write to the

Command/Data Out Register (CDOR) takes place, and is not destroyed. If the TLC is not in

continuous mode, GPIB data is latched in this register when ACDS1 & ~ATN and the DI bit in ISR1

is set . The Not Ready For Data (NRFD) message is asserted until the byte is read from the DIR.

The Acceptor Handshake (AH) completes automatically after the byte is read unless the TLC is in

Ready For Data (RFD) Holdoff mode. In that case, the GPIB Handshake is not finished until the

Finish Handshake (FH) auxiliary command is issued telling the NAT4882 to release the Holdoff. By

using the RFD Holdoff mode, the same byte may be read several times or a GPIB Talker may be

held off until the program is ready to proceed. This register can also be read by asserting the

DACK* and RD* pins. For more information on the RFD Holdoff mode, refer to the Auxiliary

Register A description later in this chapter.

DI1 is the least significant bit of the data byte and corresponds to GPIB data line DIO1. DI8 is the

most significant bit of the data byte and corresponds to GPIB DIO8.

Bit Mnemonic Description

7-0r DIR[7-0] GPIB Data lines DIO[8-1]

© National Instruments Corporation 2-5 NAT4882 Programmer Reference Manual

NAT4882 Interface Registers Chapter 2

Command/Data Out Register (CDOR)

Access: location 0 (not affected by the page-in auxiliary command or the Page-In pin)

Mode: µPD7210

Attributes: Write-Only

76543210

CDO7 CDO6 CDO5 CDO4 CDO3 CDO2 CDO1 CDO0

W

The Command/Data Out Register (CDOR) moves data from the computer to the GPIB when the

interface is the GPIB Talker or the Active Controller. Outgoing data is separately latched by this

register and is not destroyed by a read from the DIR. When a byte is written to the CDOR, the

NAT4882 GPIB Source Handshake (SH) function is initiated (that is, the local message nba is true)

and the byte is transferred to the GPIB. This register is also written on the assertion of the WR*

signal when DACK* is asserted. The CDOR is a transparent latch; therefore, changes on the CPU

data bus (D(7:0)) during write cycles to the CDOR are reflected on the GPIB data bus (DIO(8:1)).

Bit Mnemonic Description

7-0w CDO[7-0] GPIB Data lines DIO[8-1]

NAT4882 Programmer Reference Manual 2-6 © National Instruments Corporation

Chapter 2 NAT4882 Interface Registers

Interrupt Status Register 1 (ISR1)

Access: location 1 (not affected by the page-in auxiliary command or the Page-In pin)

Mode: µPD7210

Attributes: Read-Only

Bits are cleared when read and SISB=0

Interrupt Mask Register 1 (IMR1)

Access: location 1 (not affected by the page-in auxiliary command or the Page-In pin)

Mode: µPD7210

Attributes: Write-Only

76543210R

CPT APT DET END RX DEC ERR DO DI

CPT IE APT IE DET IE END IE DEC IE ERR IE DO IE DI IE

W

The Interrupt Status Register 1 (ISR1) is made up of eight Interrupt Status bits. The Interrupt Mask

Register 1 (IMR1) is made up of eight Interrupt Enable bits that directly correspond to the Interrupt

Status bits in ISR1. As a result, ISR1 and IMR1 service eight possible interrupt conditions, where

each condition has an Interrupt Status bit and an Interrupt Enable bit associated with it. If the

Interrupt Enable bit and the GLINT bit (in ISR0) is true when the corresponding status condition or

event occurs, a hardware interrupt request is generated. Bits in ISR1 are set and cleared by the

NAT4882 regardless of the status of the Interrupt bits in IMR1. If an interrupt condition occurs at

the same time ISR1 is being read, the NAT4882 holds off setting the corresponding Status bit until

the read has finished. All bits in IMR1 are cleared by a hardware reset.

Bit Mnemonic Description

7r CPT Command Pass Through bit

7w CPT IE Command Pass Through Interrupt Enable bit

The CPT bit flags the occurrence of any GPIB command not

recognized by the NAT4882, and all following GPIB secondary

commands when the Command Pass Through feature is enabled by the

CPT ENAB bit, AUXRB[0]w. Any GPIB command message

not decoded by the NAT4882 is treated as an undefined command (see

Table 2-3 for a list of commands recognized in 7210 mode). However,

any addressed command is automatically ignored when the NAT4882

is not addressed. The CPT can also flag the occurrence of a GPIB

command or group of commands specified by the AUXRE[3-2]w or

AUXRF[3-0]w bits.

© National Instruments Corporation 2-7 NAT4882 Programmer Reference Manual

NAT4882 Interface Registers Chapter 2

Bit Mnemonic Description

Undefined commands are read using the Command Pass Through

Register (CPTR). The NAT4882 holds off the GPIB Acceptor

Handshake in the Accept Data State (ACDS) until the program writes

the Valid or Non-Valid auxiliary command function code to the

AUXMR. If CPT ENAB is cleared, undefined commands are simply

ignored. However, commands specified by the AUXRE[3-2]w and

AUXRF[3-0]w are still flagged.

CPT is set by:

[UCG + ACG & (TADS + LADS)] & undefined & ACDS &

CPT ENAB

+ UDPCF & SCG & ACDS1 & CPT ENAB

+ DHADT & GET & ACDS

+ DHADC & (SDC + DCL) & ACDS

+ DHATA & TAG & ~UNT & ACDS

+ DHALA & LAG & ~UNL & ACDS

+ DHUNTL & (UNT + UNL) & ACDS

+ DHALL & (UCG + ACG + SCG) & ACDS

CPT is cleared by:

pon + (read ISR1) & ~SISB + (read CPT) & SISB

Notes

UCG: GPIB Universal Command Group message

ACG: GPIB Addressed Command Group message

GET: GPIB Group Execute Trigger message

SDC: GPIB Selected Device Clear message

DCL: GPIB Device Clear message

UNT: GPIB Untalk message

UNL: GPIB Unlisten message

TADS: GPIB Talker Addressed State

LADS: GPIB Listener Addressed State

defined: GPIB command automatically recognized and

executed by NAT4882

undefined: GPIB command not automatically recognized and

executed by NAT4882

ACDS: GPIB Accept Data State

CPT ENAB: AUXRB[0]w

SISB: AUXRI[0]w

DHADT: AUXRE[3]w

DHADC: AUXRE[2]w

DHATA: AUXRF[3]w

DHALA: AUXRF[2]w

DHUNTL: AUXRF[1]w

DHALL: AUXRF[0]w

UDPCF: Undefined Primary Command Function

SCG: GPIB Secondary Command Group message

pon: Power On Reset

NAT4882 Programmer Reference Manual 2-8 © National Instruments Corporation

Chapter 2 NAT4882 Interface Registers

Bit Mnemonic Description

TAG: GPIB Talk Address Group message

LAG: GPIB Listen Address Group message

read ISR1: Read the Interrupt Status Register 1

read CPTR: Read of the Command Pass Through Register

UDPCF is set by:

[UCG + ACG & (TADS + LADS)] & undefined & ACDS &

CPT ENAB

UDPCF is cleared by:

[(UCG + ACG) & defined + TAG + LAG] & ACDS + -(CPT

ENAB) + pon

6r APT Address Pass Through

6w APT IE Address Pass Through Interrupt Enable

The APT bit indicates that a secondary GPIB address has been

received and is available in the CPTR for inspection.

Note: The application program must check this bit when using

NAT4882 address mode 3.

When APT is set, the Data Accepted (DAC) message is held and the

GPIB Handshake stops until either the Valid or Non-Valid auxiliary

command is issued.

APT is set by:

ADM1 & ADM0 & (TPAS + LPAS) & SCG & ACDS

APT is cleared by:

pon + (read ISR1) & ~SISB + (Valid + Non-Valid) & SISB

Notes

ADM1: Address Mode Register bit 1, ADMR[1]w

ADM0: Address Mode Register bit 0, ADMR[0]w

SISB: Static Interrupt Status bits, AUXRI[0]w

Valid: Valid Auxiliary Command issued

Non-Valid: Non-Valid Auxiliary Command issued

TPAS: GPIB Talker Primary Addressed State

LPAS: GPIB Listener Primary Addressed State

SCG: GPIB Secondary Command Group

ACDS: GPIB Accept Data State

pon: Power On Reset

read ISR1: Read the Interrupt Status Register 1

© National Instruments Corporation 2-9 NAT4882 Programmer Reference Manual

NAT4882 Interface Registers Chapter 2

Bit Mnemonic Description

5r DET Device Execute Trigger bit

5w DET IE Device Execute Trigger Interrupt Enable bit

The DET bit indicates that the GPIB Group Execute Trigger (GET)

command was received while the NAT4882 was a GPIB Listener–that

is, while the NAT4882 was in DTAS.

DET is set by:

DTAS = GET & LADS & ACDS

DET is cleared by:

pon + (read ISR1) & ~SISB + clearDET

Notes

DTAS: GPIB Device Trigger Active State

pon: Power On Reset

read ISR1: Read the Interrupt Status Register 1

SISB: Static Interrupt Status Bits, AUXRI[0]w

clearDET: clearDET Auxiliary Command issued

4r END RX End Received bit

4w END IE End Received Interrupt Enable bit

The END RX bit is set when the NAT4882 is a Listener and the GPIB

uniline message, END, is received with a data byte from the GPIB

Talker, when the data byte in the DIR matches the contents of the End

Of String Register (EOSR) and REOS is set, or when the data byte in

the DIR matches the ASCII newline character (hex 0A) and NLEE is

set. The END bit is always set before the DI bit when a byte that sets

END is received.

END RX is set by:

LACS & (EOI + EOS & REOS + NL & NLEE) & ACDS

END RX is cleared by:

pon + (read ISR1) & ~SISB + clearEND

Notes

LACS: GPIB Listener Active State

EOI: GPIB End Or Identify Signal

EOS: GPIB End Of String message

NL: ASCII 'Newline' message (hex 0A)

ACDS: GPIB Accept Data State

NAT4882 Programmer Reference Manual 2-10 © National Instruments Corporation

Chapter 2 NAT4882 Interface Registers

Bit Mnemonic Description

pon: Power On Reset

read ISR1: Read the Interrupt Status Register 1

REOS: END on EOS Received bit, AUXRA[2]w

SISB: Static Interrupt Status Bits, AUXRI[0]w

NLEE: New Line End Enable, IMR0[5]w

clearEND: clearEND Auxiliary Command issued

3r DEC Device Clear bit

3w DEC IE Device Clear Interrupt Enable bit

The DEC bit indicates that either the NAT4882 received the GPIB

Device Clear (DCL) command or that the NAT4882 received the

GPIB Selected Device Clear (SDC) command while it was a GPIB

Listener. The NAT4882 is in DCAS.

DEC is set by:

DCAS = (SDC & LADS + DCL) & ACDS

DEC is cleared by:

pon + (read ISR1) & ~SISB + clearDEC

Notes

DCAS: GPIB Device Clear Active State

pon: Power On Reset

read ISR1: Read the Interrupt Status Register 1

SISB: Static Interrupt Status Bits, AUXRI[0]w

clearDEC: clearDEC Auxiliary Command issued

2r ERR Error bit

2w ERR IE Error Interrupt Enable bit

The definition of the ERR bit depends on the status of the NTNL bit.

If NTNL=0, the ERR bit indicates that the contents of the CDOR have

been lost. ERR is set when data is sent over the GPIB without a

specified Listener, when a byte is written to the CDOR during SIDS,

or when a transition from SDYS to SIDS has occurred. If NTNL=1,

the ERR bit indicates that the Source Handshake is attempting to send

data or commands across the bus and finds that there are no Listeners–

that is, that NDAC and NRFD are unasserted. Data is not lost, because

the Source Handshake will attempt to source the data or command as

soon as a Listener appears.

© National Instruments Corporation 2-11 NAT4882 Programmer Reference Manual

NAT4882 Interface Registers Chapter 2

Bit Mnemonic Description

ERR is set by:

~NTNL & TACS & SDYS & DAC & RFD

+ ~NTNL & SIDS & (write CDOR)

+ ~NTNL & (SDYS to SIDS)

+ NTNL & SDYS & EXTDAC & RFD

ERR is cleared by:

pon + (read ISR1) & ~SISB + clearERR

Notes

TACS: GPIB Talker Active State

SDYS: GPIB Source Delay State

DAC: GPIB Data Accepted message

EXTDAC: GPIB Data Accepted message asserted by a device

other than the NAT4882 Acceptor Handshake

RFD: GPIB Ready For Data message

SIDS: GPIB Source Idle State

write CDOR: Writing to the Command/Data Out Register

SDYS to SIDS: Transition from GPIB Source Delay State to

Source Idle State

pon: Power On Reset

SISB: Static Interrupt Status Bits, AUXRI[0]w

NTNL: No Talking when No Listener bit, AUXRG[3]w

clearERR: clearERR Auxiliary Command issued

read ISR1: Read the Interrupt Status Register 1

1r DO Data Out bit

1w DO IE Data Out Interrupt Enable bit

The DO bit indicates that the NAT4882, as GPIB Talker, is ready to

accept another data byte from the CPU for transmission to the GPIB.

The DO bit is cleared when a byte is written to the CDOR or when the

NAT4882 ceases to be the Active Talker.

DO is set by:

(TACS & SGNS & ~nba)

DO is cleared by:

~(TACS) + ~(SGNS) + nba + (read ISR1) & ~SISB

Notes

TACS: GPIB Talker Active State

SGNS: GPIB Source Generate State

nba: New Byte Available Local Message

SISB: Static Interrupt Status Bits, AUXRI[0]w

read ISR1: Read the Interrupt Status Register 1

NAT4882 Programmer Reference Manual 2-12 © National Instruments Corporation

Chapter 2 NAT4882 Interface Registers

Bit Mnemonic Description

0r DI Data In bit

0w DI IE Data In Interrupt Enable bit

The DI bit indicates that the NAT4882, as a GPIB Listener, has

accepted a data byte from the GPIB Talker.

DI is set by:

LACS & ACDS & ~(continuous mode)

DI is cleared by:

pon + (read ISR1) & ~SISB + (Finish Handshake) & (Holdoff

mode) + (read DIR)

Notes

LACS: GPIB Listener Active State

ACDS: GPIB Accept Data State

continuous

mode: Listen in Continuous Mode auxiliary command in

effect

SISB: Static Interrupt Status Bits, AUXRI[0]w

pon: Power On Reset

read ISR1: Read the Interrupt Status Register 1

finish

Handshake: Finish Handshake auxiliary command issued

Holdoff mode: RFD Holdoff state

read DIR: Read Data In Register

© National Instruments Corporation 2-13 NAT4882 Programmer Reference Manual

NAT4882 Interface Registers Chapter 2

Interrupt Status Register 2 (ISR2)

Access: location 2 (not affected by the page-in auxiliary command or the Page-In pin)

Mode: µPD7210

Attributes: Read-Only

Bits clear when read if SISB=0

Interrupt Mask Register 2 (IMR2)

Access: location 2 (not affected by the page-in auxiliary command or the Page-In pin)

Mode: µPD7210

Attributes: Write-Only

76543210R

INT SRQI LOK REM CO LOKC REMC ADSC

0 SRQI IE DMAO DMAI CO IE LOKC IE REMC IE ADSC IE

W

The Interrupt Status Register 2 (ISR2) consists of six Interrupt Status bits and two Internal Status

bits. The Interrupt Mask Register 2 (IMR2) consists of five Interrupt Enable bits and two Internal

Control bits. If the Interrupt Enable and GLINT bits (in ISR0) are true when the corresponding

status condition or event occurs, an interrupt request is generated. Bits in ISR2 are set and cleared

regardless of the status of the bits in IMR2. If the NAT4882 must set or clear a bit or bits in ISR2

while ISR2 is being read, the NAT4882 holds off setting or clearing the bit or bits until the read is

finished. All bits in IMR2 are cleared on a hardware reset.

Bit Mnemonic Description

7r INT Interrupt bit

This bit is the logical OR of all the Enabled Interrupt Status bits in

ISR0, ISR1 and ISR2, each one ANDed with its Interrupt Enable bit.

INT is set by:

Global IE & [(CPT & CPT IE) + (APT & APT IE) + (DET &

DET IE) + (ERR & ERR IE) + (END RX & END IE) + (DEC &

DEC IE) + (DO & DO IE) + (DI & DI IE) + (SRQI & SRQI IE)

+ (REMC & REMC IE) + (CO & CO IE) +

(LOKC & LOKC IE) + (ADSC & ADSC IE) + (STBO IE &

STBO) + (IFCI IE & IFCI) + (ATNI IE & ATNI) + (TO IE & TO)

+ (SYNC IE & SYNC)]

NAT4882 Programmer Reference Manual 2-14 © National Instruments Corporation

Chapter 2 NAT4882 Interface Registers

Bit Mnemonic Description

Notes

Global IE: Enable Interrupt on Command Pass Through bit

CPT: Command Pass Through bit

CPT IE: Enable Interrupt on Command Pass Through bit

APT: Address Pass Through bit

APT IE: Enable Interrupt on Address Pass Through bit

DET: Device Execute Trigger bit

DET IE: Enable Interrupt on Device Execute Trigger bit

ERR: Error bit

ERR IE: Enable Interrupt on Error bit

END RX: End Received bit

END IE: Enable Interrupt on End Received bit

DEC: Device Clear bit

DEC IE: Enable Interrupt on Device Clear bit

DO: Data Out bit

DO IE: Enable Interrupt on Data Out bit

DI: Data In bit

DI IE: Enable Interrupt on Data In bit

SRQI: Service Request Input bit

SRQI IE: Enable Interrupt on Service Request Input bit

REMC: Remote Change bit

REMC IE: Enable Interrupt on Remote Change bit

CO: Command Output bit

CO IE: Enable Interrupt on Command Output bit

LOKC: Lockout Change bit

LOKC IE: Enable Interrupt on Lockout Change bit

ADSC: Address Status Change bit

ADSC IE: Enable Interrupt on Address Status Change bit

STBO: Status Byte Out bit

STBO IE: Enable Interrupt on Status Byte Out bit

IFCI: IFC Assertion bit

IFCI IE: Enable Interrupt on IFC Assertion bit

ATNI: ATN Assertion bit

ATNI IE: Enable Interrupt ATN Assertion bit

TO: Time Out bit

TO IE: Enable Interrupt on Time Out bit

SYNC: Synchronize bit

SYNC IE: Enable Interrupt on Synchronize bit

7w 0 Unused bit

Write zero to this bit.

6r SRQI Service Request Input bit

6w SRQI IE Service Request Input Interrupt Enable bit

The SRQI bit indicates that a GPIB Service Request (SRQ)

message has been received while the NAT4882 was

Controller-In-Charge (CIC). The term ~(RQS & DAV) ensures

© National Instruments Corporation 2-15 NAT4882 Programmer Reference Manual

NAT4882 Interface Registers Chapter 2

Bit Mnemonic Description

that if SRQ remains asserted while serial polling a device in APRS, the

SRQI bit will be set again, indicating that another device is also

requesting service. In version 2 of the NAT4882 (NAT4882B), if the

clear SRQI auxiliary command is issued and SRQ is still asserted, the

SRQI bit clears for one clock pulse and is set again. In version 1

(NAT4882A), the command clears the SRQI bit, and it is not reset.

Refer to the Key Status Register (KSR) to determine the version

number of your NAT4882 chip.

SRQI is set when:

(CIC & SRQ & -(RQS & DAV)) becomes true

where RQS = DIO7 & ~ATN & SPMS

SRQI is cleared by:

pon + (read ISR2) & ~SISB + clearSRQI

Notes

CIC: GPIB Controller-In-Charge

SRQ: GPIB Service Request message

RQS: GPIB Request Service message

SISB: Static Interrupt Status Bits, AUXRI[0]w

clearSRQI: clearSRQI Auxiliary Command Issued

DAV: GPIB Data Valid message

pon: Power On Reset

read ISR2: Read Interrupt Status Register 2

5r LOK Lockout bit

LOK is used, along with the REM bit, to indicate the status of the

NAT4882 GPIB Remote/Local (RL) function. If set, the LOK bit

indicates that the NAT4882 is in Local With Lockout State (LWLS) or

Remote With Lockout State (RWLS). LOK is a Non-Interrupt bit.

5w DMAO DMA Out Enable bit

Setting DMAO enables the NAT4882 to assert the DRQ line when the

set DO condition occurs. Once asserted the NAT4882 will keep the

DRQ pin asserted until the set DO condition is false.

4r REM Remote bit

This bit is set when the NAT4882 GPIB RL function is in either

Remote State (REMS) or Remote With Lockout State (RWLS). The

NAT4882 RL function transfers to one of these states when the

System Controller has asserted the Remote Enable line (REN), and the

CIC addresses the NAT4882 as a Listener.

NAT4882 Programmer Reference Manual 2-16 © National Instruments Corporation

Chapter 2 NAT4882 Interface Registers

Bit Mnemonic Description

4w DMAI DMA Input Enable bit

Setting DMAI enables the NAT4882 to assert the DRQ line when the

set DI condition occurs. Once asserted, the NAT4882 keeps the DRQ

pin asserted until any of the clear DI conditions (except read ISR1)

occurs.

3r CO Command Out bit

3w CO IE Command Out Interrupt Enable bit

CO = 1 indicates that the CDOR is empty and that another command

can be written to it for transmission over the GPIB without overwriting

a previous command.

CO is set by:

(CACS & SGNS & ~nba)

CO is cleared by:

(read ISR2) & ~SISB + ~CACS + ~SGNS + cdba

Notes

CACS: GPIB Controller Active State

SGNS: GPIB Source Generate State

SISB: Static Interrupt Status Bits, AUXRI[0]w

nba: New Byte Available local message

read ISR2: Read the Interrupt Status Register 2

2r LOKC Lockout Change bit

2w LOKC IE Lockout Change Interrupt Enable bit

LOKC is set if there is a change in the LOK bit, ISR2[5]r, (LOCS<–

>LWLS or REMS<–>RWLS).

LOKC is set by any change in LOK.

LOKC is cleared by:

pon + (read ISR2) & ~SISB + clearLOKC

Notes

LOK: ISR2[5]r

pon: Power On Reset

SISB: Static Interrupt Status Bits, AUXRI[0]w

clearLOKC: clearLOKC auxiliary command issued

read ISR2: Read the Interrupt Status Register 2

© National Instruments Corporation 2-17 NAT4882 Programmer Reference Manual

NAT4882 Interface Registers Chapter 2

Bit Mnemonic Description

1r REMC Remote Change bit

1w REMC IE Remote Change Interrupt Enable bit

REMC is set when there is a change in the REM bit, ISR2[4]r,

(LOCS<–>REMS or LWLS<–>RWLS).

REMC is set by any change in REM.

REMC is cleared by:

pon + (read ISR2) & ~SISB + clearREMC

Notes

REM: ISR2[4]r

pon: Power On Reset

SISB: Static Interrupt Status Bits, AUXRI[0]w

clearREMC: clearREMC auxiliary command issued

read ISR2: Read the Interrupt Status Register 2

0r ADSC Addressed Status Change bit

0w ADSC IE Addressed Status Change Interrupt Enable bit

ADSC is set when there is a change in one of the four bits TA, LA,

CIC, MJMN of the Address Status Register (ADSR).

ADSC is set by:

[(any change in TA) + (any change in LA) + (any change in

CIC) + (any change in MJMN)] & -(lon + ton)

ADSC is cleared by:

pon + (read ISR2) & ~SISB + clearADSC + lon + ton

Notes

TA: Talker Active bit, ADSR[1]r

LA: Listener Active bit, ADSR[2]r

CIC: Controller-In-Charge bit, ADSR[7]r

MJMN: Major/Minor bit, ADSR[0]r

lon: Listen Only bit, ADMR[6]w

ton: Talk Only bit, ADMR[7]w

pon: Power On Reset

SISB: Static Interrupt Status Bits, AUXRI[0]w

clearADSC: clearADSC auxiliary command issued

read ISR2: Read the Interrupt Status Register 2

ADSR: Address Status Register

ADMR: Address Mode Register

NAT4882 Programmer Reference Manual 2-18 © National Instruments Corporation

Chapter 2 NAT4882 Interface Registers

Serial Poll Status Register (SPSR)

Access: location 3 (except immediately after the page-in auxiliary command is issued or if

the Page-In pin is asserted)

Mode: µPD7210

Attributes: Read-Only

Serial Poll Mode Register (SPMR)

Access: location 3 (except immediately after the page-in auxiliary command is issued or if

the Page-In pin is asserted)

Mode: µPD7210

Attributes: Write-Only

76543210R

S8 PEND S6 S5 S4 S3 S2 S1

S8 rsv/RQS S6 S5 S4 S3 S2 S1

Bit Mnemonic Description

7r S8 Serial Poll Status bit 8

7w,

5-0r, S[6-1] Serial Poll Status bits 6 through 1

5-0w

Cleared by issuing the Chip Reset auxiliary command. These bits send

device- or system-dependent status information over the GPIB when

the NAT4882 is serial polled. When STBO IE = 0 and the NAT4882,

as the GPIB Talker, receives the GPIB multiline Serial Poll Enable

(SPE) command message, the NAT4882 transmits a byte of status

information, SPMR[7- 0], to the Controller-In-Charge after the

Controller Goes to Standby and becomes an Active Listener. In this

mode, the SPMR bits S[8,6-1] are double-buffered and if the register is

written to while the device is addressed during a serial poll (serial poll

active state, SPAS), the value written is saved. These bits are updated

when SPAS is terminated. When STBO IE = 1, the device STB

should be written to these bits in response to an STBO interrupt and

the value written will be sourced as the STB during that particular

serial poll.

W

© National Instruments Corporation 2-19 NAT4882 Programmer Reference Manual

NAT4882 Interface Registers Chapter 2

Bit Mnemonic Description

6r PEND Pending bit

PEND is set when rsv=1. PEND is cleared when the NAT4882 is in

Negative Poll Response State [NPRS] and the local Request Service

message [rsv] is false. Reading the PEND status bit can confirm that a

request was accepted and that the Status Byte (STB) was transmitted

(PEND=0).

6w rsv/RQS Request Service/ RQS bit

When STBO IE = 0, bit 6 is the rsv bit. The rsv bit generates the

GPIB local rsv message. When rsv is set and the GPIB Active

Controller is not serial polling the NAT4882, the NAT4882 enters the

Service Request State (SRQS) and asserts the GPIB SRQ signal.

When the Active Controller reads the STB during the poll, the

NAT4882 clears rsv at the Affirmative Poll Response State (APRS).

The rsv bit is also cleared by pon, by issuing the Chip Reset auxiliary

command, or by writing a zero (0) to it.

When STBO IE = 1, bit 6 is the RQS bit. The RQS bit should be

written in response to an STBO interrupt along with the STB. The

value written to the RQS bit is sourced on GPIB DIO7 (RQS) along

with the STB during that particular serial poll.

NAT4882 Programmer Reference Manual 2-20 © National Instruments Corporation

Chapter 2 NAT4882 Interface Registers

Key Status Register (KSR)

Access: location 3 (immediately after the page-in auxiliary command is issued or if

the Page-In pin is asserted)

Mode: µPD7210

Attributes: Read-Only

76543210R

V3 V2 V1 V0 KEYDQ MODE 0 0

The Key Status Register contains a value unique to each version of the NAT4882 and can be used to

distinguish itself from a standard µPD7210. It is also used to read data from an electronic key, if

attached.

Bit Mnemonic Description

7-4r V[3-0] The version number of the NAT4882. NAT4882A reads 0001.

NAT4882B reads 0010.

3r KEYDQ Key Data bit

KEYDQ returns the logic value of the KEYDQ pin. If you are using

an electronic key, the KEYDATEN bit in the KEY Register must be

cleared to read data from the key. Key data bits are read from the key

memory on the rising edge of KEYCLK.

2r MODE MODE bit

MODE returns the logic value of the MODE pin. The MODE pin