National ADC12010, ADC12040, ADC12020, ADC12L063 User Manual

August 2005

National Semiconductor

Rev F

Evaluation Board Instruction Manual

ADC12040 12-Bit, 40 Msps, 5 Volt, 380 mW A/D Converter

ADC12010 12-Bit, 10 Msps, 5 Volt, 160 mW A/D Converter

ADC12020 12-Bit, 20 Msps, 5 Volt, 185 mW A/D Converter

ADC12L063 12-Bit, 62 Msps, 3.3 Volt 354 mW A/D Converter

© 2001, 2002, 2003, 2004 National Semiconductor Corporation.

1 http://www.national.com

Table of Contents

1.0 Introduction.............................................................................................................................3

2.0 Board Assembly .....................................................................................................................3

3.0 Quick Start..............................................................................................................................4

4.0 Functional Description............................................................................................................4

4.1 Input (signal conditioning) circuitry............................................................................4

4.1.1 Single Input ...............................................................................................4

4.1.2 Dual Input..................................................................................................5

4.2 ADC reference circuitry .............................................................................................5

4.3 ADC clock circuit .......................................................................................................5

4.5 Digital Data Output....................................................................................................6

4.5 Power Supply Connections .......................................................................................6

4.6 Power Requirements.................................................................................................6

5.0 Installing the ADC12040 Evaluation Board ............................................................................6

6.0 Obtaining Best Results...........................................................................................................6

6.1 Clock Jitter.................................................................................................................6

6.2 Coherent Sampling....................................................................................................7

7.0 Evaluation Board Specifications.............................................................................................8

8.0 Hardware Schematic..............................................................................................................9

9.0 Evaluation Board Bill of Materials...........................................................................................10

A1.0 Operating in the Computer Mode.........................................................................................12

A2.0 Summary Tables of Test Points and Connectors ................................................................12

2 http://www.national.com

1.0 Introduction

These Design Kits (each consisting of an Evaluation

Board, National's WaveVision software and this manual)

is designed to ease evaluation and design-in of Nationals

ADC12040, ADC12010, ADC12020, or ADC12L063 12bit Analog-to-Digital Converter, which operate at speeds

up to 40 Msps, 10 Msps, 20 Msps and 62 Msps,

respectively. Further reference in this manual to the

ADC12040 is meant to also include the ADC12010,

ADC12020 and the ADC12L063, unless otherwise

specified or implied. Note that the maximum sample rate

capability of the WaveVision system in the Computer or

Automatic mode is 60 Msps.

The WaveVision software can be operated under

Microsoft Windows. The signal at the Analog Input is

digitized and can be captured and displayed on a PC

monitor as a dynamic waveform. The digitized output is

also available at Euro connector J2.

The software can perform an FFT on the captured data

upon command and, in addition to a frequency domain

plot, shows dynamic performance in the form of SNR,

SINAD, THD and SFDR.

A prototype area is available for building customized

circuitry.

The evaluation board can be used in either of two modes.

In the Manual mode suitable test equipment can be used

with the board to evaluate the ADC12040 performance.

In the Computer mode evaluation is simplified by

connecting the board to the WaveVision Digital Interface

Board (order number WAVEVSN BRD 3.0), which is

connected to a personal computer through a serial

communication port and running WaveVision software,

operating under Microsoft Windows. Or use WAVEVSN

BRD 4.0 when available on National's web site. Use the

WaveVision2 program (WAVEVSN2.EXE) or use

WaveVision 4.0 when available on National's web site.

The signal at the Analog Input to the board is digitized

and is available at pins B16 through B21 and C16

through C21 of J2. Pins A16 through A21 of J2 are

ground pins.

Provision is made for adjustment of the Reference

Voltage, V

REF

, with VR1.

2.0 Board Assembly

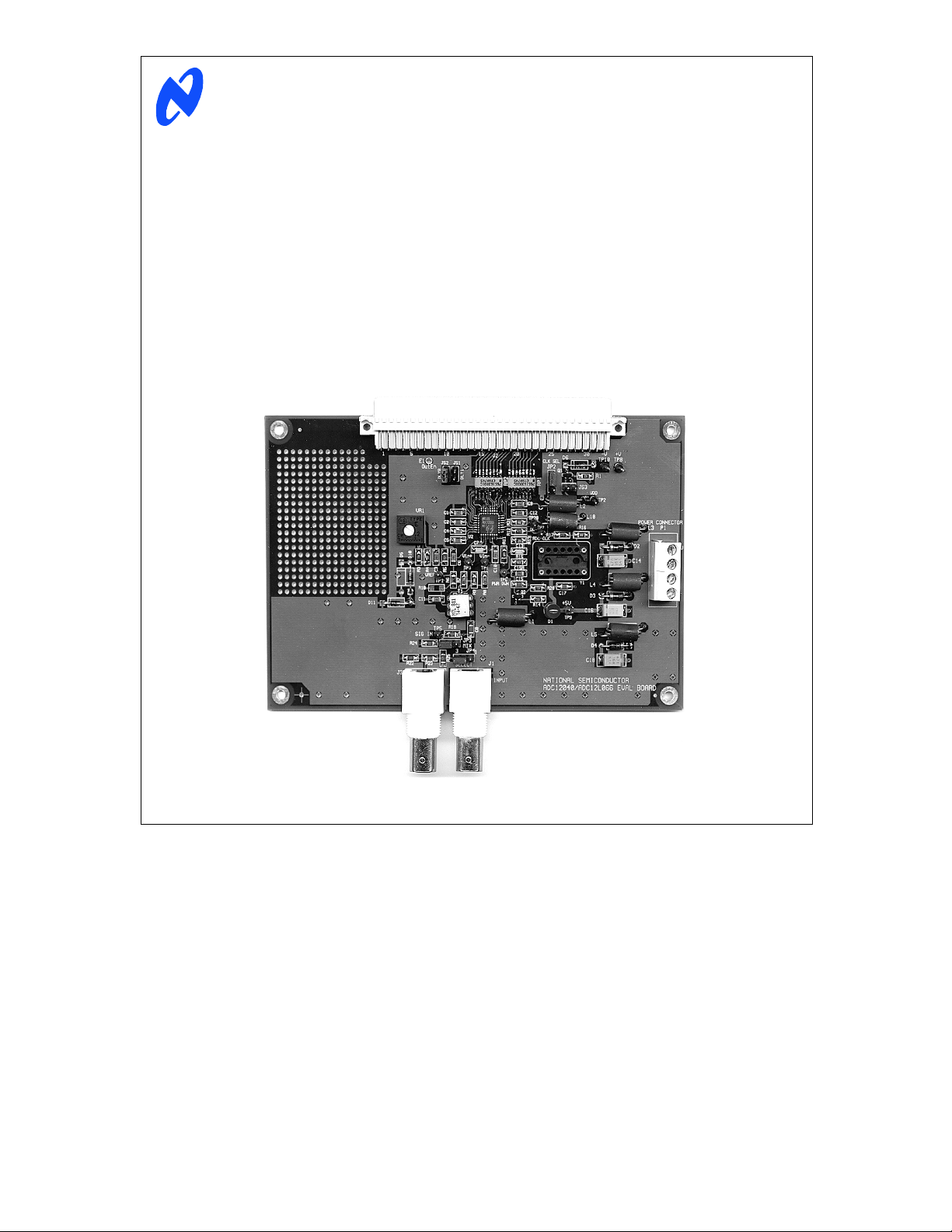

The ADC12040 Evaluation Board may come preassembled or as a bare board that must be assembled.

Refer to the Bill of Materials for a description of

components, to Figure 1 for major component placement

and to Figure 6 for the Evaluation Board schematic.

A breadboard area is provided for building customized

circuitry. For best performance, keep circuitry neat and

arrange components to provide short, direct connections.

JS0 & JS1

Detail

Standard

TP1

V

REF

JP3 & JP4

Detail

J1 Input

Position

JP2

Detail

Default

Position

JS3

Detail

Standard

VR1

Ref. Adj.

TP5

SIGNAL

INPUT

TP3

Vin+

JS1JS0

VR1

VREF

TP1

TP5

SIG IN

J3 J1

Analog

TP4

Vin-

Input

JP2

TP10

CLK

SELECT

RP2 RP1

U1

Vin+

Vin-

TP3

TP4

TP6

PWR DWN

T1

L1

JP3

MIX

JP4

SELECT

J1

J3

Analog

Input

TP20

OE-

ADC CLK

-V

-V

TP10+VTP8

CLK SEL

JP2

JS3

VDO

TP2

L2

L10

TP7

L3

Y1

L4

+5V

TP9

D1

L5

TP6

PWR

DWN

Figure 1. Component and Test Point Locations

3 http://www.national.com

TP8

+V

POWER CONNECTOR

P1

TP9

+5V

DR VD

ADC CLK

+V

GND

+5V

-V

Power

TP2

TP7

P1

3.0 Quick Start

Note: To develop the ADC clock, the Digital Interface

Board divides its on-board clock. In doing so, jitter is

introduced to the ADC clock which degrades the

observed performance of the ADC12040. See Section

6.0 Obtaining Best Results for an explanation of this

phenomenon and how to avoid it.

Refer to Figure 1 for locations of test points and major

components. For Stand-Alone operation:

1. Install an appropriate crystal into socket Y1. While

the oscillator may be soldered to the board, using a

socket will allow you to easily change clock

frequencies.

2. Connect a clean power supply to Power Connector

P1. Supply +5V at pin 3 of P1 to supply the Digital

Interface board. Supply +3.3V to pin 1 for the

ADC12L063, or +5V to pin 1 for the ADC12010,

ADC12020 and the ADC12040. Pin 2 is ground.

3. Use VR1 to set the reference voltage (V

is 2.0V for the ADC12040, ADC12010, or

ADC12020, or to 1.0V for the ADC12L063. V

can be measured at TP1.

4. To use the crystal oscillator located at Y1 to clock

the ADC, connect the jumper at JP2 to pins 2 and 3.

This is the default position. The ADC clock signal

may be monitored at TP7. Because of clock

isolation resistor R12 and the scope probe

capacitance, the clock signal at TP7 will appear

integrated.

5. Connect the jumper at JP3 between pins 1 and 2,

and the jumper at JP4 to pins 1 and 2 to select input

J1 only. This is the default position.

6. Connect a signal of 1.4 V

ADC12040, ADC12010 or the ADC12020, or 0.7

V

for the ADC12L063 from a 50-Ohm source to

P-P

Analog Input BNC J1. The ADC input signal can be

observed at TP5. Because of isolation resistor R18

and the scope probe capacitance, the input signal at

TP5 may not have the same frequency response as

the ADC input. Be sure to use a bandpass filter

before the Evaluation Board.

7. Adjust the input signal amplitude as needed to

ensure that the signals at TP3 and TP4 remains

within the valid signal range of 0V to V

8. The digitized signal is available at pins B16 through

B21 and C16 through C21 of J2. See board

schematic of Figure 6.

For Computer Mode operation:

NB: Be sure to read section 6.1 before using this

board in the Computer Mode.

1. Connect the evaluation board to the Digital Interface

Board. See the Digital Interface Board Manual for

operation of that board.

amplitude for the

P-P

REF

REF

), which

REF

.

2. Perform steps 2 and 3 of stand alone quick start,,

above.

3. Use of the crystal oscillator located at Y1 is

recommended to clock the ADC. To do so, connect

the jumper at JP2 to pins 2 and 3. This is the default

position. The ADC clock signal may be monitored at

TP7. Because of clock isolation resistor R12 and the

scope probe capacitance, the clock signal at TP7

will appear integrated.

4. Perform steps 5 through 7 of the Stand-Alone quick

start, above.

5. See the Digital Interface Board Manual for

instructions for setting the ADC clock frequency and

for gathering data.

4.0 Functional Description

The ADC12040 Evaluation Board schematic is shown in

Figure 6.

4.1 Input (signal conditioning) circuitry

The input signal to be digitized should be applied to BNC

connector J1. This 50 Ohm input is intended to accept a

low-noise sine wave signal of 2V peak-to-peak amplitude

for the ADC12040, ADC12010 and ADC12020 or 1V

peak-to-peak for the ADC12L063. To accurately evaluate

the dynamic performance of these converters, the input

test signal will have to be passed through a high-quality

bandpass filter with at least 14-bit equivalent noise and

distortion characteristics.

Signal transformer T1 provides single-ended to

differential conversion. The common mode voltage at the

ADC input is equal to the reference voltage of the ADC.

No scope or other test equipment should be connected to

TP3 or to TP4 while gathering data.

This evaluation board is capable of accommodating a

single input or two different inputs. These inputs are NOT

differential in nature, but are intended to mix two different

signals before presenting them to the ADC.

NOTE: If input frequency components above 30

MHz are required, remove capacitor C7 at the ADC

differential input pins.

4.1.1 Single Input

To evaluate the ADC12040 with a single input, connect

jumpers JP3 and JP4 in their default positions, as shows

in Figure 1. That is, short together pins 1 and 2 of JP3

and of JP4. Doing so provides a 50-Ohm input at J1. No

connection should be made to J3. This configuration is

appropriate for evaluation of dynamic performance

parameters.

4 http://www.national.com

Loading...

Loading...