MYSON MTV230MV64, MTV230MS64 Datasheet

MYSON

1024-byte RAM, 64K-byte

Character (per row) and window intensity control.

In System Programming function (ISP).

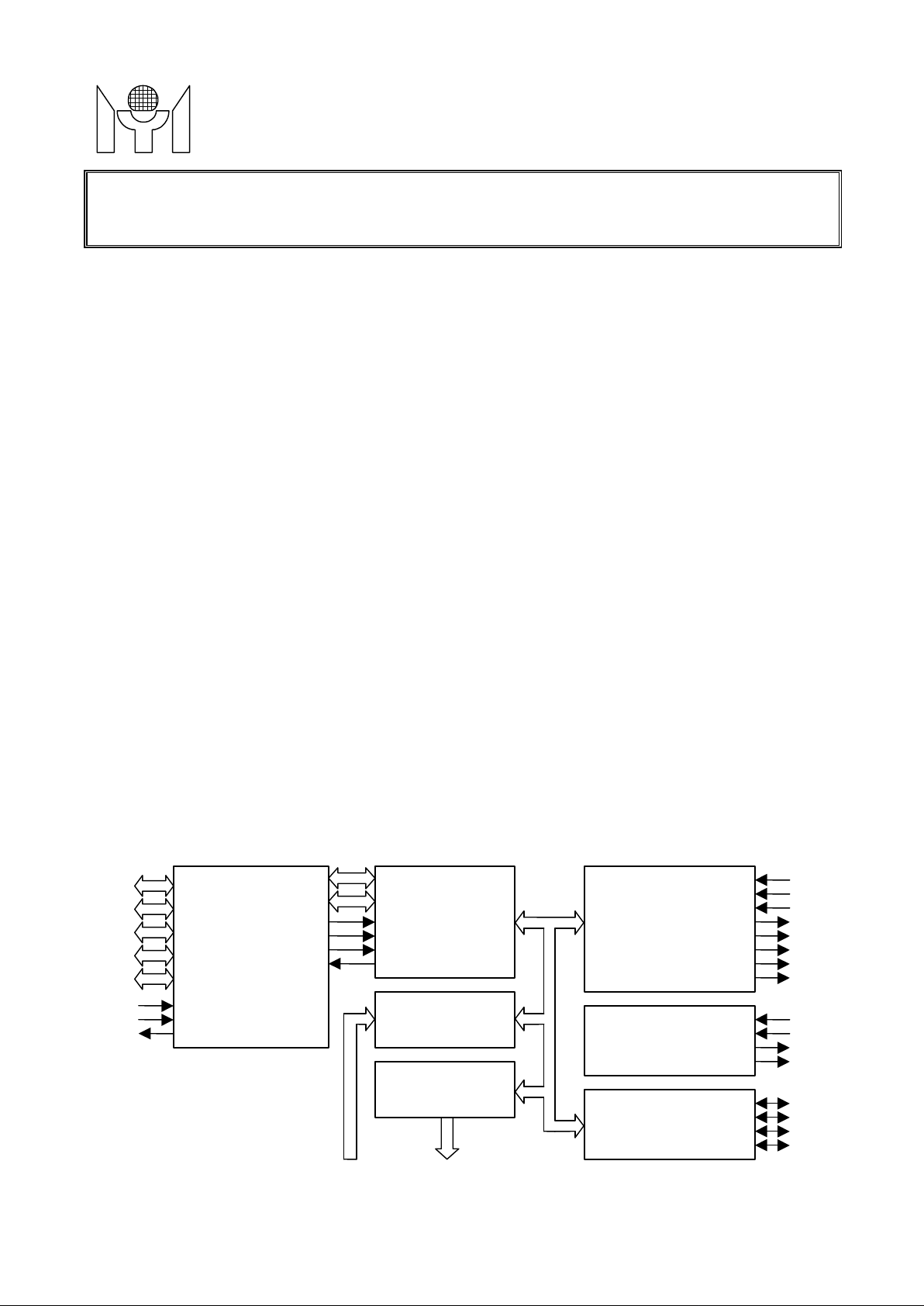

applications. It includes an 8051 CPU core, 1024-byte SRAM, OSD controller, 4 built-in PWM DACs, VESA

DDC interface, 4-channel A/D converter, a 64K-byte internal program Flash-ROM an d a 9K-word internal

CONTROL

INTERFACE

AD0-3

DA0-3

P0.0-7

P2.0-3

P0.0-7

P2.0-3

P1.0-7

P3.0-2

P3.4-5

P4.0-7

P5.0-7

CONTROL

MTV230M

TECHNOLOGY

(Rev 1.0)

8051 Embedded LCD Monitor Controller

with Flash OSD

FEATURES

• 8051 core, 12MHz operating frequency with double CPU clock option, 3.3V power supply.

•

• Maximum 4 channels of 5V open-drain PWM DAC.

• Maximum 32 bi-directional I/O pins.

• SYNC processor for composite separation/insertion, H/V polarity/frequency check and polarity adjustment.

• Built-in low power reset circuit.

• Compliant with VESA DDC2B/2Bi/2B+ standard.

• Dual slave IIC addresses.

• Single master IIC interface for internal device communication.

• Maximum 4-channel 6-bit ADC.

• Watchdog timer with programmable interval.

• OSD controller features:

. Full-screen display consists of 15 (rows) by 30 (columns) characters.

. Programmable OSD menu positioning for display screen center.

. 512 Flash-ROM fonts, with 12x18 dot matrix, including 480 standard fonts and 32 multi-color fonts.

.

. Character bordering, shadowing and blinking effect.

. Character height control (18 to 71 lines), double height and/or width control.

. 4 programmable windows with multi-level operation and programmable shadowing width/height/color.

•

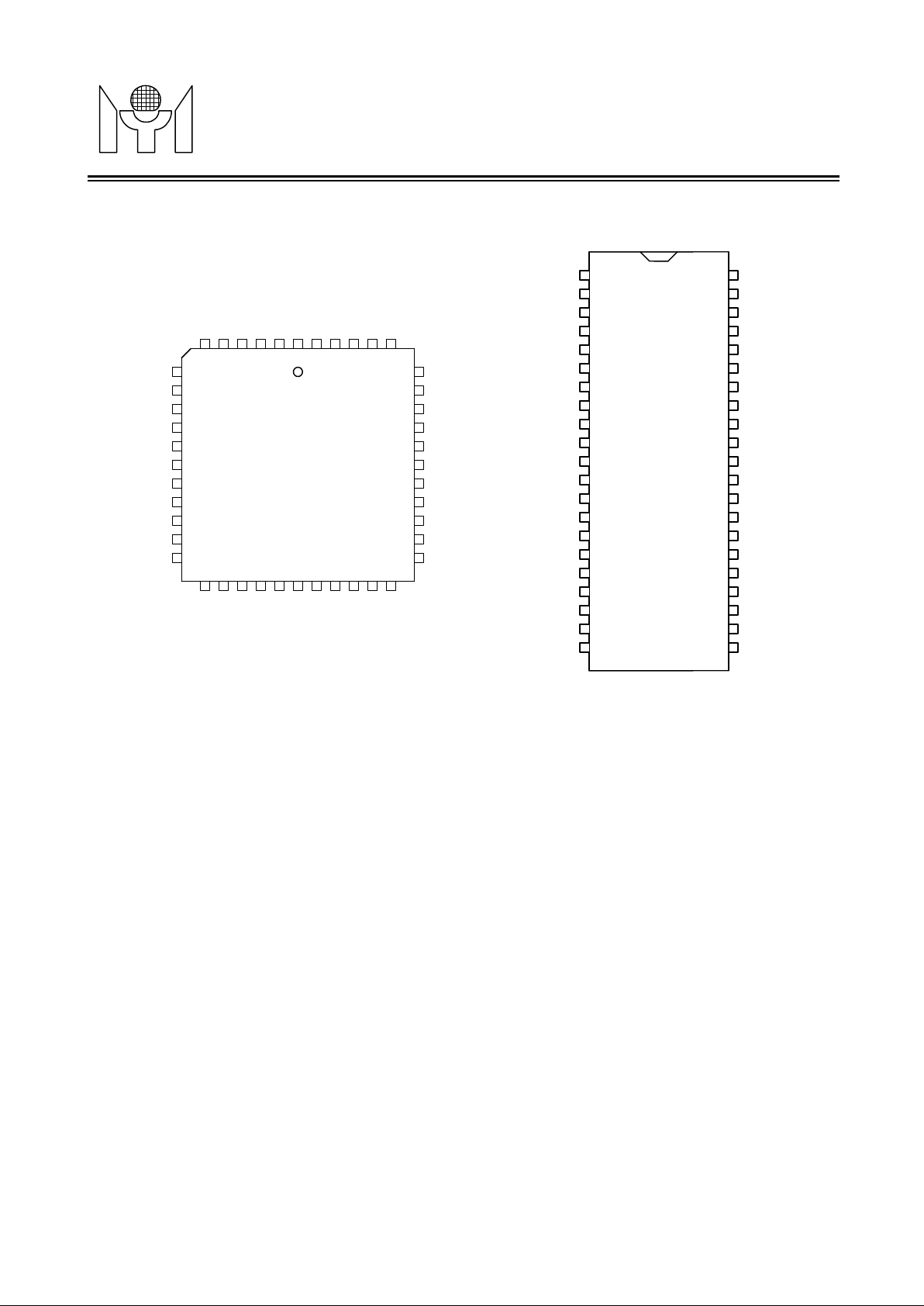

• 42-pin SDIP or 44-pin PLCC/QFP package.

program Flash-ROM.

GENERAL DESCRIPTIONS

The MTV230M micro-controller is an 8051 CPU core embedded device specially tailored to LCD Monitor

OSD character Flash-ROM.

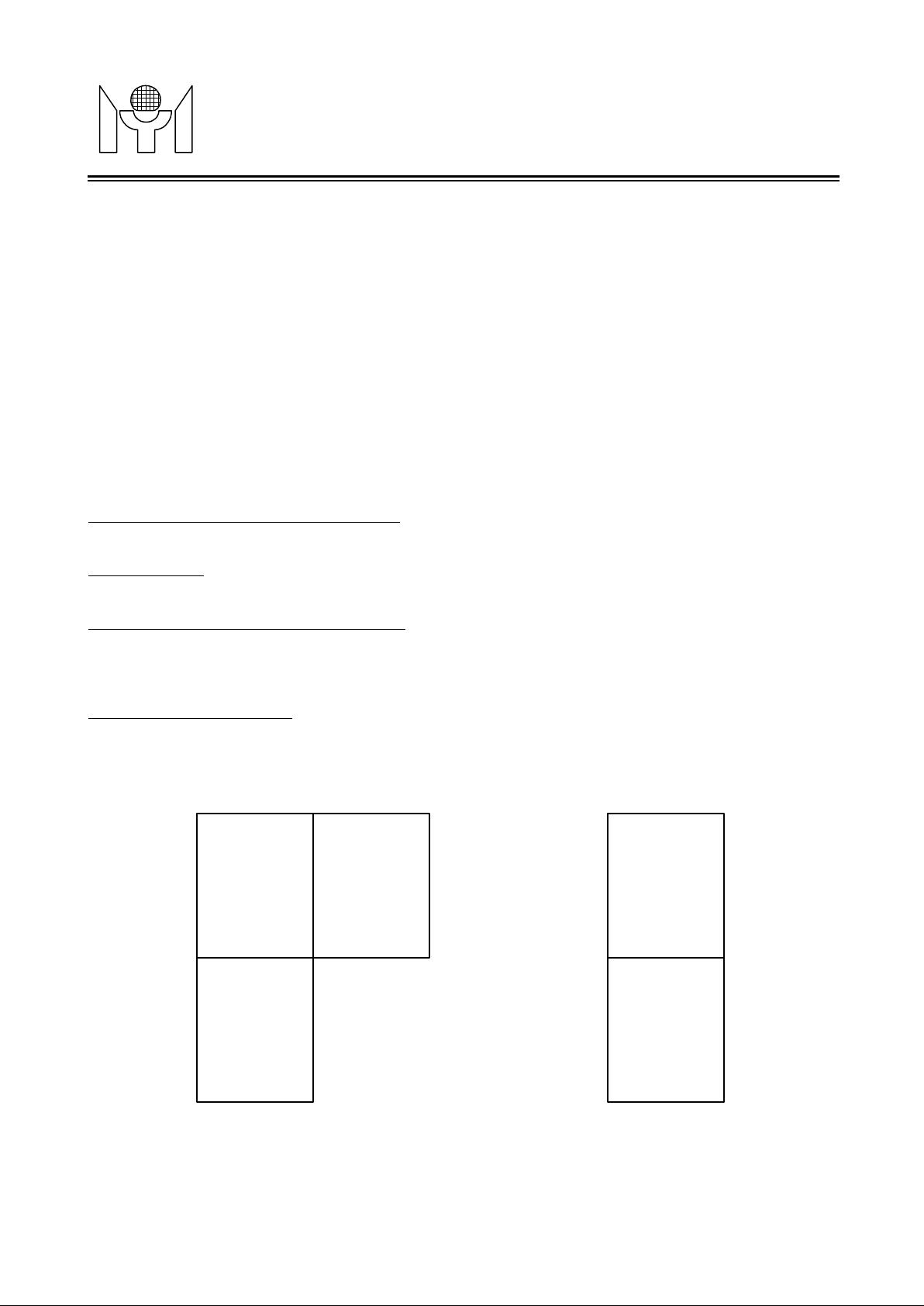

BL OCK DIAGRAM

OSDHS

OSDVS

XIN

ROUT

GOUT

BOUT

FBKG

INT

HSYNC

VSYNC

HBLANK

VBLANK

ISCL

ISDA

HSCL

HSDA

RST

X1

X2

8051

CORE

RD

WR

ALE

INT1

RD

WR

ALE

INT1

PWM DAC

XFR

ADC

OSD

H/VSYNC

DDC & IIC

This datasheet contains new product information. Myson Technology reserves the rights to modify the product specification without

notice. No liability is assumed as a result of the use of this product. No rights under any patent accompany the sale of the product.

Revision 1.0 - 1 - 2000/11/15

MYSON

P6.1/ISDA

P1.0

P1.1

P6.0/ISCL

P1.2

P1.3

VDD

RST

VSS

P3.4/T0

P3.5/T1

P4.6/HBLANK

P4.7/VBLANK

OSDHS

XIN

ROUT

GOUT

BOUT

FBKG

INT/P6.2

P5.7/DA3

P4.1/VSYNC

OSDVS

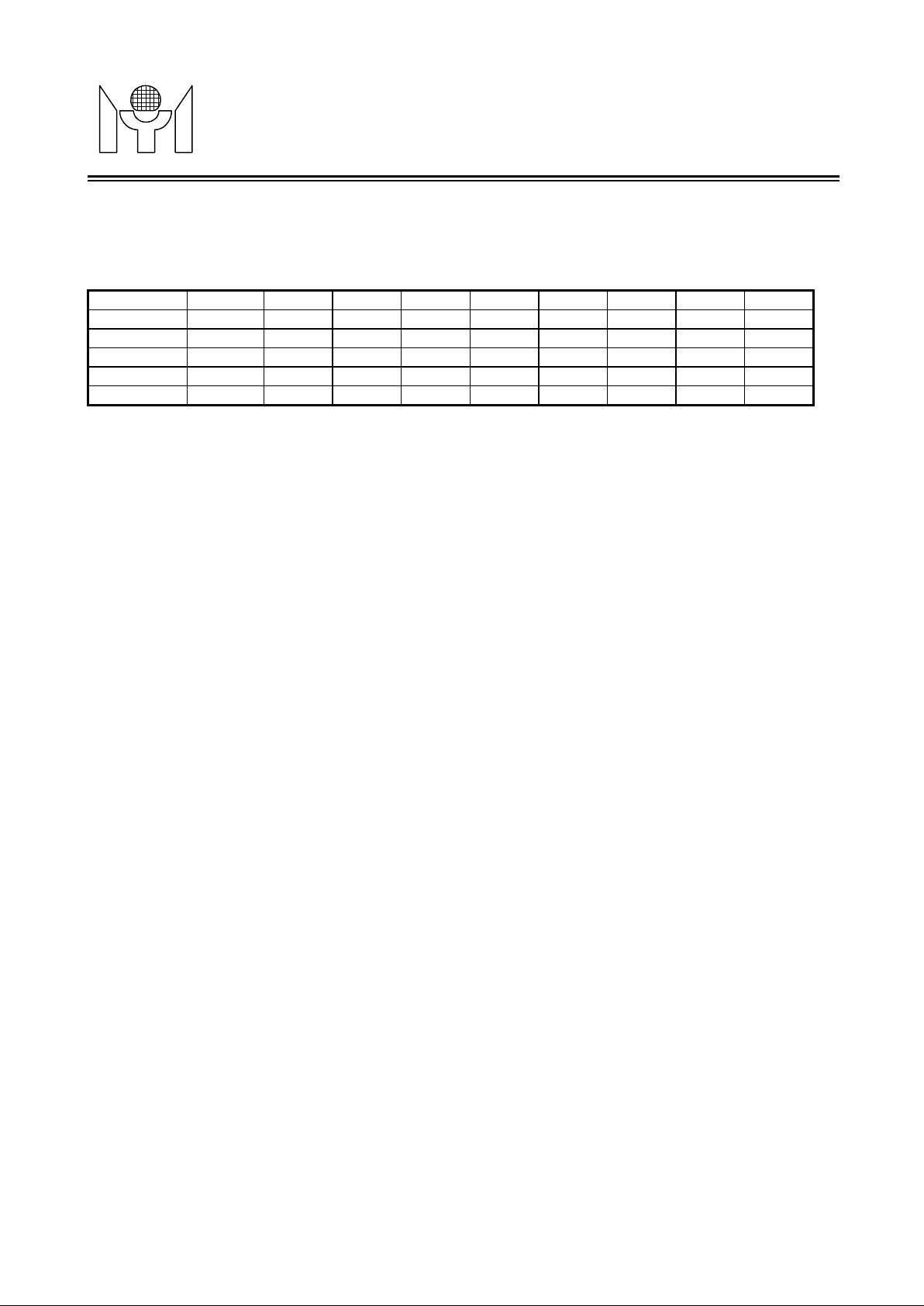

PLCC

242322212028272625

6543214443424140

19

18

P4.1/VSYNC

P4.0/HSYNC

P3.1/Txd/HSDA

P3.2/INT0

VSS

OSDVS

P4.7/VBLANK

P4.6/HBLANK

P3.4/T0

MTV230M

TECHNOLOGY

PIN CONNECTION

X1

7

X2

8

P4.5

9

P4.4

10

P4.3

11

P4.2

12

13

P4.0/HSYNC

P3.0/Rxd/HSCL

P3.1/Txd/HSDA

P3.2/INT0

14

15

16

17

MTV230M

44 Pin

39

38

37

36

35

34

33

32

31

30

29

P5.6/DA2

P5.5/DA1

P5.4/DA0

P5.3/AD3

P5.2/AD2

P5.1/AD1

P5.0/AD0

P1.7

P1.6

P1.5

P1.4

ROUT401

XIN

OSDHS

X1

X2

P4.5

P4.4

P4.3

P4.2

P3.0/Rxd/HSCL

VDD

RST

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

MTV230M

42 Pin

SDIP

(Rev 1.0)

GOUT

42

BOUT

41

FBKG

39

INT/P6.2

38

P5.7/DA3

37

P5.6/DA2

36

P5.5/DA1

35

P5.4/DA0

34

P5.1/AD1

33

P5.0/AD0

32

P1.7

31

P1.6

30

P1.5

29

P1.4

28

P1.3

27

P1.2

26

P1.1

25

P1.0

24

P6.1/ISDA

23

P6.0/ISCL

2221

P3.5/T1

Revision 1.0 - 2 - 2000/11/15

MYSON

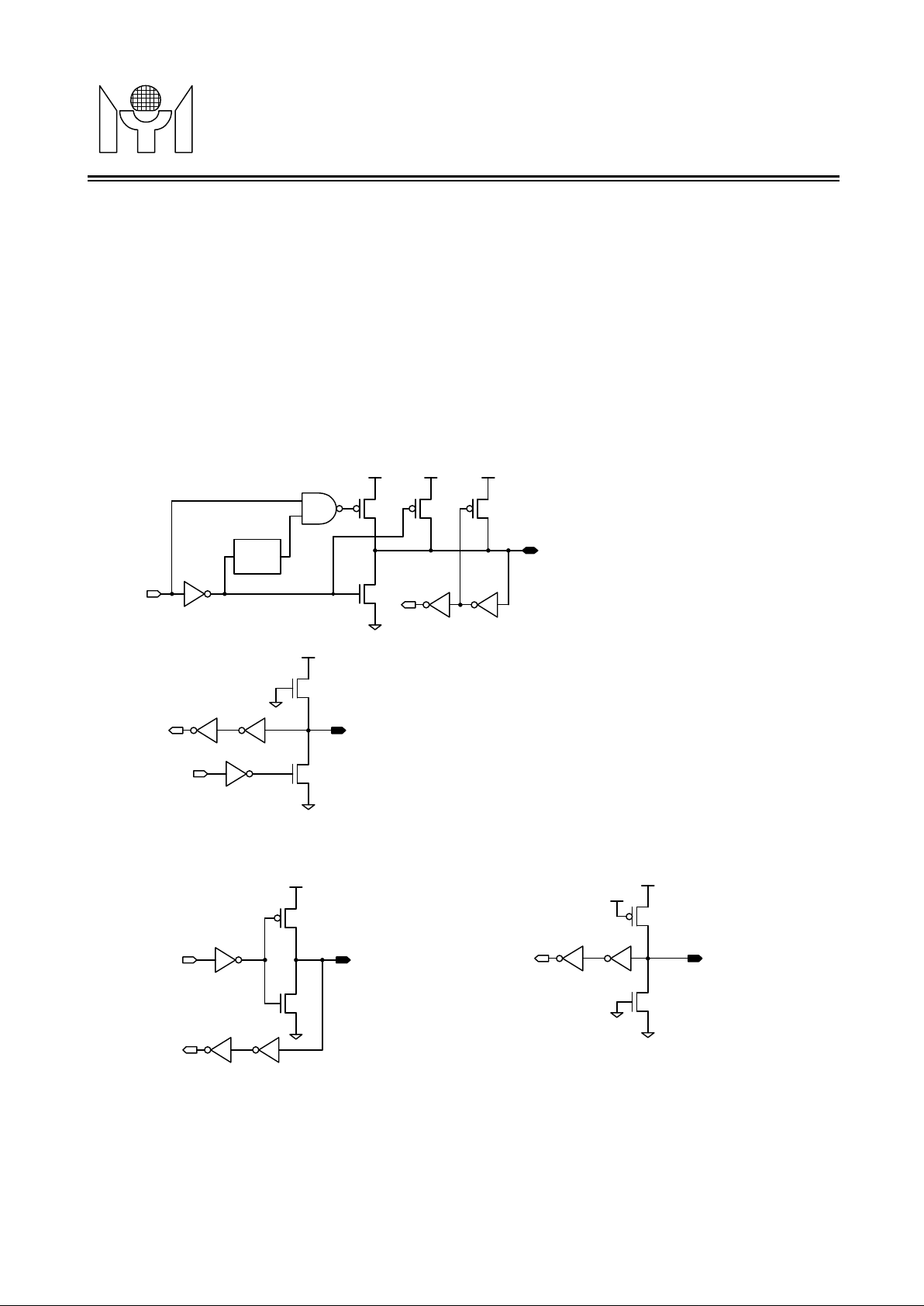

driving heavy load device.

CMOS Pin (Output Mod e)

CMOS Pin (Input Mo d e)

MTV230M

TECHNOLOGY

(Rev 1.0)

PIN CONFIGURATION

A “CMOS pin” can be used as Input or Output mode. To use these pins as output mode, S/W needs to set

the corresponding output enable control bit “Pxxoe” to 1. Otherwise, the “Pxxoe” should clear to 0. In Output

mode, these pins can sink and drive at least 4mA current.

A “5V open drain pin” means it can sink at least 4mA current but no drive current to VDD. It can be used as

input or output function and needs an external pull up resistor.

A “8051 standard pin” is a pseudo open drain pin. It can sink at least 4mA current when output low level, and

drive at least 4mA current for 160nS when output transit from low to high, then keep drive 1 00uA to maintain

the pin at a high level. It can be used as input or output function. It needs an external pull up resistor when

Output

Data

2 OSC

period

delay

4mA 10uA

4mA

Input

Data

120uA

Pin

8051 Stand ard Pin

Input

Data

Output

Data

Output

Data

Input

Data

4mA

4mA

Pxxoe = 1

No Current

Pin

4mA

Pin

5V Open Drain Pin

Input

Data

No Current

Pin

No Current

Pxxoe = 0

Revision 1.0 - 3 - 2000/11/15

MYSON

MTV230M

TECHNOLOGY

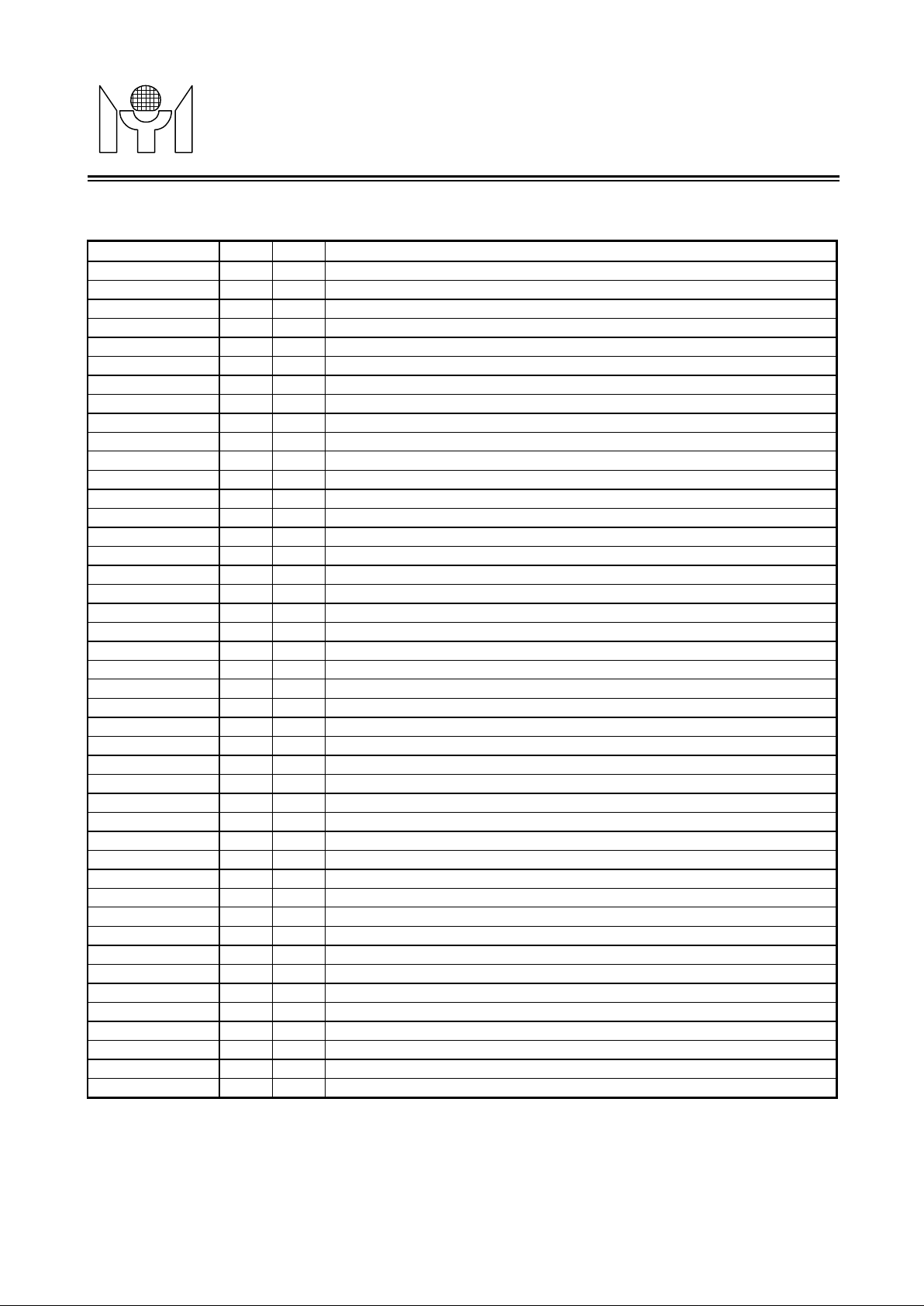

PIN DESCRIPTION

Name Type

RST

VDD

VSS

X2

X1

P1.0

P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

P3.0/Rxd /HSCL

P3.1/Txd/HSDA

P3.2/INT0

P3.4/T0

P3.5/T1

P4.7/VBLANK

P4.6/HBLANK

P4.5/HCLAM P

P4.4

P4.3

P4.2

P4.1/VSYNC

P4.0/HSYNC

P5.7/DA3

P5.6/DA2

P5.5/DA1

P5.4/DA0

P5.3/AD3

P5.2/AD2

P5.1/AD1

P5.0/AD0

P6.0/ISCL

P6.1/ISDA

INT/P6.2

FBKG

BOUT

GOUT

ROUT

XIN

OSDHS

OSDVS

O 8 Oscillator output

I/O 25 General purpose I/O (8051 standard)

I/O 26 General purpose I/O (8051 standard)

I/O 27 General purpose I/O (8051 standard)

I/O 28 General purpose I/O (8051 standard)

I/O 29 General purpose I/O (8051 standard)

I/O 30 General purpose I/O (8051 standard)

I/O 31 General purpose I/O (8051 standard)

I/O 32 General purpose I/O (8051 standard)

I/O 15 General purpose I/O / Rxd / Slave IIC clock (5V open drain)

I/O 16 General purpose I/O / Txd / Slave IIC data (5V open drain)

I/O 17 General purpose I/O / INT0 (8051 standard)

I/O 21 General purpose I/O / T0 (8051 standard)

I/O 22 General purpose I/O / T1 (8051 standard)

I/O 5 General purpose I/O / Vertical blank output (CMOS)

I/O 6 General purpose I/O / Horizontal blank output (CMOS)

I/O 9 General purpose I/O / Hclamp output (CMOS)

I/O 10 General purpose I/O (CMOS)

I/O 11 General purpose I/O (CMOS)

I/O 12 General purpose I/O (CMOS)

I/O 13 General purpose I/O / Vsync input (5V open drain)

I/O 14 General purpose I/O / Hsync or Xsync input (5V open drain)

I/O 40/38 General purpose I/O / PWM DAC output (5V open drain)

I/O 39/37 General purpose I/O / PWM DAC output (5V open drain)

I/O 38/36 General purpose I/O / PWM DAC output (5V open drain)

I/O 37/35 General purpose I/O / PWM DAC output (5V open drain)

I/O 36/- General purpose I/O / ADC Input (CMOS)

I/O 35/- General purpose I/O / ADC Input (CMOS)

I/O 34 General purpose I/O / ADC Input (CMOS)

I/O 33 General purpose I/O / ADC Input (CMOS)

I/O 23 General purpose output / Master IIC clock (5V open drain)

I/O 24 General purpose output / Master IIC data (5V open drain)

O 41/39 OSD intensity output / General purpose output (CMOS)

O 42/40 OSD fast blanking output (CMOS)

O 43/41 OSD blue color video signal output (CMOS)

O 44/42 OSD green color video signal output (CMOS)

O 1 OSD red color video signal output (CMOS)

#44/42

I 19 Active high reset

- 18 Positive Power Supply

- 20 Ground

I 7 Oscillator input

I 2 OSD pixel clock input (CMOS)

I 3 OSD vertical SYNC input (CMOS)

I 4 OSD horizontal SYNC input (CMOS)

Description

(Rev 1.0)

Revision 1.0 - 4 - 2000/11/15

MYSON

FUNCTIONAL DESCRIPTIONS

fetches its program code from the 64K bytes Flash in MTV230M. It uses Port0 and Port2 to access the

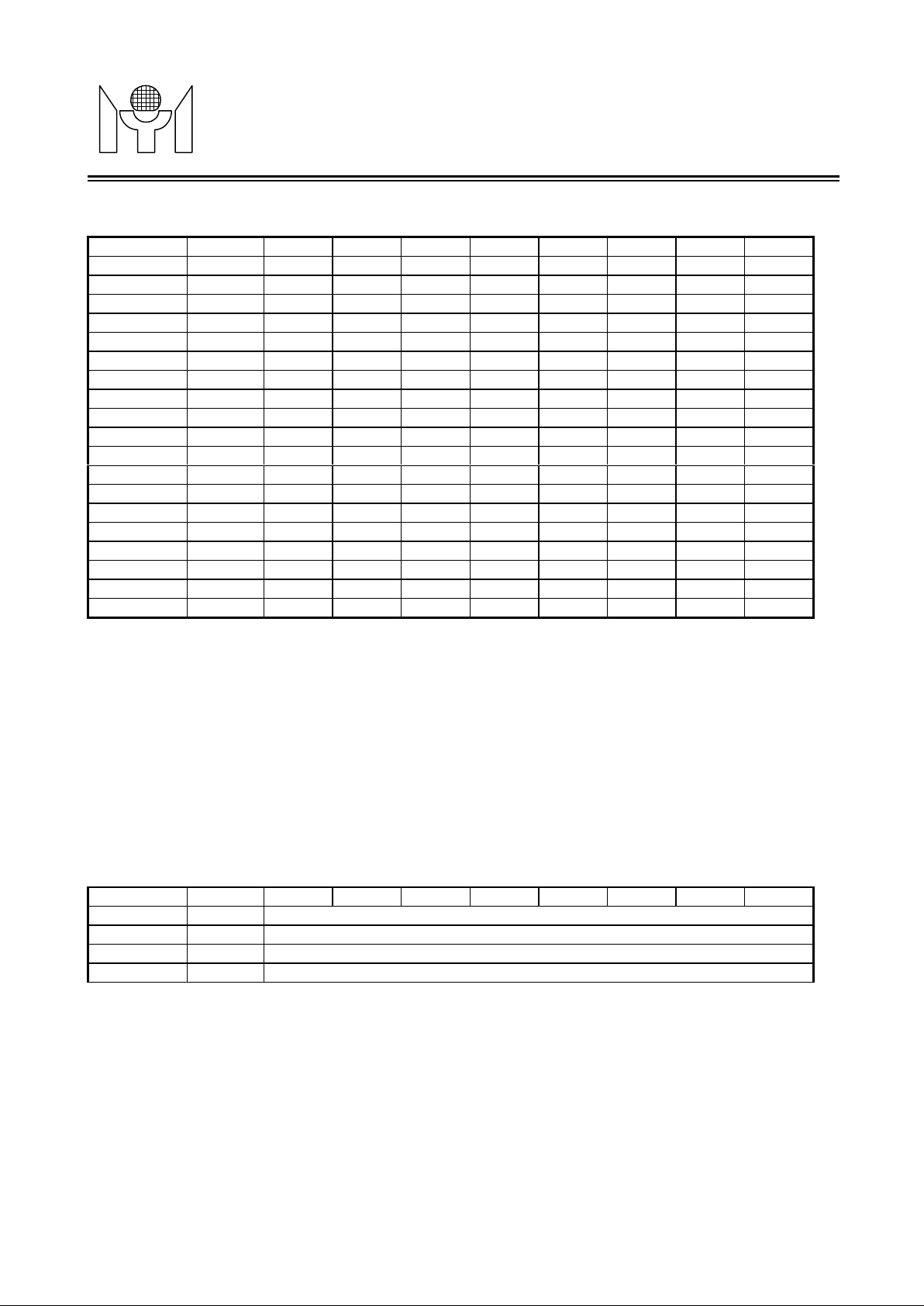

2. Memory Allo catio n

2.4 Auxiliary RAM (AUXRAM)

MTV230M

TECHNOLOGY

1. 8051 CPU Core

(Rev 1.0)

The CPU core of MTV230M is compatible with the industry standard 8051, which incl udes 256 bytes RAM,

Special Function Registers (SFR), two timers, five interrupt sources and serial interface. The CPU core

“external special function register” (XFR) and external auxiliary RAM (AUXRAM).

The CPU core can run at double rate when FclkE is set. Once the bit is set, the CPU runs as if a 24MHz X’tal

is applied on MTV230M, but the peripherals (IIC, DDC, H/V processor ) still run at the original frequency.

Note: All registers listed in this document reside in 8051’s external RAM area (XFR). For internal RAM

memory map, please refer to 8051 spec.

2.1 Internal Special Function Registers (SFR)

The SFR is a group of registers that are the same as standard 8051.

2.2 Internal RAM

There are total 256 bytes internal RAM in MTV230M, same as standard 8052.

2.3 External Special Function Registers (XFR)

The XFR is a group of registers allocated in the 8051 external RAM area F00h - FFFh. These registers are

used for OSD control or other special function. Program can use "MOVX" instruction to access these

registers.

There are total 768 bytes auxiliary RAM allocated in the 8051 external RAM area 800h - AFFh. Program can

use "MOVX" instruction to access the AUXRAM.

FFh

Internal RAM

Accessible by

addressing only

MOV A,@Ri

instruction)

80h

7Fh

Internal RAM

Accessible by

direct and indirect

addressing

indirect

(Using

SFR

Accessible by

direct addressing

FFFh

F00h

AFFh

XFR

Accessible by

indirect external

RAM addressing

(Using MOVX

instruction)

AUXRAM

Accessible by

indirect external

RAM addressing

(Using MOVX

instruction

00h

800h

Revision 1.0 - 5 - 2000/11/15

MYSON

PWMF

MTV230M

TECHNOLOGY

3. Chip Configu ratio n

The Chip Configuration registers define the chip pins function, as well as the connection, configuration and

frequency of the functional block.

Reg name addr bi t7 bit6 bit5 Bit4 bit 3 b it2 bit1 bit0

PADMOD

PADMOD

PADMOD

PADMOD

OPTION

PADMOD (w) : Pad mode control registers. (All are "0" in Chip Reset)

HIICE = 1 → pin “P3.0/Rxd/HSCL” is HSCL; pin “P3.1/Txd/HSDA” is HSDA.

IIICE = 1 → pin “P6.1/ISDA” is ISDA; pin “P6.0/ISCL” is ISCL.

HVE = 1 → pin “P4.7/VBLANK” is VBLANK; pin “P4.6/HBLANK” is HBLANK.

HclpE = 1 → pin “P4.5/HCLAMP” is HCLAMP.

FclkE = 1 → CPU is running at double rate.

P62E = 1 → pin “INT/P6.2” is P6.2.

DA3E = 1 → pin “P5.7/DA3” is DA3.

DA2E = 1 → pin “P5.6/DA2” is DA2.

DA1E = 1 → pin “P5.5/DA1” is DA1.

DA0E = 1 → pin “P5.4/DA0” is DA0.

AD3E = 1 → pin “P5.3/AD3” is AD3.

AD2E = 1 → pin “P5.2/AD2” is AD2.

AD1E = 1 → pin “P5.1/AD1” is AD1.

AD0E = 1 → pin “P5.0/AD0” is AD0.

P47oe = 1 → P4.7 is output pin.

P46oe = 1 → P4.6 is output pin.

P45oe = 1 → P4.5 is output pin.

P44oe = 1 → P4.4 is output pin.

P43oe = 1 → P4.3 is output pin.

P42oe = 1 → P4.2 is output pin.

F2Bh (w) HIICE IIICE HVE HclpE FclkE P62E

F2Ch (w) DA3E DA2E DA1E DA0E AD3E AD2E AD1E AD0E

F2Dh (w) P47oe P46oe P45oe P44oe P43oe P42oe P41oe P40oe

F2Eh (w) P57oe P56oe P55oe P54oe P53oe P52oe P51oe P50oe

F2Fh (w)

= 0 → pin “P3.0/Rxd/HSCL” is P3.0/Rxd; pin “P3.1/Txd/HSDA” is P3.1/Txd.

= 0 → pin “P6.1/ISDA” is P6.1; pin “P6.0/ISCL” is P6.0.

= 0 → pin “P4.7/VBLANK” is P4.7; pin “P4.6/HBLANK” is P4.6.

= 0 → pin “P4.5/HCLAMP” is P4.5.

= 0 → CPU is running at normal rate.

= 0 → pin “INT/P6.2” is INT.

= 0 → pin “P5.7/DA3” is P5.7.

= 0 → pin “P5.6/DA2” is P5.6.

= 0 → pin “P5.5/DA1” is P5.5.

= 0 → pin “P5.4/DA0” is P5.4.

= 0 → pin “P5.3/AD3” is P5.3.

= 0 → pin “P5.2/AD2” is P5.2.

= 0 → pin “P5.1/AD1” is P5.1.

= 0 → pin “P5.0/AD0” is P5.0.

= 0 → P4.7 is input pin.

= 0 → P4.6 is input pin.

= 0 → P4.5 is input pin.

= 0 → P4.4 is input pin.

= 0 → P4.3 is input pin.

DIV253 SlvAbs1 SlvAbs0 ENSCL Msel MIICF1 MIICF0

(Rev 1.0)

Revision 1.0 - 6 - 2000/11/15

MYSON

Selects 94KHz PWM frequency.

Selects 47KHz PWM frequency.

Selects 50KHz Master IIC frequency.

oe and P5(n)

MTV230M

TECHNOLOGY

= 0 → P4.2 is input pin.

P41oe = 1 → P4.1 is output pin.

= 0 → P4.1 is input pin.

P40oe = 1 → P4.0 is output pin.

= 0 → P4.0 is input pin.

P57oe = 1 → P5.7 is output pin.

= 0 → P5.7 is input pin.

P56oe = 1 → P5.6 is output pin.

= 0 → P5.6 is input pin.

P55oe = 1 → P5.5 is output pin.

= 0 → P5.5 is input pin.

P54oe = 1 → P5.4 is output pin.

= 0 → P5.4 is input pin.

P53oe = 1 → P5.3 is output pin.

= 0 → P5.3 is input pin.

P52oe = 1 → P5.2 is output pin.

= 0 → P5.2 is input pin.

P51oe = 1 → P5.1 is output pin.

= 0 → P5.1 is input pin.

P50oe = 1 → P5.0 is output pin.

= 0 → P5.0 is input pin.

(Rev 1.0)

OPTION (w) : Chip option configuration (All are "0" in Chip Reset).

PWMF = 1 →

= 0 →

DIV253 = 1 → PWM pulse width is 253 step resolution.

SlvAbs1,SlvAbs0 : Slave IIC block A's slave address length.

ENSCL = 1 → Enables slave IIC block to hold HSCL pin l ow while MTV230M is not able to

catch-up the speed of external master.

Msel = 1 → Master IIC block connects to HSCL/HSDA pins.

MIICF1,MIICF0 = 1,1 → Selects 400KHz Master IIC frequency.

4. I/O Ports

4.1 Port1

Port1 is a group of pseudo open drain pins. It can be use as general purpose I/O. The b ehavior Port is the

same as standard 8051.

= 0 → PWM pulse width is 256 step resolution.

= 1,0 → 5-bits slave address.

= 0,1 → 6-bits slave address.

= 0,0 → 7-bits slave address.

= 0 → Master IIC block connecst to ISCL/ISDA pins.

= 1,0 → Selects 200KHz Master IIC frequency.

= 0,1 →

= 0,0 → Selects 100KHz Master IIC frequency.

4.2 P3.0-2, P3.4-5

If these pins are not set as IIC pins, Port3 can be used as general purpose I/O, interrupt, UART and Timer

pins. The behavior of Port3 is the same as standard 8051.

4.3 Port4, Port5 and Port6

Port4 and Port5 are used as general purpose I/O. S/W needs to set the corresponding P4(n)

Revision 1.0 - 7 - 2000/11/15

oe

MYSON

to define whether these pins are input or output. Port6 is purely output.

Each PWM DAC output pulse width of the converter is controlled by an 8-bit register in XFR. The frequency

of PWM clock is 47KHz or 94KHz, selected by PWMF. And the total duty cycle step of these DAC outputs is

Pulse width of PWM DAC 0

Pulse width of PWM DAC 1

Pulse width of PWM DAC 2

Pulse width of PWM DAC 3

* All of PWM DAC converters are centered with value 80h after power on.

MTV230M

TECHNOLOGY

Reg name addr bi t7 bit6 bit5 b it4 bit3 bit 2 bi t1 bit0

PORT4

PORT4

PORT4

PORT4

PORT4

PORT4

PORT4

PORT4

PORT5

PORT5

PORT5

PORT5

PORT5

PORT5

PORT5

PORT5

PORT6

PORT6

PORT6

F30h(r/w) P40

F31h(r/w) P41

F32h(r/w) P42

F33h(r/w) P43

F34h(r/w) P44

F35h(r/w) P45

F36h(r/w) P46

F37h(r/w) P47

F38h(r/w) P50

F39h(r/w) P51

F3Ah(r/w) P52

F3Bh(r/w) P53

F3Ch(r/w) P54

F3Dh(r/w) P55

F3Eh(r/w) P56

F3Fh(r/w) P57

F28h(w) P60

F29h(w) P61

F2Ah(w) P62

(Rev 1.0)

PORT4 (r/w) : Port 4 data input/output value.

PORT5 (r/w) : Port 5 data input/output value.

PORT6 (w) : Port 6 data output value.

5. PWM DAC

253 or 256, selected by DIV253. If DIV253=1, writing FDH/FEH/FFH to DAC reg ister ge nerates stable high

output. If DIV253=0, the output will pulse low at least once even if content of the DAC reg ister is FFH. Writing

00H to DAC register generates stable low output.

Reg name addr bi t7 bit6 bit5 b it4 bit3 bit 2 bi t1 bit0

DA0

DA1

DA2

DA3

DA0-3 (r/w) : The output pulse width control for DA0-3.

F20h (r/w)

F21h (r/w)

F22h (r/w)

F23h (r/w)

Revision 1.0 - 8 - 2000/11/15

MYSON

inputs presence check, frequency counting, polarity detection and H/V output polarity control. The present

CVpre flag is set and users can select the extracted "CVSYNC" for the source of polarity check,

6.2 H/V Frequency Counter

VSYNC/CVSYNC is present or continuously updated when VSYNC/CVS YNC is non-present. The 12 bits

Hpol

CVpre

Vbpl

VSYNC

Vpre

Vfreq

Vpol

VBLANK

HSYNC

CVSYNC

Hpre

Hfreq

Hbpl

HBLANK

XOR

MTV230M

TECHNOLOGY

(Rev 1.0)

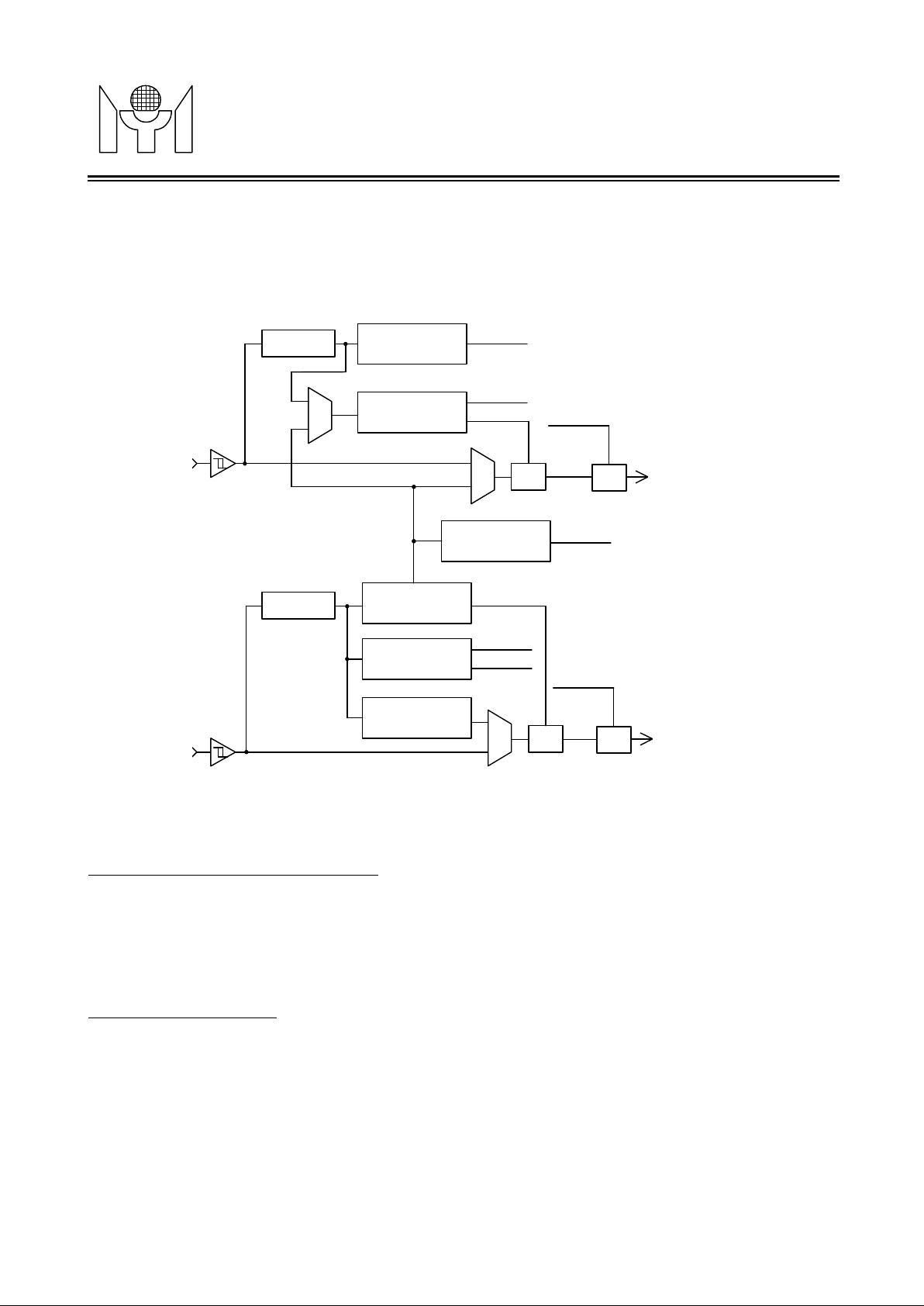

6. H/V SYNC Processing

The H/V SYNC processing block performs the functions of composite signal separation /insertion, SYNC

and frequency function block treat any pulse shorter than one OSC period as noise.

Digital Filter

Present

Check

Polarity Check &

Freq. Count

Present

Check

XOR

XOR

Digital Filter

Polarity Check &

Sync Seperator

Present Check &

Freq. Count

Composite

Pulse Insert

XOR

H/V SYNC Processor Block Diagram

6.1 Composite SYNC Separation/Insertion

The MTV230M continuously monitors the input HSYNC, if the vertical SYNC pulse can be extracted from the

input, a

frequency count, and VBLANK output. The CVSYNC will have 8us delay compared to the original signal.

The MTV230M can also insert pulse to HBLANK output during com posite active time of VSYNC. The width

of the insert pulse is 1/8 HSYNC period and the insertion frequency can adapt to original HSYNC. The insert

pulse of HBLANK can be disabled or enabled by setting “NoHins” control bit.

MTV230M can discriminate HSYNC/VSYNC frequency and saves the information in XFRs. The 14 bits

Hcounter counts the time of 64xHSYNC period, then loads the result into the HCNTH/HCNTL latch. The

output value will be [(128000000/H-Freq) - 1], updated once per VSYNC/CVSYNC perio d when

Vcounter counts the time between two VSYNC pulses, then loads the result into the VCNTH/VCNTL latch.

The output value will be (62500/V-Freq), updated every VSYNC/CVSYNC perio d. An extra overflow bit

indicates the condition of H/V counter overflow. The VFchg/HFchg interrupt is set when VCNT/HCNT value

changes or overflowes. Table 6.2.1 and table 6.2.2 show the HCNT/VCNT value under the operations of

12MHz.

Revision 1.0 - 9 - 2000/11/15

MYSON

CVpre flag interrupt may be disabled when S/W disables the composite function.

6.4 H/V Polarity Detect

The polarity functions detect the input HSYNC/VSYNC high and low pulse duty cycle. If the high pulse

duration is longer than that of the low pulse, the negative polarity is asserted; otherwise, positive polarity is

6.5 Output HBLANK/VBLANK Control and Polarity Adjust

mux selection and output polarity are S/W controllable.

flag is set each time when MTV230M detects a VSYNC pulse. The flag is cleared by S /W writing a "0".

MTV230M

TECHNOLOGY

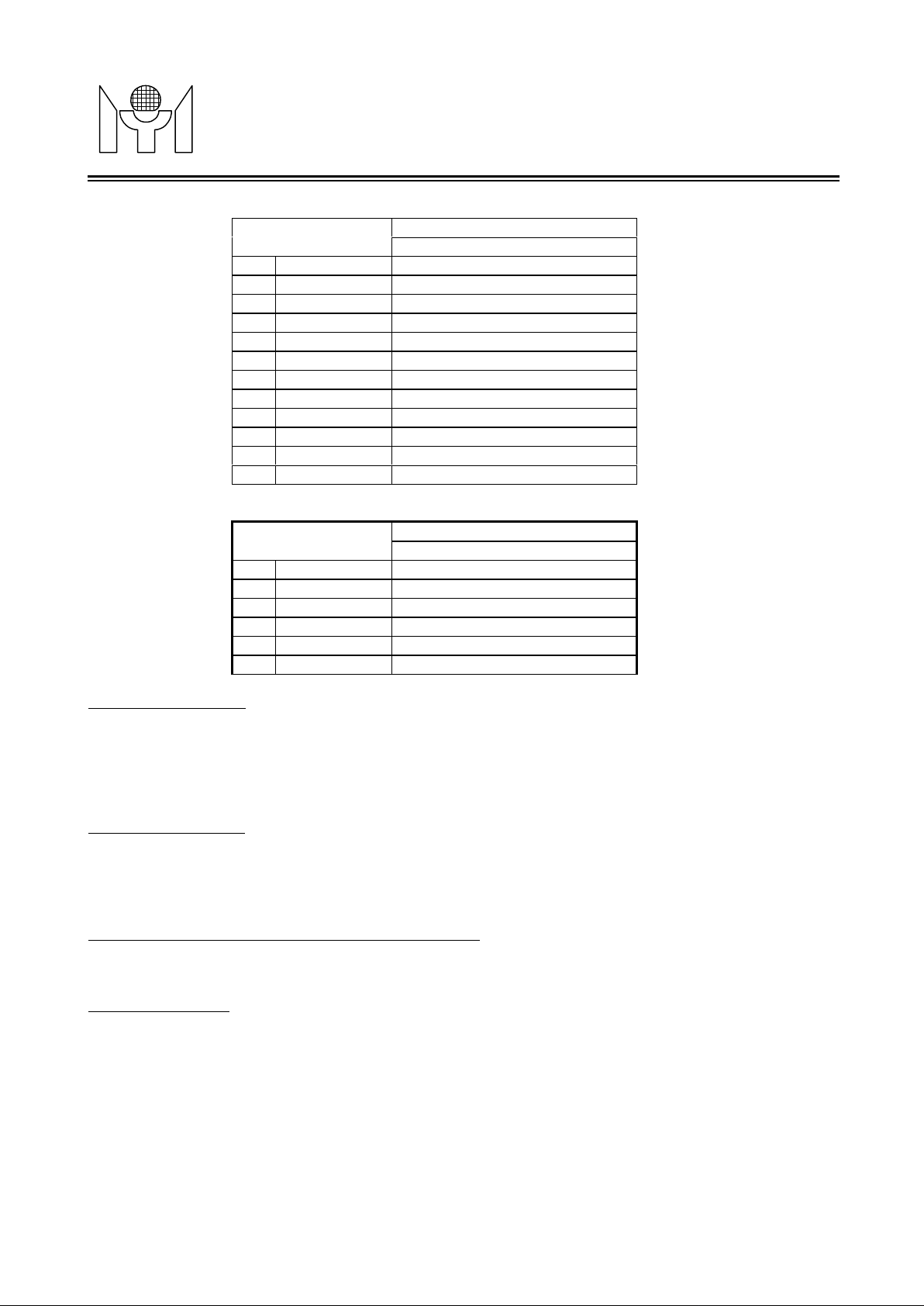

6.2.1 H-Freq Table

H-Freq(KHZ)

1

2

3

4

5

6

7

8

9

10

11

12

6.2.2 V-Freq Table

1

2

3

4

5

6

31.5

37.5

43.3

46.9

53.7

60.0

68.7

75.0

80.0

85.9

93.8

106.3

V-Freq(Hz)

56

60

70

72

75

85

Outpu t Value (14 bit s )

12MHz OSC (hex / dec)

Outpu t value (12bits)

12MHz OSC (hex / dec)

(Rev 1.0)

0FDEh / 4062

0D54h / 3412

0B8Bh / 2955

0AA8h / 2728

094Fh / 2383

0854h / 2132

0746h / 1862

06AAh / 1706

063Fh / 1599

05D1h / 1489

0554h / 1364

04B3h / 1203

45Ch / 1116

411h / 1041

37Ch / 892

364h / 868

341h / 833

2DFh / 735

6.3 H/V Present Check

The Hpresent function checks the input HSYNC pulse, Hpre flag is set when HSYNC is over 10KHz or

cleared when HSYNC is under 10Hz. The Vpresent function checks the input VSYNC pulse, the Vpre flag is

set when VSYNC is over 40Hz or cleared when VSYNC is under 10Hz. The HPRchg interrupt is set when

the Hpre value changes. The VPRchg interrupt is set when the Vpre/CVpre value changes. However, the

asserted. The HPLchg interrupt is set when the Hpol value changes. The VPLchg interrupt is set when the

Vpol value changes.

The HBLANK is the mux output of HSYNC and composite Hpulse. The VBLANK is the mux output of

VSYNC and CVSYNC. The

6.6 VSYNC Interrupt

The MTV230M checks the VSYNC input pulse and generates an interrupt at its leading edge. The VSYNC

Revision 1.0 - 10 - 2000/11/15

Loading...

Loading...