MYSON MTV004 Datasheet

MYSON

TECHNOLOGY

On-Screen Display Shrink Version

FEATURES

•

On-chip phase lock loop circuitry for multi-sync operation.

•

Horizontal input up to 100 KHz.

•

273-byte display registers to control full screen display.

•

Full screen display consisting of 10 rows by 24 characters.

•

128 alphanumeric characters or graphic symbols built in character ROM.

•

12 x 16 dot matrix per character.

•

Character by character color selection.

•

4 color selections in a total of 8 color combinations per row.

•

4-character size options available by doubling character height and/or width.

•

Programmable positioning for display screen center.

•

Character bordering and shadowing.

•

Programmable vertical character height for multi-sync operation.

•

Multi-level windowing effect.

•

Half tone and fast blanking output.

•

Compatible with both SPI bus and I2C interface through pin selection.

•

16-pin PDIP package.

MTV004

GENERAL DESCRIPTION

MTV004 is designed for use in monitor applications to display the built-in characters or symbols onto the

monitor screen. The display operation is enabled by transferring data and control information in the

microcontroller to RAM through a serial data interface. It can execute the full screen display automatically as

well as some specific functions such as character bordering, shadowing, double height, double width and color

control, frame positioning, vertical display height, and windowing effect.

BLOCK DIAGRAM

6

SSB

SCK

SDA

VFLB

HFLB

VCO

12

8

8

SERIAL DATA

INTERFACE

7

2

RAEN,CAEN

ARWDB

10

VERTD

5

HORD

2

RP

3

ADDRESS BUS

ADMINISTRATOR

6

CH

CHS

6

5

CONTROL LOGIC

PHASE LOCK LOOP

VERTICAL

CONTROL

LOGIC

HORIZONTAL

DATA

DAEN

2

RAEN,CAEN

9

DADDR

5

WADDR

DHOR

DVERT

4

LP

NROW

DVERT

2

LD1/2

DHOR

ARWDB

VCLK

LP1/2

VCLK

DATA

WACTIVE

CCS1

C(R,G,B)*4

WACTIVE

CCS1

CCS0

CWS

CHS

CH

DISPLAY

REGISTERS

(RAM)

CHARACTER ROMS

2

12-BIT SHIFT

REGISTERS

8

WINDOWS &

FRAME

6

CONTROL

WWR

WWG

WWB

12

COLOR

ENCODER

C(R,G,B)*4

CCS0

7

CRADDR

4

LP

NROW

CWS

BSEN

SHADOW

LUMA

BORDER

BSEN

SHADOW

6

VERTD

5

HORD

OSDENB

9

VDD

16

VSS

4

VDDA

VSSA

1

15

ROUT

14

GOUT

13

BOUT

12

FBKG

11

HTONE

This data sheet contains new product information. Myson Technology reserves the rights to modify the product specification without notice.

No liability is assumed as a result of the use of this product. No rights under any patent accompany the sale of the product.

MTV004 Revision 4.0 06/24/1999

1/9

MYSON

TECHNOLOGY

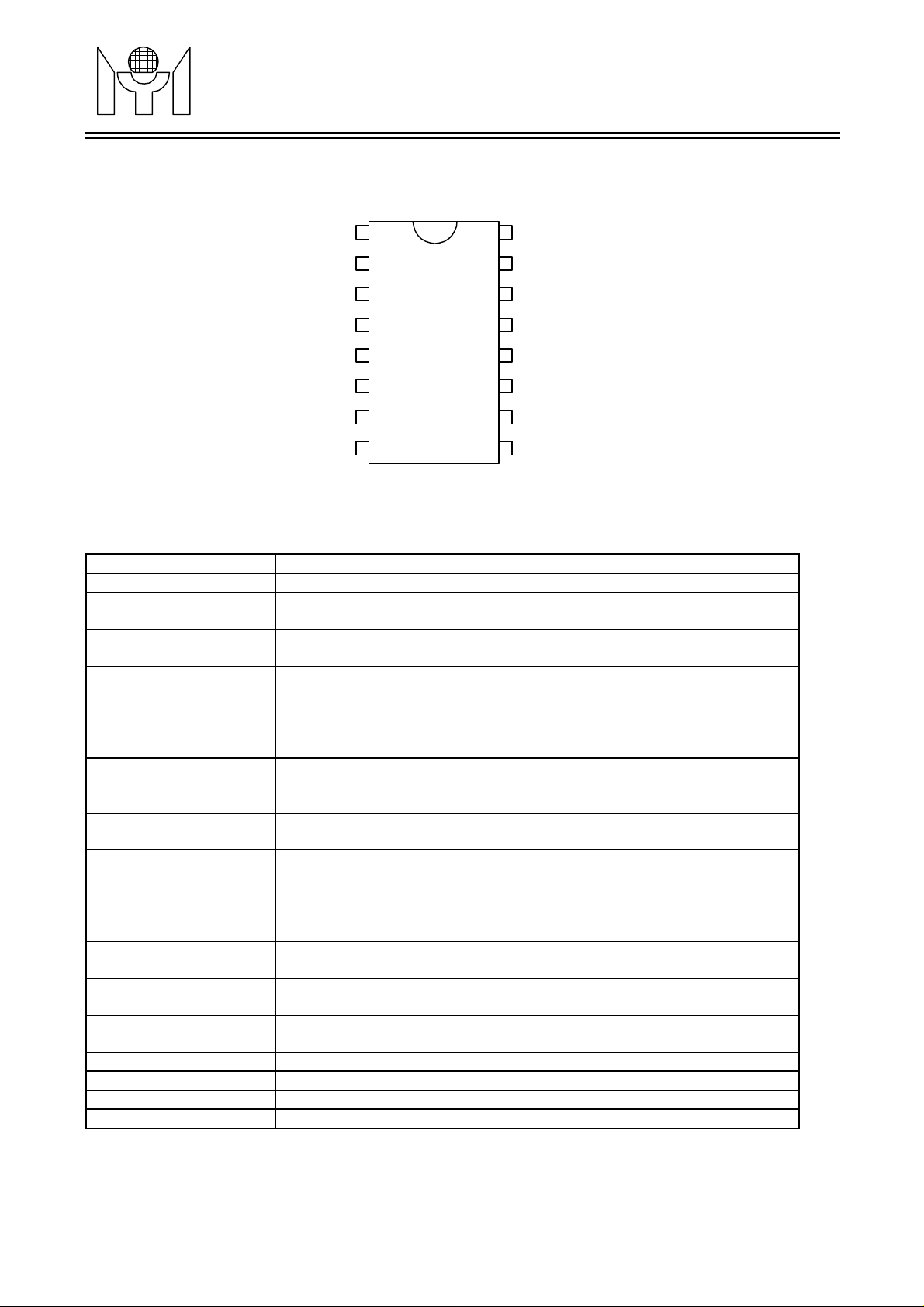

1.0 CONNECTION DIAGRAM

(16 pins PDIP 300 mil PACKAGE)

VSSA

VCO

RP

VDDA

HFLB

SSB

SDA

SCK

2.0 PIN DESCRIPTIONS

1

2

3

4

5

6

7

8

MTV004

16

15

14

13

12

11

10

9

MTV004

VSS

ROUT

GOUT

BOUT

FBKG

HTONE

VFLB

VDD

Name I/O Pin# Function

VSSA - 1

VCO I/O 2

RP I/O 3

VDDA - 4

HFLB I 5

SSB I 6

SDA I 7

SCK I 8

VDD - 9

VFLB I 10

HTONE O 11

FBKG O 12

BOUT O 13

GOUT O 14

ROUT O 15

VSS - 16

Analog Ground.

Voltage Control Oscillator. This pin is used to control the internal oscillator

frequency by DC voltage input from an external low pass filter.

Bias Resistor. The bias resistor is used to regulate the bias current for the

internal oscillator to resonate at the specific dot frequency.

Analog Power Supply. Positive 5 V DC supply for internal analog circuitry.

A 0.1uF decoupling capacitor should be connected across to VDDA and

VSSA as close to the device as possible.

Horizontal Input. This pin is used to input the horizontal synchronizing

signal. It is triggered by a negative edge and has an internal pull-up resistor.

Serial Interface Enable. Used to enable the serial data and to select I2C or

SPI bus operation. If this pin is left floating, the I2C bus is enabled, otherwise

the SPI bus is enabled.

Serial Data Input. The external data transfers through this pin to the internal

display and control registers. It has an internal pull-up resistor.

Serial Clock Input. Clock input pin used to synchronize transferring of data.

It has an internal pull-up resistor.

Digital Power Supply. Positive 5 V DC supply for internal digital circuitry. A

0.1uF decoupling capacitor should be connected across to VDD and VSS as

close to the device as possible.

Vertical Input. This pin is used to input the vertical synchronizing signal. It is

negatively triggered and has an internal pull-up resistor.

Half Tone Output. This pin is used to attenuate external R,G,B amplifiers

for a transparent windowing effect.

Fast Blanking Output. Used to cut off external R,G,B signals while

the chip is displaying characters or windows.

Blue Color Output. Blue color video signal output.

Green Color Output. Green color video signal output.

Red Color Output. Red color video signal output.

Digital Ground.

2/9

MTV004 Revision 4.0 06/24/1999

MYSON

TECHNOLOGY

MTV004

3.0 FUNCTIONAL DESCRIPTIONS

3.1 Serial Data Interface

The serial data interface receives data transmitted from an external controller. There are 2 types of bus that

can be accessed through the serial data interface: SPI bus and I2C bus.

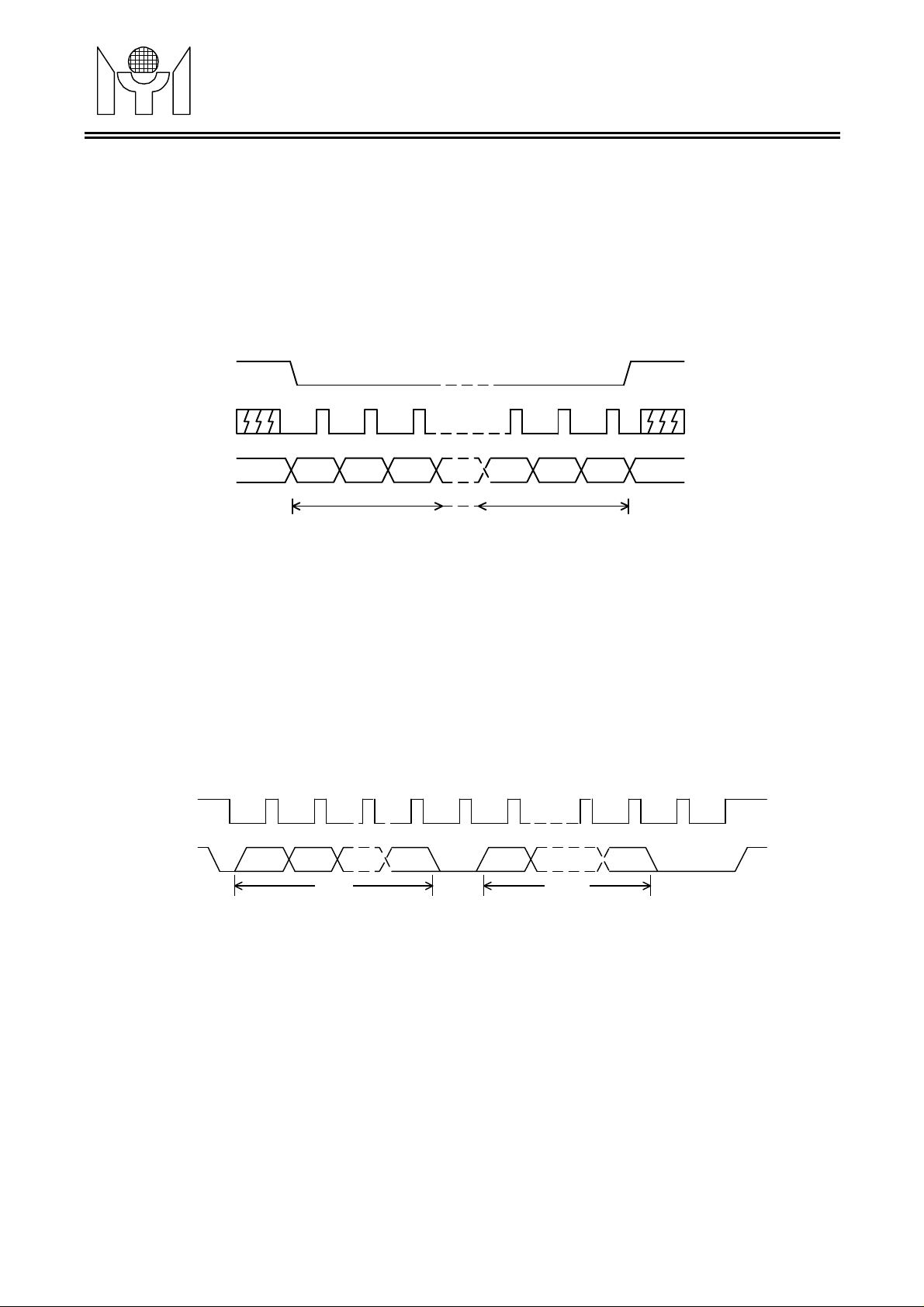

3.1.1 SPI Bus

While SSB pin is pulled to "high" or "low" level, the SPI bus operation is selected. A valid transmission should

be started by pulling SSB to "low" level, enabling MTV004 in receiving mode, and retaining "low" level until the

last cycle for a complete data packet transfer. The protocol is shown in Figure 2:

SSB

SCK

SDA

MS

B

first byte last byte

LSB

Figure 2. Data Transmission Protocol

There are 3 transmission formats as shown below:

Format (a) R - C - D → R - C - D → R - C - D ..........

Format (b) R - C - D → C - D → C - D → C - D .......

Format (c) R - C - D → D → D → D → D → D .........

R=row address, C=column address, D=display data

3.1.2 I2C Bus

The I2C bus operation is only selected when the SSB pin is left floating. A valid transmission should begin by

writing the slave address 7AH, which is the mask option, to MTV004. The protocol is shown in Figure 3:

SCK

SDA

START ACK

There are 3 transmission formats as shown below:

Format (a) S - R - C - D → R - C - D → R - C - D ..........

Format (b) S - R - C - D → C - D → C - D → C - D .......

Format (c) S - R - C - D → D → D → D → D → D ........

S=slave address, R=row address, C=column address, D=display data

B7 B6 B0 B7 B0

fist byte

second byte last byte

Figure 3. Data Transmission Protocol (I2C)

¡@¡@¡@¡@¡@

ACK STOP

Each arbitrary length of data packet consists of 3 portions: row address (R), column address (C) and display

data (D). Format (a) is suitable for updating small amounts of data that will be allocated with different row and

column addresses. Format (b) is recommended for updating data that has the same row address but a different

column address. Format (c) should be used for massive data updating or a full-screen data change to increase

3/9

MTV004 Revision 4.0 06/24/1999

Loading...

Loading...