MYSON MTL001 Datasheet

MYSON

On-chip output PLL provide clock frequency fine-tune (inverse, duty cycle

Double scan capability for interlaced input.

MTL001

TECHNOLOGY

(Rev. 0.95)

XGA Flat Panel Controller

FEATURES

General

• Auto configuration of sampling clock frequency, phase, H/V center, as well as white ba lance.

• Auto detection of present or non-present or over range sync signals and their polarities.

• Composite sync separation and odd/even field detection of interlaced video.

•

• Selection of serial 2-wire I

• 3.3V supplier, 5V I/O tolerance in 256-pin PQFP or 272-pin BGA package.

2

C or 8-bit direct host interface to 8-bit MCU.

Input Processor

• Single RGB (24-bit) or Dual RGB (48-bit) input rates up to 100MHz.

• Support both non-interlaced and interlaced RGB graphic input signals.

• YUV 4:2:2 or YUV 4:1:1 (CCIR601) interlaced video input.

• Glue-less connection to Philips SAA711x digital video decoder.

• Built-in YUV to RGB color space converter.

• Compliant with digital LVDS/PanelLink TMDS input interface.

• PC input resolution up to XGA 1024x768 @85Hz.

and delay).

Video Processor

• Independent programmable Horizontal and Vertical scaling ratios from 1/32 to 32

• Flexible de-interlacing unit for digital YUV video input data.

• Zoom to full screen resolution of de-interlaced YUV video data stream.

• Built-in programmable gain control for white balance alignments.

• Built-in programmable 8-bit or 10-bit gamma correction table.

• Built-in programmable temporal color dithering.

• Built-in programmable interpolation look-up table.

• Support smooth panning under viewing window change.

Output Processo r

• Single pixel (18/24-bit) or Dual pixel (36/48-bit) per clock digital RGB output.

• Built-in output timing generator with programmable clock and H/V sync.

• Support VGA/SVGA/XGA display resolution.

• Overlay input interface with external OSD controller.

•

Memory Interf ace

• Support 48/32/24 bit bus width, SDRAM/SGRAM x2 or x3 configuration.

• Optional display through internal line buffer without external frame-buffer mem ory.

• Support power down mode.

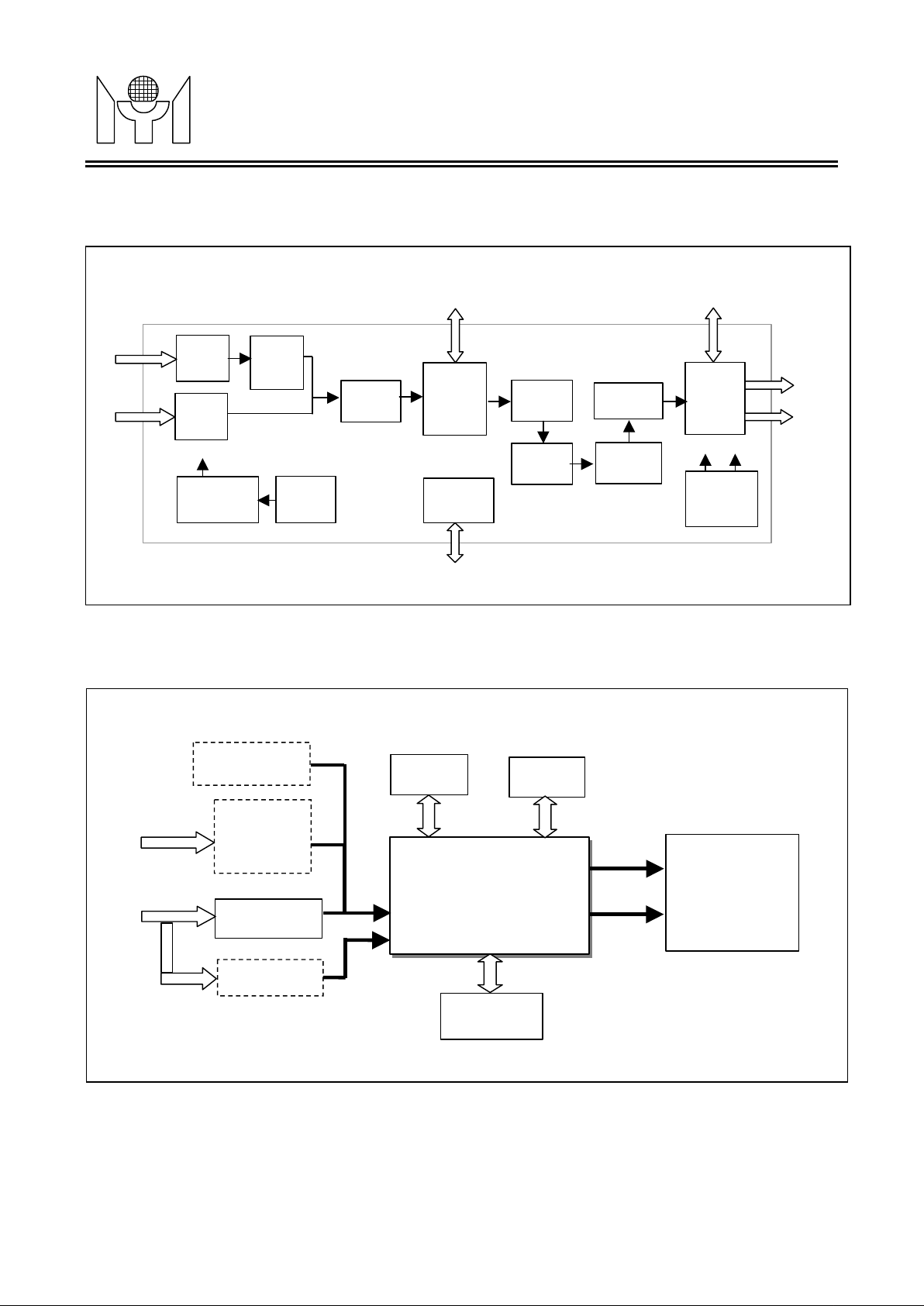

GENERAL DESCRIPTION

The MTL001 Flat Panel Display (FPD) Controller is an input format converter for TFT-LCD Monitor or LCD

TV application which accepts 15-pin D-sub RGB graphic signals (through ADC), YUV sign als from digital

video decoder or digital RGB graphic signals from PanelLink TMDS receiver. It includes a RGB/YUV input

processor, configurable frame-buffer memory interface, video scaling up/down processor, OSD input

interface and output display processor in 256-pin PQFP or 272-pin BGA package.

Revision 0.95 - 1 - 2000/06/14

MYSON

video

RGB

To SDRAM/SGRAM

Generator

8-bit MCU

MTV130

OSD

SDRAM/

SGRAM

Decoder

S-Video

MTL001

TECHNOLOGY

BL OCK DIAGRAM

Digital

PC

YUV

Input

RGB

Input

Auto

Calibration

YUV

to

RGB

Mode

Detect

Scale

Down

Frame

Buffer

Control

Host

Interface

To 8-bit MCU

Scale

Up

Gain

Control

Dithering

Gamma

Correct

(Rev. 0.95)

To external OSD

OSD

&

Output

MUX

Output &

Memory

Timing

RGB

output

APPLICA TIONS

LVDS/PanelLink

TMDS Receiver

Composite/

D-sub RGB

graphic signals

Digital

Video

ADC1

ADC2

MTL001

FPD Monitor

Controller

MTV212

TFT-LCD

Flat Panel

This datasheet contains new product information. Myson Technology reserves the rights to modify the product specification without

notice. No liability is assumed as a result of the use of this product. No rights under any patent accompany the sale of the product.

Revision 0.95 - 2 - 2000/06/14

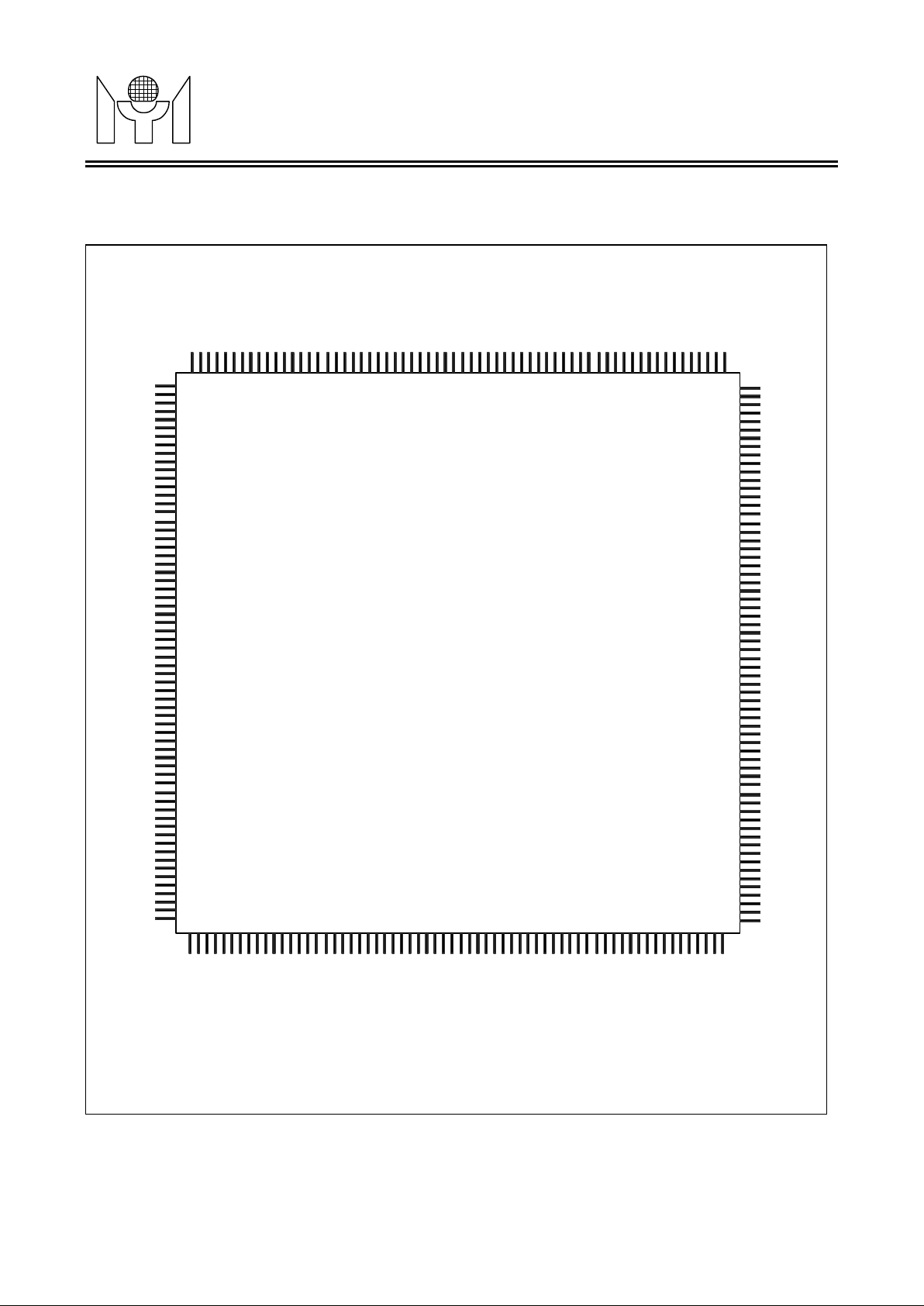

MYSON

64* PVDD

63* AVDD

62* AVDD

61* XI

65* PVSS

PVDD *129

PVSS *130

OSDRED *131

OSDGRN *132

OSDBLU *133

OSDEN *134

MTL001

TECHNOLOGY

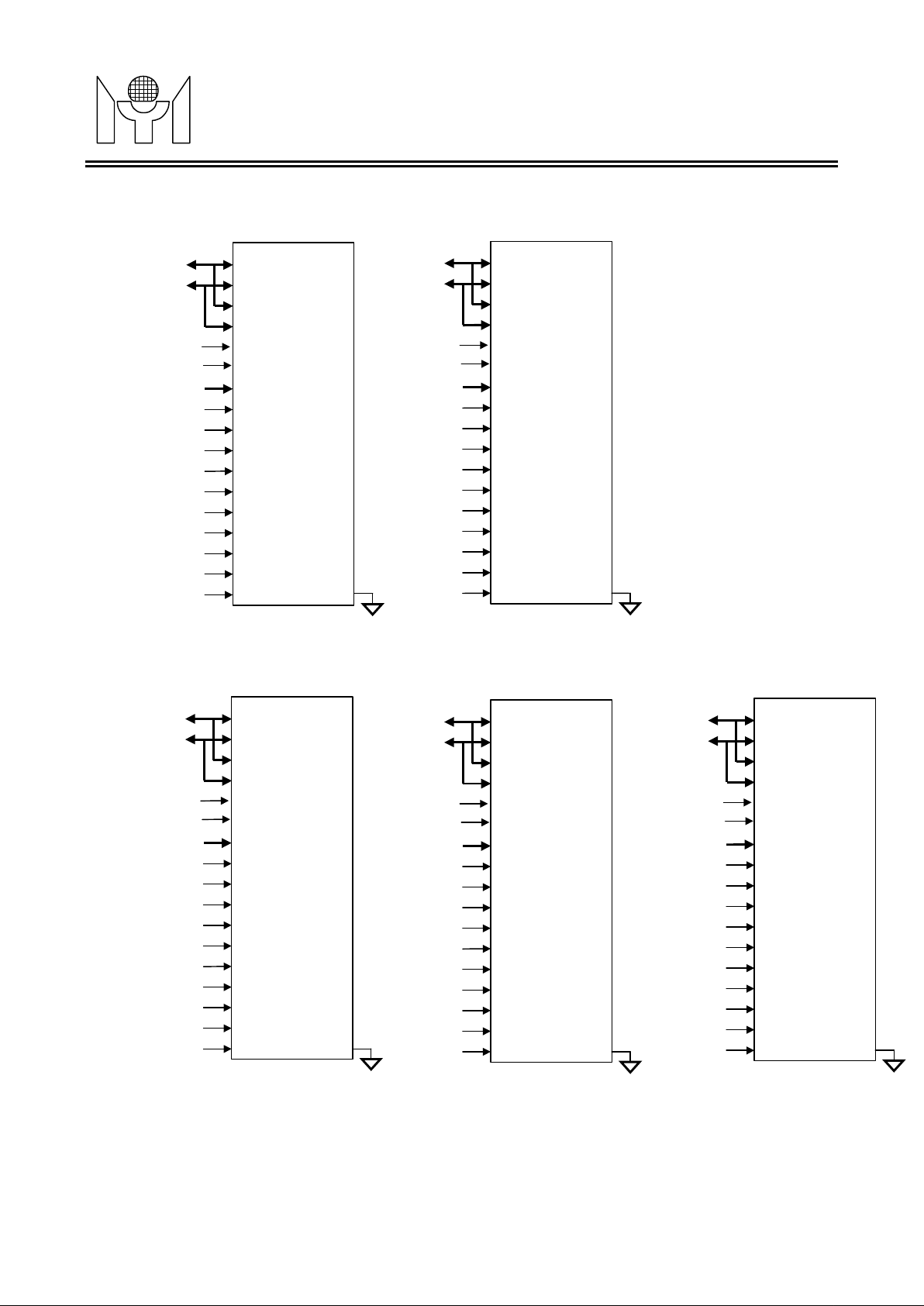

1. PIN CONNECTION

BA/MA11 *182

MA8 *183

MA7 *184

MA6 *185

MA5 *186

MA4 *187

11* G1IN7/UVIN7

10* DVSS

9* R1IN0/YIN0

8* R1IN1/YIN1

7* R1IN2/YIN2

PVSS *193

PVSS *194

MWE# *195

MCAS# *196

MRAS# *197

DQM1 *198

DQM0 *199

DVSS *200

DVDD *201

MD7 *202

MD6 *203

MD5 *204

MD4 *205

MD3 *206

MD2 *207

MD1 *208

MD0 *209

PVDD *210

MD31 *211

MD30 *212

MD29 *213

MD28 *214

MD27 *215

MD26 *216

MD25 *217

MD24 *218

PVSS *219

AD0 *220

AD1 *221

AD2 *222

AD3 *223

AD4 *224

AD5 *225

AD6 *226

AD7 *227

HCS# *228

PVDD *229

ALE *230

PVSS *231

HWR# *232

HRD# *233

EXTMCLK *234

RST# *235

BUSSEL *236

IRQ *237

GPIO7 *238

GPIO6 *239

GPIO5 *240

GPIO4 *241

GPIO3 *242

GPIO2 *243

GPIO1 *244

GPIO0 *245

EXTDCLK *246

CLAMP *247

HSYNC/CS*248

VSYNC *249

TMDSSEL *250

TDIE/SOG*251

PVDD *252

IPCLK *253

NC *254

PVSS *255

PVSS *256

PVDD *192

MA3 *188

MA2 *189

MA1 *190

MA0 *191

6* R1IN3/YIN3

5* R1IN4/YIN4

4* R1IN5/YIN5

3* R1IN6/YIN6

2* R1IN7/YIN7

1* PVDD

12* G1IN6/UVUN6

(Rev. 0.95)

DQM3/MA10 *149

PVSS *181

MCK *180

MD9 *166

MD8 *167

MCS# *168

DVSS *169

MD39 *170

MD38 *171

MD37 *172

MD36 *173

MD35 *174

MD34 *175

MD33 *176

MD32 *177

MCKE *178

DVDD *179

MD15 *160

MD14 *161

MD13 *162

MD12 *163

MD11 *164

MD10 *165

MD44 *154

MD43 *155

MD42 *156

MD41 *157

MD40 *158

DVDD *159

DQM2/MA9 *148

MD22 *141

MD21 *142

MD20 *143

MD19 *144

MD18 *145

MD17 *146

MD16 *147

DVSS *150

MD47 *151

MD46 *152

MD45 *153

MTL001

(256-pin PQFP)

52* B2IN4

51* B2IN5

50* B2IN6

49* B2IN7

48* PVDD

47* G2IN0

46* G2IN1

45* G2IN2

44* G2IN3

43* G2IN4

42* G2IN5

41* G2IN6

40* G2IN7

39* PVSS

38* R2IN0

37* R2IN1

36* R2IN2

35* R2IN3

34* R2IN4

33* R2IN5

32* R2IN6

31* R2IN7

30* DVDD

29* RGBSEL

28* DVSS

27* B1IN0

26* B1IN1

25* B1IN2

24* B1IN3

23* B1IN4

22* B1IN5

21* B1IN6

20* B1IN7

19* DVDD

18* G1IN0/UVIN0

17* G1IN1/UVIN1

16* G1IN2/UVIN2

15* G1IN3/UVUN3

14* G1IN4/UVIN3

13* G1IN5/UVUN5

OSDINT *135

OVSYNC *136

OHSYNC *138

DVSS *137

DVDD *139

MD23 *140

128* PVSS

127* PVSS

126* OCLK

125* PVDD

124* DDEN

123* DVSYNC

122* DHSYNC

121* DVDD

120* R1OUT0

119* R1OUT1

118* R1OUT2

117* R1OUT3

116* R1OUT4

115* R1OUT5

114* R1OUT6

113* R1OUT7

112* DVSS

111* G1OUT0

110* G1OUT1

109* G1OUT2

108* G1OUT3

107* G1OUT4

106* G1OUT5

105* G1OUT6

104* G1OUT7

103* B1OUT0

102* B1OUT1

101* B1OUT2

100* B1OUT3

99* B1OUT4

98* B1OUT5

97* B1OUT6

96* B1OUT7

95* DVSS

94* DDCLK1

93* DDCLK2

92* DVDD

91* R2OUT0

90* R2OUT1

89* R2OUT2

88* R2OUT3

87* R2OUT4

86* R2OUT5

85* R2OUT6

84* R2OUT7

83* PVDD

82* G2OUT0

81* G2OUT1

80* G2OUT2

79* G2OUT3

78* G2OUT4

77* G2OUT5

76* G2OUT6

75* G2OUT7

74* B2OUT0

73* B2OUT1

72* B2OUT2

71* B2OUT3

70* B2OUT4

69* B2OUT5

68* B2OUT6

67* B2OUT7

66* PVSS

60* XO

59* AVSS

58* AVSS

57* PVSS

56* B2IN0

55* B2IN1

54* B2IN2

53* B2IN3

Note: Pin connection of 272-pin BGA to be defined later

Revision 0.95 - 3 - 2000/06/14

MYSON

Vertical sync input

MTL001

TECHNOLOGY

(Rev. 0.95)

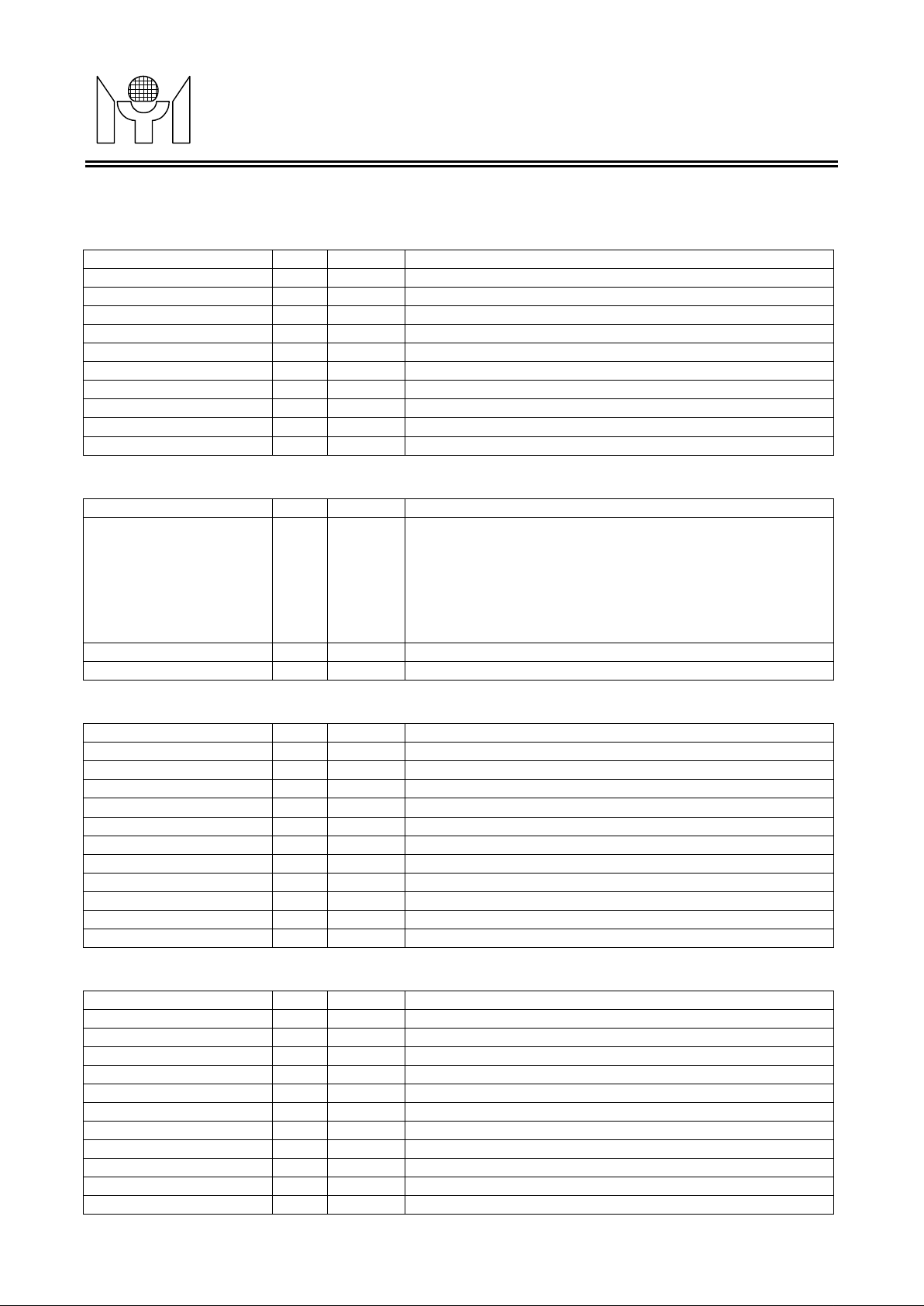

2. PIN DESCRIPTION

ADC1 Input Inter face (YUV or RGB or TMDS Inpu t Data)

Name Type Pin# Description

VSYNC I 249

HSYNC/CS I 248 Horizontal or Composite sync input

RGBSEL O 29 Input select. 1:RGB input, 0:YUV input

TMDSSEL O 250 TMDS input select, active high

CLAMP O 247 Clamp pulse output for ADC

IPCLK I 253 Input pixel clock

R1IN[7:0]/YIN[7:0] I 2-9 Red or Y channel or TMDS input data (Single/Dual ADC)

G1IN[7:0]/UVIN[7:0] I 11-18 Green or UV channel or TMDS input data (Single/Dual ADC)

B1IN[7:0] I 20-27 Blue channel or TMDS input data (Single/Dual ADC)

TDIE I 251 TMDS digital input enable

ADC2 Input Inter face (RGB Data)

Name Type Pin# Description

R2IN[7:0] I 31-38 Red channel input data (Dual ADC)

or Control bit for YUV video input

Bit 4: VPHREF, Video input Horizontal reference signal

Bit 3: VPVS, Video input VSYNC signal

Bit 2: VPODD, Video input ODD/EVEN field signal

Bit 1: VPHS, Video input HSYNC signal

Bit 0: VPCLK, Video input clock signal

G2IN[7:0] I 40-47 Green channel input data (Dual ADC)

B2IN[7:0] I 49-56 Blue channel input data (Dual ADC)

Displ ay Outp ut Interface

Name Type Pin# Description

DDEN O 124 Display data output enable for LCD panel

DVSYNC O 123 Display Vertical sync output

DHSYNC O 122 Display Horizontal sync output

DDCLK1 O 94 Display output clock for odd data

DDCLK2 O 93 Display output clock for even data

R1OUT[7:0] O 113-120 Red output even data , bit[7:2] for 6-bit panel

G1OUT[7:0] O 104-111 Green output even data , bit[7:2] for 6-bit panel

B1OUT[7:0] O 96-103 Blue output even data , bit[7:2] for 6-bit panel

R2OUT[7:0] O 84-91 Red output odd data , bit[7:2] for 6-bit panel

G2OUT[7:0] O 75-82 Green output odd data , bit[7:2] for 6-bit panel

B2OUT[7:0] O 67-74 Blue output odd data , bit[7:2] for 6-bit panel

Memory Interf ace

Name Type Pin# Description

MCK O 180 Memory output clock

MCKE O 178 Memory clock enable

MCS# O 168 Memory chip select, active low.

MRAS# O 197 Mem ory row address strobe, active low

MCAS# O 196 Mem ory column address strobe, active low

MWE# O 195 Memory write enable, active low

DQM[1:0] O 198-199 Memory data mask byte enable

BA/MA11 O 182 Memory bank address or Memory address line

DQM3/MA10 O 149 SGRAM data mask byte enable or SDRAM address line

DQM2/MA9 O 148 SGRAM data mask byte enable or SDRAM address line

MA[8:0] O 183-191 Memory address line

Revision 0.95 - 4 - 2000/06/14

MYSON

Vertical sync for external OSD

Horizontal sync for external OSD

OSD intensity input

OSD overlay enable

Oscillator frequency input

Oscillator frequency output

Bit 6: ADHS, Horizontal sync for A/D converter

Input Sync On Green

MTL001

TECHNOLOGY

MD[47:40] I/O 151-158 Memory Blue (B1) data

MD[39:32] I/O 170-177 Memory Green (G1) data

MD[31:24] I/O 211-218 Memory Red (R1) data

MD[23:16] I/O 140-147 Memory Blue (B0) data

MD[15:8] I/O 160-167 Memory Green (G0) data

MD[7:0] I/O 202-209 Memory Red (R0) data

(Rev. 0.95)

Host Interface

Name Type Pin# Descrip tio n

RST# I 235 System reset input, active low.

AD[7:0] I/O 227-220 T he address and da ta bus of 8-bit direct interface or

2-wire I2C series bus

Bit 1: SDA, serial bus data

Bit 0: SCK, serial bus clock

HWR# I 232 Host write strobe , active low

HRD# I 233 Host read strobe, active low

ALE I 230 Host address latch enable for 8-bit direct bus

HCS# I 228 Host chip select

BUSSEL I 236 Bus mode selection. 0: I2C bus, 1: 8-bit direct bus

IRQ O 237 Interrupt request output

OSD Interf ac e

Name Type Pin# Description

OCLK O 126 Clock for external OSD

OVSYNC O 136

OHSYNC O 138

OSDRED I 131 OSD red input

OSDGRN I 132 OSD green input

OSDBLU I 133 OSD blue input

OSDINT I 135

OSDEN I 134

Other Interface

Name Type Pin# Description

XI I 61

XO O 60

EXTDCLK I 246 External display clock input

EXTMCLK I 234 External memory clock input

GPIO[7:0] I/O 238-245 General purpose I/O or

NC - 254 No connection

Bit 7: ADVS, Vertical sync for A/D converter

Bit 2: MA9_SGRAM, Memory address 9 for SGRAM

Bit 0: RAWHS/SOG, Input source HSYNC or

Default: Bit[7:2]: Output direction

Bit[1:0]: Input direction

3.3V Power and Grou n d

Name Pin# Description

DVDD 19, 30, 92, 121, 139, 159, 179, 201 Digital power 3.3V

DVSS 10, 28, 95, 112, 137, 150, 169, 200 Digital ground

PVDD 1, 48, 64, 83, 125, 129, 192, 210, 229, 252 Pad power 3.3V

PVSS 39, 57, 65, 66, 127, 128, 130, 181, 193, 194, Pad ground

Revision 0.95 - 5 - 2000/06/14

MYSON

MTL001

TECHNOLOGY

219, 231, 255, 256

AVDD 62, 63 Analog power 3.3V

AVSS 58, 59 Analog ground

(Rev. 0.95)

Revision 0.95 - 6 - 2000/06/14

MYSON

Single Pixel mode, only the ports

The Digital RGB input port works just in the same way as Sec 3.1.1 except that pin

With a flexible single or double

The 16 bit data bus is shared by ports

depending on the type of input images.

MTL001

TECHNOLOGY

(Rev. 0.95)

3. FUNCTIONAL DESCRIPTION

3.1 Input Process or

General Descrip t io n

The function of Input Interface is to provide the interface between MTL001 and external in put devices. It can

process both non-interlaced and interlaced RGB graphic input, YUV video input, and digita l RGB input

compliant with digital LVDS/PanelLink TMDS interface. It also contains the Decimation circuit to scale down

the input image with arbitrary ratios down to 1/32 and the built-in YUV to RGB color space converter.

3.1.1 RGB Inpu t Format

The RGB input port can work in two modes: Single Pixel mode (24 bits) and Double Pixel mode (48 bits). For

R1IN[7:0], G1IN[7:0], and B1IN[7:0] are internally sampled. For Double

Pixel mode, besides the ports R1IN[7:0], G1IN[7:0], and B1IN[7:0], the ports R2IN[7:0], G2IN[7:0], and

B2IN[7:0] are needed additionally. The R/G/B1IN ports are sampled at the rising edge of the RGB input clock,

and the R/G/B2IN ports are sampled at the falling edge.

3.1.2 TMDS Input Form at

“Digital Input Enable

DIEN” is needed.

pixel input interface, the supported format is up to true color, including the 18

bit/pixel or 24 bit/pixel in 1 or 2 pixels/clock mode.

3.1.3 YUV Input Form at

The YUV input port supports interlaced video data from the most common video decoder ICs like SAA711x.

R1IN[7:0] and G1IN[7:0]. The 5 bit control signals are shared with the

port R2IN[4:0]. The 16 bit data is sampled at the rising edge of the shared video clock VPCLK when the

shared data enable HREF is active. The supported formats are YUV4:1:1 and YUV4:2:2 with CCIR601

standard.

3.1.4 YUV to RGB Convert er

It is used to convert YCbCr format into RGB format. The basic equations are as follows:

R = Y + 1.371(Cr – 128)

G = Y – 0.698(Cr – 128) – 0.336(Cb – 128)

B = Y + 1.732(Cb - 128)

3.1.5 De-interlace mod e

For interlace input, MTL001 features several de-interlacing algorithms for processing interlaced video data

¨ Static Mode

In this mode, the first and second fields are simply put together without an y filtering. Memory for two fields is

needed. It is commonly used in still image input.

¨ Tog gl e Mode

In this mode, only one field is displayed at a time. First field and second field is toggling displayed. The

missing lines are calculated from duplicating the neighboring lines. For moving picture, it has a good quality.

¨ Spatial Mod e

In this mode, two fields are toggled displayed, just like Toggle mode. The missing lines are calculated from

interpolating the neighboring lines. This mode has an generally good quality for still and moving picture.

3.1.6 Sync Processor

The V/H SYNC processing block performs the functions of Composite signal separation/insertion, SYNC

inputs the presence check, frequency counting, polarity detection and control. It contains a de-glitch circuit to

filter out any pulse shorter than one OSC period which is treated as noise am ong V/H SYNC pulses.

Revision 0.95 - 7 - 2000/06/14

MYSON

input sample registers to aid in centering the screen automatically.

s phase and frequency. MTL001

colors. This advanced function helps the firmware to analyze ADC performance. Usually the firmware can

s phase and frequency.

MTL001

TECHNOLOGY

¨ V/H SYNC Frequency Counter

(Rev. 0.95)

MTL001 measures VSYNC/HSYNC frequency counted in the proper clock and save the information in

register. Users can read the figure and calculate VSYNC/HSYNC frequency using the following formulae:

f

= f

= f

osc

osc

/ N

/ N

vsync

f

hsync

Where f

f

f

N

N

¨ V/H SYNC Presenc e Chec k

vsync

hsync

osc

vsync

hsync

51/256

vsync

58

hsync

: VSYNC frequency

: HSYNC frequency

: oscillator clock with 14.31818 MHz

: counted number of VSYNC

: counted number of HSYNC

This function checks the input VSYNC, where Vpre flag is set when VSYNC is over 40Hz or cleared when

VSYNC is under 10Hz and the input is HSYNC, where Hpre flag is set when HSYNC is over 10KHz or

cleared when HSYNC is under 10Hz.

¨ V/H Polari ty Detect

This function detects the input VSYNC/HSYNC high and low pulse duty cycle. If the high pulse duration is

longer than that of low pulse, the negative polarity is asserted; otherwise, positive polarity is asserted.

¨ Comp os it e SYNC separatio n/ins erti on

MTL001 continuously monitors the input HSYNC. If the input VSYNC can be extracted from it, a CVpre flag is

set. MTL001 can insert HSYNC pulse during Composite VSYNC’s active time and the insertion frequency

can adapt to original HSYNC’s.

3.1.7 Aut o Tune

Auto Tune function consists of Auto Position that automatically centering the screen and A uto Calibration

which contains Phase Calibration, Histogram, Min/Max Value, and Pixel Grab described as below. With this

auto adjustment support it is possible to measure the correct phase, frequency, gain, and offset of ADC. The

horizontal and vertical back porches of input image and the horizontal and vertical active reg ions can also be

measured. Firmware can adjust input image registers automatically by reading Auto Tune’s registers in single

or burst mode.

¨ Auto Position

MTL001 provides Horizontal/Vertical back porch and active region values. Users can use these values to set

¨ Phase Calibrati on

MTL001 provides Auto Calibration registers to measure the quality of current ADC’s phase and frequency.

The biggest Auto Calibration registers value means the right value of ADC’

has two kinds of algorithms to calculate Auto Calibration’s value. One is the traditional Difference method, the

other is MYSON’s proprietary method; the latter one is recommended for a better performance.

¨ Histogr am

Histogram means the total number of input pixels below/above one threshold value, for individual R/G/B

use this information to measure ADC’s noise margin, and adjust its offset and gain, or even aid in the mode

detection.

¨ Mi n /Max Value

Min/Max value means minimum or maximum pixel value within the specified input act ive image region for

each RGB channel. This information is usually used to adjust ADC’s offset and gain.

¨ Pixel Grab

Pixel Grab means users can grab a single input pixel at any one point. The position of the point can be

programmed by users. This is another traditional method to measure ADC’

Revision 0.95 - 8 - 2000/06/14

MYSON

because they share the same line buffers.

: Image will be scaled up/down based on scaling factor. Every point of output image data

image data will be filtered by the

MTL001

TECHNOLOGY

(Rev. 0.95)

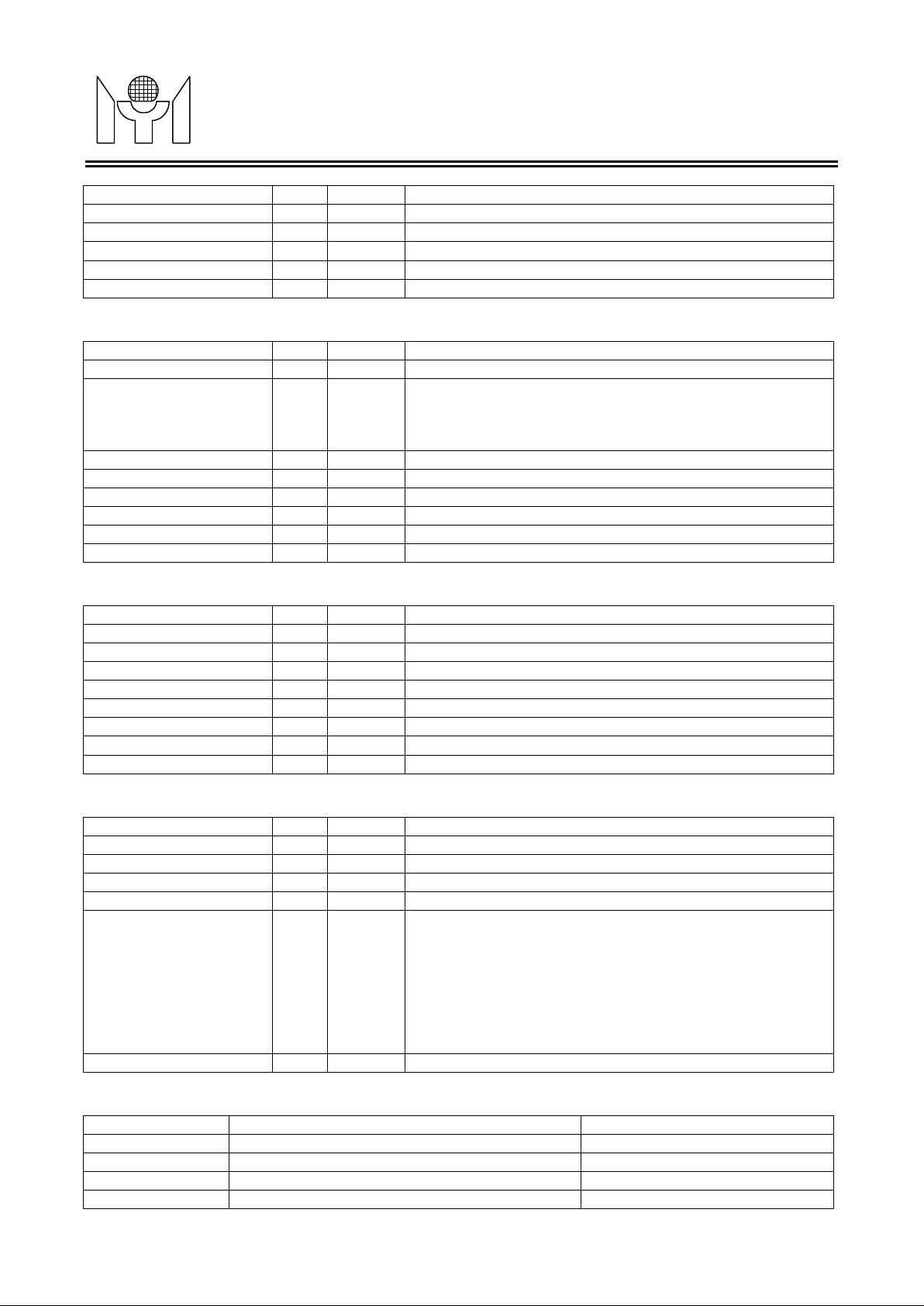

3.2 Video Proc ess o r

General Descrip t io n

MTL001 possesses a powerful and programmable video processor b y providing the following functions:

Scaling Up/Down, Gain Control, Brightness Control, Gamma Correction, and Dithering Control.

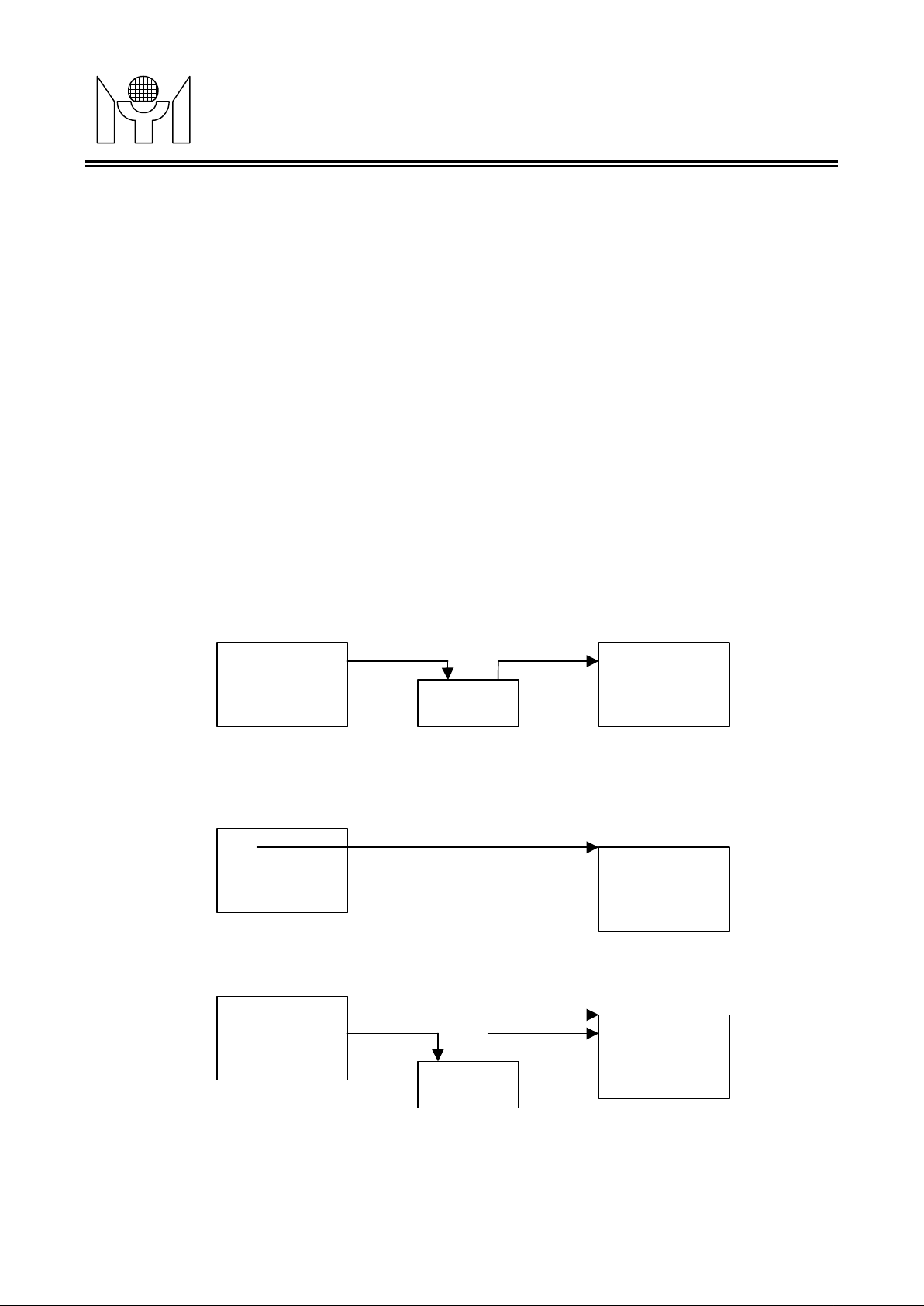

The block diagram of Video Processor is as follows:

Scaling Factor

SCALING

GAIN

BRIGHTNESS

Transition Table

Gain Factor

Brightness Factor

GAMMA

DITHERING

Fig. 3.2.1 Video Processor Block Diagram

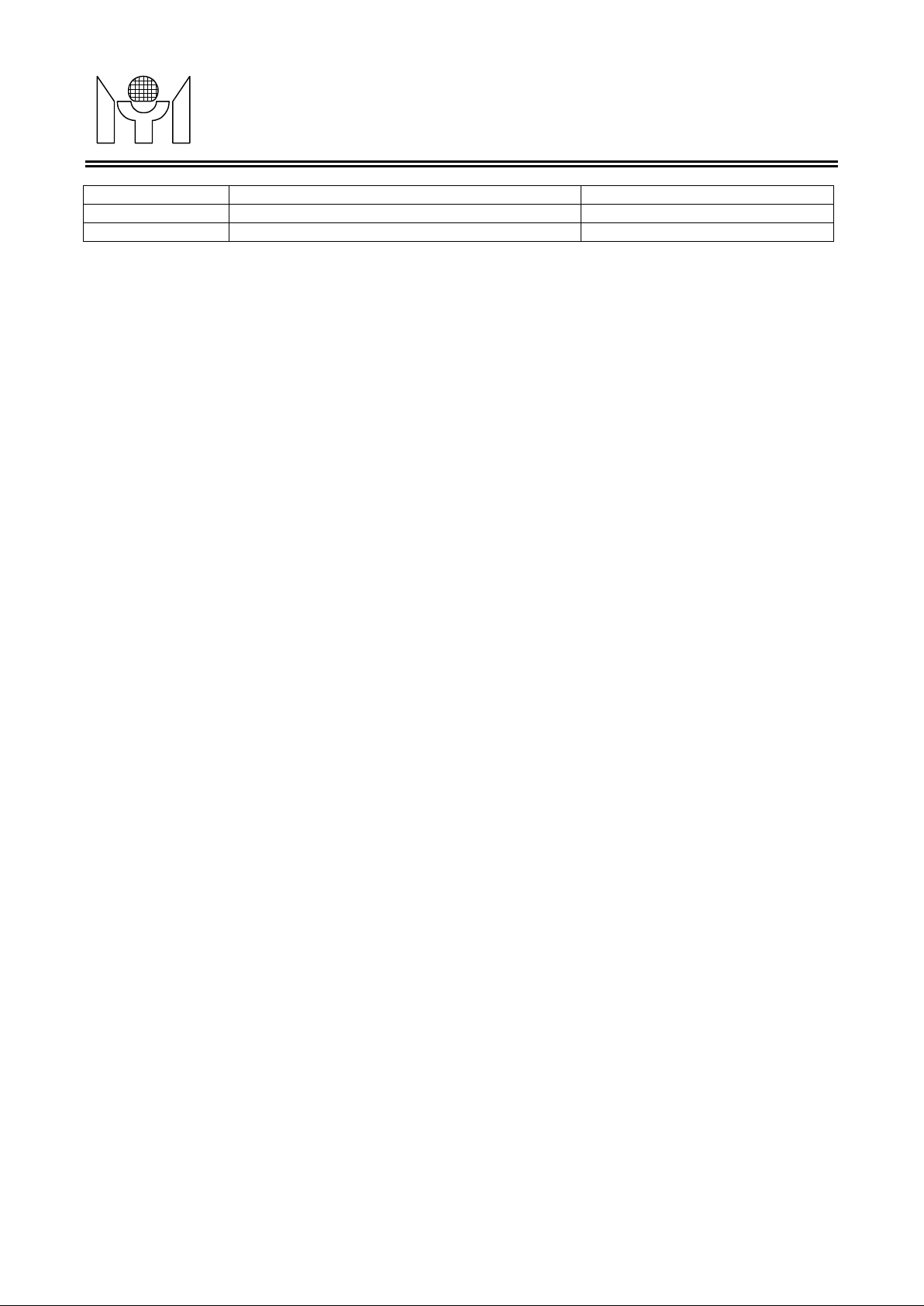

3.2.1 Scaling

MTL001 provides scaling function ranging from 1/32 to 32 for both up and down sca ling, and for both

horizontal and vertical processing. Note that the up and down scaling cannot operate in the same time,

For scaling up, both horizontal and vertical processing, MTL001 provides four methods:

¨ Pass Mod e: Image will be passed through without considering any scaling factor.

¨ Dupl ic ate Mode: Image will be scaled up/down based on scaling factor. Every point of output image

comes from the input. In this method, Output image will have the good contrast but may be nonuniformed.

¨ Bi linear Mode

will be filtered by bilinear filter. In this method, output image will have the good scaling quality but may

be blurred.

Gamma Table

Dithering Table

¨ Interpo l atio n Table Mode: Image will be scaled up/down based on scaling factor. Every point of output

user defined filter.

Revision 0.95 - 9 - 2000/06/14

MYSON

programming the gain and brightness coefficients. This adjustment is applied to RGB colors individually.

Gamma Correction is used to compensate the non-linearity of LCD display panel. MTL001 contains an 8/10-

true color (8 bits per color) or high color (6 bits per color) display.

MTL001

TECHNOLOGY

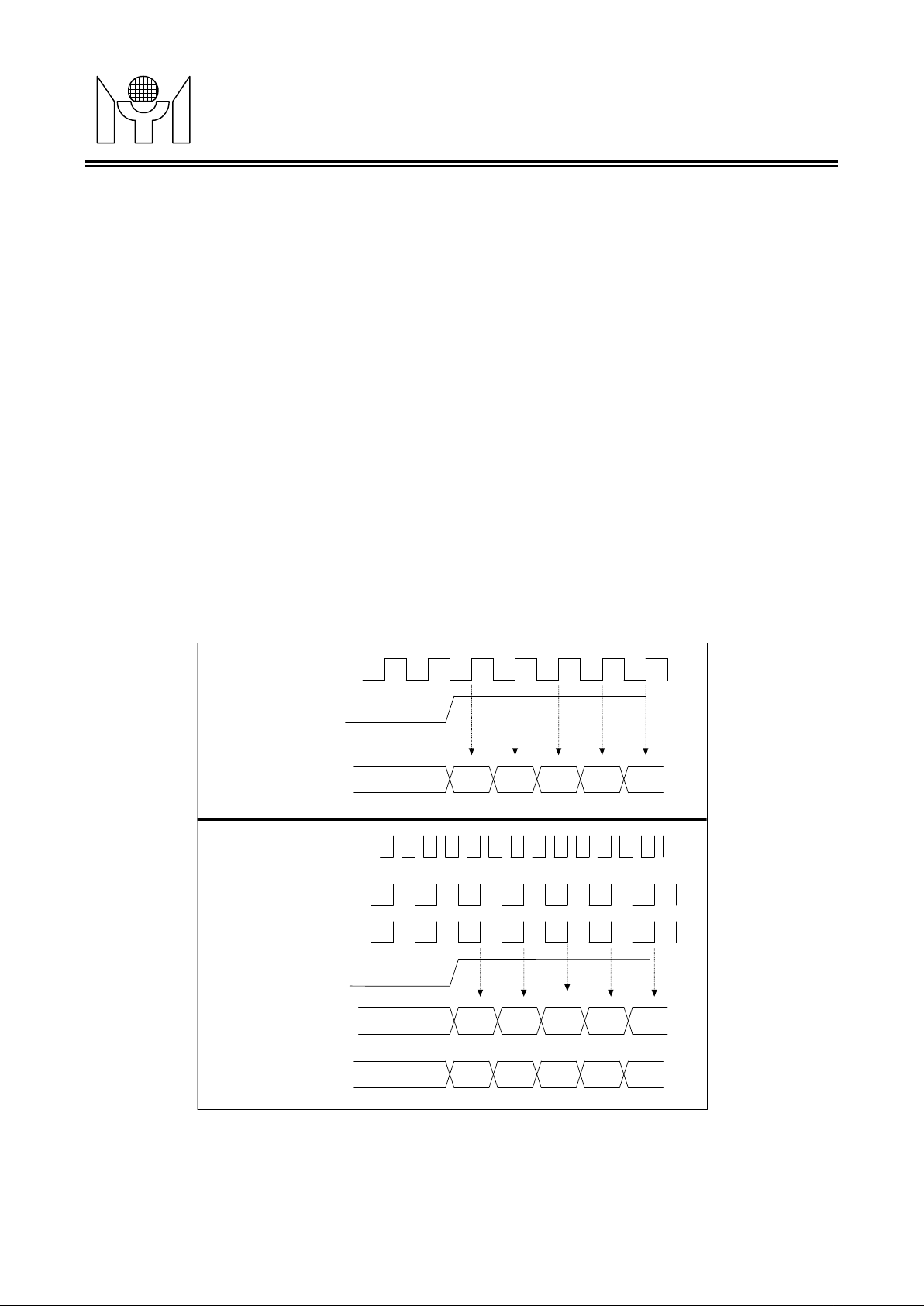

Input pixel A B

Interpolation pixel

SC

64

SC’

[a]

63

32

[b]

O

(Rev. 0.95)

[a]: duplicate filter

[b]: bilinear filter

[c]: user defined filter

[c]

32 63

Fig. 3.2.2 Scaling filter

Note: For scaling down, for both horizontal and vertical processing, MTL001 provides three methods: Pass

mode, Duplicate mode, and Bilinear mode.

3.2.2 Gain/Brightness Control

MTL001 provides Gain and Brightness control to adjust the contrast and brightness of output color by

Auto-white balance can be achieved by using this function.

3.2.3 Gamma Correcti on

bit Gamma table to fix this phenomenon. The 10-bit Gamma Table performs a better output quality, and is

commonly used together with dithering function. A traditional 8-bit Gamma correction table can also be used.

3.2.4 Color Dithering

MTL001 supports

In the latter case, users can turn on dithering function to avoid artificial contour due to truncation. The

dithering function works in two modes:

O = [(64-SC’)*A + SC’*B]/64

SC

¨ Static dithering: Dithering coefficient is fixed.

¨ Temporal dithering : Dithering coefficient is time dependent.

Revision 0.95 - 10 - 2000/06/14

MYSON

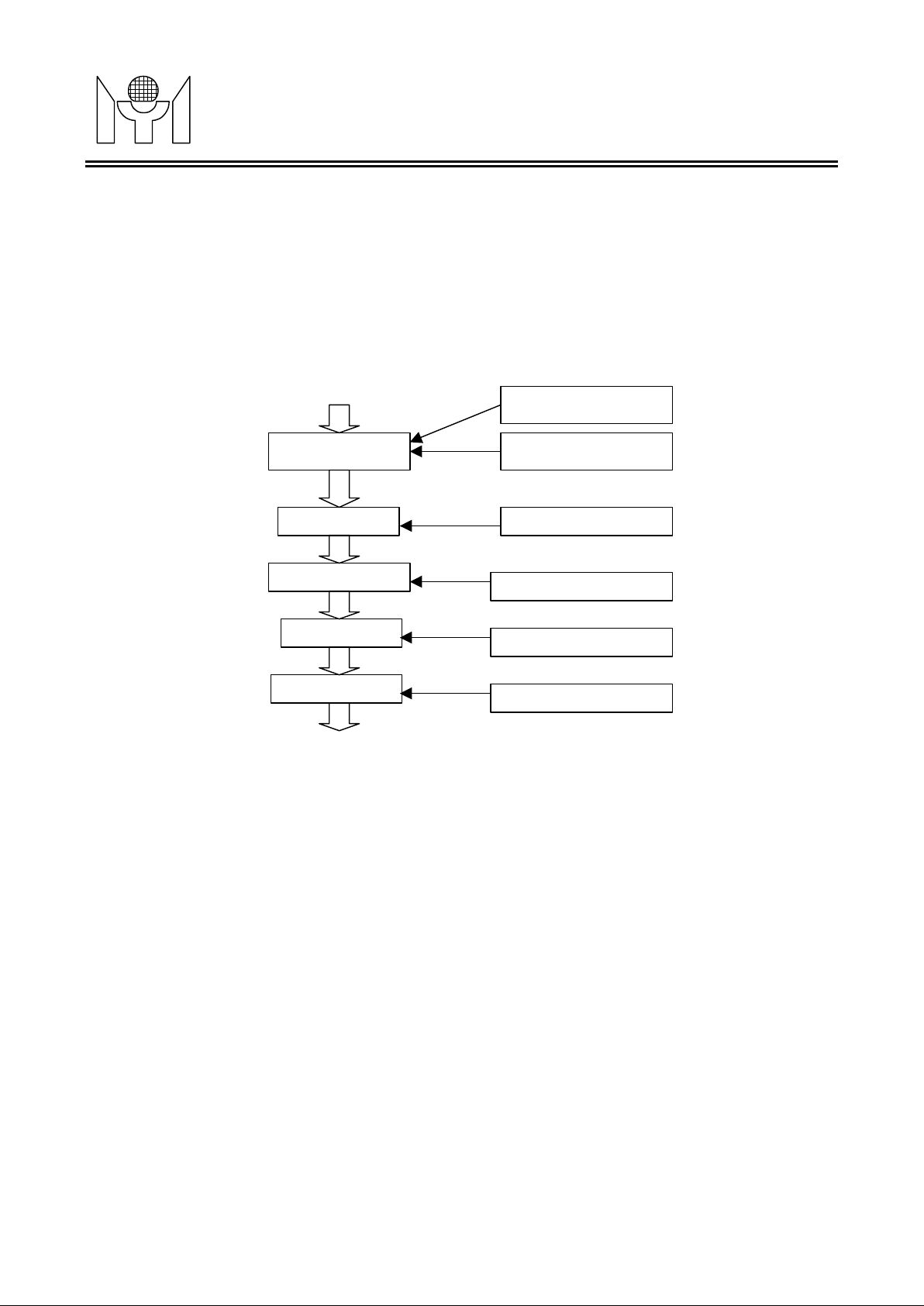

Output processor provides the interface for both LCD panel and OSD controller. MTL001 can work for framebuffer or non-frame-buffer mode. When in frame-buffer mode, there is no restriction between the timing of

input and output. When in non-frame-butter mode, output frame rate must be equal to input frame rate and

output display time must be equal to input display time due to the absence of frame buffer. Some features

based on using the frame buffer do not work in non-frame-buffer mode, for example the screen write, static

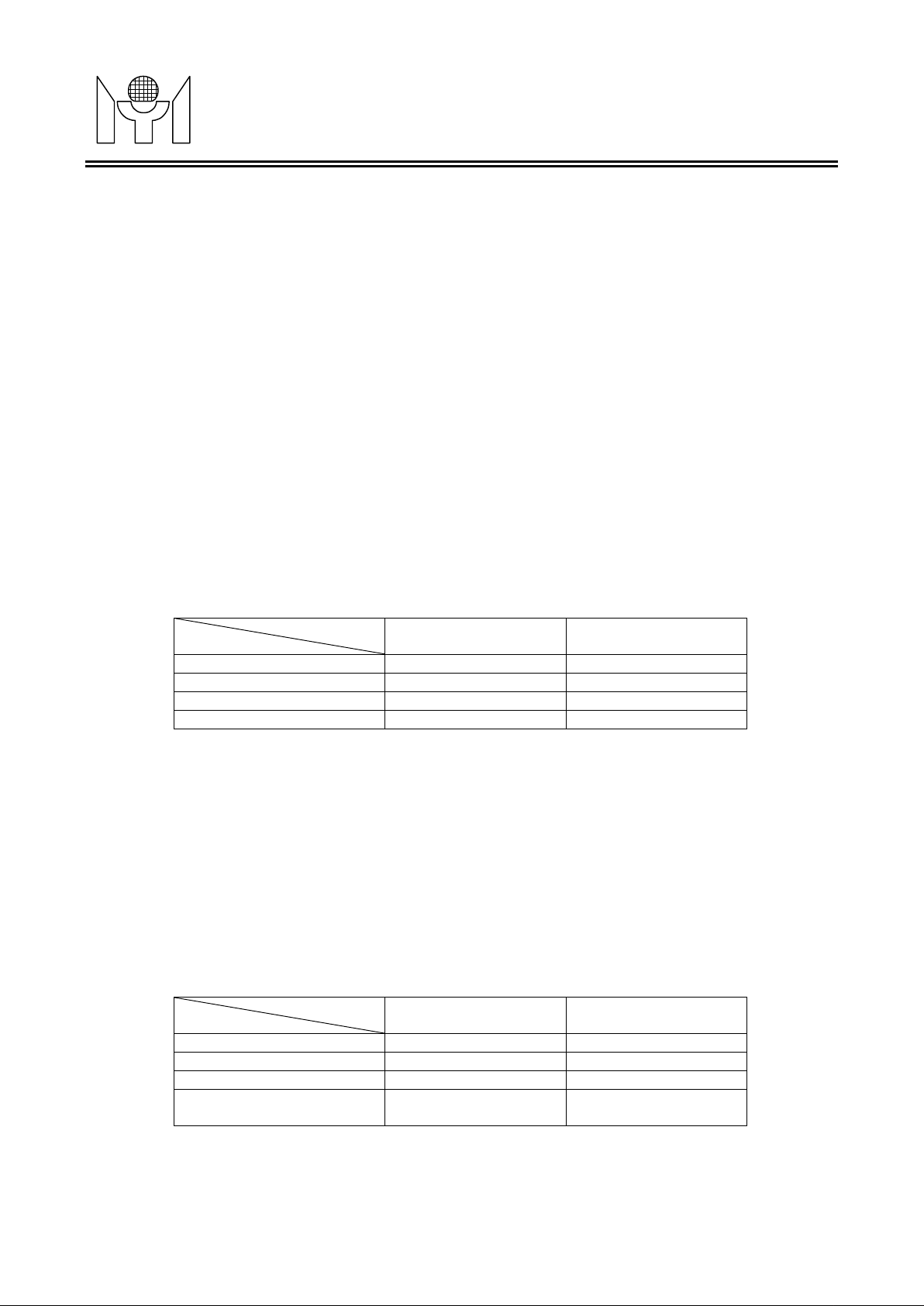

display timing modes:

Frame SYNC Mode

3.2.3 Display Timing modes

MTL001

TECHNOLOGY

(Rev. 0.95)

3.3 Outpu t Process or

General Descrip t io n

mode in de-interlace etc.

3.3.1 Display Timing Generatio n

There are three

¨ Frame-buf fer Mode: is used for frame rate conversion. External frame buffer is needed.

¨ Non-fr ame-buffer Mode: performs a low cost version of solution where the external frame buffer is not

needed. This mode is used in the condition that output frame rate is equal to input frame; some features

are disabled in this mode.

¨

gives the moving picture a smooth change.

: is used for video input. In this m ode, output frame is synchronized to input frame,

Frame Buff er Mode:

Input Frame

Non Frame Buf f er Mode

Input Frame

x

Lock point

Frame SYNC Mode

Input Frame

x

Lock point

Output Frame

External Frame Buffer

Output Frame

Output Frame

External Frame Buffer

Fig.

Revision 0.95 - 11 - 2000/06/14

MYSON

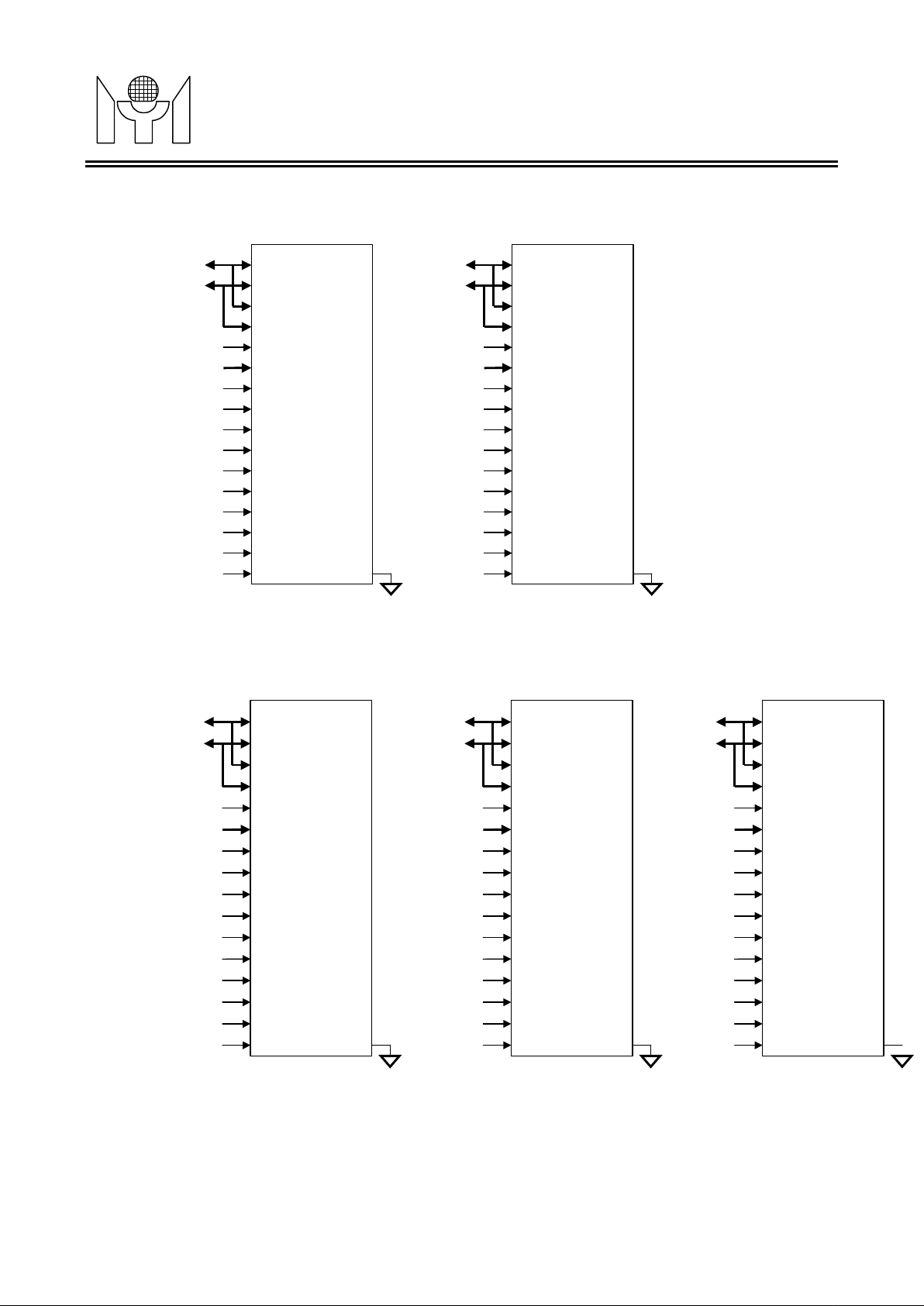

Is designed to support TFT panels with single pixel input. Only PORT1 is active. The frequency of DCLK1 is

R1OUT/G1OUT

R1OUT/G1OUT

R2OUT/G2OUT

SINGLE PO RT

3.2.4 Display Data Timing

MTL001

TECHNOLOGY

3.3.2 OSD Overlay

MTL001 allows the integration of overlay data with the scaled output pixel stream. It provides a fully

compatible OSD interface. Individual OSD clock, OSD HSYNC and OSD VSYNC are sent to external OSD

device. MTL003 receives OSD Enable, OSD Red, OSD Green, OSD Blue, and OSD Intensity from external

OSD device.

3.3.3 RGB Outp u t Format

MTL001 output interface consists of two pixel ports, each containing Red, Green, and Blue color information

with a resolution of 6/8 bits per color. These two ports are PORT1 and PORT 2 respectively.

The control signals for output port are the display horizontal sync signal (DHSYNC), the display vertical sync

signal (DVSYNC) and the display data enable signal (DDEN).

All the signals mentioned above are synchronous to the output clock. The output timing relative to the active

edge of the output clock is programmable.

There are two RGB output formats:

¨ Sing l e Pixel Mode

equal to the internal display clock.

¨ Dual Pixel Mod e

Is designed to support TFT panels with dual pixel input. PORT1 and PORT2 are used. The first pixel is at

PORT1, and the second at PORT2.

(Rev. 0.95)

DCLK

DDEN

/B1OUT

DUAL PORT

DCLK

DCLK1

000 rgb0 rgb1 rgb2 rgb3 rgb4

DCLK2

DDEN

/B1OUT

/B2OUT

000 rgb0 rgb2 rgb4 rgb6 rgb8

000 rgb1 rgb3 rgb5 rgb7 rgb9

Fig.

Revision 0.95 - 12 - 2000/06/14

MYSON

SDRAM Config ur atio n

SGRAM Config u ratio n

MTL001

TECHNOLOGY

(Rev. 0.95)

3.4 Memo r y Inter f ace

General Descrip t io n

In frame buffer mode, the MTL001 connects to the external frame buffers by means of memory interface. The

external frame memory can be made for 1M516bits SDRAM, 256K532bits or 512K532bits SGRAM

devices. Due to different applications such as VGA, SVGA, XGA as well as SXGA, the image resolution of

input and output will be limited resulting from the bandwidth of memory interface. Two configurations with 24,

32 and 48 bits bus modes will be supported to resolve the bandwidth constraint in most of applications. The

clock for external frame memory devices can be provided from the internal PLL circuit or the external clock

applied to pin EXTMCLK and its frequency can be up to 118 MHz. The MTL001 also supplies a simple and

complete memory self-testing mechanism for SDRAM and SGRAM, which can be used to detect memory cell

status and to check connection in memory interface.

3.4.1

In current applications, the most popular arrangement of SDRAM is 1M516bits. To achieve the desired

bandwidth in memory interface, 2 or 3 devices are constructed in parallel. The m emory clock ranging from

50MHz to 118MHz is tuned by giving appropriate parameters f or the internal PLL circuit. In two devices

configuration, the 24 and 32 bits bus modes are supported. In three devices, the 48 bits bus mode is

supported. In 24 bits bus mode, the maximum supported input image resolution is up to 10245768 @ 60Hz.

In 32 and 48 bits bus mode, the maximum supported input image resolution is up to 1 0245768 @ 85Hz.

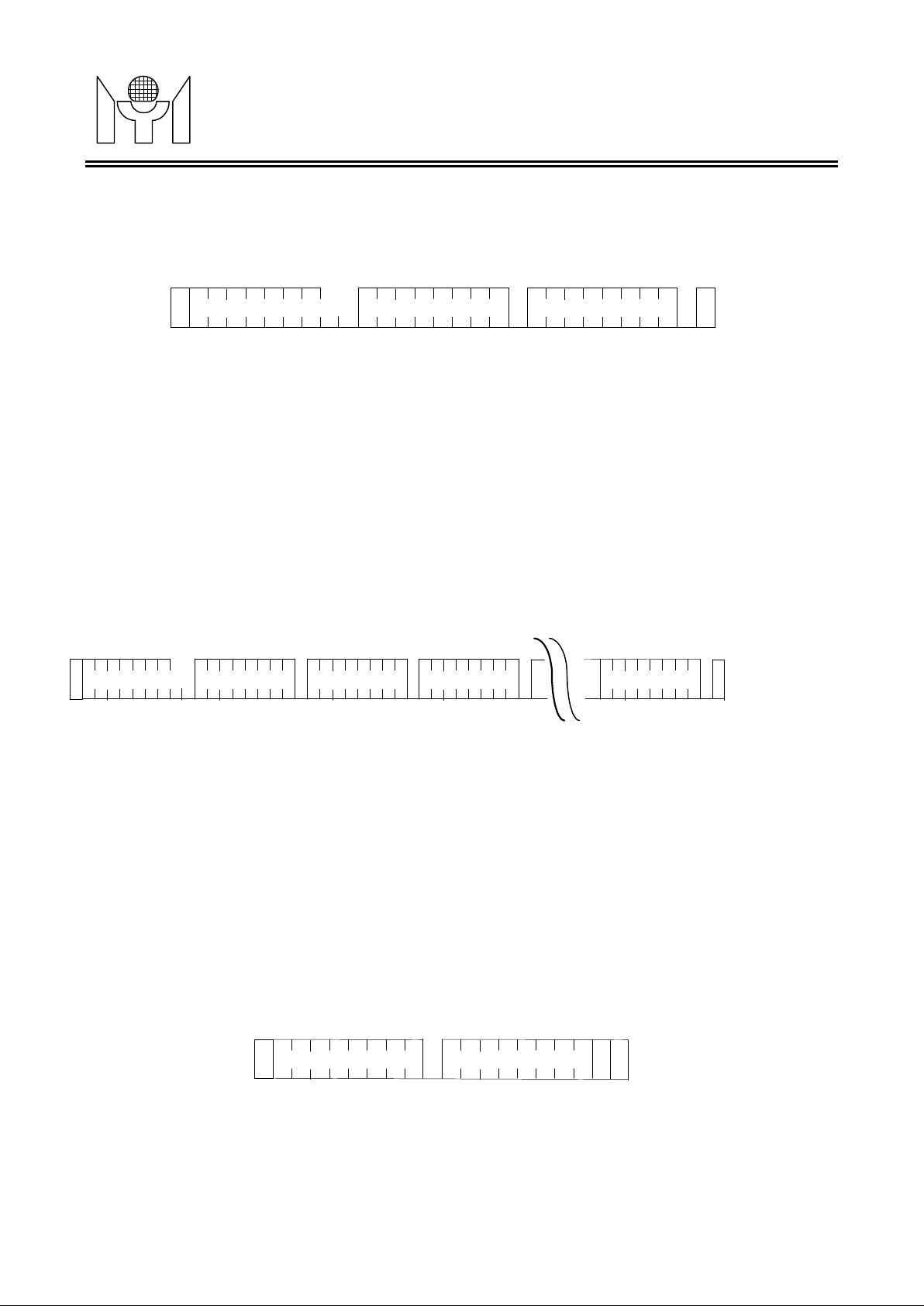

Table 3.4.1 gives the configuration for different input and output image format. Figure 3.4.1 sho ws the

connection between the MTL001 and SDRAM devices in 2 configurations.

Unit: device

Output Resolution

Input Resolution

YUV 2 2

VGA (6405480) 2 2

SVGA (8005600) 2 2

XGA (10245768) 2 2

Table 3.4.1 SDRAM configuration in different input and output modes

3.4.2

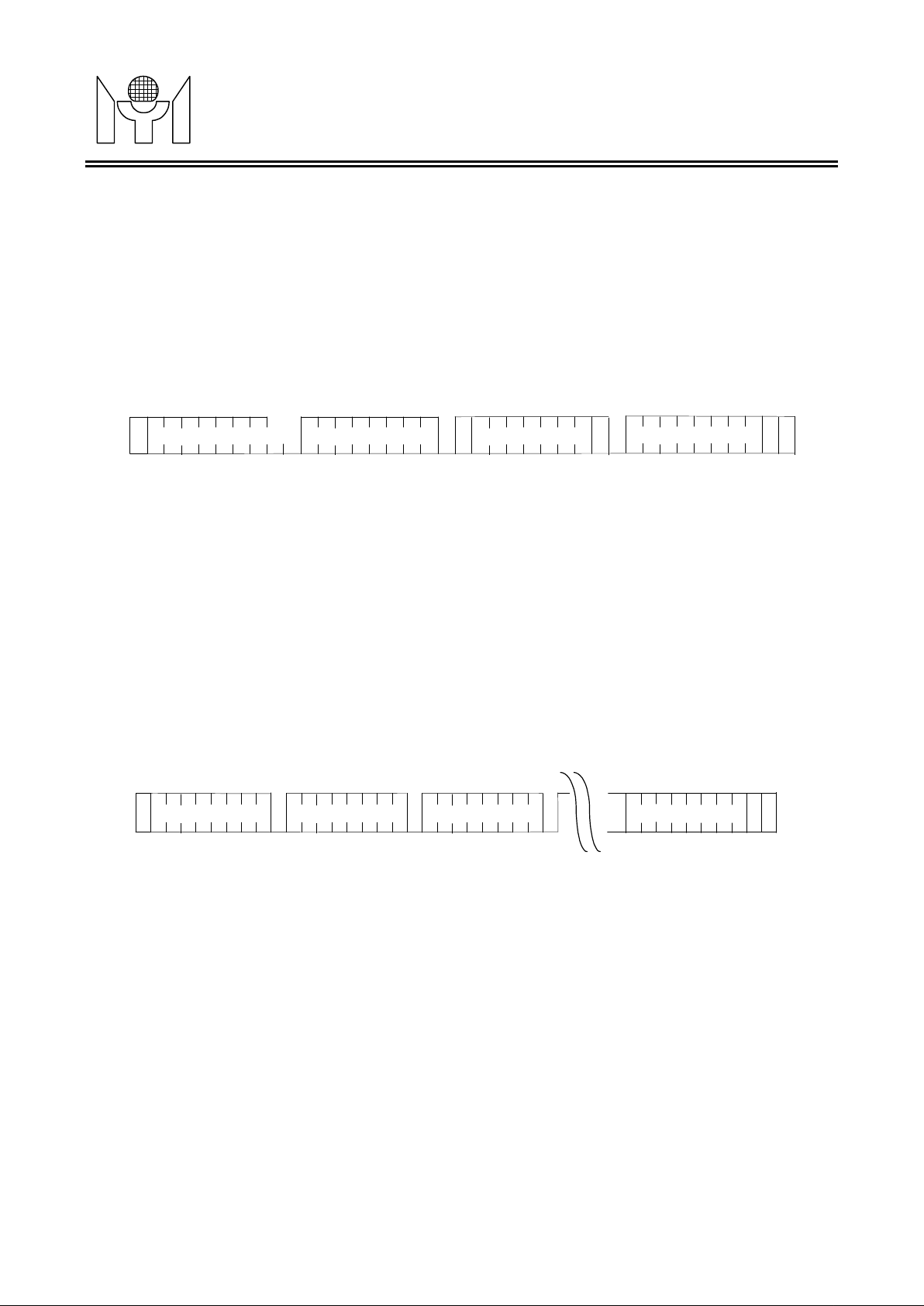

The SGRAM devices in 256K532bits and 512K532bits constructions are usually used to feature the wide

data bus for high speed applications. In case of SGRAM usage, the 32 bits data bus of each device is divided

into 2 parts to store input image data. The memory clock is adjustable to achieve the desired range of

performance like the SDRAM case above. The maximum supported input image resolution in 24 bits bus

mode (2 devices) is up to 8005600 @ 85Hz, and both the 32 bits bus mode (2 devices) and the 48 bits bus

mode (3 devices) can support maximum input image resolution up to 10245768 @ 85Hz. Table 3.4.2

provides the configuration for different input and output image form at. Figure 3.4.2 and 3.4.3 show the

connection between the MTL001 and SGRAM devices in 2 configurations by 256K532bits and 512K532bits

constructions respectively.

Unit: device

Output Resolution

Input Resolution

YUV 2 2

VGA (6405480) 2 2

SVGA (8005600) 2 2

XGA (10245768)

(512Kx32 bits / 256Kx32 bits)

SVGA XGA

SVGA XGA

2 / 3 2 / 3

Table 3.4.2 SGRAM configurations in different input and output modes

Revision 0.95 - 13 - 2000/06/14

MYSON

DQ7~0

DQ15~8

A8~0

LDQM

UDQM

/CS

/RAS

/CAS

CKE

/WE

MCKE

MCS

MRAS#

MCAS#

MWE#

DQM0

DQM1

MA[8:0]

SDRAM(1M

CLK

MCK

MD[7:0]

MD[31:24]

A10BAA9

DQM2/MA9

DQM3/MA10

BA/MA11

DQ7~0

DQ15~8

A8~0

LDQM

UDQM

/CS

/RAS

/CAS

CKE

/WE

CLK

A10BAA9

MCKE

MCS#

MRAS#

MCAS#

MWE#

DQM0

DQM1

MA[8:0]

MCK

DQM2/MA9

DQM3/MA10

BA/MA11

MD[15:8]

MD[39:32]

SDRAM(1M

/WE

/WE

/WE

MTL001

TECHNOLOGY

516bits) 5 2

516bits) 5 3

(Rev. 0.95)

MD[7:0]

MD[31:24]

BA/MA11

DQM3/MA10

MA[8:0]

DQM0

DQM1

MCKE

MCS#

MRAS#

MCAS#

MWE#

DQ7~0

DQ15~8

BA

A10

A9DQM2/MA9

A8~0

LDQM

UDQM

CLKMCK

CKE

/CS

/RAS

/CAS

MD[15:8]

MD[39:32]

BA/MA11

DQM3/MA10

DQM2/MA9

MA[8:0]

DQM0

DQM1

MCK

MCKE

MCS#

MRAS#

MCAS#

MWE#

DQ7~0

DQ15~8

BA

A10

A9

A8~0

LDQM

UDQM

CLK

CKE

/CS

/RAS

/CAS

MD[23:16]

MD[47:40]

BA/MA11

DQM3/MA10

DQM2/MA9

MA[8:0]

DQM0

DQM1

MCK

MCKE

MCS#

MRAS#

MCAS#

MWE#

Fig. 3.4.1 The interface between MTL001 and 1Mx16 bits SDRAM

DQ7~0

DQ15~8

BA

A10

A9

A8~0

LDQM

UDQM

CLK

CKE

/CS

/RAS

/CAS

Revision 0.95 - 14 - 2000/06/14

MYSON

/WE

/WE

/WE

/WE

/WE

MTL001

TECHNOLOGY

SGRAM(128K532bits52 ) 5 2

MD[7:0]

MD[31:24]

BA/MA11 A9(BA)

MA[8:0]

DQM0

DQM1

DQM2/MA9

DQM3/MA10

MCKE

MCS#

MRAS#

MCAS#

MWE#

DQ7~0

DQ15~8

DQ23~16

DQ31~24

A8~0

DQM0

DQM1

DQM2

DQM3

CLKMCK

CKE

/CS

/RAS

/CAS

DSF

MD[15:8]

MD[39:32]

BA/MA11

MA[8:0]

DQM0

DQM1

DQM2/MA9

DQM3/MA10

MCK

MCKE

MCS#

MRAS#

MCAS#

MWE#

(Rev. 0.95)

DQ7~0

DQ15~8

DQ23~16

DQ31~24

A9(BA)

A8~0

DQM0

DQM1

DQM2

DQM3

CLK

CKE

/CS

/RAS

/CAS

DSF

SGRAM(128K532bits52 ) 5 3

MD[7:0]

MD[31:24]

BA/MA11 A9(BA)

MA[8:0]

DQM0

DQM1

DQM2/MA9

DQM3/MA10

MCKE

MCS#

MRAS#

MCAS#

MWE#

DQ7~0

DQ15~8

DQ23~16

DQ31~24

A8~0

DQM0

DQM1

DQM2

DQM3

CLKMCK

CKE

/CS

/RAS

/CAS

Fig. 3.4.2 The interface between MTL001 and 256Kx32 bits SGRAM

DSF

MD[15:8]

MD[39:32]

BA/MA11

MA[8:0]

DQM0

DQM1

DQM2/MA9

DQM3/MA10

MCK

MCKE

MCS#

MRAS#

MCAS#

MWE#

DQ7~0

DQ15~8

DQ23~16

DQ31~24

A9(BA)

A8~0

DQM0

DQM1

DQM2

DQM3

CLK

CKE

/CS

/RAS

/CAS

DSF

MD[23:16]

MD[47:40]

BA/MA11

MA[8:0]

DQM0

DQM1

DQM2/MA9

DQM3/MA10

MCK

MCKE

MCS#

MRAS#

MCAS#

MWE#

DQ7~0

DQ15~8

DQ23~16

DQ31~24

A9(BA)

A8~0

DQM0

DQM1

DQM2

DQM3

CLK

CKE

/CS

/RAS

/CAS

DSF

Revision 0.95 - 15 - 2000/06/14

MYSON

GPIO[2]

GPIO[2]

GPIO[2]

GPIO[2]

GPIO[2]

MTL001

MD[7:0]

MD[31:24]

BA/MA11

MA[8:0]

DQM0

DQM1

DQM2/MA9

DQM3/MA10

MCKE

MCS#

MRAS#

MCAS#

MWE#

TECHNOLOGY

SGRAM(256K532bit s52 ) 5 2

DQ7~0

DQ15~8

DQ23~16

DQ31~24

A10(BA)

A9

A8~0

DQM0

DQM1

DQM2

DQM3

CLKMCK

CKE

/CS

/RAS

/CAS

/WE

DSF

MD[15:8]

MD[39:32]

BA/MA11 A10(BA)

MA[8:0]

DQM0

DQM1

DQM2/MA9

DQM3/MA10

MCKE

MCS#

MRAS#

MCAS#

MWE#

DQ7~0

DQ15~8

DQ23~16

DQ31~24

A9

A8~0

DQM0

DQM1

DQM2

DQM3

CLKMCK

CKE

/CS

/RAS

/CAS

/WE

(Rev. 0.95)

DSF

MD[7:0]

MD[31:24]

BA/MA11

MA[8:0]

DQM0

DQM1

DQM2/MA9

DQM3/MA10

MCKE

MCS#

MRAS#

MCAS#

MWE#

SGRAM(256K532bit s52 ) 5 3

DQ7~0

DQ15~8

DQ23~16

DQ31~24

A10(BA)

A9

A8~0

DQM0

DQM1

DQM2

DQM3

CLKMCK

CKE

/CS

/RAS

/CAS

/WE

DSF

MD[15:8]

MD[39:32]

BA/MA11 A10(BA)

MA[8:0]

DQM0

DQM1

DQM2/MA9

DQM3/MA10

MCKE

MCS#

MRAS#

MCAS#

MWE#

DQ7~0

DQ15~8

DQ23~16

DQ31~24

A9

A8~0

DQM0

DQM1

DQM2

DQM3

CLKMCK

CKE

/CS

/RAS

/CAS

/WE

DSF

MD[23:16]

MD[47:40]

BA/MA11

MA[8:0]

DQM0

DQM1

DQM2/MA9

DQM3/MA10

MCKE

MCS#

MRAS#

MCAS#

MWE#

DQ7~0

DQ15~8

DQ23~16

DQ31~24

A10(BA)

A9

A8~0

DQM0

DQM1

DQM2

DQM3

CLKMCK

CKE

/CS

/RAS

/CAS

/WE

DSF

Fig. 3.4.3 The interface between MTL001 and 512Kx32 bits SGRAM

Revision 0.95 - 16 - 2000/06/14

MYSON

frame buffer, and display output as well.

C interface supports Random Write, Sequential Write, Current Address Read, Random Read and

For Random Write operation, it contains the slave address with R/W bit set to 0 and the word address which

is comprised of 8 bits that provides the access to any one of the 256 bytes in the selected memory range.

MTL001

TECHNOLOGY

(Rev. 0.95)

3.5 Host Inter fac e

General Descrip t io n

The primary function of Host Interface is to provide the interface between MTL001 and external CPU by 2wire I2C Bus or Direct Bus selected by the input pin BUSSEL. It can generate a ll the I/O decoded control

timing to control all the registers in MTL001. The other function is Screen Write, which allows users to clear

3.5.1 I2C Serial Bus

The I2C serial interface uses 2 wires, SCK (clock) and SDA(data I/O) respectively. The SCK is used as the

sampling clock and SDA is a bi-directional signal for the data. The communication must be started with a

valid START condition, concluded with STOP condition and acknowledged by ACK condition by the receiver.

The I2C bus device address of MTL001 is 0111010x.

AD[0] SCK, serial bus clock.

AD[1] SDA, bi-directional serial bus data.

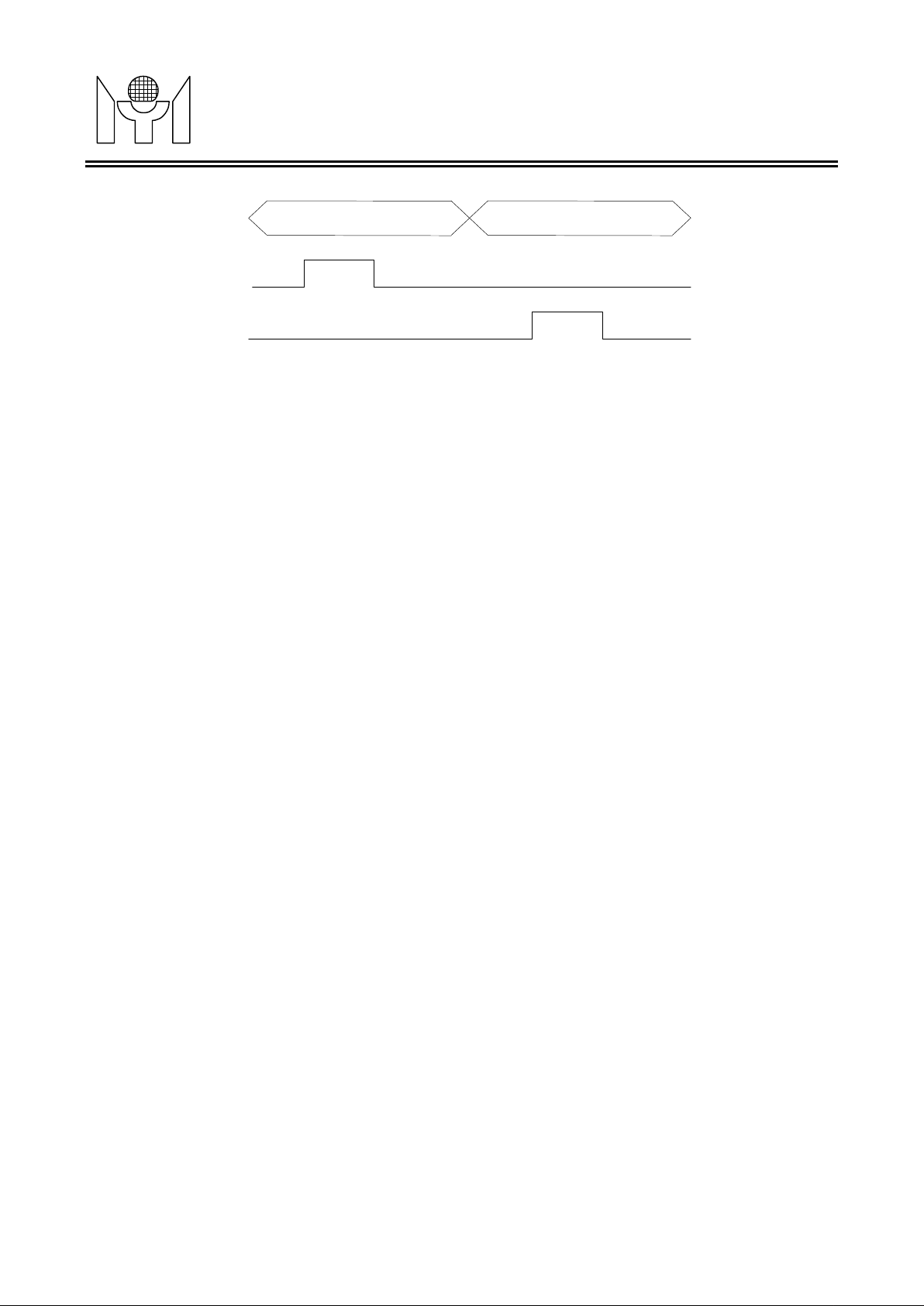

The START condition means a HIGH to LOW transition of SDA when SCK is high, the STOP condition

means a LOW to HIGH transition of SDA when SCK is high. And data of SDA can only change when SCK is

low. Ref. Fig.3.5.1.

SDA

SCK

START

Fig. 3.5.1 START, STOP ,and DATA definition

2

The I

Sequential Read operations.

¨ Random Write

Upon receipt of the word address, MTL003 responds with an Acknowledge and waits for the next eight bits of

data again, responding with an Acknowledge, and then the master generates a stop co ndition. Ref. Fig.3.5.2.

DATA

CHANGE

DATA

CHANGE

STOP

Revision 0.95 - 17 - 2000/06/14

MYSON

3.5.2 Random Write

Current Add ress Read

access address is n, the read data should access from address n+1. Upon receipt of the slave address with

bits data. After receiving data

MTL001

TECHNOLOGY

S

T

A

R

T

SDA

¨ Sequential Writ e

The initial step of Sequential Write is the same as Random Write, after the receipt of each word data,

MTL001 will respond with an Acknowledge and then internal address counter will increment by one for next

data write. If the master stops writing data, it will generate stop condition. Ref. Fig. 3.5.3.

S

T

A

SLAVE

R

ADDRESS

T

SLAVE

ADDRESS

WORD

ADDRESS

A

W

C

K

Fig.

DATA n

WORD

ADDRESS

DATA n+1

DATA

A

C

K

DATA n+x

(Rev. 0.95)

S

T

O

P

A

C

K

S

T

O

P

SDA

A

W

C

K

Fig. 3.5.3 Sequential Write

¨

MTL001 contains an address counter which maintains the last access address incremented by one. If the last

R/W bit set to 1, MTL001 generates an Acknowledge and transmits the eight

the master will generate a stop condition instead of an Acknowledge. Ref. Fig. 3.5.4.

SDA

S

T

A

R

T

A

C

K

SLAVE

ADDRESS

A

C

K

A

R

C

K

A

C

K

DATA

A

C

K

S

T

O

P

Fig. 3.5.4 Current Address Read

Revision 0.95 - 18 - 2000/06/14

MYSON

The operation of Random Read allows access to any address. Before the reading data operation, it must

the master issues the start condition, slave address and then the word

address it is to read. After the word address acknowledge, the master generating a start condition again and

slave address with R/W bit is set to 1. MTL001 then transmits the 8 bits of data. Upon the completion of

The Direct Bus use AD[7:0], HWR#, HRD#, ALE, HCS# as the interface with host. ALE is used to latch read

S

MTL001

TECHNOLOGY

¨ Rando m Read

issue a “dummy write” operation —

receiving data, the master will generate a stop condition instead of an Acknowledge. Ref. Fig 3.5.5.

S

T

A

R

T

A

C

K

SLAVE

ADDRESS

A

R

C

K

SDA

T

A

R

T

SLAVE

ADDRESS

WORD

ADDRESS

A

W

C

K

Fig. 3.5.5 Random Read

(Rev. 0.95)

S

T

DATA

O

P

¨ Sequent i al Read

The initial step can be as either Current Address Read or Random Read. The first read data is transmitted in

the same manner as other read methods. However, the master generates an Acknowledge indicating that it

requires more data to read. MTL001 continues to output data for each Acknowledge received. The output

data is sequential and the internal address counter increments by one for next read data. Ref. Fig. 3.5.6.

S

T

A

SLAVE

R

ADDRESS

T

SDA

A

R

C

K

Fig. 3.5.6 Sequential Read

3.5.2 8-bit Direct Bus

or write address from AD[7:0] and HRD#, HWR# to access data. Ref. Fig. 3.5.7.

DATA n

A

C

K

DATA n+1

DATA n+x

A

C

K

S

T

O

P

AD[7:0] Address and data multiplex bus.

HRD# CPU read data strobe, Active Low.

HWR# CPU write data strobe, Active Low.

ALE ALE =1 latch read or write address, ALE=0 represents I/O data.

HCS# Enable signal for CPU access, Active Low.

Revision 0.95 - 19 - 2000/06/14

MYSON

what events are happening. After the operation is completed, Firmware needs to clear interrupt status by

GPIO[7:6] pins. One is to set them as output only GPIO pins, and the other is to set them as Composite

Writing data to Reg. F4h/D0 when

pin to output ADHS which is HSYNC signal decoded from VGA input Composite signal by the

Writing data to F4h/D6 when

HWR/HRD

MTL001

TECHNOLOGY

AD[7:0]

ALE

Fig. 3.5.7 Direct Bus Timing

3.5.3 Interrupt

MTL001 supports one interrupt output signal (IRQ) which can be programmed to provide SYNC related or

function status related interrupts to the system. Upon receiving the interrupt request, Firmware needs to

firstly check the interrupt event by reading the Interrupt Flag Control registers (Reg. E8h and E9h) to decide

writing the same registers Reg. E8h and E9h. Furthermore, by using the Interrupt Flag Enable registers (Reg.

EAh and EBh), each interrupt event can be masked.

3.5.4 Screen Write

Screen Write function can be used to clear frame buffer m emory and display output by a fixed value defined

in Reg. C6h, C7h, C8h.

DATAADDRESS

(Rev. 0.95)

3.5.5 Bi-directi o nal GPIO

MTL001 supports eight General Purpose Input and Output (GPIO) pins GPIO[7:0] on chip. The GPIO[5:0]

pins are bi-directional GPIO pins, and the GPIO[7:6] pins are output only GPIO pins. T here are two functions

for

decoded VSYNC/HSYNC for A/D converters in VGA input path. The data and I/O dir ection of GPIO[7:0] pins

are controlled by Reg. F4h and F5h respectively, and each bit in the register is mapped to GPIO[7:0]

correspondingly. The following description is the process to control GPIO[0] and GPIO[6] in detail, and the

control processes of GPIO[4:1] and GPIO[7] also follows in the same m anner.

¨ Bi -directio nal GPIO contr ol proc ess

q Setting Reg. F5h /D0 = 0 or 1 to assign GPIO[0] as output or input.

q

Reg. F4h/D0 when GPIO[0] is input.

¨ Outpu t onl y GPIO contro l proc ess

q Setting Reg. F5h/D6 = 0 or 1 to assign GPIO[6] as output or tri-state.

q Setting Reg. F6h/D0 = 0 to select output source from Reg. F4h/D6 or setting it as 1 to make GPIO[6]

MTL001.

q

F5h/D6 = 0. If F6h/D0 is set to 1, the GPIO[6] pin outputs ADHS for AD converters in VGA input path.

3.5.6 Update Regist er Contents

I/O write operation to some consecutive register set can have the “Double Buffer” effect by setting the

Reg. C1h/D4. Written data is first stored in an intermediate bank of latches and then transf erred to the active

register set by setting Reg. C1h/D1-0.

GPIO[0] is assigned to output status, otherwise reading data from

GPIO[6] is assigned to output only GPIO pin, that is, F6h/D0 = 0 and

Revision 0.95 - 20 - 2000/06/14

Loading...

Loading...