MYSON MTD981AF, MTD981AG Datasheet

MYSON

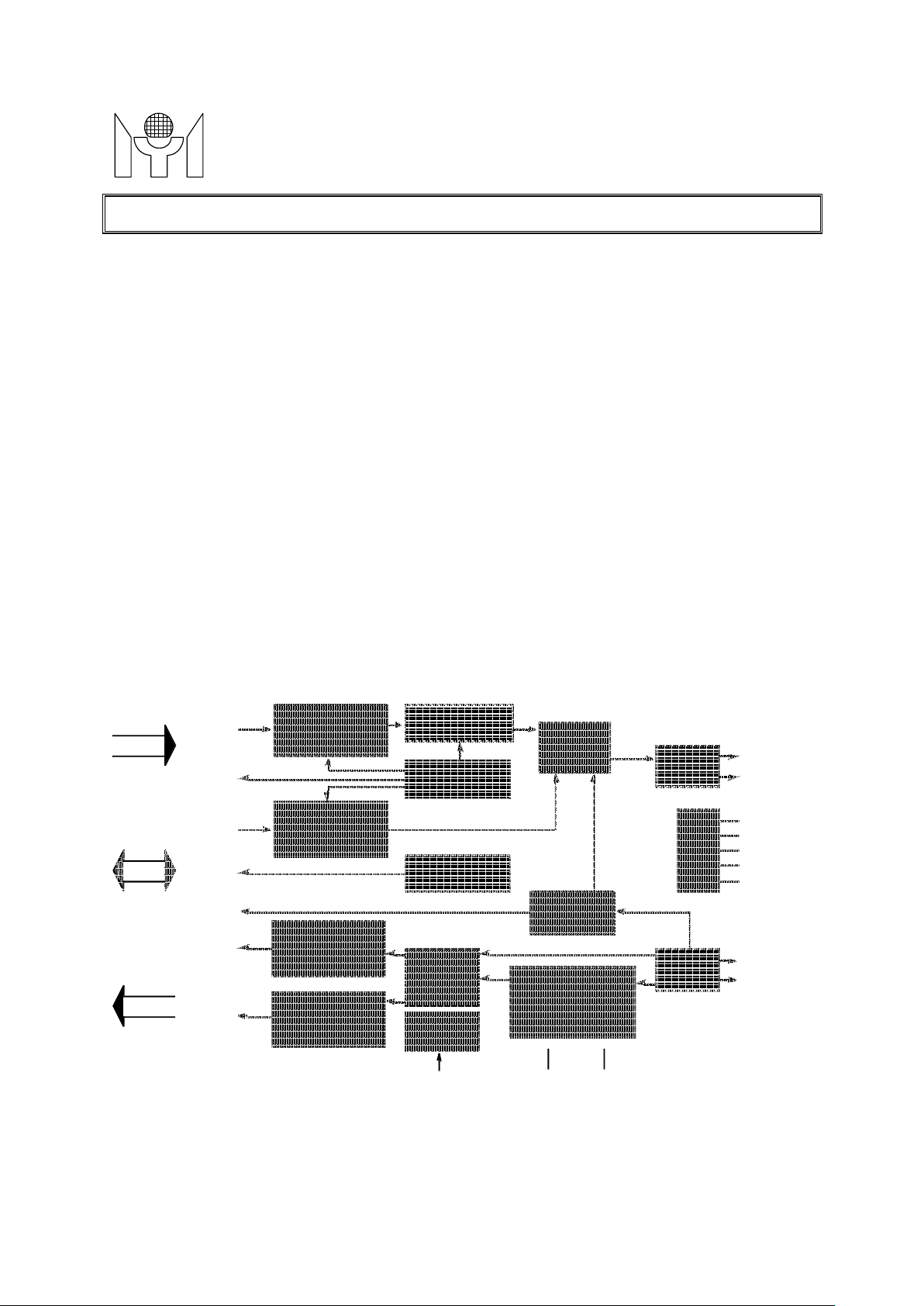

4B/5B Encoder,

Parallel/Serial,

Decoder, Serial/

Serial/Parallel

Descrambler,

5B/4B Decoder

Carrier Sense,

Collision Detect

MLT3 Encoder

Shaper &

Auto Nego-

Adaptive EQ.

Baseline Wander

Corrector, MLT3

Decoder, NRZI /NRZ

Receiver

COLLISION

MTD981A

TECHNOLOGY

10/100 Ethernet Transceiver

FEATURES

· 10BASE-T, 100BASE-TX, and 100BASE-FX IEEE-802.3 compliant transmit and receive functions

· IEEE 802.3u Clause 28 compliant Auto-Negotiation function

· Full duplex operation capable

· Baseline wander compensation

· Supports 1:1 or 1.25:1 transmit transformer

· Output waveform shaping – no external filter required

· LED indicators: LINK, TX, RX, COL, 100, 10, FDX

· Single 3.3-V power supply with 5V tolerant I/O

· 100-pin PQFP package

GENERAL DESCRIPTIONS

The MTD981A is a highly integrated analog interface IC for twisted pair Ethernet applications. It provides the

active circuitry to interface IEEE 802.3 media independent interface (MII) compliant controllers to 10BASE-T

or 100BASE-TX media. It also provides an ECL-type interface for use with 100BASE-FX fiber networks.

The MTD981A supports full duplex operation at 10 and 100 Mbps. Its operating condition can be set by

using Auto-Negotiation, parallel detection, or manual control. The MTD981A is ideal as a media interface for

10BASE-T/100BASE-TX network interface cards, motherboards, 10/100 repeaters, switching hubs, and

external PHYs.

BLOCK DIAGRAM

100M

Transmit

10M

MII Reg-

isters &

Interface

MII Serial

Management &

Control

Receive

Logic

Scrambler,

Parallel/Serial

Manchester

Encoder

Manchester

Parallel

NRZ/NRZI,

TX Clock

Generator

Clock

Recovery

Clock Ref-

erence

Pulse

Filter

tiation

Vcc Ground

10M

100M

UTP

Driver

LEDs

UTP

TXOP

TXON

LINK

TX

RX

100X

RXIP

RXIN

This datasheet contains new product information. Myson Technology reserves the rights to modify the product specification without

notice. No liability is assumed as a result of the use of this product. No rights under any patent accompany the sale of the product.

1/18

MTD981A Revision 1.2 02/19/2001

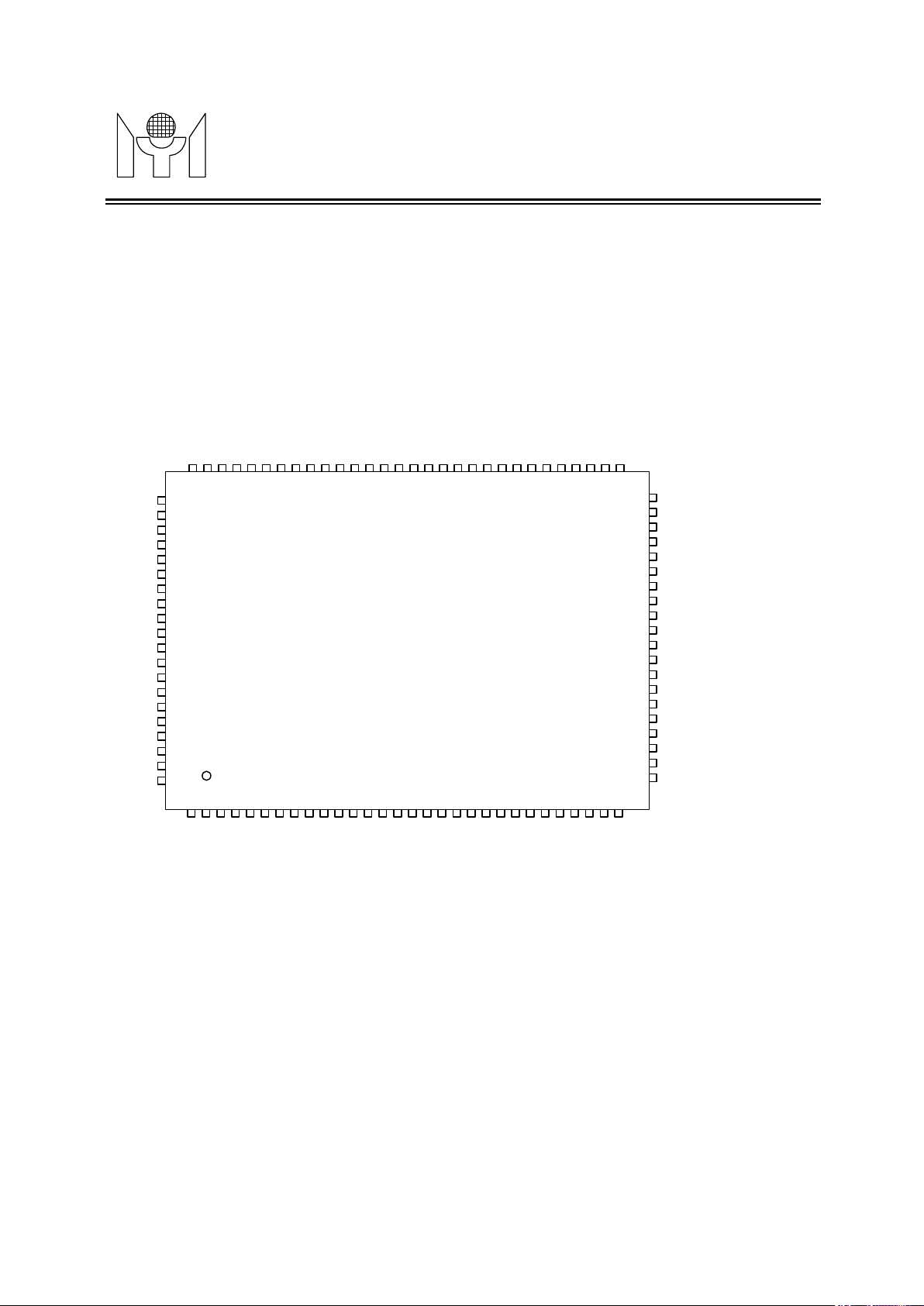

MYSON

40

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30

NC12

NC13

NC11

NC10

80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51

TECHNOLOGY

PIN CONNECTION

NC17

NC18

NC19

NC20

NC21

VAAEQ

VAAFQ

MTD981A

LEDSPD_

LEDCOL_

LEDLNK_

GNDCRV

SEL1

SEL0

VAACRV

SEL2

OGND

LEDFD_

LED10_

ANEN

LEDRX_

LEDTX_

OVDD

MDINT

CRS

COL

NC16

NC15

NC14

RPTR

SDP

RXIN

RXIP

GNDEQ

FIN

FIP

TEST2

FOP

FON

GNDREF

RBIAS

VAAREF

NC0

NC1

GNDT

TXOP

TXON

VAAT

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

NC2

NC3

NC4

NC5

NC6

MODE0

50

TXD3

49

TXD2

48

TXD1

47

TXD0

46

CVDD

45

CGND

44

TXEN

43

TXCLK

42

TXER

NC9

41

RXER

40

RXCLK

39

RXDV

38

OGND

37

OVDD

36

RXD0

35

RXD1

34

RXD2

33

RXD3

32

MDC

31

MTD981AF

MTD981AF

NC8

NC7

TP125

MODE1

PHYAD0

PHYAD1

PHYAD2

PHYAD3

PHYAD4

OVDD

OGND

GNDPLL

VAAPLL

PD

RST_

TEST

RMIISEL

CKIN

GNDT

ISO

ISODEF

2

MTD981A Revision 1.2 02/19/2001

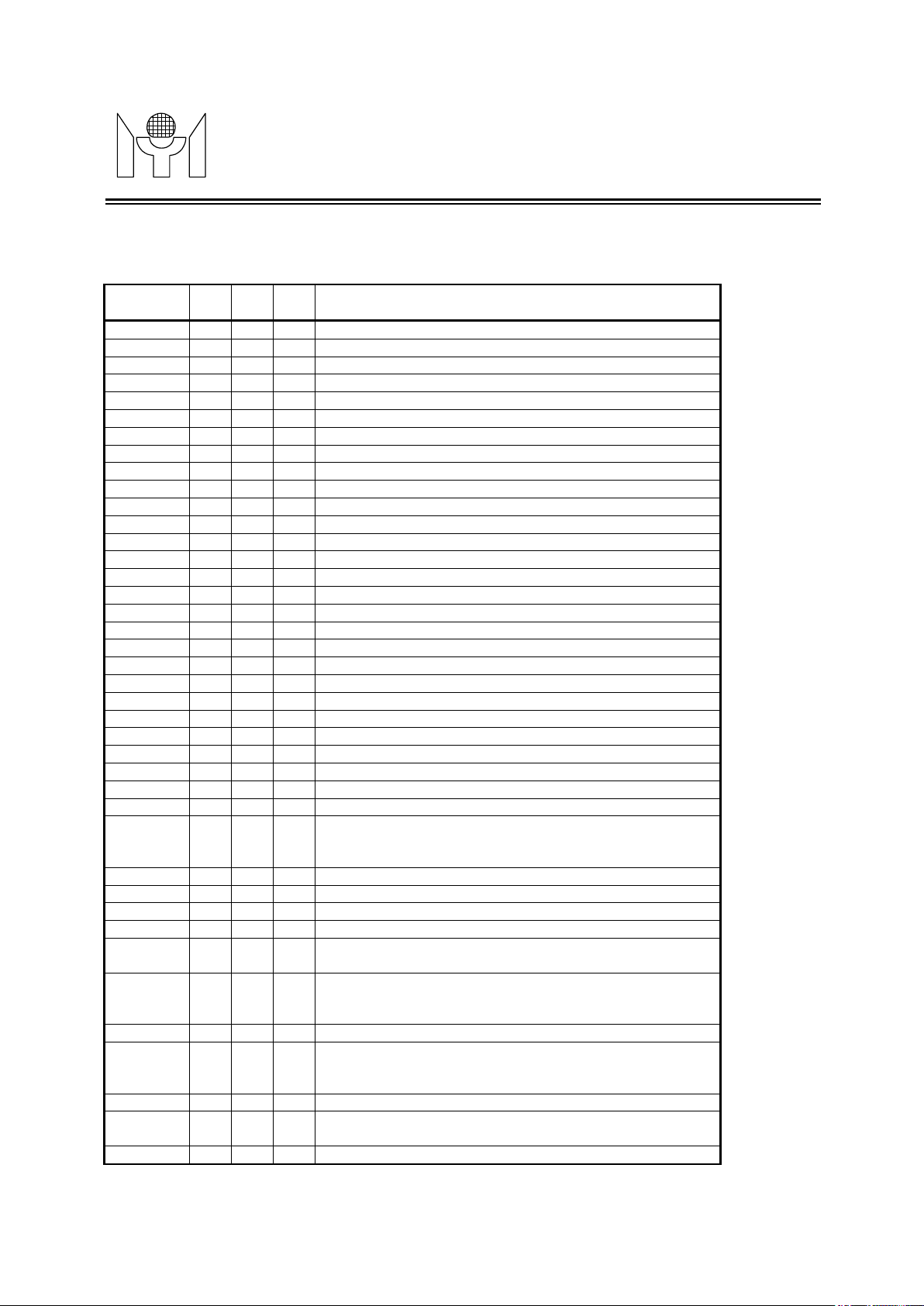

MYSON

COL

CRS

MDINT

LEDSPD_

TP125

MODE1

PHYAD0

PHYAD1

60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

TECHNOLOGY

LEDFD_

LED10_

VAAEQ

VAAFQ

ANEN

SEL1

SEL0

VAACRV

SEL2

MTD981A

LEDCOL_

LEDLNK_

GNDCRV

OGND

LEDRX_

LEDTX_

OVDD

RPTR

SDP

RXIN

RXIP

GNDEQ

FIN

FIP

TEST2

FOP

FON

GNDREF

RBIAS

VAAREF

NC0

NC1

GNDT

TXOP

TXON

VAAT

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

ISODEF

MODE0

MTD981AG

RST_

TEST

RMIISEL

CKIN

GNDT

ISO

VAAPLL

PD

GNDPLL

PHYAD2

PHYAD3

PHYAD4

OVDD

OGND

40

TXD3

39

TXD2

38

TXD1

37

TXD0

36

CVDD

35

CGND

34

TXEN

33

TXCLK

32

TXER

31

RXER

30

RXCLK

29

RXDV

28

OGND

27

OVDD

26

RXD0

25

RXD1

24

RXD2

23

RXD3

22

MDC

21

3

MTD981A Revision 1.2 02/19/2001

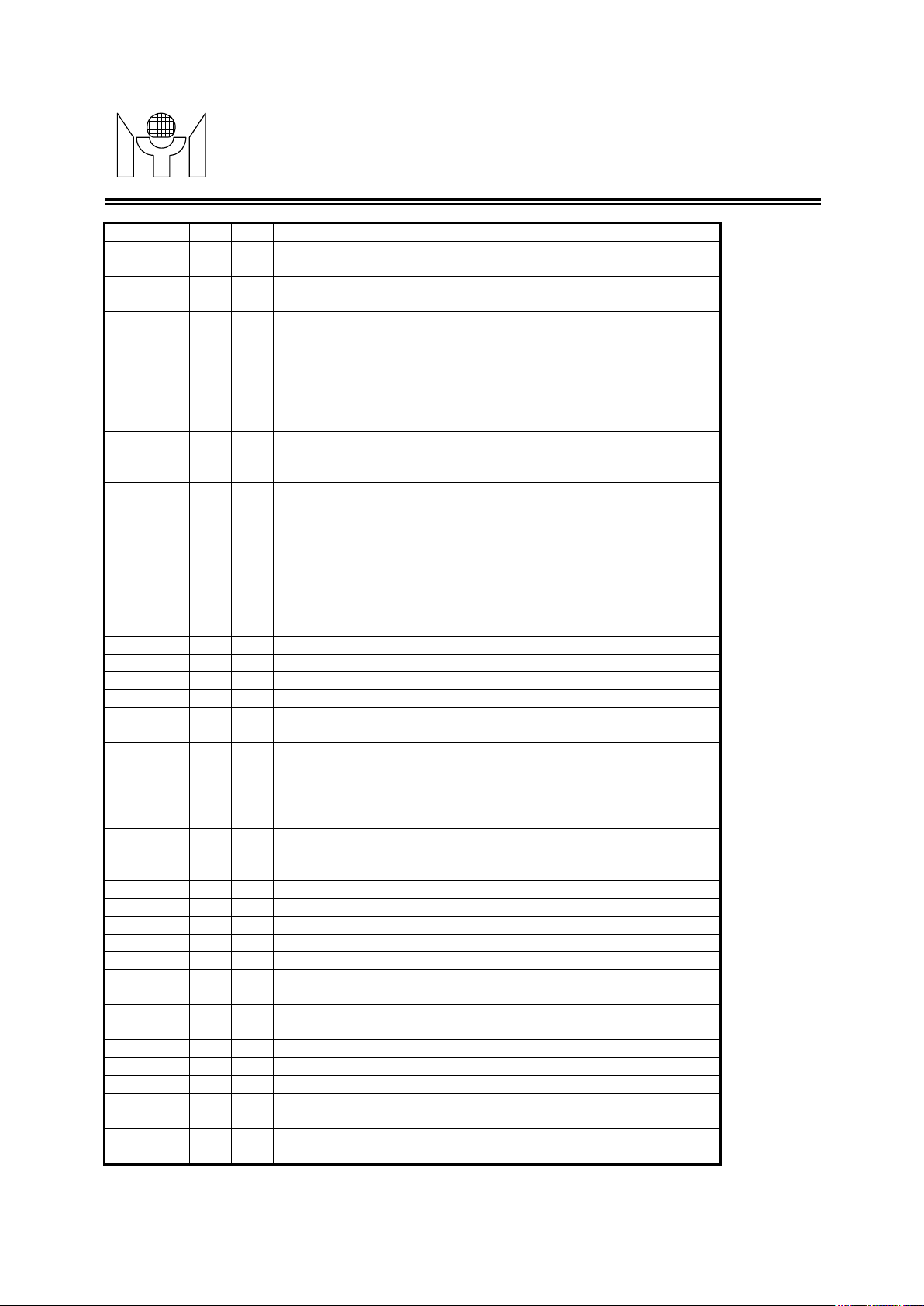

MYSON

Test mode select. Weakly pull down.

TECHNOLOGY

PIN DESCRIPTION

MTD981A

Name IO Pin #

TXD3 I 40 50 Transmit data bit 3.

TXD2 I 39 49 Transmit data bit 2.

TXD1 I 38 48 Transmit data bit 1.

TXD0 I 37 47 Transmit data bit 0.

TXEN I 34 44 Transmit enable.

TXCLK O 33 43 Transmit clock.

TXER I 32 42 Transmit error.

RXD3 O 23 33 Receive data bit 3.

RXD2 O 24 34 Receive data bit 2.

RXD1 O 25 35 Receive data bit 1.

RXD0 O 26 36 Receive data bit 0.

RXDV O 29 39 Receive data valid.

RXER O 31 41 Receive data error.

RXCLK O 30 40 Receive clock.

COL O 41 56 Collision detect.

CRS O 42 57 Carrier sense.

MDC I 22 32 MII management clock.

MDIO IO,U 21 31 MII management data input/output. Weakly pull up.

MDINT O 43 58 MII management interrupt.

TXOP O 77 97 Twisted-pair output positive node.

TXON O 78 98 Twisted-pair output negative node.

RXIP I 64 84 Twisted-pair input positive node.

RXIN I 63 83 Twisted-pair input negative node.

FOP O 69 89 Fiber output positive node.

FON O 70 90 Fiber output negative node.

FIP I 67 87 Fiber input positive node.

FIN I 66 86 Fiber input negative node.

SDP I 62 82 Signal detect positive node. Used only in fiber mode.

LEDSPD_ IO,U 44 59 100BT LED. 0 = 100baseTX; 1 = other connection.

LED10_ O 57 72 10BT LED. 0 = 10baseTX; 1 = other connection.

LEDTX_ O 47 62 Transmit LED. Toggles when there is transmit activities.

LEDRX_ O 46 61 Receive LED. Toggles when there is receive activities.

LEDFD_ O 58 73 Full-duplex LED. 0 = full duplex; 1 = half duplex.

LEDLNK_ O 48 63 Link LED. 0 = link on; 1 = link off.

(80)

Pin #

Description

(100)

When RST_ is low, this pin works as FIBER_DESEL to select the

fiber mode. Weakly pull up

LEDCOL_ IO,U 45 60 Collision led. 0 = collision; 1 = no collision. Weakly pull up.

When RST_ is low, this pin will load the SCRAM_SEL to

enable/disable the scrambler and descrambler set.

TEST I,D 7 12

CKIN I 5 10 Oscillator input.

If RMII is selected, only 50MHz oscillator can be used. In MII

mode, a 25MHz oscillator can be used.

RBIAS I 72 92 Bias control resister, to provide the internal voltage control.

PD I,D 9 14 Power down control.

1 = power down mode; 0 or floating = normal. Weakly pull down.

RPTR I,D 61 81 Repeater mode select.

4

MTD981A Revision 1.2 02/19/2001

MYSON

; 0 or floating = normal. Weakly pull down.

disabled. Weakly pull up.

select, bit 1. Weakly pull up.

select, bit 0. Weakly pull up.

mode select bit 0. Weakly pull down.

MTD981A

TECHNOLOGY

1 = repeater mode

ISODEF I,D 2 7 Isolate Default

1 =isolation; 0 or floating = normal. Weakly pull down.

ISO I,D 3 8 Isolate

1 =isolation; 0 or floating = normal. Weakly pull down.

RST_ I,U 8 13 Pin Reset select.

0=reset; 1or floating = normal. Weakly pull up

RMIISEL I,D 6 11 RMII mode select.

1 = RMII mode; 0 or floating = normal (MII mode).

Weakly pull down.

When RMII mode is selected, MTD981A will assume the 50MHz

oscillator is used as base clock.

ANEN I,U 56 71 Auto-Negotiation enable

1 = enable Auto-Negotiation; 0 = disable Auto-Negotiation.

Weakly pull up.

SEL2 I,U 53 68 Operation mode select, bit 2. Used only when autonegotiation is

SEL2 SEL1 SEL0 operation mode

X 0 0 mode select by MII registers

0 0 1 10BaseT, half duplex

0 1 X 100BaseT, half duplex

1 0 1 10BaseT, full duplex

1 1 X 100BaseT, full duplex

SEL1 I,U 54 69 Operation mode

SEL0 I,U 55 70 Operation mode

PHYAD0 I,U 18 23 PHY Address bit 0. Weakly pull up.

PHYAD1 I,U 17 22 PHY Address bit 1. Weakly pull up.

PHYAD2 I,U 16 21 PHY Address bit 2. Weakly pull up.

PHYAD3 I,U 15 20 PHY Address bit 3. Weakly pull up.

PHYAD4 I,U 14 19 PHY Address bit 4. Weakly pull up.

TP125 IO,D 20 25 Value latched in while reset to select transformer turns ratio.

=1 to select the transmit transformer with ratio 1.25:1

=0 to select the transmit transformer with ratio 1:1 (default)

Works as link_established after reset.

Weakly pull down.

MODE1 I,D 19 24 Test mode select bit 1. Weakly pull down.

MODE0 I,D 1 6 Test

TEST2 O 68 88 Used as the test mode output monitor pin

NC0 74 94 No Connection

NC1 75 95 No Connection

NC2 - 1

NC3 - 2

NC4 - 3

NC5 - 4

NC6 - 5

NC7 - 26

NC8 - 27

NC9 - 28

NC10 - 29

NC11 - 30

NC12 - 51

NC13 - 52

NC14 - 53

NC15

- 54

5

MTD981A Revision 1.2 02/19/2001

MYSON

TECHNOLOGY

NC16 - 55

NC17 - 76

NC18 - 77

NC19 - 78

NC20 - 79

NC21 - 80

CVDD IO 36 46 Power pin for core.

CGND IO 35 45 Power pin for core.

MTD981A

6

MTD981A Revision 1.2 02/19/2001

Loading...

Loading...