MYSON MTD800 Datasheet

ut notice.

No liability is assumed as a result of the use of this procuts. No rights under any patent accompany the sales of the product.

MYSON

GENERAL DESCRIPTION

Supports both full-duplex and half-duplex mode

duplex flow control method.

Contains separate transmit and receive FIFOs.

Supports Magic packet and Microsoft wake-up

frame filtering.

Supports ACPI and PCI power management.

Supports up to 128K bytes boot ROM or flash

memory without external latch.

Programmable EEPROM interface.

perform ACPI function, and the capability of sensing

PME# WakeUp

TXD[3:0]

MTD 800

TECHNOLOGY

Integrated Fast Ethernet Controller

FEATURES

• Compliant to PCI bus interface v2.2.

• IEEE802.3 and 802.3u compliant.

• High performance with PCI bus master structure.

• Programmable PCI burst length for low CPU utilization rate.

• Transmit packet queuing capability for higher performance.

•

operation.

• Supports both IEEE802.3x and XON/XOFF full

•

•

•

• Supports CardBus STSCHG pin and status

changed registers. The CIS can be stored in the

EEPROM.

•

(Preliminary)

MTD800 is a highly integrated fast ethernet

controller for PCI interface. The chip contains a PCI

interface block, two large FIFOs( each is 2KiloBytes )

for transmit and receive DMA, IEEE802.3 and 802.3u

compliant MAC interface for MII connection. Besides

that, the chip has the built-in Wake-Up controller to

IEEE 802.3x frame to support XON/XOFF flow control protocol. The chip also has EEPROM and BootROM interface for no glue logic board

implementation. For CardBus application, MTD800

supports four status-changed registers, an interface

for accessing CIS which is stored in EEPROM and

STSCHG pin to reflect the general wake-up event.

• Autoload EEPROM contents after power-on.

•

• 128 pin PQFP package.

• Single 3.3V Power Supply.

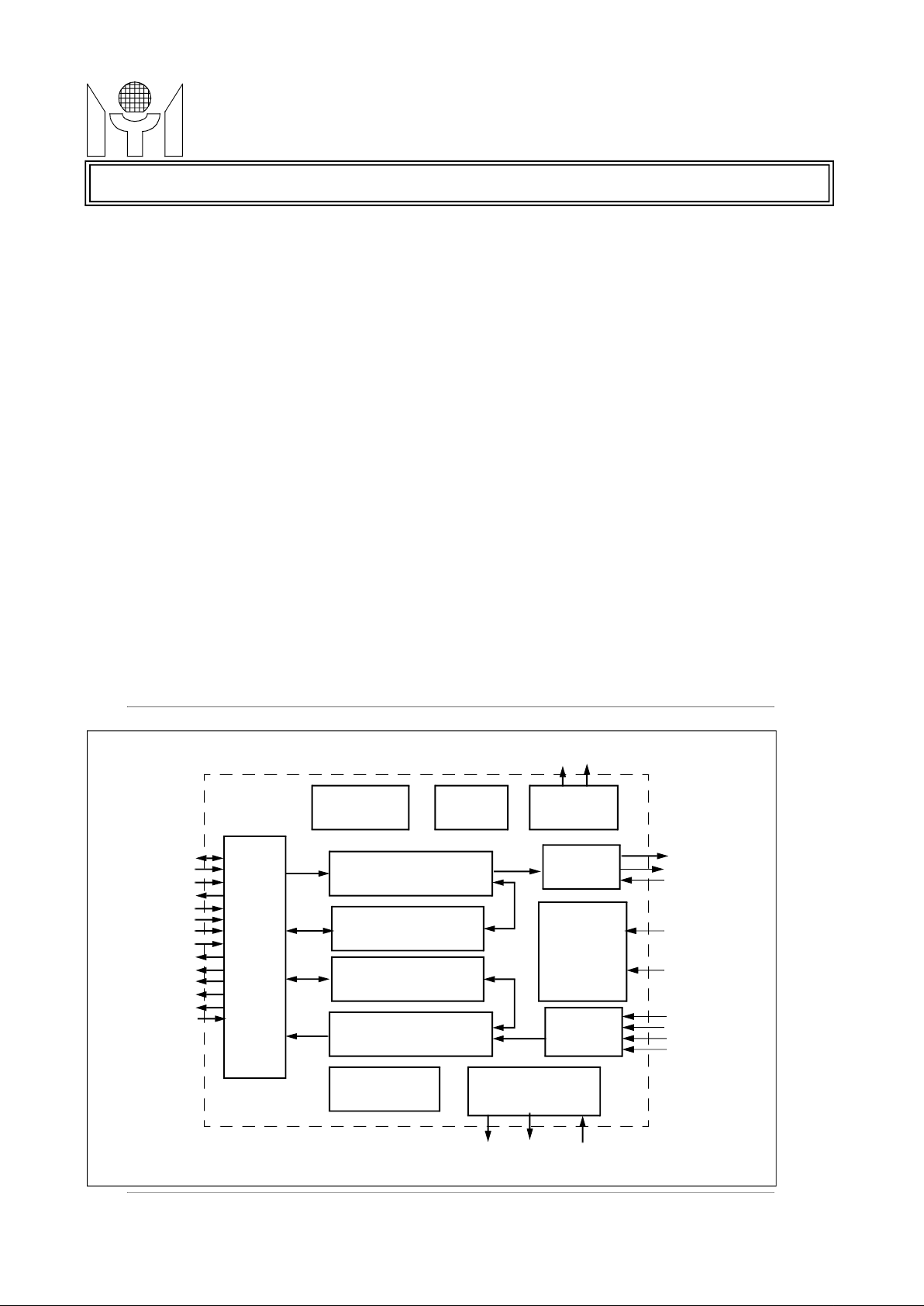

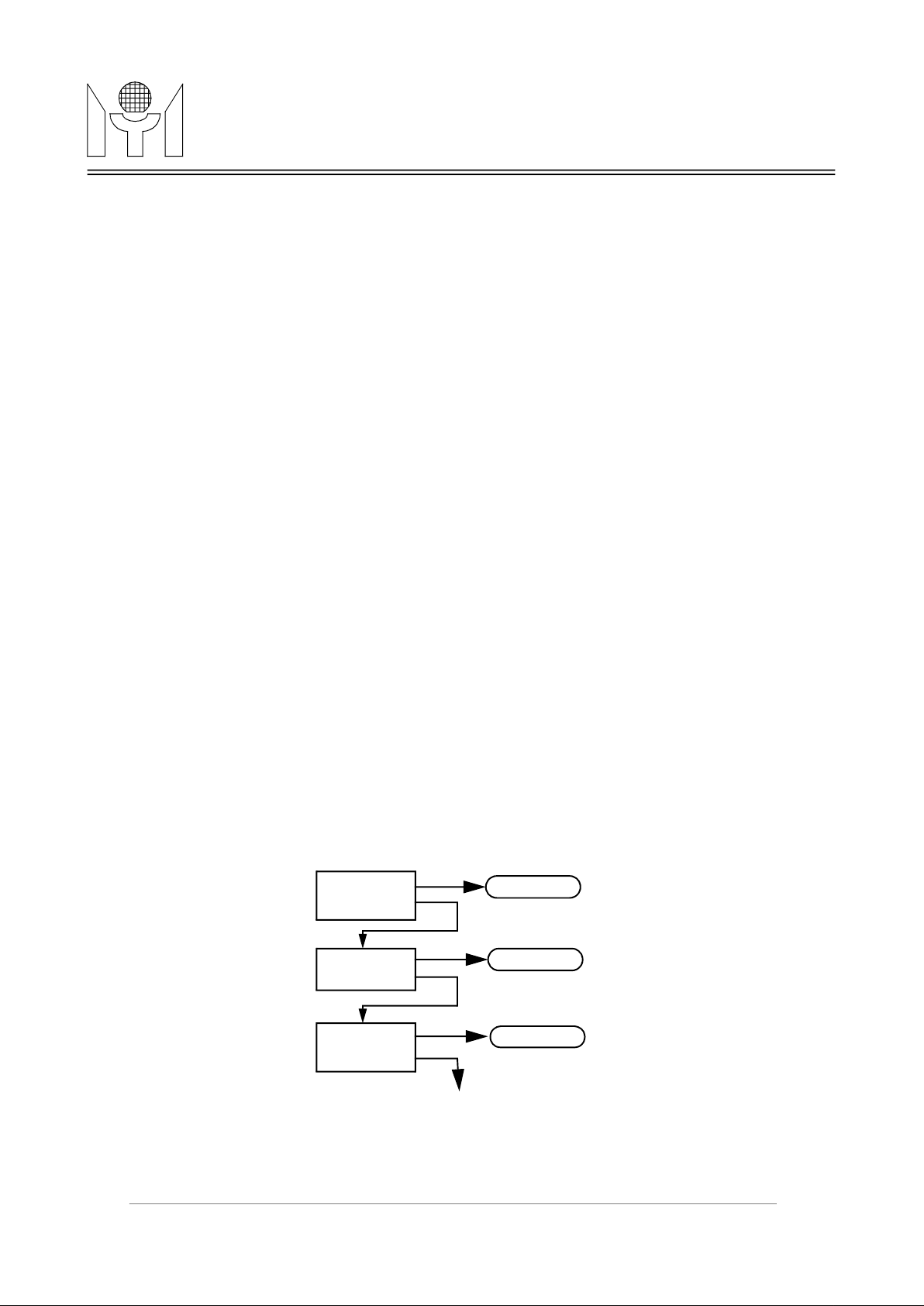

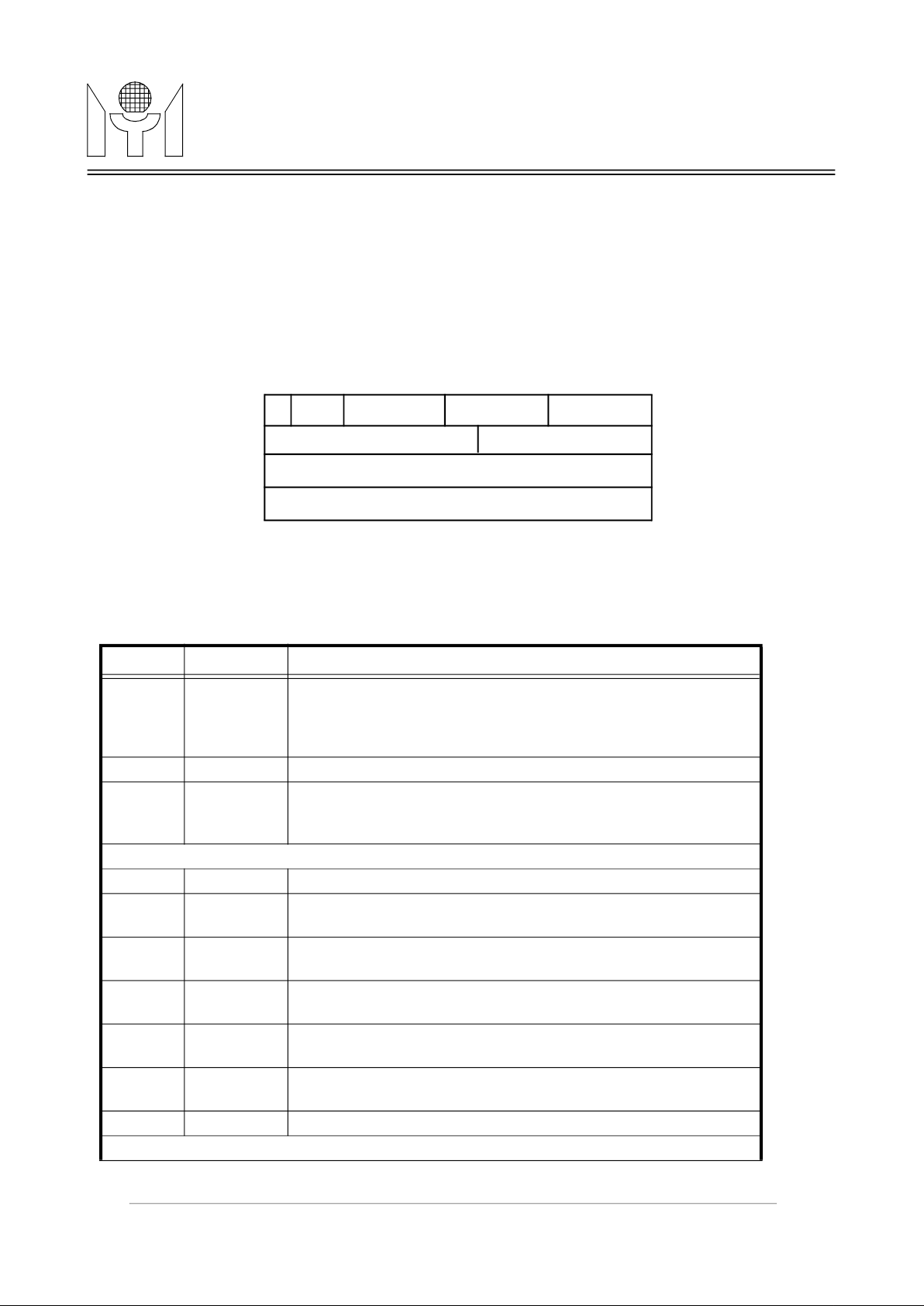

BL OCK DIAGRAM

EEPROM

Control Logic

AD[31:0]

PCICLK

RST#

INTA#

CBE3[3:0]

IDSEL

FRAME#

IRDY#

TRDY#

DEVSEL#

STOP#

PAR

REQ#

GNT#

PCI

Interface

Tx FIFO

Tx DMA Control

Rx DMA Control

Rx FIFO

Boot ROM

Interface

LED

LED Control

Tx MII

Interface

MAC

Protocol

Processor

Rx MII

Interface

TXEN

TXCK

CRS

COL

RXD[3:0]

RXDV

RXCK

RXER

CFG & CSR

Registers

This datasheet contains new product information. Myson Technology reserves the rights to modify the product specification witho

1/42 MTD800 Revision 0.0 07/20/1999

Wake-up

Controller

IOSLATE#

MYSON

PCICLK provides timing reference for the MTD800 related PCI transac-

drain pins are floated. This signal is asynchronous to PCICLK and have to

be asserted for at least 10 active PCI clock cycles.

address phase followed by one or more data phases. During the first cycle

while it is considered as a data bus during subsequent cycles.

BRWR#

WUP/SGH

MTD 800

TECHNOLOGY

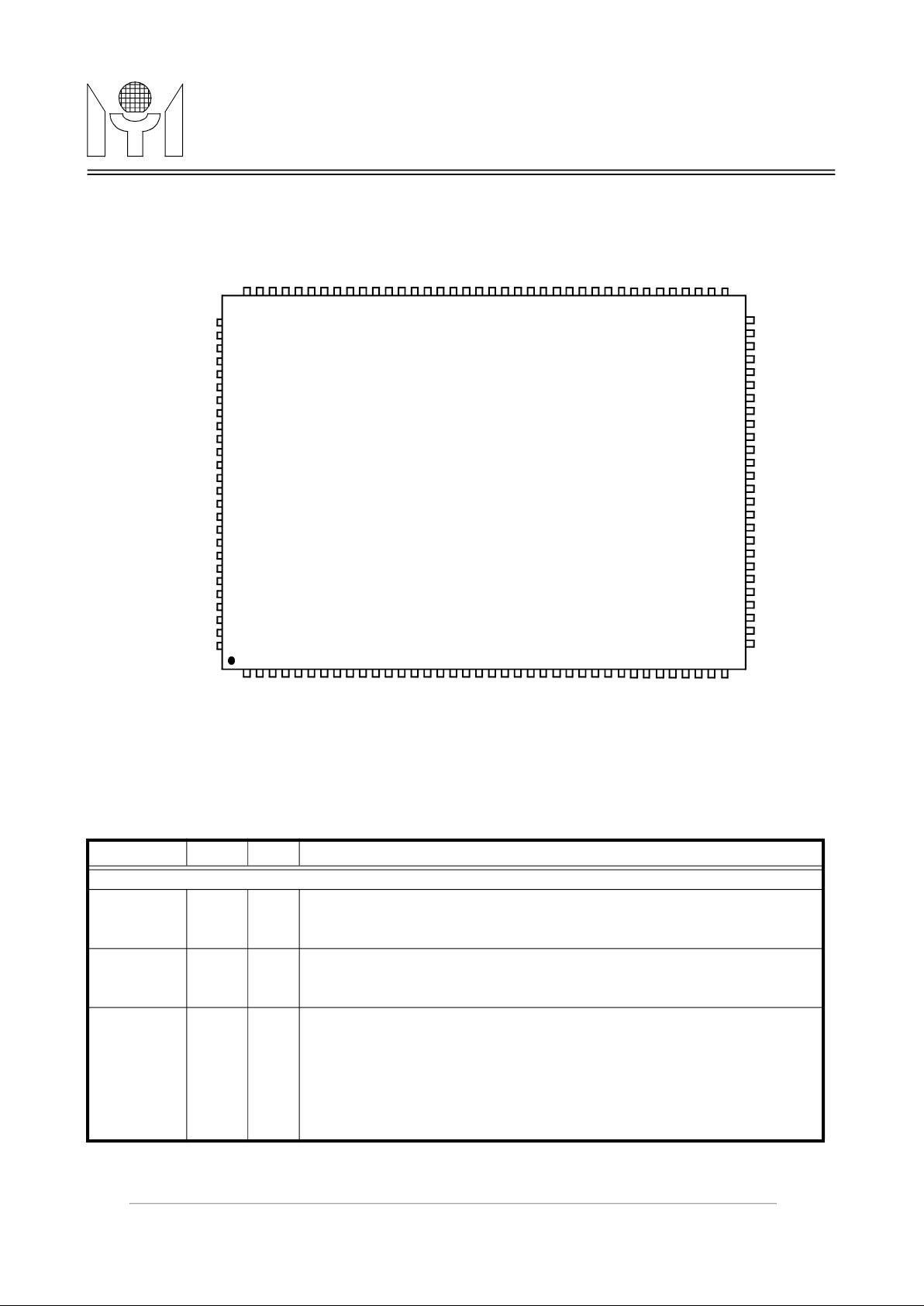

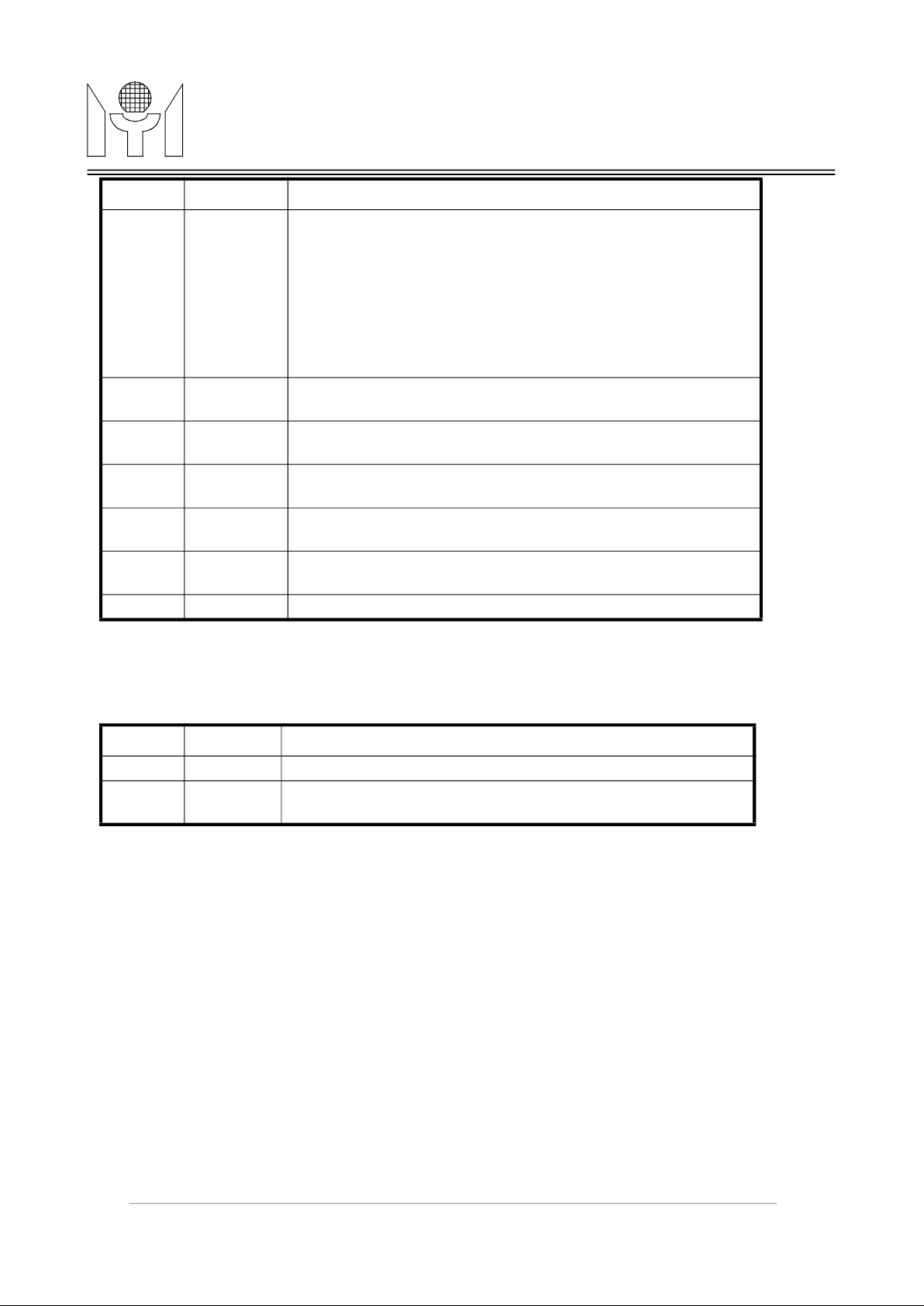

1.0 PIN CONNECTION

128 pin QFP

VDD_M

MDIO

MDC

102

101

VSS_M

COL

CRS

RXER

RXD3

RXD2

RXD1

RXD0

RXCK

VDD

VSS

TXEN

TXD3

TXD2

TXD1

TXD0

TXCK

RXDV

INTA#

RST#

VDD

PCICLK

VSS

GNT#

REQ#

PME#

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

100

010203040506070809

(Preliminary)

PAUSE

ACT

EpSel

ByPass#

VSS

VDD

VDD

RSTOUT#

ISOLATE#

VSS

BRA16

BRA15

BRA14

BRA13

BRA12

BRA11

BRA10

BRA9

BRA8

BRA7

VSS

VDD

BRA6

BRA5

BRA4

BRA3

BRA2

BRA1

BRA0

BRD7

BRD6

VSS_M

VDD_M

BRD5

9998979695949392919089888786858483828180797877767574737271706968676665

MTD800

1011121314151617181920212223242526272829303132333435363738

BRD4

64

TEST#

63

BRD3

62

BRD2

61

BRD1

60

BRD0

59

BRCS#

58

BRRD#

57

ECS

56

VSS

55

VDD

54

53

AD0

52

AD1

51

AD2

50

AD3

49

AD4

48

AD5

47

AD6

46

AD7

45

CBE0#

44

AD8

43

AD9

42

AD10

41

VDD

40

VSS

39

VSS

AD31

AD30

AD29

VDD

AD28

AD27

AD26

AD25

AD24

AD23

AD22

IDSEL

CEB3#

VSS

VSS

VDD

VDD

AD21

AD20

AD19

AD18

AD17

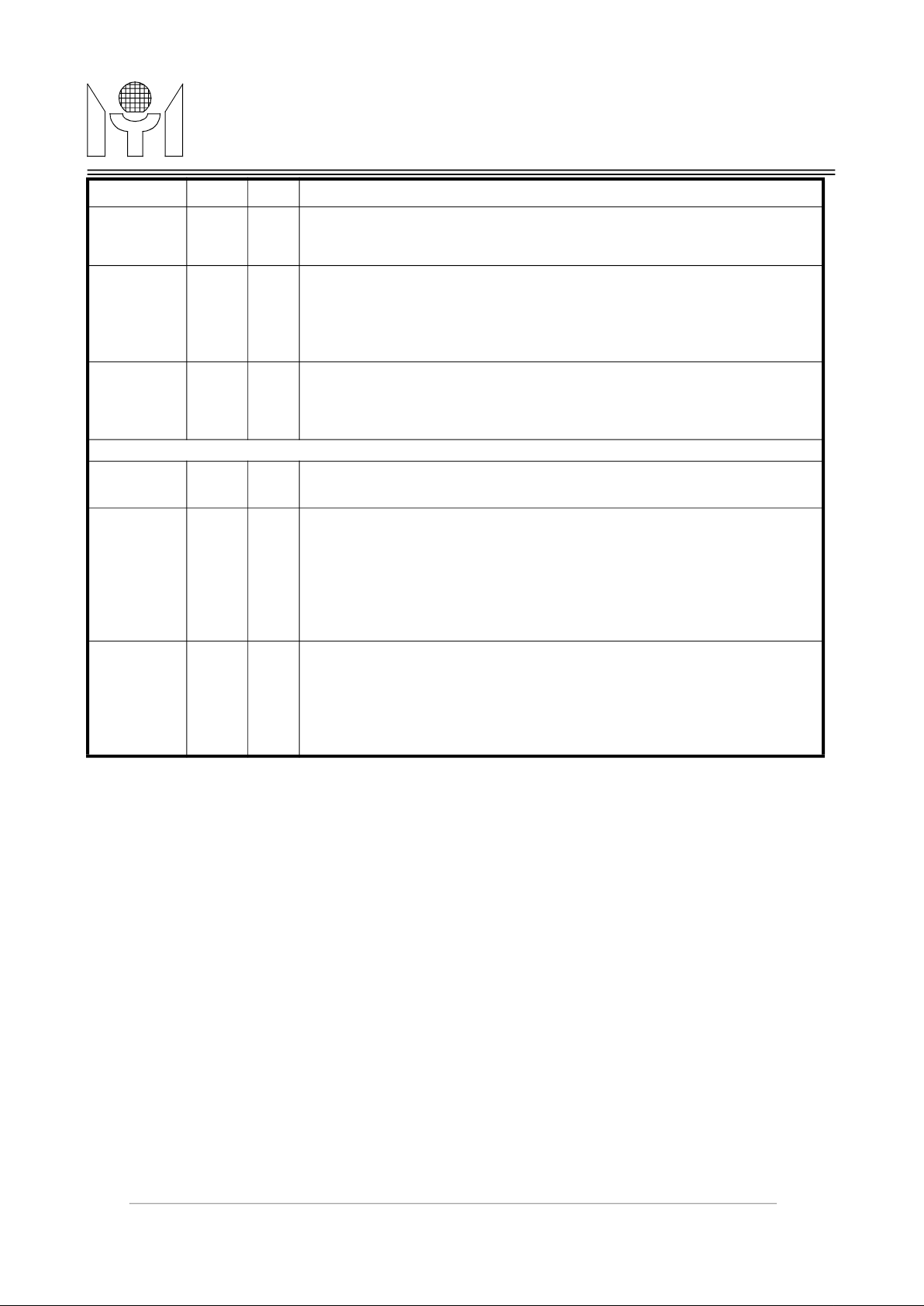

2.0 PIN DESCRIPTIONS

Name Pin # I/O Description s

PCI Bus Interface

PCICLK 124 I

RST# 122 I

1 - 6,

9, 10

13 -15

AD[31:0]

20 - 24,

34 - 38,

41 - 43,

45 -52

tions. All PCI signals except RST#,INTA# and PME# are sampled on the

rising edge of this clock.

When RST# is asserted, all output signals are put into tristate and all open

32-bit multiplexed address and data bus. A bus transaction consists of an

I/O

in which the FRAME# is asserted, the AD[31:0] represents the address bus

AD16

IRDY#

CBE2#

TRDY#

FRAME#

PAR

AD15

CBE1#

STOP#

PERR#

DEVSEL#

AD11

AD14

AD13

AD12

2/42 MTD800 Revision 0.0 07/20/1999

MYSON

4-bit multiplexed bus command and byte enables. During the address

cycles, CBE represents the byte enable signals for PCI data bus.

this signal is asserted to indicate that the master is ready to accept data

from the selected target. Wait states are inserted until both IRDY# and

TRDY# are asserted.

used in conjunction with IRDY#. A data phase is completed on any clock

when both IRDY# and TRDY# are asserted.

Asserted by MTD800 to indicate that the device has decoded the address

DEVSEL# indicates whether any device on the bus or bridge has termi-

INTA# is an asynchronous signal which is used to request an interrupt.

Asserted by the PCI bus arbiter to indicate that MTD800 has granted the

Asserted by MTD800 to signal bus arbiter that it needs the dedicated

by MTD800 to request a change in the device or system power state.

Collision signal. COL is asserted high when PHY detects a collision on the

Transmit Data signals. TXD are driven by MTD800 and transits synchro-

nously with respect to the TXCK.

Transmit Data Enable. TXEN is driven by MTD800 and transits synchro-

nously with respect to the TXCK.

MTD 800

TECHNOLOGY

Name Pin # I/O Description s

CBE#[3:0]

IDSEL 12 I Used as a chip select during access to the configuratio n registers

FRAME# 26 I/O

IRDY# 27 I/O

TRDY# 28 I/O

DEVSEL# 29 I/O

STOP# 30 I/O

INTA# 121 O/D

PAR 32 I/O

1 1, 25,

33, 44

I/O

phase transaction, CBE is considered as bus command. On the data phase

Driven by MTD800 to Indicate the start and duration of a transaction. The

FRAME# is deasserted when the master is ready to complete the final data

phase in the transaction.

During a write transaction, the current bus master asserts IRDY# to indicate

that valid data is being driven onto the PCI bus. During a read transaction,

During a read transaction, the target asserts TRDY# to indicate that valid

data is being driven onto the PCI bus. During a write transaction, this signal

is asserted to indicate that the target is ready to accept data. TRDY# is

as the target of current access. As an input, DEVSEL# indicates whether

any device on the bus has been selected.

Asserted by MTD800 to disconnect any further transaction. As an input,

nated the transaction.

Ensures even parity across AD[31:0] and CBE[3:0]. PAR is stable and valid

for one clock after the address phase. During the data phase, PAR is stable

and valid for one clock after either IRDY#(write transaction) or TRDY#(read

transaction) is asserted.

(Preliminary)

GNT# 126 I

REQ# 127 O/Z

PERR# 31 I/O PERR# is asserted when a data parity error is detected.

PME# 128 O/D

COL 104 I

RXDV 120 I

TXCK 119 I

TXD[3:0]

TXEN 114 O

RXCK 11 1 I

115 118

bus control authority.

access to the PCI bus.

An interrupt signal for the occurrence power management event. Asserted

Netwo r k Interface

medium. This signal is asynchronous to TXCK or RXCK.

Receive data valid. RXDV is asserted high by PHY to indicate the incoming

receive data RXD[3:0] is valid. This signal is synchronous to RXCK.

Transmit Clock. TXCK is a continuous clock that provides the timing refer-

ence for the transfer of the TXD[3:0] and TXEN signals.

O

Receive Clock. RXCK is a continuous clock that provides the timing reference for the transfer of the RXD[3:0], RXDV and RXER.

3/42 MTD800 Revision 0.0 07/20/1999

MYSON

Carrier Sense signal. CRS is asserted by PHY when either the transmit or

receive medium is non-idle. This signal is asynchronous to TXCK or RXCK.

Management Data Clock. MDC is sourced by the MTD800 to control the

to PHY. A 1.5K pull up resistor is required to connect to this pin.

MII interface. A 510 ohm pull up resistor is required to connect to this pin.

BootROM read signal. Read out the content of BootROM onto the memory

BootROM write signal. When flash memory is used, BRWR# is asserted

A chip select signal for the external EPRO M (BootROM) or flash memory.

A multiplexed signal for BootROM data bit 0 and Serial ROM Data input.

A multiplexed signal for BootROM data bit 1 and Serial ROM Data output.

BootROM data bus from bit 3 to bit 7.

BootROM address bus from bit 0 to bit 16.

Misc. Interface

Wakeup Pin/CardBus STSCHG Pin.

In PCI application, this pin is the Wakeup pin to signal the host system of an

wakeup event happened.

EEPROM Bypass Mode. When asserted low, the EEPROM function will be dis-

MTD 800

TECHNOLOGY

Name Pin # I/O Description s

RXD[3:0]

RXER 106 I

CRS 105 I

MDC 100 O

MDIO 101 I/O

LED_ACT# 98 O

LED_PAUS

E#

ECS 56 O

107 110

99 O

Receive Data signals. RXD are driven by PHY and transit synchronously

I

with respect to the RXCK.

Receive Error signal. RXER is asserted high to indicate a coding error is

detected by PHY. This signal is synchronous to RXCK.

transfer of the MDIO data. A 1.5K pull up resistor is required to connect to

this pin.

Management Data Input/Output. A bi-directional data interface connected

LED Status Output

Activity LED. This signal will drive the led light on when detecting activity on

Pause LED. This signal will drive the led light on when detecting transmission is paused under the condition of receiving a XON frame.

Bo o tROM/ EEPROM Int er face

A chip select signal for the external EEPROM. EEPROM is used to provide

the configuration data and Ethernet Address. A 100K pull-up resister is connected to this pin.

(Preliminary)

BRRD# 57 O

BRWR# 58 O

BRCS# 59 O

BRD0/EEDI 60 I/O

BRD1/EEDO 61 I/O

BRD2/EECK 62 I/O A multiplexed signal for BootROM data bit 2 and Serial ROM Clock signal.

70 - 69,

BRD[7:3]

BRA[16:0]

WAKEUP/

STSCHG

66 - 65, 63I/O

89- 80,

77 - 71

53 O/Z

support data bus.

low to enable the write action.

The BootROM contains codes that can be usually executed for a system

boot function.

O

In Card bus application, this pin is used as the STSCHG pin to signal the system of

any status changed. This pin is enabled as STSCHG pin if the PME_Enable bit of

the power management control register is set and the FMR.GWAKE, FMR.WAKE

are both set.

ByPass# 96 I

able. This is useful for testing purpose. For normal operation, it should be connected to VDD.

4/42 MTD800 Revision 0.0 07/20/1999

MYSON

ISOLATION pin. This pin should connect to the PCI stable power signal

(VDD). When PCI Bus is in B3 state, the power signal becomes deas-

serted, however the ISOLATION pin is active. Under this condition, the

PME# are isolated from the PCI Bus.

Hardware reset is detected. The pulse width is 245us. The PHY can use

this output pin as its reset signal, then PHY can avoid to keep being reset

MTD 800

TECHNOLOGY

Name Pin # I/O Description s

EEPROM selection pin. EpSel is to determine which type of EEPROM is

EpSel 97 I

ISOLATE# 91 I

RSTOUT# 92 O

VDD_M,

VSS_M

VDD

VSS

67, 102

68, 103

7, 16,

17, 40,

54,64,

78, 93,

94,

112,

123

8, 18,

19, 39,

55, 79,

90, 95,

113,

125

chosen. 93C46 is used when EpSel connects to VSS, while 93C66 is

selected if EpSel connects to VDD.

PCIRST# and PCICLK are ignored and all the PCI output signals except

Reset Output pin. A active-low pulse is generated when Power-On or

during D3 state.

Power Supply & Ground

P/G Digital 3.3V power and ground for internal SRAM.

P Digital 3.3V power supply.

G Digital Ground.

(Preliminary)

5/42 MTD800 Revision 0.0 07/20/1999

MYSON

3.0 FUNCTIONAL DESCRIPTION

putation. The MTD800 is directly compatible with revision 2.2 of the PCI Local Bus Specification and supports

with the host memory.

The DMA Transmit Function is responsible for fetching data from the host’s memory into the on-chip transmit

FIFO, and then signalling MAC transmit interface to relay the transmitted data onto the network if the fullness

buffers. The transmit descriptor format is shown as figure 3.2. It consists of four long words. The first two

words contain the transmit frame status, frame length and the descriptor ownership information. The last two

descriptor words are given in table 3.1 and table 3.2 respectively. Note that the transmit buffer address are not

necessary to be in alignment of longword while the descriptors address should be longword aligned. The own-

ership of buffer is indicated in the “own” bit of the first descriptor. When driver has completed the preparation

demands MTD800 to fetch the buffer and the associated descriptor. After the packet has been transmitted

can be reused. Meanwhile, the driver is able to acquire the transmit status by reading the “TSW” in the first

descriptor. The MTD800 also has an advanced feature to enhance the transmit performance by “closing” the

Buffer 0

Buffer 1

Buffer 2

MTD 800

TECHNOLOGY

3.1 PCI Bu s Operat i on

The peripheral component interconnect (PCI) is a high-speed backplane in modern PC. The MTD800 uses

the PCI bus to communicate with the host CPU and main memory to achieve high performance network com-

a subset of the PCI bus transactions. It contains I/O read/write, Memory read/write and Configuration read/

write operations. Besides that, all kinds of termination cycle are also supported. The MTD800 is acting as a

PCI bus target when handshaking with the host, while operating as a PCI bus initiator when communicating

3.2 DMA Transm i t Func t i o n

of FIFO reaches the predefined threshold. The structure for the data to be transmitted is described in a format

of chained link list(see figure 3.1). Descriptors that reside in the host memory act as pointers to these transmit

(Preliminary)

words are the address pointers for the current data buffer and the next descriptor. The bit field definition of the

of being transmitted packet, it sets the “own” bit to represent the buffer that belongs to the MTD800, and

onto the network, the MTD800 clears the “own” bit and issues an interrupt to notify the driver that the buffer

first descriptor early once the packet has been transferred into the FIFO completely.

Descriptor 0

Descriptor 1

Descriptor 2

point to

next descriptor

Figure 3.1 Descriptor chained structure

6/42 MTD800 Revision 0.0 07/20/1999

MYSON

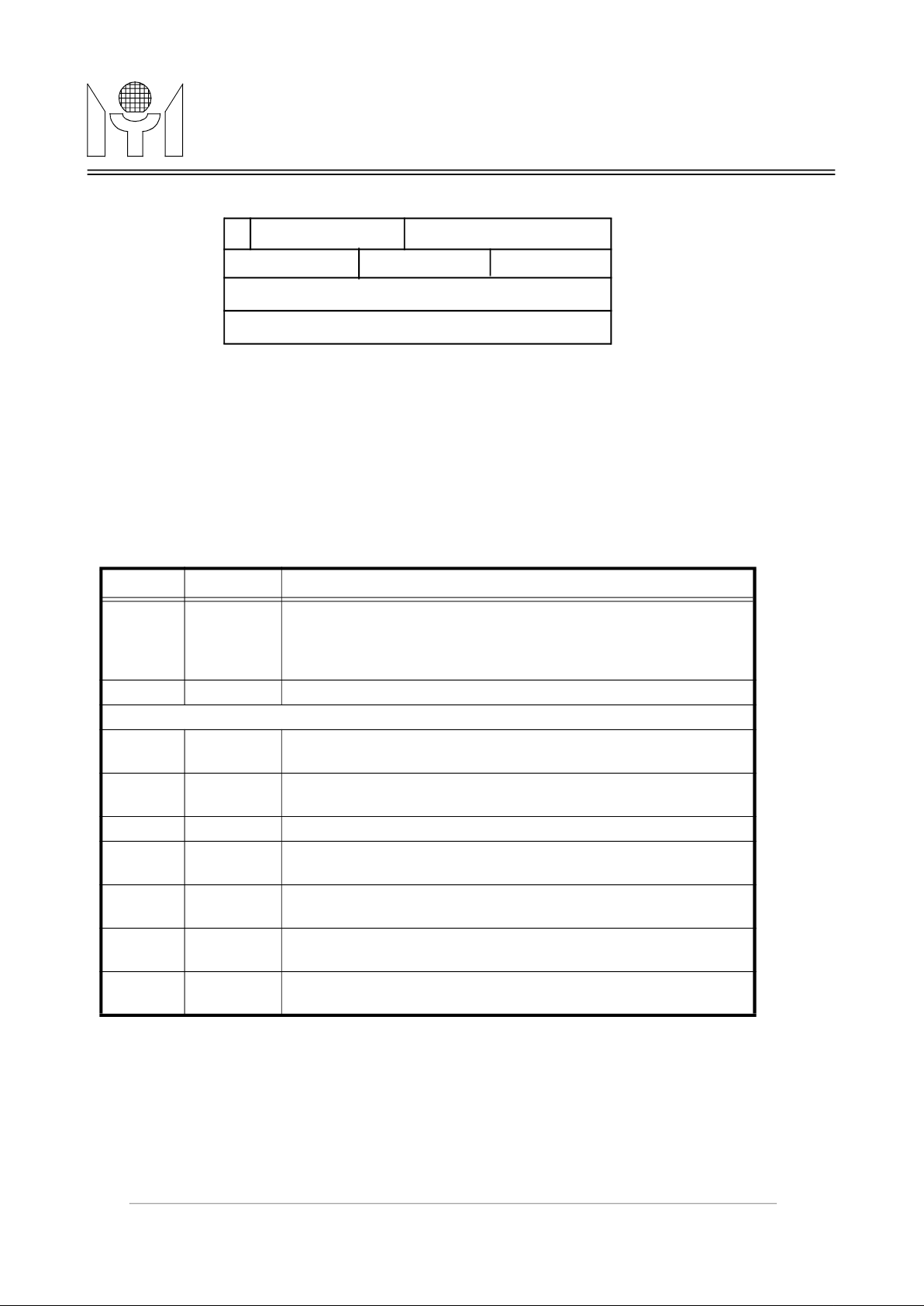

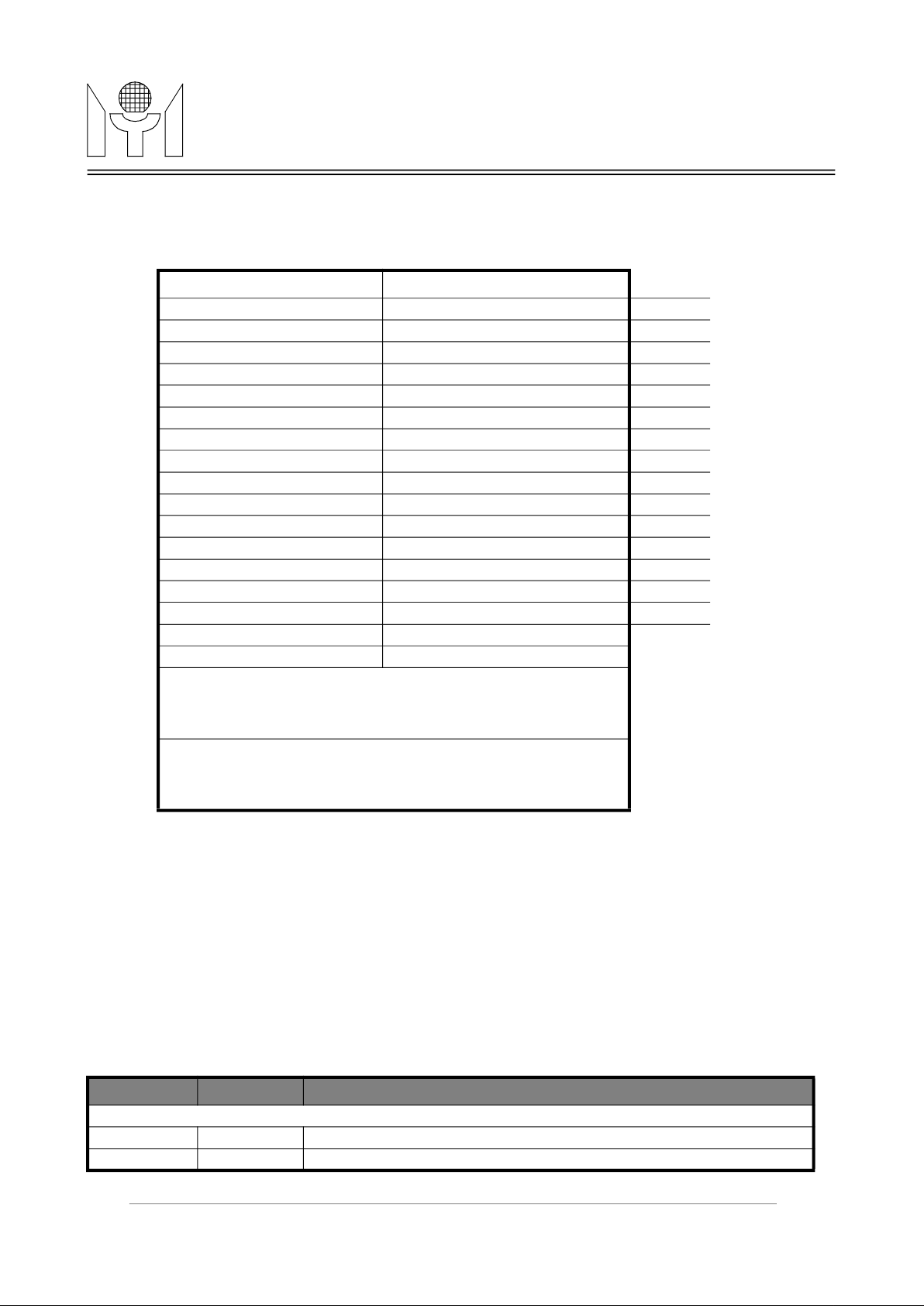

Owner: This bit is controlled by driver, When set, identifies that the

descriptor is owned by the MTD800. When reset, indicates that the

descriptor is owned by the host; Driver must reset this bit when initializa-

Transmit Status Word (TSW)

Abort: This bit is set when the current transmitting packet is aborted due

Collision Retry Count: This 8-bit counter indicates that the number of

Tx Data Buffer Start Address

MTD 800

TECHNOLOGY

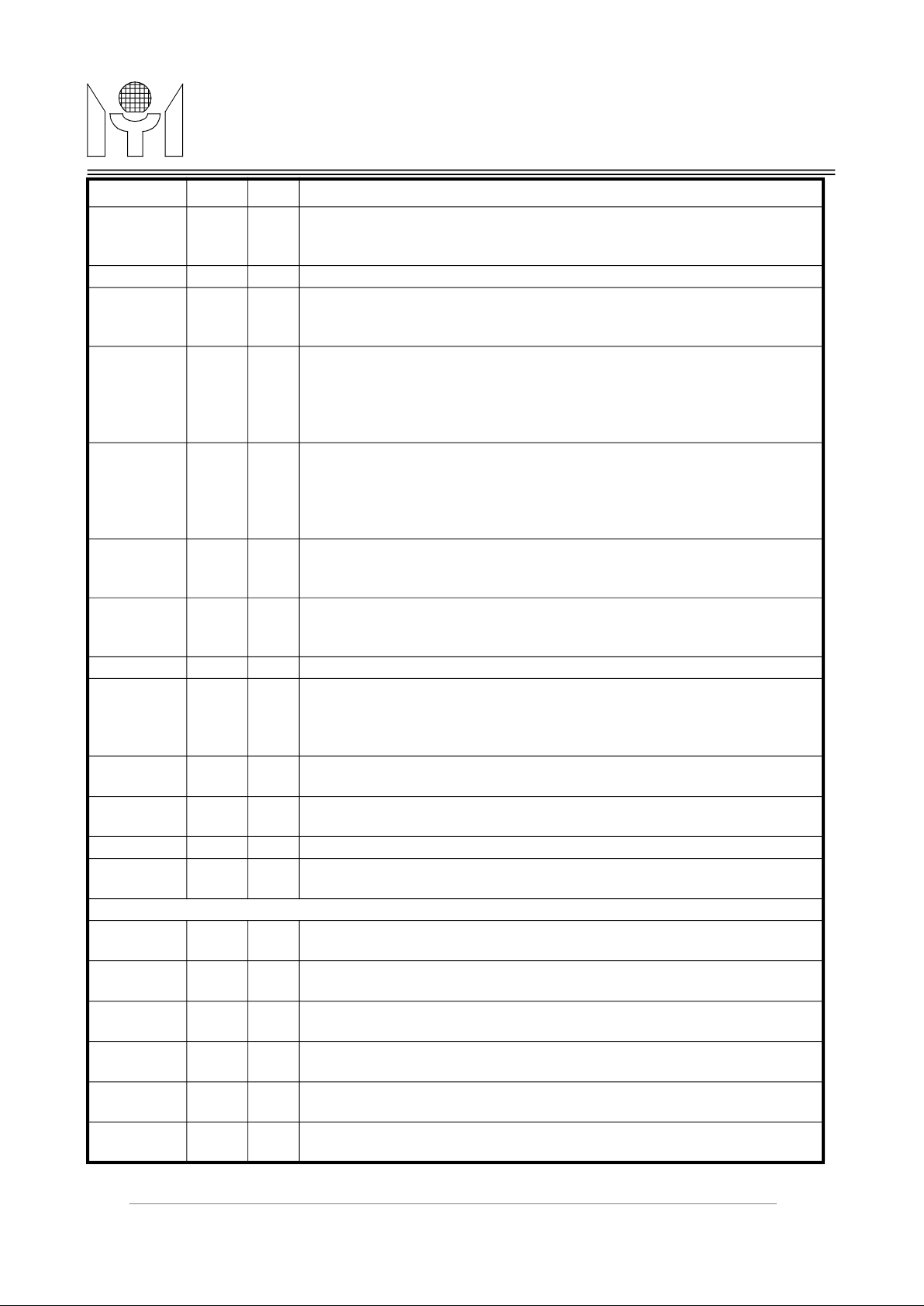

O

Figure 3.2 The Transmit Descriptor Format

Table 3.1 Transmit Descriptor 0 ( TDES0)

Bit Symb ol Descr ipt ion

31 OWN

Reserved

TCW

TSW

PKTS[10:0]

Next Descriptor Address

(Preliminary)

TBS[10:0]

tion.

30 -13 - Reserved

13 ABORT

to the excessive collision or late collision,

12 CSL Carrier Sense Lost: When set, the carrier is lost during the transmission

of packet.

11 LC Late Collision: This bit is set when late collision occurs.

10 EC Excessive Collisions: This bit is set when the successive collision count

exceeds 16 or 256 and the transmitting packet will be aborted.

9 DFR Deferred: When set, indicates that MTD800 has to defer while ready to

transmit a frame because of carrier sense asserted.

8 HF Heart-beat Failure: This bit is only effective in 10Base-T mode. When

set, indicates a heartbeat collision check failure.

7- 0 NCR[7:0]

collisions have occurred.

aa

7/42 MTD800 Revision 0.0 07/20/1999

MYSON

3.3 DMA Receive Funct i o n

transmit buffer. Descriptors that reside in the host memory act as pointers to these receive buffers. The

descriptor format is shown as figure 3.3. It consists of four long words. The first two words contain the receive

frame status, frame length and the descriptor ownership information. The last two words are the address

pointers for the current data buffer and the next descriptor. The bit field definition of the descriptor words are

given in table 3.3 and table 3.4 respectively. Note that the receive buffers and descriptors address both should

Transmit Configure Word (TCW)

Early Interrupt Control: This bit supports for interrupt Pacing. When set,

indicates that MTD800 will issue interrupt after the packet has been

Last Descriptor: When set, it means the pointed buffer contains the last

First Descriptor: When set, it means the buffer contains the first segment

0 0 Intermediate buffer.

append to the transmitted packet.

PAD control : When set, the MTD800 will automatically pad zero’s to

Retry Late Collision : When set, the late collision will be considered as a

normal collision and the MTD800 just increases a collision count instead

Packet Size : This field contains the length of the transmitted packet. The

If the transmitted packet only use one single buffer, the TBS should be

equal to PKTS. The size is also indicated in bytes.

MTD 800

TECHNOLOGY

(Preliminary)

Table 3.2 Transmit Descriptor 1 ( TDES1 )

Bit Symb ol Descr ipt ion

31 IC Interrupt Control: This bit supports for interrupt Pacing. When set, indi-

cates that MTD800 will issue interrupt after the packet has been transmit-

ted.

30 EIC

transferred into the internal FIFO.

29 LD

segment of a frame.

28 FD

of a frame. In descriptor ring structure, each buffer is classified as follows

: FD LD Description

1 1 Single buffer descriptor

1 0 First buffer descriptor, further buffer chained

0 1 Chained buffer packet end

27 CRC CRC append : When set, the MTD800 will generate a CRC field to

26 PAD

the end of packet whose length is less than 64 bytes.

25 RTLC

of aborting the packet.

24 - 22 - Reserved.

21 - 11 PKTS[10:0]

value should be valid for the first descrip tor. The size is indicated in

bytes.

10 - 0 TBS Transmit Buffer Size : This field contains the size information of buffer.

The DMA Receive Function is responsible for collecting the network nibble-stream into the on-chip receive

FIFO, and then transferring the data onto the host’s memory if the fullness of FIFO reaches the predefined

PCI burst length. The data structure for the receive buffer is a forward-link buffer chain which is similar to the

be longword aligned. At the beginning, the driver allocates a set of free buffers and makes the ownership of

these buffers belong to the chip. The MTD800 starts to fetches the first descriptor into its internal registers.

8/42 MTD800 Revision 0.0 07/20/1999

MYSON

Once the packet has arrived in, the received data can be immediately transferred onto the dedicated location

of the host memory by means of the predefined address which contains in the third word of the descriptor.

After the receive buffer has been filled up with the received packet, the MTD800 clears the “own” bit in the

interrupt” operation, which demands the driver to move the data earlier than the completion of receiving the

Owner : This bit is controlled by driver, When set, identifies that the

descriptor is owned by the MTD800. When reset, indicates that the

descriptor is owned by the host; Driver must reset this bit when initializa-

Frame Length : Indicates that the frame length of received packet. This

field is valid only when the descriptor contains the last segment of a

Multicast Address Received : The MTD800 receives a multicast address

Broadcast Address Received : The MTD800 receives a broadcast address

segment of a received frame.

segment of a received frame.

Rx Data Buffer Start Address

MTD 800

TECHNOLOGY

descriptor and issues an interrupt to notify the driver that the data in the buffer are ready to be taken away.

The MTD800 also has an advanced feature to boost the receiving process. That is so-called “receive early

whole packet.

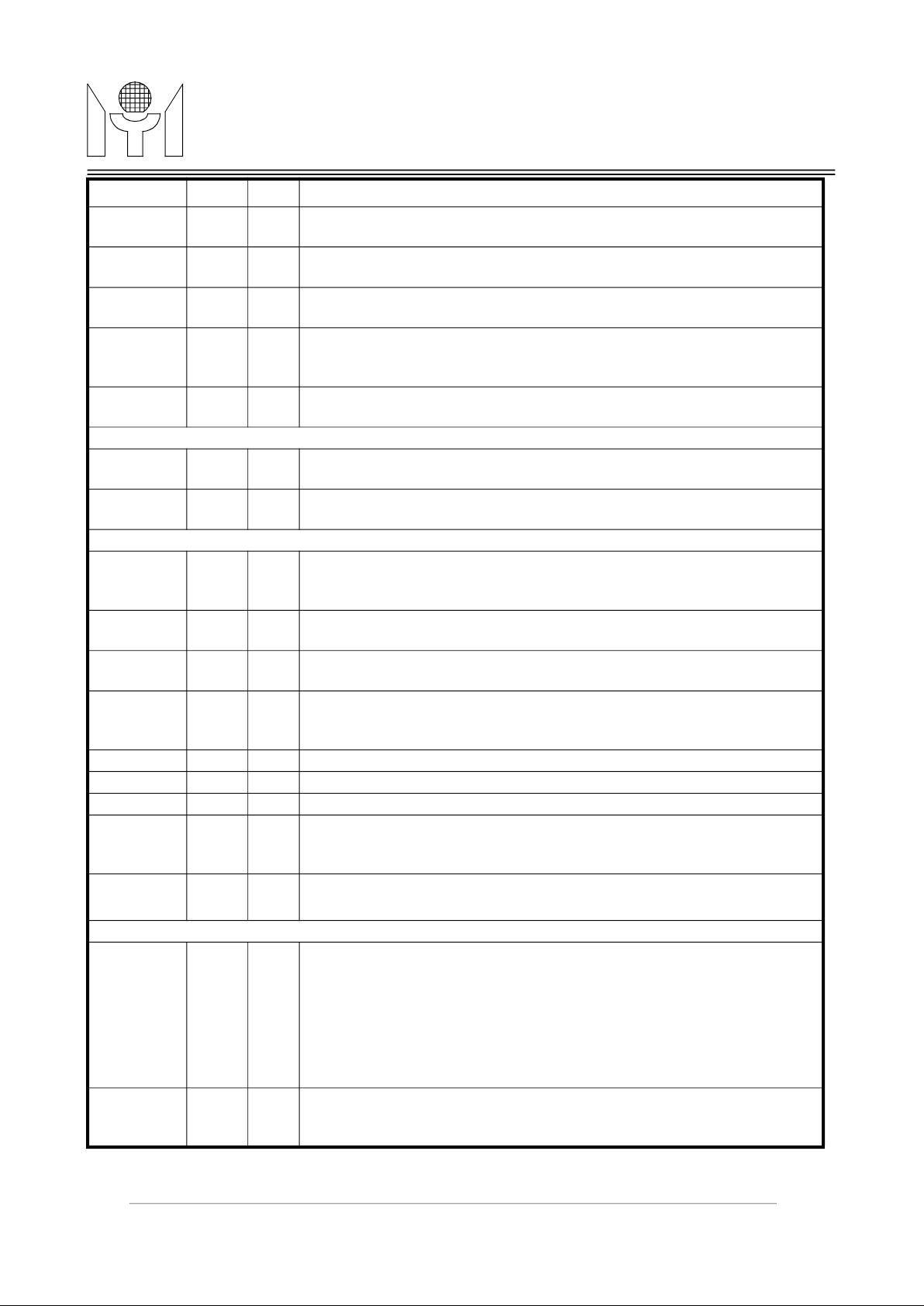

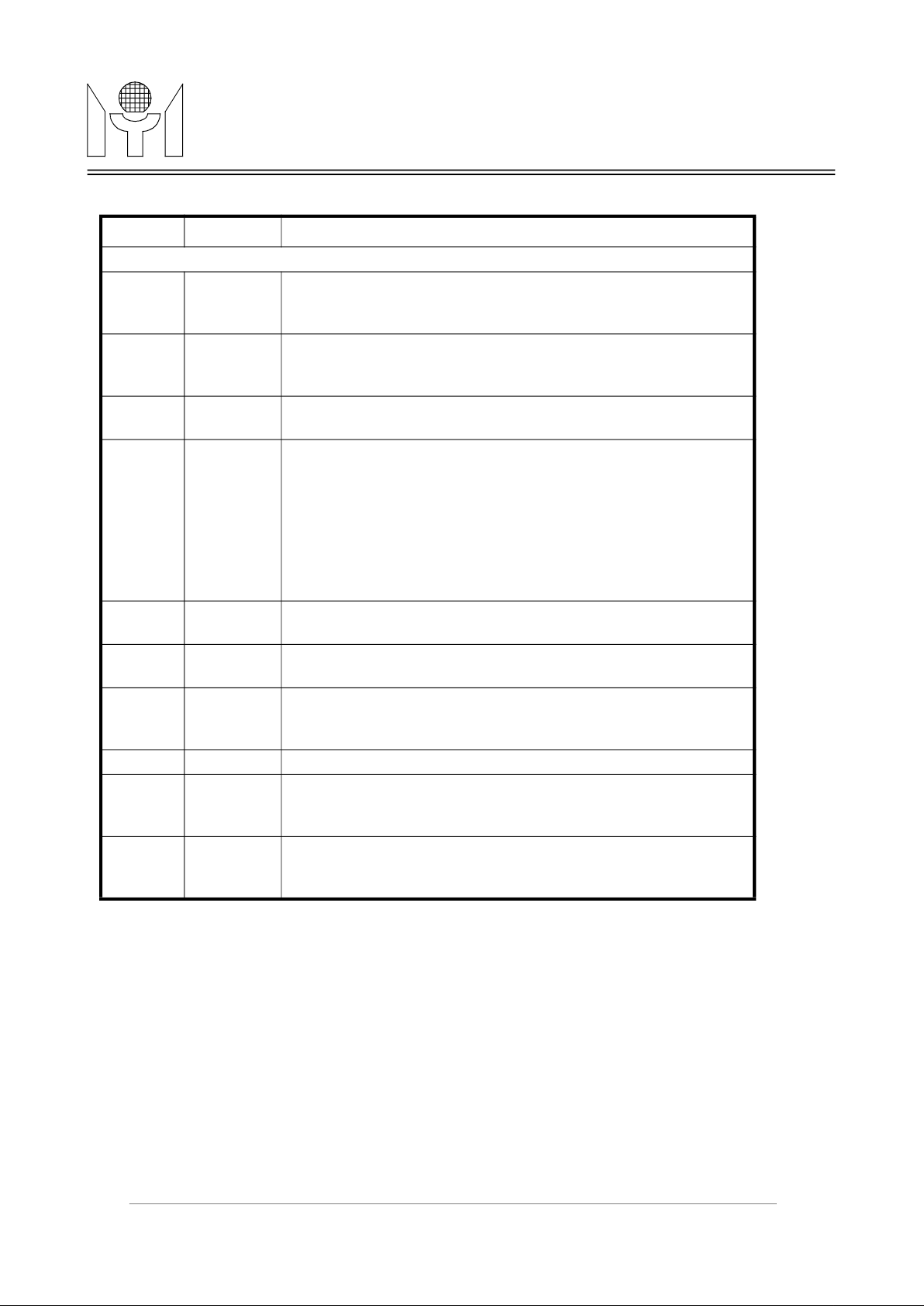

O

Figure 3.3 The Receive Descriptor Format

FLNG[10:0]

Reserved

Next Descriptor Address

RSR1

RSR0

RBS[10:0]

(Preliminary)

Table 3.3 Receive Descriptor 0 (RDES0)

Bit Symb ol Descrip t ion

31 OWN

tion.

30 - 28 - Reserved.

27 - 16 FLNG[11:0]

frame.

Receive Status Register 1( RSR1 )

15 - Reserved.

14 MAR

packet.

13 BAR

packet.

12 PHY Physical Address Received : The MTD800 receives a physical address

packet.

11 FSD First Descriptor : When set, indicates that the descriptor contains the first

10 LSD Last Descriptor : When set, indicates that the descriptor contains the last

9 - 8 - Reserved.

Receive Status Register 0 ( RSR0)

9/42 MTD800 Revision 0.0 07/20/1999

MYSON

3.4 Netw o rk Interf ace and MAC Proto c o l Handler

The network interface for transmit and receive function are both in a format of MII and ready for the intercon-

nection to PHY chip. The MTD800 defines a simple and efficient protocol for transforming the FIFO data back

and forth to a nibble-stream that is directly connected to MII. Meanwhile, the built-in Media Access Controller

(i) transmit function : encapsulates the nibble-stream coming from transmit DMA with preambles, Start Frame

(iii) CSMA/CD function : executes the listening before transmission, makes sure 96-bit time for interframe

gap , detects collision and enforces the event by issuing jam pattern, enters into backoff state after

collision and waits for retransmission .

incoming packet with the predefined flow control destination address ( .i.e. 01-80-c2-00-00-01 ) and length/

Error Summary: This bit is set to 1 for receive error, the errors include the

- Frame Alignment Error (FAE),

packet whose length is less than 64 bytes.

Long Packet Received : When set, indicates that the received frame

length exceeds the maximum Ethernet-specified size of 1518 bytes.

Frame Align Error : When set, indicates that the received frame has an

alignment Error.

MTD 800

TECHNOLOGY

Bit Symb ol Descrip t ion

7 ES

following

- Runt packet Error (RUNT),

- Long packet Error (LONG) ,

- CRC Error (CRC), and

- Receive coding Error (RXER).

6 RUNT Runt Packet Received : When set, indicates the MTD800 receives a

5 LONG

4 FAE

3 CRC CRC Error : When set, indicates a CRC error occurred on the received

frame.

2 RXER Receive Error : When s et, i ndicates a receive coding error occurred on

the received frame.

1 - 0 - Reserved

(Preliminary)

Table 3.4 Receive Descriptor 1 (RDES1)

Bit Symb ol Descr ipt ion

31 - 11 - Reserved

10 - 0 RBS Receive buffer size : Receive buffer size for this descriptor, the size is

measured in bytes. The buffer size must be a multiple of 4.

(MAC), which is compliant to IEEE 802.3, performs the following functions ;

Delimiter (SFD), the frame check sequence and the padding zeroes if necessary;

(ii) receive function : delimits the incoming packet , extracts the destination address for recognition and

checks frame validation before transferring data onto the internal receive FIFO;

The MAC of the MTD800 also supports full-duplex function and IEEE 802.3x flow control protocol. If the

10/42 MTD800 Revision 0.0 07/20/1999

MYSON

type field ( .i.e. 88-08 ), the MAC detects to receive the flow control packet and then pauses the transmission

process after the completion of the current transmitted packet. The MAC continues to transmit packets after

the pause-time has expired. On the other hand, the MAC can automatically send out a flow control packet

3.5 EEPROM and B o ot ROM Interfac e

Bus application, the CIS can also be saved in the EEPROM. The BootROM contains the codes for executing

a system boot function. Since EEPROM and BootROM share some I/O pins, these two devices can not be

bled at the same time.

3.5.1 EEPROM Contents

size of EEPROM ( e.g. 93C66 ) is required. The memory map of EEPROM and the bit field description for

MTD 800

TECHNOLOGY

once the fullness of receiving FIFO has reached a predefined threshold to prevent the FIFO from overflowing

and rendering packet loss.

The MTD800 uses EEPROM to store configuration data, Ethernet and Wake-up-Lan address etc. For Card-

ena

(Preliminary)

For desktop PCI application, the MTD800 only use 12 words to store configuration and address information.

Therefore, an EEPROM with the size of 64 x 16 bits ( i.e., 93C46 ) is enough to convey the data for such an

application. However, in the system of CardBus, it needs more space to save CIS data and usually a large

configuration words are shown in the following tables.

11/42 MTD800 Revision 0.0 07/20/1999

MYSON

(2) The low order byte of the first word contains the pointer to the last word of implementation specific area.

(4) The Card Bus CIS data are stored in the range addressed from 280H to 3FFH. The address is an offset

Last Word Pointer

SubSystem Vendor ID1

SubSystem Vendor ID0

Wake-up Lan Address 1

Wake-up Lan Address 0

Wake-up Lan Address 3

Wake-up Lan Address 2

Wake-up Lan Address 5

Wake-up Lan Address 4

Used for Card Bus Information Tuples

MTD 800

TECHNOLOGY

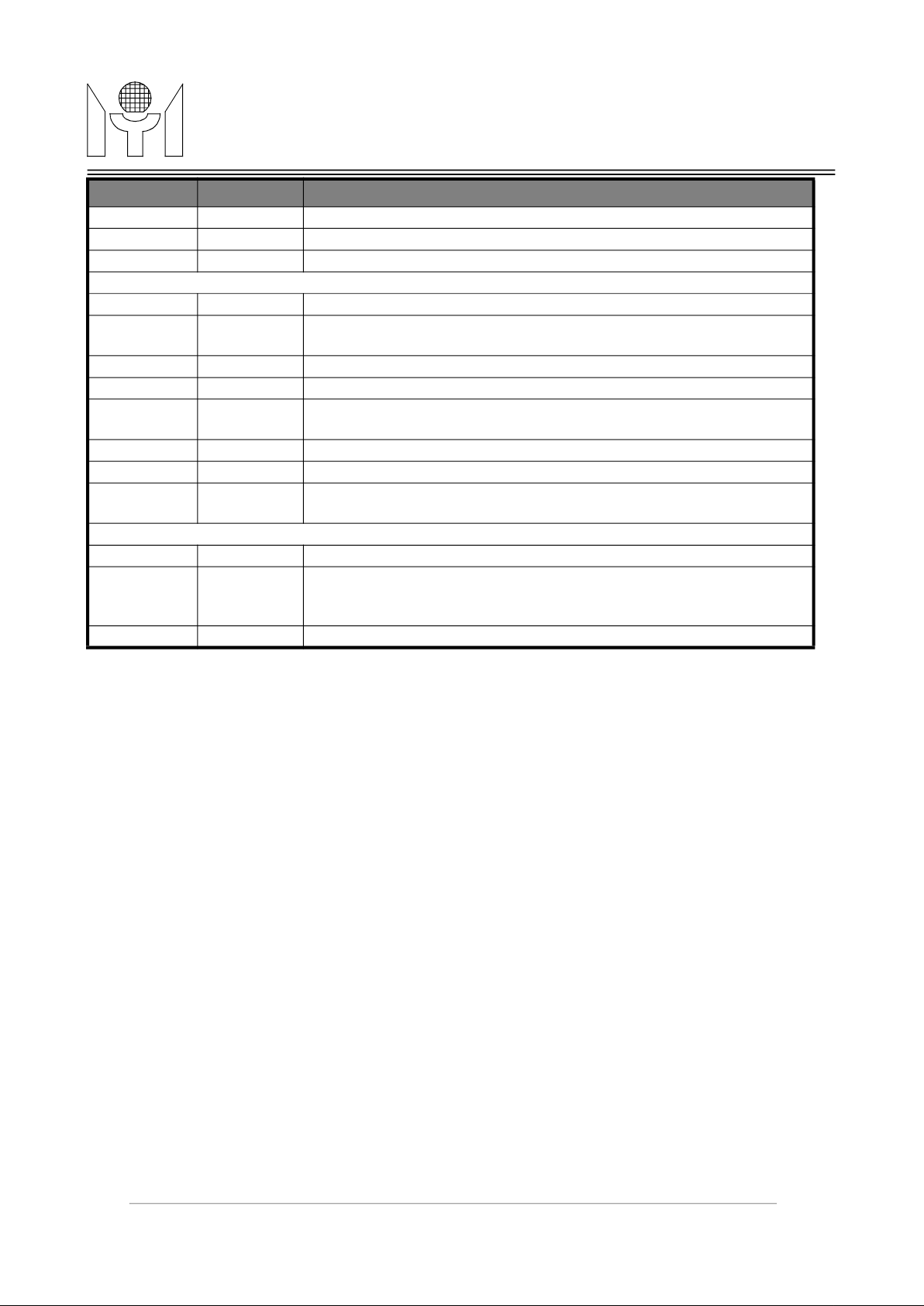

Table 3.5 EEPROM Memory Map

Offset D15 D8 D7 D0

00H 73H

01H CFG 0 202H

02H CIS Pointer 1 CIS Pointer 0 204H

03H CIS Pointer 3 CIS Pointer 2 206H

04H MAX_LAT MIN_GNT 208H

05H SubSystem ID1 SubSystem ID 0 20AH

06H

07H Reserved Reserved 20EH

08H Ethernet Address 1 Ethernet Address 0 210H

09H Ethernet Address 3 Ethernet Address 2 212H

0AH Ethernet Address 5 Ethernet Address 4 214H

0BH Reserved Reserved 216H

0CH

0DH

0EH

0FH Reserved Reserved 21EH

10H CFG 2 CFG 1 220H

11H Reserved Reserved

12H

|

3FH

40H

|

FFH

Reserved for future use

(Preliminary)

offset from

Mem Base

200H

20CH

218H

21AH

21CH

222H

27EH

280H

3FFH

|

|

Note:

(1) The above figure shows the layout of serial EEPROM which takes the size of 4K bits.

In this case, the value is “10H”. For different implementation, the area can be extended to “3FH’ in

maximum.

(3) The high order byte of the first word will be written as “73H” if the EEPROM has been programmed.

from Memory Base Address. The CIS can only be accessed from memory address space.

Table 3.6 Bit-Field Description of the Configuration words

Bit Symbol Desc ript ion

Configuration Register 0

7 PMC Pow er Management Capability. Corresponding to Bit 4 of CFSR.

6 NDFA Not Defined Flow control Address. Corresponding to Bit 12 of RCR.

12/42 MTD800 Revision 0.0 07/20/1999

MYSON

The MTD800 features a easy way to program external EEPROM in-suit. When the RESET is active and if the

upper byte of 00H on EEPROM is not 73H, the SROMPS bit in CSR40 register will be cleared to indicate that

ming mode if DPM bit is also set. In this mode the user can directly control the EEPROM interface signals by

writing to the SROM_CR Port and the value on the EECS, ESK and EDI bits will be driven onto the ECS,

EECLK( BRD2) and EEDI( BRD0) outputs respectively. These outputs will be latched so the user can gener-

ate a clock on EECLK by repetitively writing 1 then 0 to the appropriate bit. This can be used to generate the

EEPROM has already been programmed.

3.5.3 Boo t ROM Interface and Operatio n

Transmit Flow Control packet Enable. Corresponding to Bit 8 of TCR

Indicates the Boot ROM size. Corresponding to Bit 28 -26 of BROM_CR.

PME_Enable. When set, indicates that the chip can assert wake-up event

cleared, the wake-up pin is asserted low.

Magic Packet Enable. Corresponding to Bit 1 of WUECSR.

acts as a wake-up pin.

MTD 800

TECHNOLOGY

Bit Symbol Desc ript ion

5 TFCEN

4 - 2 BRSZ[2:0]

1 - 0 BRSPD[1:0] Boot ROM Speed Select. Corresponding to Bit 25 - 24 of BROM_CR.

Configuration Register 1

7 RFCEN Receive Flow Control packet Enable. Corresponding to Bit 13 of RCR.

6 PME

5 PSD3c PME Support D3cold. Corresponding to Bit 31 of CFPMR.

4 PSD1 PME Support D1. Corresponding to Bit 28 of CFPMR.

3 WPP

2 - Reserved.

1 MPE

0 STSCHG

7 - 2 - Reserved.

1 WPPN

0 - Reserved.

pin. Corresponding to Bit 8 of CFPMR.

Wake-up pin property. When set, the wake-up pin is asserted high, while

Status Change Enable. When set, the STSCHG pin is active, otherwise it

Configuration Register 2

Wake-up pin pattern. When set, the wake-up output pin is a level signal,

while cleared, the wake-up output pin is a pulse signal with the width of

160ms.

(Preliminary)

3.5.2 Direct Pro g ramm i n g of EEPROM

the current EEPROM has not been programmed yet. This allows the MTD800 to enter into Direct Program-

EEPROM signals as per the 93C46 or 93C66 data sheet.

To read out the EEPROM data, users have to generate EEPROM interface signals into ECS, EECLK and

EEDI as described above and in the mean time read the data from EEDO( BRD1 ) input via pin BRD1/EEDO.

Reading Data Transfer Port during programming will not affect the latched data on ECS, EECLK and EEDI

outputs. When the EEPROM has been programmed and verified ( remember to program the upper b yte of

00H with 73H), the user can give MTD800 a power-on reset to return to normal operation or set AUTOLD bit

to read in the new data.

The Direct Programming mode is mainly used for production to program every bit of the blank EEPROM. The

MTD800 also provides a flexible feature to allow the driver to reprogram the content of EEPROM, even the

13/42 MTD800 Revision 0.0 07/20/1999

Loading...

Loading...