MYSON MTD516 Datasheet

without notice. No liability is assumed as a result of the use of this procuts. No rights under any patent accompany the sales o

MYSON

GENERAL DESCRIPTION

IEEE802.3 and IEEE802.3u compliant.

packet filtering function.

4MB/2MB packet buffer with SGRAM/SDRAM

flexible memory interface.

Build in internal/external memory test function.

The MTD516 complies fully with the

The MTD516 provides EEPROM interface

agement interface.

MTD516

TECHNOLOGY

16 Port 10M/100M Ethernet Switch

FEATURES

•

• Provide 16 RMII (Reduced Media Independent

Interface) ports.

• Programmable 1K/8K MAC addresses filtering

database.

• Store and forward switching function and bad

• Optional back_pressure/802.3x flow control/

flooding control/broadcast control.

• Optional EEPROM Interface for advanced

switch configurations.

•

• Port VLAN/trunking.

• Link/Rx activity, packet buffer utilization LED

display.

• 83MHz for non-blocking 16 port switch.

•

• 208 pin PQFP package, 3.3V operation voltage.

(Preliminary)

IEEE802.3, 802.3u and 802.3x specifications and

is a non-blocking 16 port 10M/100M Ethernet

switch device.

Support 16 RMII ports for 10M/100M operation. 4MB memory interface provides maximum

2730 packet buffers for Ethernet packet buffering.

Up to 8192 address entrys are provided by the

MTD516, and the MTD516 use full Ethernet

address compare algorithm to minimize hashing

collision events.

to config port trunking, port VLAN, static entry,

802.3x flow control threshold, flooding port,

broadcast control threshold. Each MTD516 ports

support 10M/100M auto-negotiation by MII man-

The MTD516 also provides 2 pins for Link/

RX activity, packet buffer utilization LED display

function.

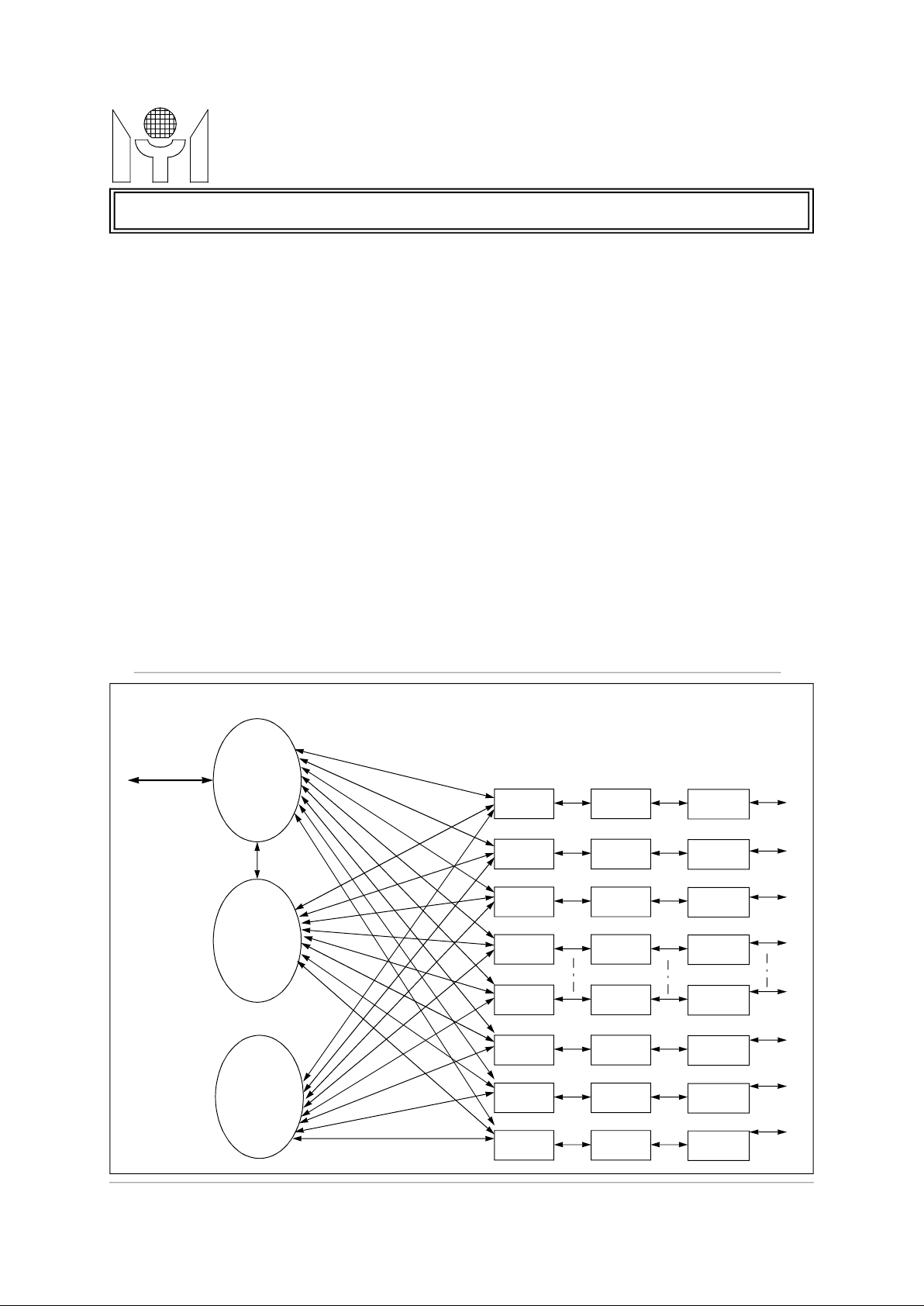

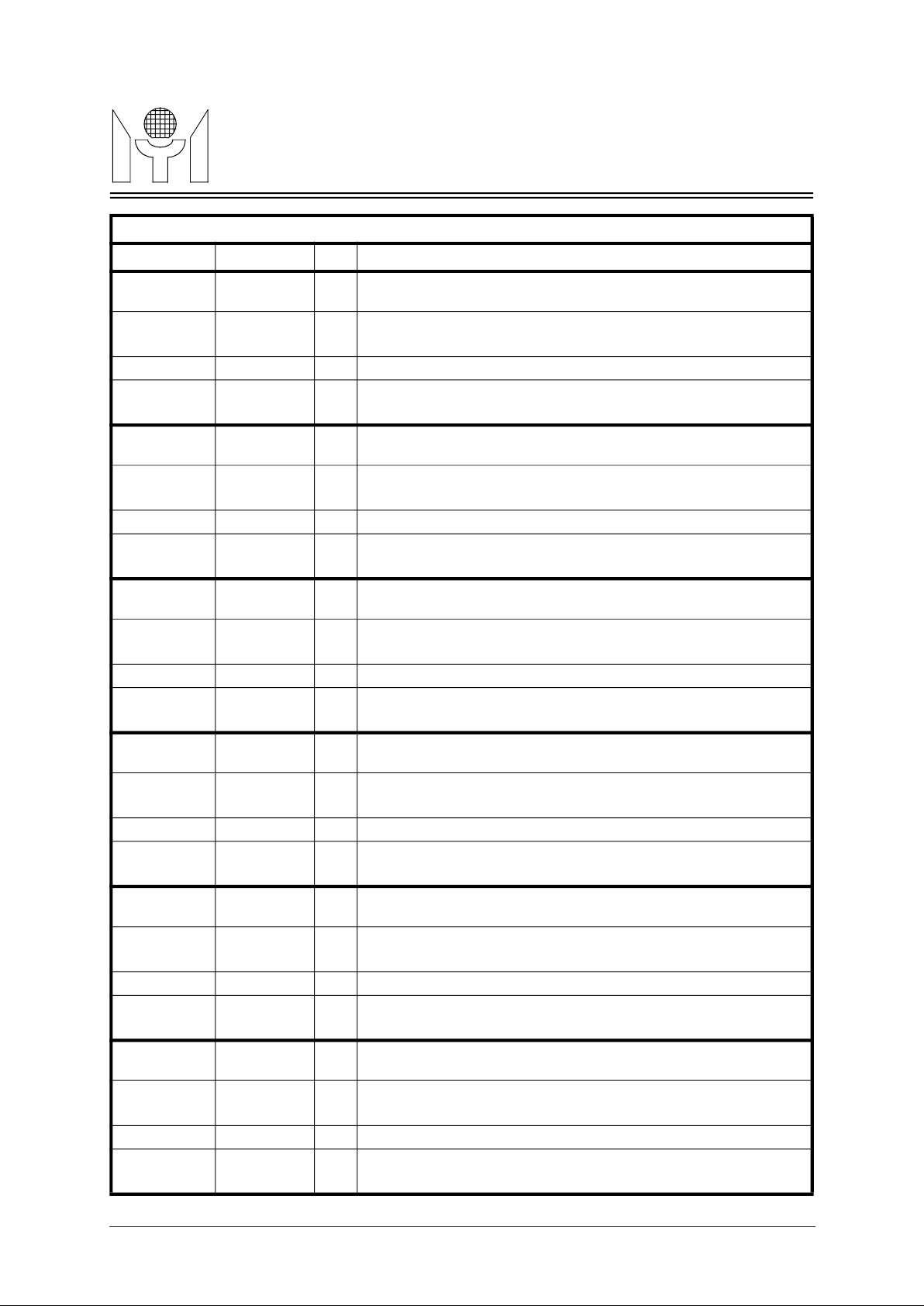

BL OCK DIAGRAM

SDRAM/

SGRAM

Interface

Memory

Controller

Memor y

Arbiter

Port

Switch

Logic

MAC0DMA0

MAC1DMA1

MAC2DMA2

MAC3DMA3

MAC4DMA4

MAC13DMA13

MAC14DMA14

MAC15DMA15

RMII0

RMII1

RMII2

RMII3

3~12

RMII12

RMII13

RMII14

RMII15

This datasheet contains new product information. Myson Technology reserves the rights to modify the product specification

the product.

1/27 MTD516 Revision 1.2 19/06/2000

f

without notice. No liability is assumed as a result of the use of this procuts. No rights under any patent accompany the sales o

MYSON

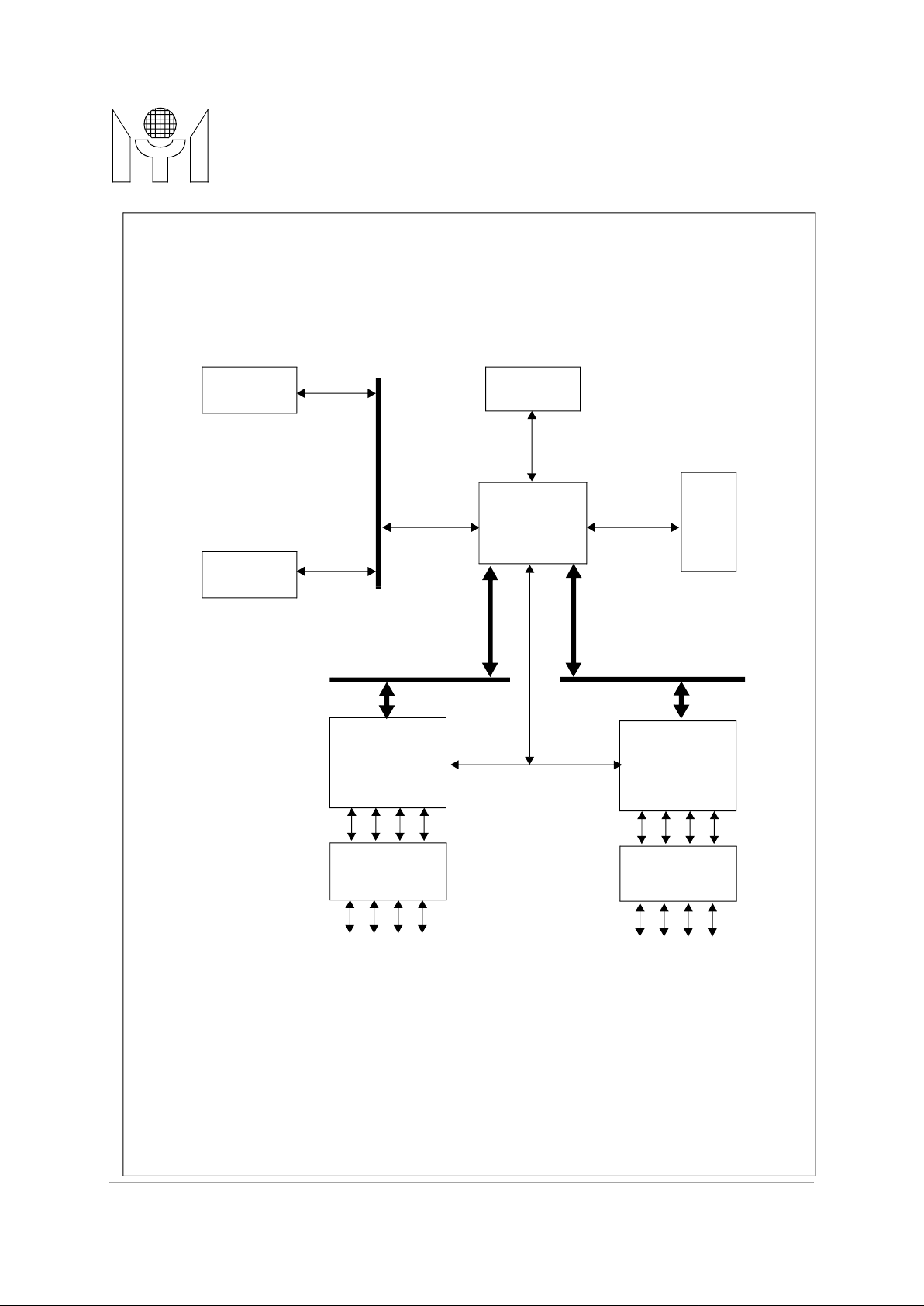

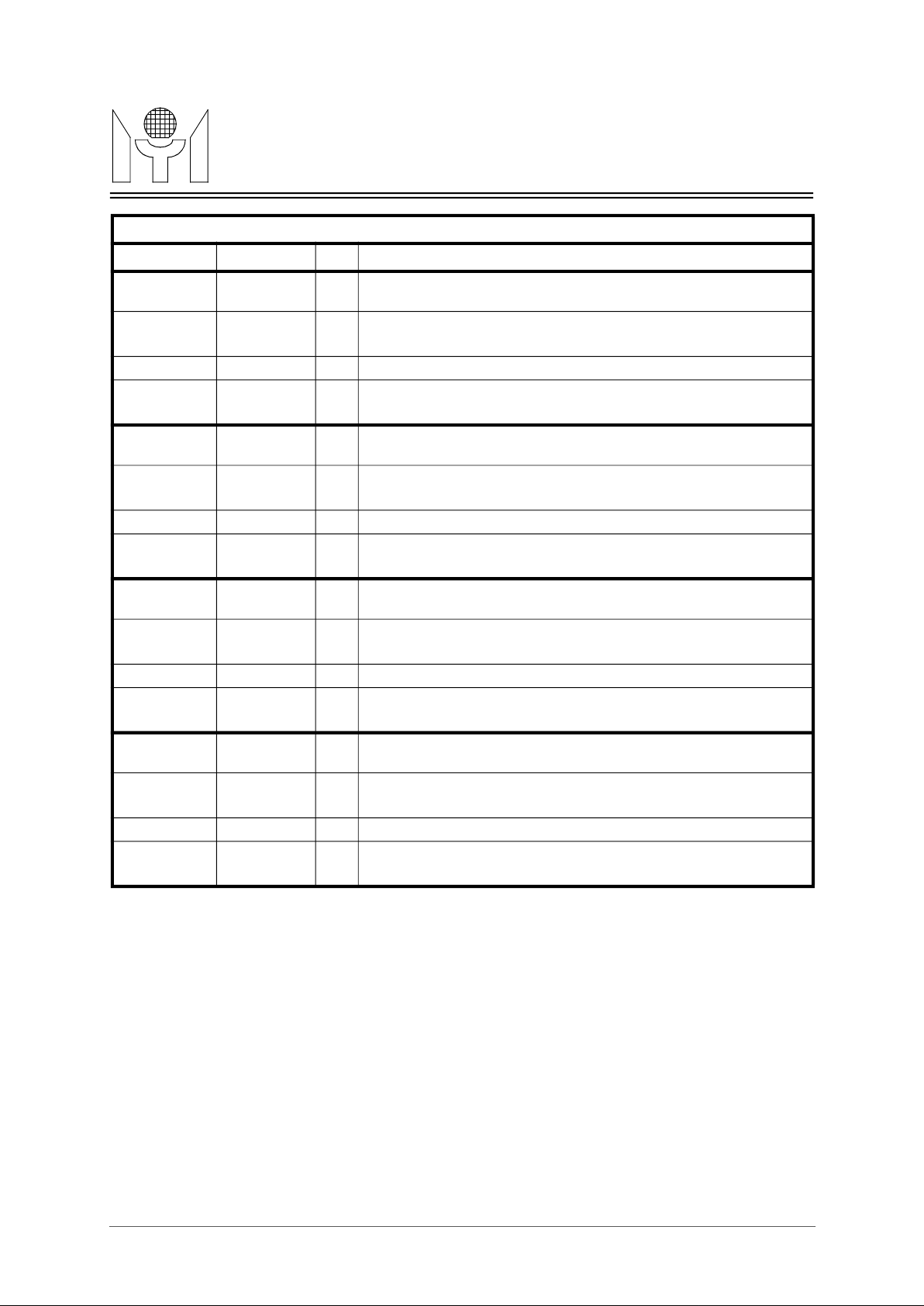

SYSTEM DIA GRAM

RMII11-15

Transfor mer

(**Pr ogra m mab le)

MII mana gement

MTD516

TECHNOLOGY

SGRAM

(512kx32x2)

SGRAM

(256kx32x2)

(**OPT I O N)

EEPROM

MTD516

(Preliminary)

LEDs

RMII 0-7

OCTAL

PHYsceiv er

OCTAL

Transfor mer

RJ45 RJ45

OCTAL

PHYsceiver

OCTAL

This datasheet contains new product information. Myson Technology reserves the rights to modify the product specification

the product.

2/27 MTD516 Revision 1.2 19/06/2000

f

MTD516 Revision 1.2 19/06/2000

MYSON

MTD516

TECHNOLOGY

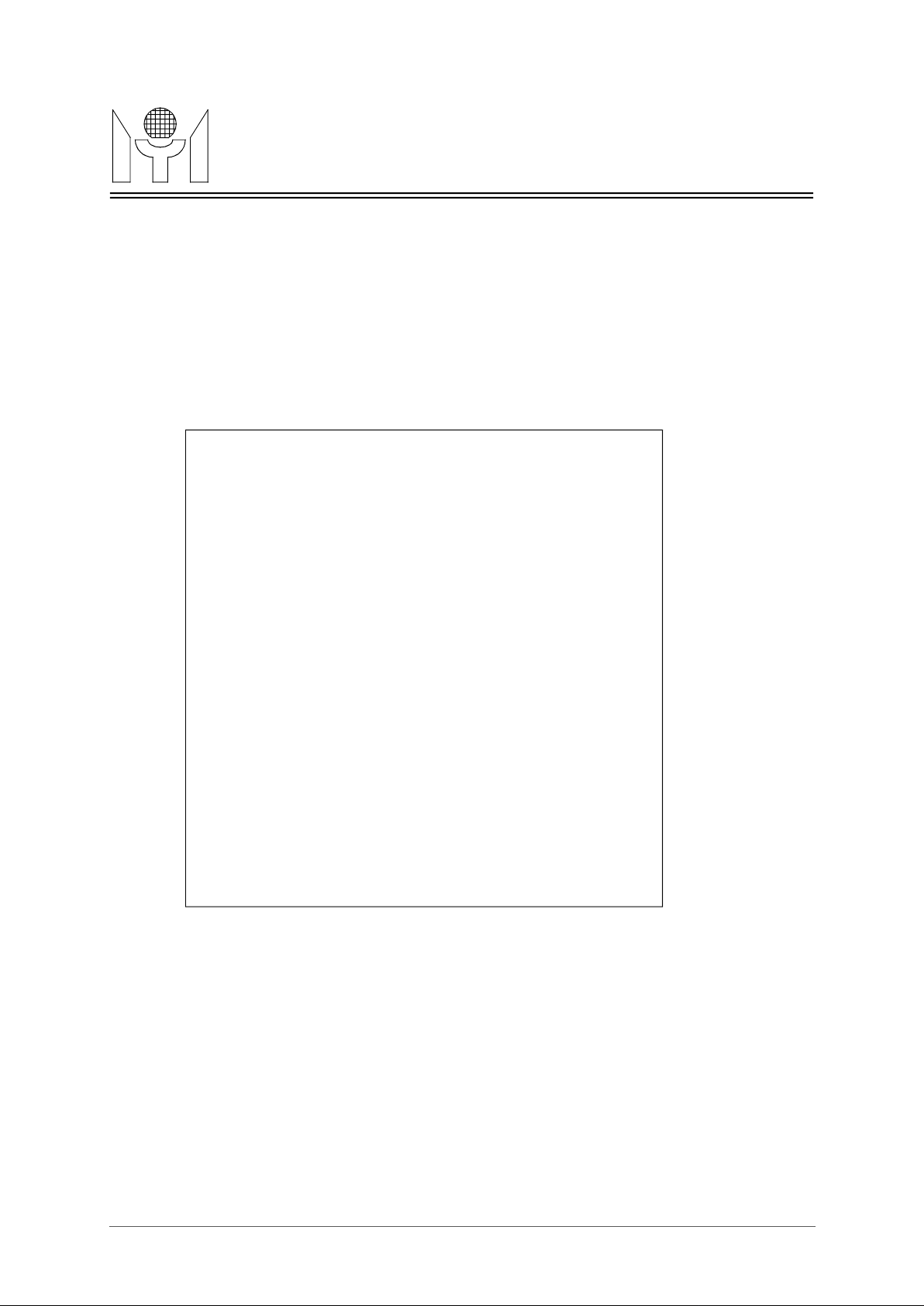

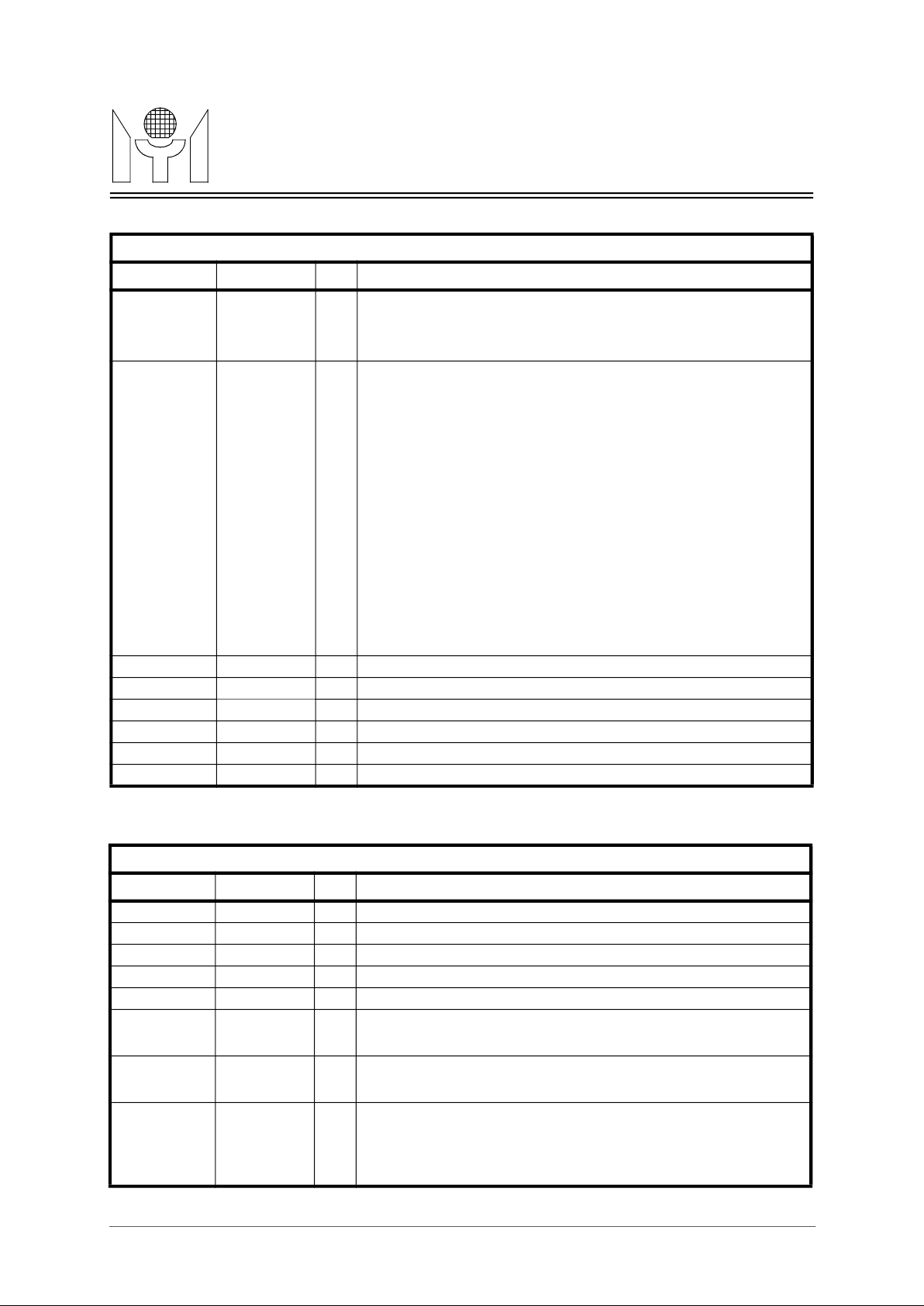

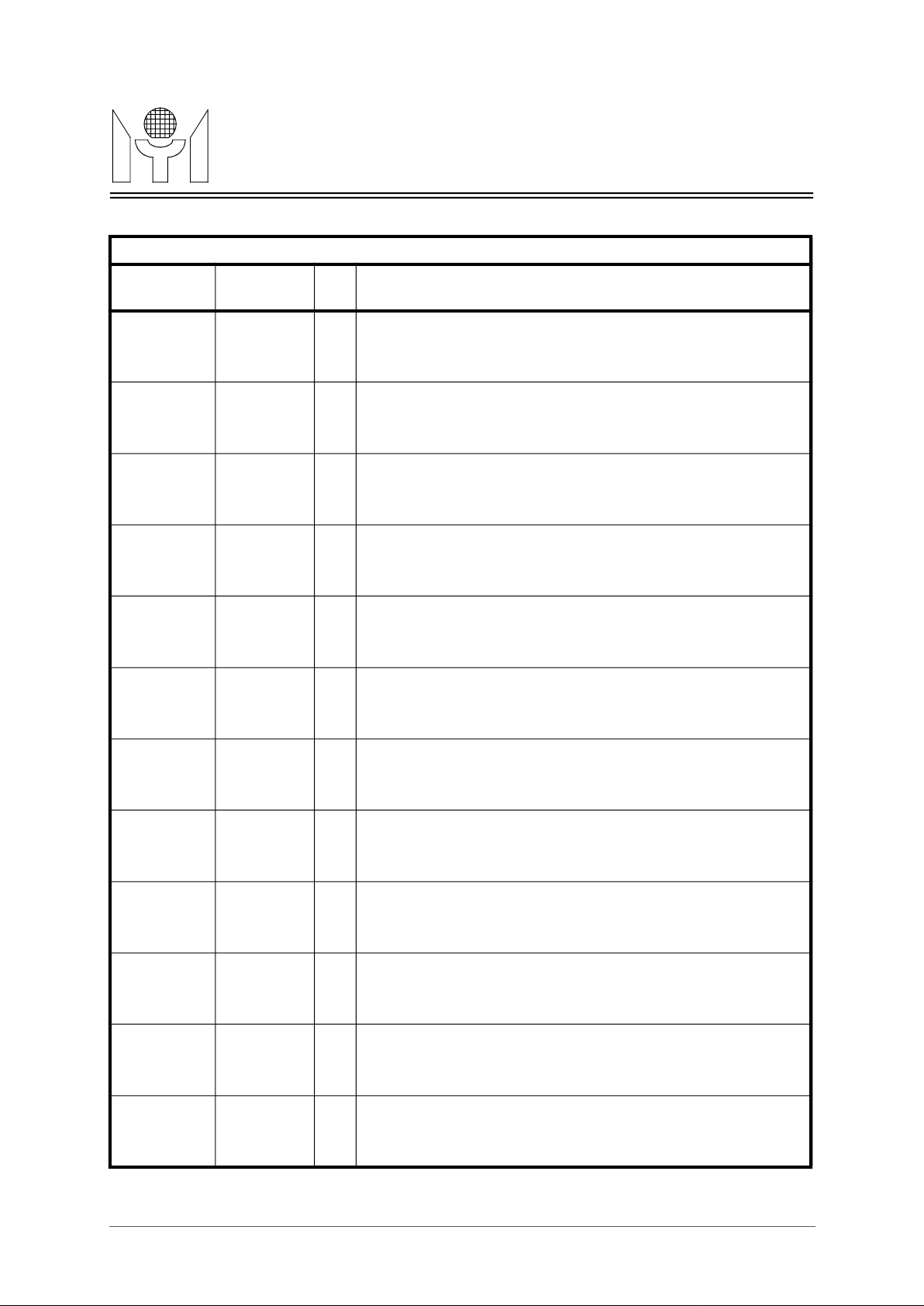

1.0 PIN CONNECTION

DQ9

DQ8

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

156

155

154

153

152

151

150

149

DQ10

DQ11

GND

VCC

DQ12

DQ13

DQ14

DQ15

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

LEDDATA

LEDCLK

EEDATA

EECLK

GND

REFCLK

VCC

RESETB

MDC

MDIO

TXD0_1

TXD0_0

TXEN0

CRSDV0

RXD0_0

RXD0_1

GND

VCC

TXD1_1

TXD1_0

TXEN1

CRSDV1

RXD1_0

RXD1_1

TXD2_1

TXD2_0

TXEN2

CRSDV2

RXD2_0

RXD2_1

TXD3_1

TXD3_0

TXEN3

CRSDV3

RXD3_0

RXD3_1

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

148

(Preliminary)

DQ7

DQ16

DQ17

DQ18

DQ19

DQ20

VCC

GND

DQ21

DQ22

DQ23

WEB

CASB

RASB

CS0BBAAD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

VCC

MEMCLK

GND

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ47

DQ46

DQ45

DQ44

VCC

GND

DQ43

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

DQ42

103

DQ41

102

DQ40

101

DQ32

100

DQ33

99

DQ34

98

DQ35

97

DQ36

96

DQ37

95

VCC

94

GND

93

DQ38

92

DQ39

91

DQ48

90

DQ49

89

DQ50

88

DQ51

87

DQ52

86

DQ53

85

DQ54

84

DQ55

83

VCC

82

MTD516

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

SYSCLK

GND

RXD15_1

RXD15_0

CRSDV15

TXEN15

TXD15_0

TXD15_1

RXD14_1

RXD14_0

CRSDV14

TXEN14

TXD14_0

TXD14_1

VCC

GND

RXD13_1

RXD13_0

CRSDV13

TXEN13

TXD13_0

TXD13_1

RXD12_1

RXD12_0

CRSDV12

TXEN12

TXD12_0

TXD12_1

RXD11_1

RXD11_0

010203040506070809101112131415161718192021222324252627282930313233343536373839404142434445464748495051

TXD4_1

TXD4_0

TXEN4

CRSDV4

RXD4_0

RXD4_1

TXD5_1

TXD5_0

TXEN5

GND

VCC

CRSDV5

RXD5_0

RXD5_1

TXD6_1

TXD6_0

TXEN6

CRSDV6

RXD6_0

RXD6_1

TXD7_1

TXD7_0

TXEN7

CRSDV7

RXD7_0

RXD7_1

GND

VCC

TXD8_1

TXD8_0

TXEN8

CRSDV8

RXD8_0

RXD8_1

TXD9_1

TXD9_0

TXEN9

CRSDV9

RXD9_0

RXD9_1

GND

VCC

TXD10_1

TXD10_0

TXEN10

CRSDV10

RXD10_0

RXD10_1

TXD11_1

TXD11_0

3/27

52

TXEN11

CRSDV11

MTD516 Revision 1.2 19/06/2000

MYSON

RMII Port Inter f ace Pins

Port0 RMII receive interface signal, CRSDV0 is asserted high when

port0 media is non_idle.

Port0 RMII transmit enable signal.

Port0 RMII transmit data bit_0.

Port0 RMII transmit data bit_1.

Port1 RMII receive interface signal, CRSDV1 is asserted high when

port1 media is non_idle.

Port1 RMII transmit enable signal.

Port1 RMII transmit data bit_0.

Port1 RMII transmit data bit_1.

Port2 RMII receive interface signal, CRSDV2 is asserted high when

port2 media is non_idle.

Port2 RMII transmit enable signal.

Port2 RMII transmit data bit_0.

Port2 RMII transmit data bit_1.

Port3 RMII receive interface signal, CRSDV0 is asserted high when

port3 media is non_idle.

Port3 RMII transmit enable signal.

Port3 RMII transmit data bit_0.

Port3 RMII transmit data bit_1.

Port4 RMII/MII receive interface signal, CRSDV4 is asserted high when

port4 media is non_idle.

Port4 RMII transmit enable signal

Port5 RMII receive interface signal, CRSDV5 is asserted high when

port5 media is non_idle.

Port5 RMII transmit enable signal.

Port5 RMII transmit data bit_0.

Port5 RMII transmit data bit_1.

MTD516

TECHNOLOGY

2.0 PIN DESCRIPTIONS

Name Pin Number I/O Descriptio ns

CRSDV0

RXD0_0

RXD0_1

TXEN0

TXD0_0

TXD0_1

CRSDV1

RXD1_0

RXD1_1

TXEN1

TXD1_0

TXD1_1

CRSDV2

186

187

188

185

184

183

194

195

196

193

192

191

200

I

IIPort0 RMII receive data bit_0.

Port0 RMII receive data bit_1.

O

O

O

I

IIPort1 RMII receive data bit_0.

Port1 RMII receive data bit_1.

O

O

O

I

(Preliminary)

RXD2_0

RXD2_1

TXEN2

TXD2_0

TXD2_1

CRSDV3

RXD3_0

RXD3_1

TXEN3

TXD3_0

TXD3_1

CRSDV4

RXD4_0

RXD4_1

TXEN4

TXD4_0

TXD4_1

CRSDV5

201

202

199

198

197

206

207

208

205

204

203

4

5

6

3

2

1

12

IIPort2 RMII receive data bit_0.

Port2 RMII receive data bit_1.

O

O

O

I

IIPort3 RMII receive data bit_0.

Port3 RMII receive data bit_1.

O

O

O

I

IIPort4 RMII/MII receive data bit_0.

Port4 RMII/MII receive data bit_1.

O

OOPort4 RMII/MII transmit data bit_0.

Port4 RMII/MII transmit data bit_1.

I

RXD5_0

RXD5_1

TXEN5

TXD5_0

TXD5_1

13

14

9

8

7

IIPort5 RMII receive data bit_0.

Port5 RMII receive data bit_1.

O

O

O

4/27

MTD516 Revision 1.2 19/06/2000

MYSON

Port6 RMII receive interface signal, CRSDV6 is asserted high when

port6 media is non_idle.

Port6 RMII transmit enable signal.

Port6 RMII transmit data bit_0.

Port6 RMII transmit data bit_1.

Port7 RMII receive interface signal, CRSDV7 is asserted high when

port7 media is non_idle.

Port7 RMII transmit enable signal.

Port7 RMII transmit data bit_0.

Port7 RMII transmit data bit_1.

Port8 RMII receive interface signal, CRSDV8 is asserted high when

port8 media is non_idle.

Port8 RMII transmit enable signal.

Port8 RMII transmit data bit_0.

Port8 RMII transmit data bit_1.

Port9 RMII receive interface signal, CRSDV9 is asserted high when

port9 media is non_idle.

Port9 RMII transmit enable signal.

Port9 RMII transmit data bit_0.

Port9 RMII transmit data bit_1.

Port10 RMII receive interface signal, CRSDV10 is asserted high when

port10 media is non_idle.

Port11 RMII receive interface signal, CRSDV11 is asserted high when

port11 media is non_idle.

Port11 RMII receive data bit_0.

Port11 RMII receive data bit_1.

Port11 RMII transmit enable signal.

Port11 RMII transmit data bit_0.

Port11 RMII transmit data bit_1.

RMII Port Inter f ace Pins

MTD516

TECHNOLOGY

Name Pin Number I/O Descriptio ns

CRSDV6

RXD6_0

RXD6_1

TXEN6

TXD6_0

TXD6_1

CRSDV7

RXD7_0

RXD7_1

TXEN7

TXD7_0

TXD7_1

CRSDV8

18

19

20

17

16

15

24

25

26

23

22

21

32

I

IIPort6 RMII receive data bit_0.

Port6 RMII receive data bit_1.

O

O

O

I

IIPort7 RMII receive data bit_0.

Port7 RMII receive data bit_1.

O

O

O

I

(Preliminary)

RXD8_0

RXD8_1

TXEN8

TXD8_0

TXD8_1

CRSDV9

RXD9_0

RXD9_1

TXEN9

TXD9_0

TXD9_1

CRSDV10

RXD10_0

RXD10_1

TXEN10

TXD10_0

TXD10_1

CRSDV11

33

34

31

30

29

38

39

40

37

36

35

46

47

48

45

44

43

52

IIPort8 RMII receive data bit_0.

Port8 RMII receive data bit_1.

O

O

O

I

IIPort9 RMII receive data bit_0.

Port9 RMII receive data bit_1.

O

O

O

I

IIPort10 RMII receive data bit_0.

Port10 RMII receive data bit_1.

O Port10 RMII transmit enable signal.

OOPort10 RMII transmit data bit_0.

Port10 RMII transmit data bit_1.

I

RXD11_0

RXD11_1

TXEN11

TXD11_0

TXD11_1

53

54

51

50

49

I

I

O

O

O

5/27

MTD516 Revision 1.2 19/06/2000

MYSON

Port12 RMII receive interface signal, CRSDV12 is asserted high when

port12 media is non_idle.

Port12 RMII transmit enable signal.

Port12 RMII transmit data bit_0.

Port12 RMII transmit data bit_1.

Port13 RMII receive interface signal, CRSDV13 is asserted high when

port13 media is non_idle.

Port13 RMII transmit enable signal.

Port13 RMII transmit data bit_0.

Port13 RMII transmit data bit_1.

Port14 RMII receive interface signal, CRSDV14 is asserted high when

port14 media is non_idle.

Port14 RMII transmit enable signal.

Port14 RMII transmit data bit_0.

Port14 RMII transmit data bit_1.

Port15 RMII receive interface signal, CRSDV15 is asserted high when

port15 media is non_idle.

Port15 RMII transmit enable signal.

Port15 RMII transmit data bit_0.

Port15 RMII transmit data bit_1.

RMII Port Inter f ace Pins

MTD516

TECHNOLOGY

Name Pin Number I/O Descripti ons

CRSDV12

RXD12_0

RXD12_1

TXEN12

TXD12_0

TXD12_1

CRSDV13

RXD13_0

RXD13_1

TXEN13

TXD13_0

TXD13_1

CRSDV14

58

59

60

57

56

55

64

65

66

63

62

61

72

I

IIPort12 RMII receive data bit_0.

Port12 RMII receive data bit_1.

O

O

O

I

IIPort13 RMII receive data bit_0.

Port13 RMII receive data bit_1.

O

O

O

I

(Preliminary)

RXD14_0

RXD14_1

TXEN14

TXD14_0

TXD14_1

CRSDV15

RXD15_0

RXD15_1

TXEN15

TXD15_0

TXD15_1

73

74

71

70

69

78

79

80

77

76

75

IIPort14 RMII receive data bit_0.

Port14 RMII receive data bit_1.

O

O

O

I

IIPort15 RMII receive data bit_0.

Port15 RMII receive data bit_1.

O

O

O

6/27

MTD516 Revision 1.2 19/06/2000

MYSON

Note: SGRAM/SDRAM access time: 10 ns (max)

Synch ro n o u s DRAM/GRAM Interface Pins

Memory row/column address bus outputs

AD[7:0] are row/column address [7:0].

Memory data bus DQ[63:56] : 119~112

DQ[47:44] : 111~108

DQ[11:8] : 158~155

SGRAM/SDRAM row address select

SGRAM/SDRAM write enable

Memory chip select 0

Memory clock output.

Miscellaneous Pins

System reset input, low active.

Switch core system clock input

MII management clock inout.

MII management data inout

After 150 ms, it indicate SDC.

After 150 ms, it indicate SDIO.

MTD516

TECHNOLOGY

Name Pin Number I/O Descriptions

AD[8:0]

123~131

DQ[63:0]

RASB 134 O

CASB 135 O SGRAM/SDRAM column address select

WEB 136 O

BA 132 O SGRAM/SDRAM bank select

CS0B 133 O

MEMCLK 121 O

119~112,

84~91,

111~108,

105~102,

92~93,

96~101,

172~165,

137~139,

142~146,

164~161,

158~155,

147~154

O

AD[8] : This pin should connect to SGRAM/SDRAM MSB address bit.

I/O

DQ[55:48] : 84~91

DQ[43:40] : 105~102

DQ[39:38] : 92~93

DQ[37:32] : 96~101

DQ[31:24] : 172~165

DQ[23:21] : 137~139

DQ[20:16] : 142~146

DQ[15:12] : 164~161

DQ[7:0] : 147~154

(Preliminary)

Name Pin Number I/O Descriptions

RESETB 180 I

SYSCLK 82 I

REFCLK 178 I RMII reference clock input

MDC 181 I/O

MDIO 182 I/O

EECLK/

SDC

EEDATA/

SDIO

LEDCLK

176

175

174

I/O After ResetB deassert to ? ms , this pin indicate EECLK,

I/O After ResetB deassert to ? ms , this pin be indicated EEDATA,

I/O LED Clock.

Using bursted clock for latching 32 display informations (one clock

latch one information) , per burst have 32 continuous clocks (clock

period = 320 ns); and the time between burst to burst is 655 us.

7/27

MTD516 Revision 1.2 19/06/2000

MYSON

The serial output display informations using bursted styling ,per burst

have 32 informations, as following:

01 P0_RxAct 17 Uti_1%

02 P1_RxAct 18 Uti_3%

03 P2_RxAct 19 Uti_5%

04 P3_RxAct 20 Uti_10%

05 P4_RxAct 21 Uti_15%

06 P5_RxAct 22 Uti_20%

07 P6_RxAct 23 Uti_30%

08 P7_RxAct 24 Uti_35%

09 P8_RxAct 25 Uti_40%

10 P9_RxAct 26 Uti_50%

11 P10_RxAct 27 Uti_60%

12 P11_RxAct 28 Uti_70%

16 P15_RxAct 32 MemTestFail

Miscellaneous Pins

MTD516

TECHNOLOGY

Name Pin Number I/O Descriptions

LEDDA TA

173

I/O LED Data (high_active).

LEDCLK LEDDATA LEDCLK LEDDATA

(Preliminary)

VCC 1 1,28,42,68,

83,95,107,

122,141,160,

179,190,

GND 10,27,41,67,

81,94,106,

120,140,159,

177,189,

13 P12_RxAct 29 Uti_80%

14 P13_RxAct 30 Uti_90%

15 P14_RxAct 31 BufferAlarm

PWR Power pins

GND Ground pins

8/27

MTD516 Revision 1.2 19/06/2000

MYSON

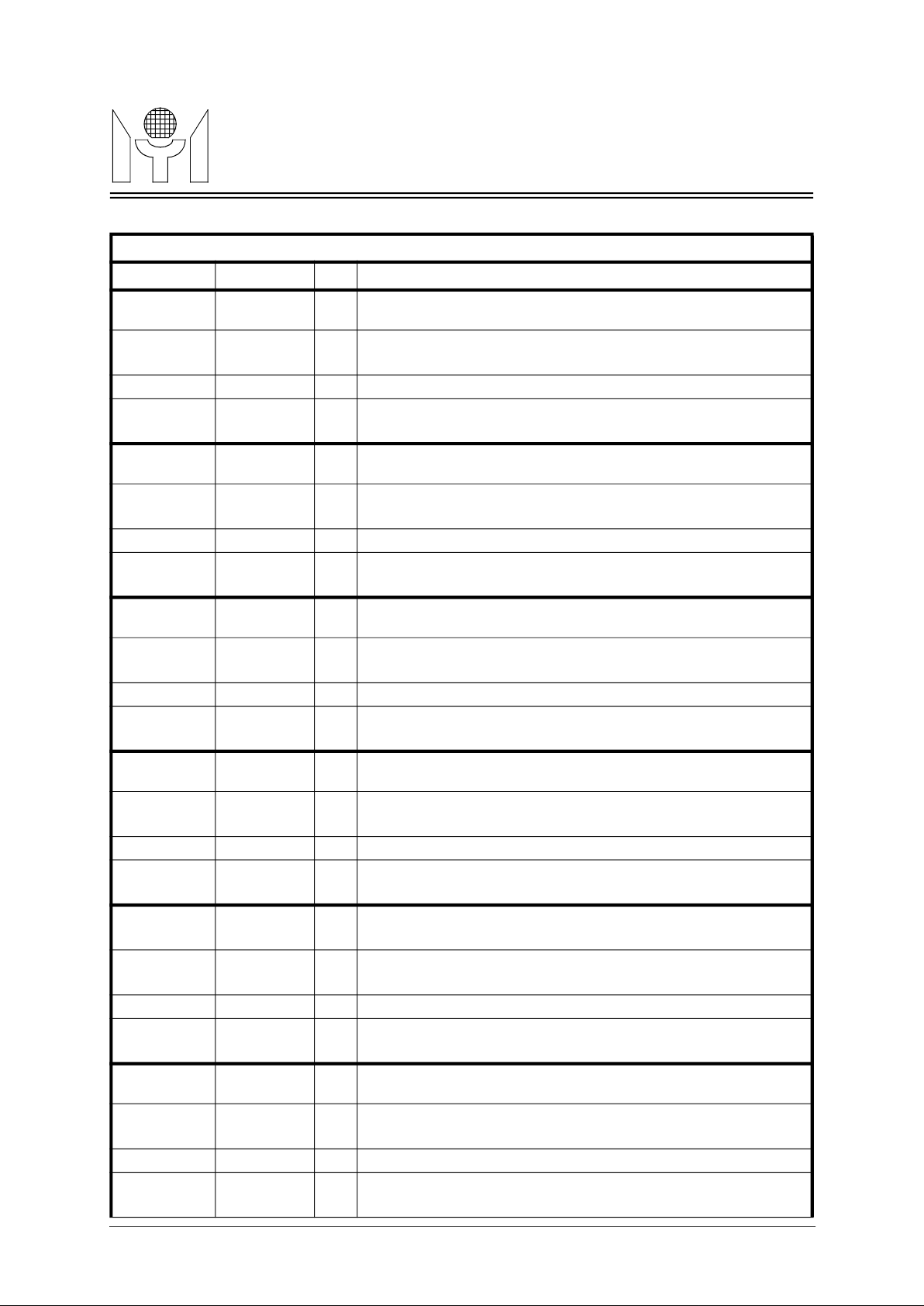

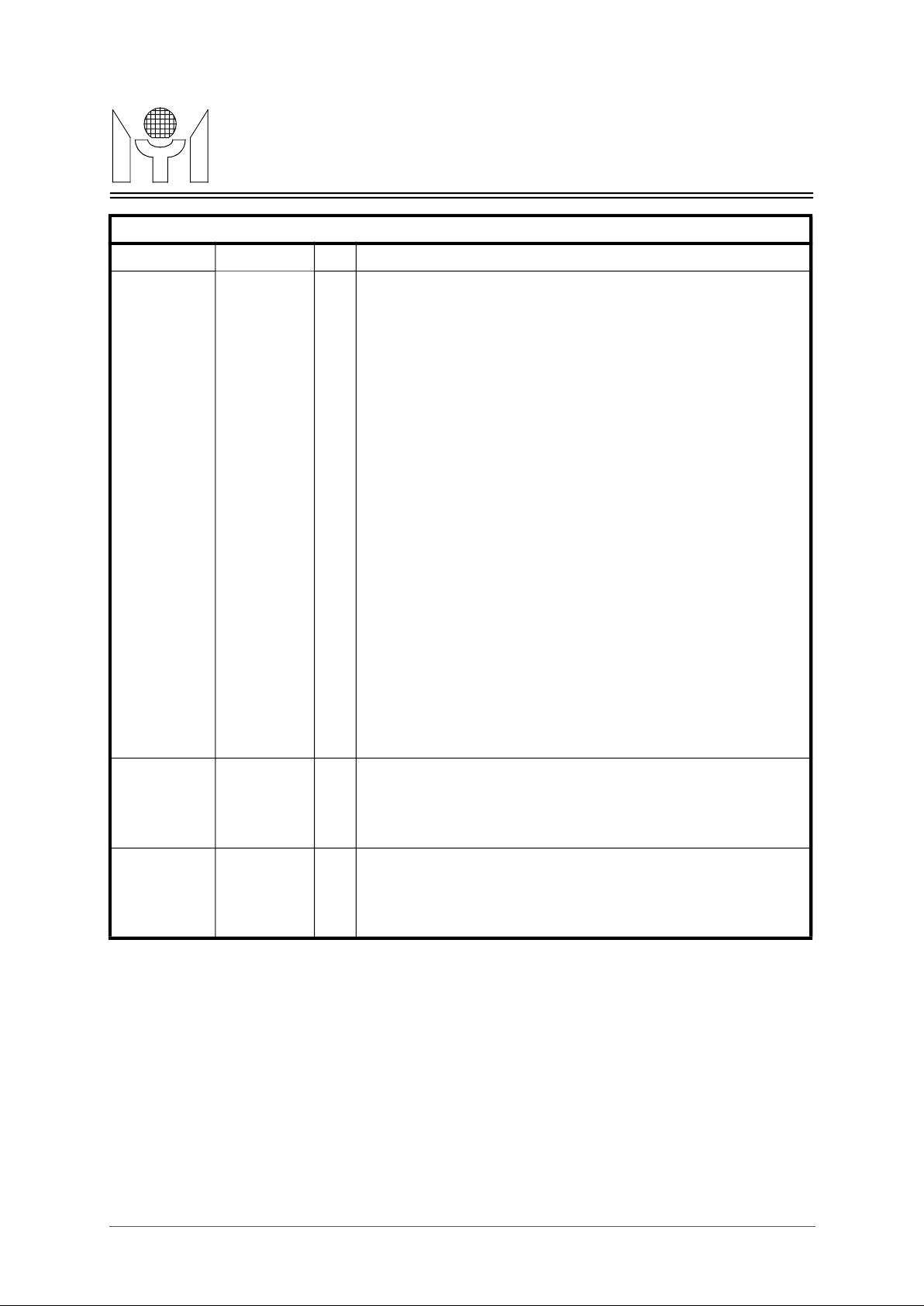

Power on Setti ng Config uratio n

Jump er Configu ratio n After Power On Reset

802.3x flow control function enable.

external pull_hgih =1, 802.3x flow control enable.

external pull_low = 0, backpressure disable.

external pull_hgih =1, memory BIST enable.

external pull_low = 0, memory BIST disable.

external pull_hgih =1, chip fast test mode enable.

external pull_hgih =1, chip scan test mode enable.

8K entry address table enable.

external pull_low = 0, 8K address table disable; defaule is 1K entry.

Auto_load from EEPROM function enable.

Broadcast storm protect function enable.

external pull_hgih =1, 12 port switch enable.

Port 15 FX function indicator.

MTD516

TECHNOLOGY

3.0

Pin Name Function

MDC

FlowCtrlEn

EECLK

BakPsureEn

EEDA TA

MiiPollEn

LEDCLK

AgingEn

LEDDA TA

BISTEn

(Preliminary)

defa

ult

1

external pull_low = 0, 802.3x flow control disable.

1 In Half duplex mode, backpressure function enable.

external pull_hgih =1, backpressure enable.

1 Polling PHY device’s MII register function enable.

external pull_hgih =1, PHY auto polling enable.

external pull_low = 0, PHY auto polling disable.

1 Aging out function for address learning enable.

external pull_hgih =1, aging out function enable.

external pull_low = 0, aging out function disable.

1 Embbeded memory self-test function enable.

Descriptio ns

TXEN13

TXEN12

TXEN11

TXEN10

TXEN9

TXEN8

TXEN7

FastMode

ScanMode

8KAddrTblEn

EEPROMEn

BroadStor-

mEn

En12PortSW

P15FXEn

0 For chip test only.

external pull_low = 0, chip fast test mode disable.

0 For chip test only.

external pull_low = 0, chip scan test mode disable.

0

external pull_hgih =1, 8K address table enable.

0

external pull_hgih =1, auto load from EEPROM function enable.

external pull_low = 0, auto load from EEPROM function disable.

0

external pull_hgih =1, broadcast storm protection enable.

external pull_low = 0, broadcast storm protection disable.

0 For 12 port switch, only Port11~Port0 enable.

external pull_low = 0, default is 16 port switch.

0

external pull_hgih =1, port15 FX function enable.

external pull_low = 0, port15 FX function disable.

9/27

Loading...

Loading...